# EXTREME TEMPERATURE MEMORY DESIGN WITH THE REDUCED DESIGN TIME USING SILICON ON SAPPHIRE TECHNOLOGY

By

#### ZHE YUAN

Bachelor of Science in Electrical Engineering Sichuan Institute of Technology Chengdu, Sichuan, China 2002

Master of Science in Electrical Engineering Syracuse University Syracuse, NY 2004

Submitted to the Faculty of the

Graduate College of the

Oklahoma State University

in partial fulfillment of

the requirements for

the Degree of

DOCTOR OF PHILOSOPHY/EDUCATION

Dec., 2011

# EXTREME TEMPERATURE MEMORY DESIGN WITH THE REDUCED DESIGN TIME USING SILICON ON SAPPHIRE TECHNOLOGY

| Dissertation Approved:       |

|------------------------------|

| Dr. Chriswell Hutchens       |

| Dissertation Adviser         |

| Dr. James Stine              |

| Dr. Louis Johnson            |

| Dr. Nohpill Park             |

| Outside Committee Member     |

| Dr. Sheryl A. Tucker         |

| Dean of the Graduate College |

#### **ACKNOWLEDGMENTS**

I would like to take this opportunity to thank my committee chair and advisor Dr. Chriswell Hutchens and express my sincere gratitude for his valuable advice, patience and contribution. Especially I would like to thank him on my guidance in memory design and ADC design. I wish to express my sincere thanks to Dr. Louis Johnson, Dr. James E. Stine and Dr. Nohpill Park for serving on my graduate committee.

I feel proud to have served as a research assistant in the Mixed Signal VLSI Design Lab for 6 years at Oklahoma State University. It has been a wonderful and exciting learning opportunity and research experience at MSVLSI Lab. I would like to thank Dr. Liu, Dr. Hooi Miin Soo, Dr. Vijayraghavan Madhuravasal, Mr. Ranganthan Sridharan, Mr. Srikanth Vellore, Mr. Ran Liao for all their help and suggestions along the course of this work.

I want to thank for my parents for their constant encouragement, love and support. To all of them I dedicate this work.

#### **GLOSSARY**

SRAM Static Random-access Memory

ROM Read-only Memory

NMOS n-channel Metal-Oxide-Semiconductor

PMOS p-channel Metal-Oxide-Semiconductor

I<sub>D</sub> Dain Current

V<sub>DS</sub> Drain to Source Voltage

V<sub>GS</sub> Gate to Source Voltage

KP  $\mu C_{ox}$

KP<sub>P</sub> KP of PMOS

KP<sub>N</sub> KP of NMOS

μ Mobility

C<sub>ox</sub> Oxide Capacitance

I<sub>ON</sub> On-state Current

I<sub>OFF</sub> Off-state Current

V<sub>TH</sub> Threshold Voltage

ASIC Application Specific Integrated Circuit

IC Integrated Circuit

LVS Layout Versus Schematic

LEF Library Exchange Format

VHDL VHSIC (Very High Speed Integrated Circuits) Hardware Description

Language

Verilog Hardware Description Language

VDD Supply Voltage

GND Ground

VSS Ground

VTC Voltage Transfer Characteristic

DRC Design Rule Check

I/O Input/Output

ALF Advanced Library Format

TLF Timing Library Format

RTL Register Transfer Level

OSU Oklahoma State University

MSVLSI mixed signal circuit design group of OSU

U<sub>T</sub> Thermal Voltage

V<sub>SB</sub> Source to Body Voltage

$V_{TH0}$  Threshold Voltage with  $V_{SB} = 0$

RTL Register transfer level

# TABLE OF CONTENTS

| Chapter                                             | Page |

|-----------------------------------------------------|------|

| I. INTRODUCTION                                     | 11   |

| 1.1 Research Objective                              | 11   |

| 1.2 OSU cell library, HC11 and LEON3                | 12   |

| 1.3 SOI and Bulk Comparison                         | 16   |

| 1.3.1 High Speed, Low Power and High Device Density |      |

| 1.2.2 Low Leakage                                   |      |

| 1.2.3 No Latch Up                                   |      |

| 1.2.4 Floating Body Effect                          |      |

| 1.3 Design Methodologies                            |      |

| 1.4 Dissertation organization                       |      |

| II. ACCURATE DATA FOR CELL LIBRARY AND MEMORY       | 22   |

| 2.1 Measured ION/IOFF, Threshold and Mobility       | 22   |

| 2.2 Summery                                         |      |

| III. CELL LIBRAY AND MEMORY DESIGN                  | 31   |

| 3.1 Introduction                                    | 31   |

| 3.2 Cell Library Design                             |      |

| Chapter                                  | Page |

|------------------------------------------|------|

| 3.3 Memory Design                        | 34   |

| 3.3.1 The Architecture of the Memories   | 34   |

| 3.3.2 Critical Delay Path                |      |

| 3.3.3 General SRAM Design Issues         |      |

| 3.3.4 PMOS SRAM Cell Design              |      |

| 3.3.5 Stacked-NMOS Sense Amp Design      |      |

| 3.3.6 ROM Design                         |      |

| 3.3.7 8T SRAM Cell Design                |      |

| 3.4 Summary                              |      |

| IV. MEMORY TESTING                       | 51   |

| 4.1 Introduction                         | 51   |

| 4.2 SRAM Testing                         |      |

| 4.2.1 SRAM Testing Condition             |      |

| 4.2.2 SRAM Testing Analysis              |      |

| 4.2.3 SRAM Testing Diagnosis             |      |

| 4.2.4 SRAM Testing on PCB                | 64   |

| 4.3 ROM Testing                          |      |

| 4.3.1 ROM Testing Condition              | 65   |

| 4.3.2 ROM Testing Analysis               | 66   |

| 4.3.3 ROM Testing Diagnosis              |      |

| 4.4 Cache Testing                        | 71   |

| 4.5 Testing Summary                      | 74   |

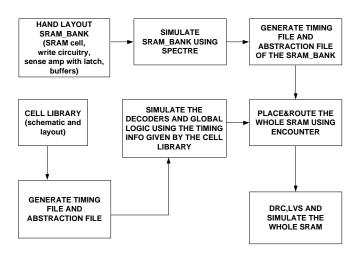

| V. SRAM DESIGN WITH ENCOUNTER SUPPORT    | 75   |

| 5.1 Introduction                         | 75   |

| 5.2 Memory design with Encounter Support | 75   |

| VI. CONCLUSIONS                          | 80   |

| REFERENCES                               |      |

| APPENDICES                               | 86   |

### LIST OF TABLES

| ΓABLE                                                                                                     | Page |

|-----------------------------------------------------------------------------------------------------------|------|

| 1.1 Comparison of SOI and Bulk CMOS                                                                       | 19   |

| 2.1 I <sub>ON</sub> /I <sub>OFF</sub> ratio and the variations of I <sub>ON</sub> /I <sub>OFF</sub> ratio | 25   |

| $2.2\ V_{TH}$ and the variations of $V_{TH}$ at different temperatures                                    | 28   |

| 2.3 Kp at different temperatures                                                                          |      |

| 2.4 $I_{ON}$ and $I_{OFF}$ and the variations of $I_{ON}$ and $I_{OFF}$ at 200 $^{\circ}$ C               |      |

| 2.5 $I_{ON}$ and $I_{OFF}$ and the variations of $I_{ON}$ and $I_{OFF}$ at 275 $^{\circ}$ C               | 30   |

| 3.1 SRAM cell worst case $V_{TH}$ at 200 $^{\circ}$ C                                                     | 38   |

| 3.2 K <sub>kink</sub> values for different lengths NMOS                                                   | 40   |

| 3.3 I <sub>ON</sub> and I <sub>OFF</sub> and their variations of SRAM pass transistors at 200 °C          | 44   |

| 4.1 4K SRAM testing error die of 2008 and 2007                                                            | 55   |

| 4.2 SRAM testing error classification                                                                     | 59   |

| 4.3 2K ROM testing error die of 2008 and 2007                                                             | 66   |

| 4.4 ROM testing error classification                                                                      |      |

| 4.5 Possible shorted-circuit summery                                                                      |      |

| 5.1 Comparison of SRAM design with Encounter support and hand-layout SRA                                  | M79  |

|                                                                                                           |      |

# LIST OF FIGURES

| Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1 General Flow for creating a standard cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1.5 a) Parasitic BJT inside a PD SOS NMOS transistor (b) $I_D$ - $V_{DS}$ characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| of High $V_{TH}$ NMOS with width equals 16@3.6 um, length equals 2 um. Measured                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $I_D \text{ at } V_{DS} \text{ equals } 0.2V, 0.4V, 0.6V, 0.8V, V_{GS} \text{ equals } 0 \sim 3.6V \text{ at } 195 \text{ C}. \\ 19 \\ 2.1 \text{ (a)} I_D \text{ vs } V_{DS} \text{ for } 20 \text{ x } 1.4\text{um}/1.4\text{um high } V_{TH} \text{ NMOS}, V_{DS}=0 \text{ to } 3.3V, \\ V_{GS}=0.8V \text{ to } 3.3V \text{ in } 6 \text{ steps at room temperature. (b) } I_D \text{ vs } V_{DS} \text{ of the same } \\ \text{device at low } V_{GS}, V_{GS}=0.4V \text{ to } 1.2V \text{ in } 5 \text{ steps. Note solid data is simulated and } \\ \text{dashed is measured.} \\ 23 \\ 2.2 I_{ON}/I_{OFF} \text{ ratio over (room to } 275 \text{ °C) for RP W equals } 20 \text{ x } 1.4\text{um, L equals } \\ 0.8\text{um, and RN W equals } 20 \text{ x } 1.4\text{um, L equals } 1.6\text{um. Measured } I_{ON} \text{ at } V_{DS} \\ \text{equals } 50\text{mV}, V_{GS} \text{ equals } 3.6\text{Vand } I_{OFF} \text{ at } V_{DS} \text{ equals } 3.6\text{V}, V_{GS} \text{ equals } 0\text{V} $ |

| 2.4 V <sub>TH0</sub> over (room to 275 °C) for RP W equals 20 x 1.4um, L equals 0.8um, and RN W equals 20 x 1.4um, L equals 1.6um. Calculated at V <sub>DS</sub> equals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 50mV, V <sub>GS</sub> equals 0 ~3.3V at 50mV each step                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1V, V <sub>DS</sub> equals 50mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.2 The 2K x16 SRAM block diagram for LEON3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.3 LEON3 write and read timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.4 6T PMOS SRAM cell schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

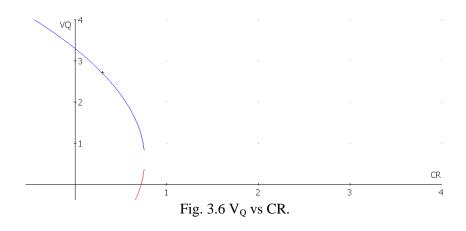

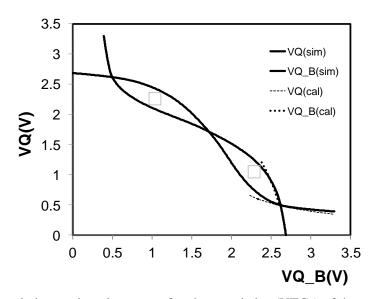

| 3.6 V <sub>O</sub> vs CR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

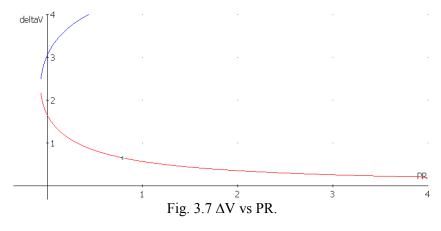

| 3.7 ΔV vs PR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

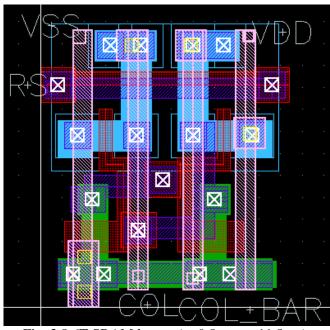

| 3.8 6T SRAM layout (x=9.8um, y=11.8um)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| inverters during read access of the cell are represented by the solid curves. The sam | ıe |

|---------------------------------------------------------------------------------------|----|

| VTCs from calculation are represented by the dash curves                              | 43 |

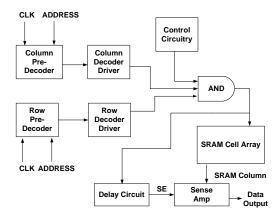

| 3.10 SRAM's read circuitry block diagram                                              | 45 |

| 3.11 Current-mode latch sense amp with precharge and PMOS diode bank bias circuit.    | 46 |

| 3.12 2K ROM structure                                                                 | 47 |

| 3.13 ROM cell structure                                                               | 48 |

| 3.14 128 x 32 cache structure                                                         | 48 |

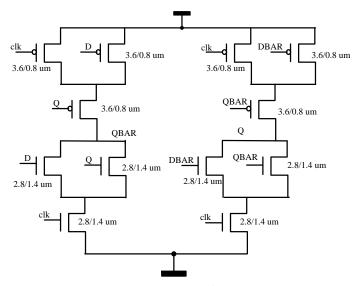

| 3.15 8T SRAM cell schematic                                                           | 49 |

| 4.1 SRAM/ROM failure types                                                            | 54 |

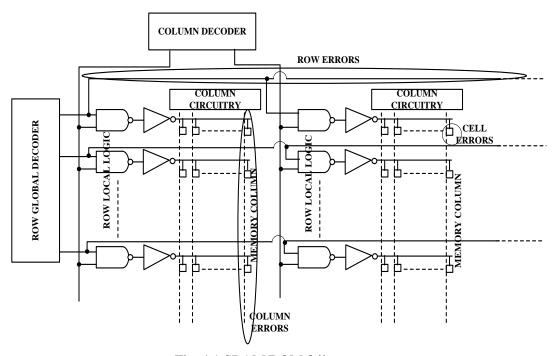

| 4.2 4K SRAM structure with the error locations                                        | 56 |

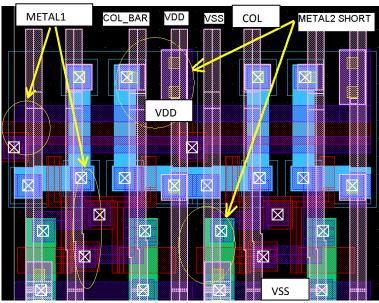

| 4.3 6T-SRAM cell layout in 2008 with possible shorts                                  | 56 |

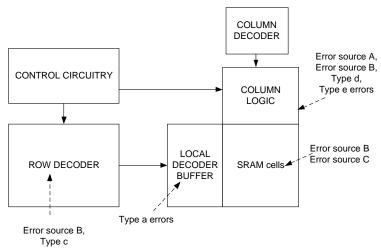

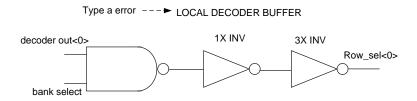

| 4.4 Local decoder buffer                                                              | 60 |

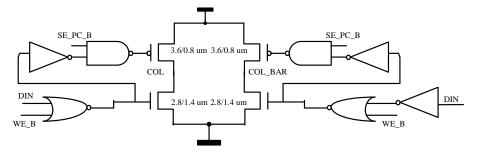

| 4.5 SRAM write circuitry                                                              | 61 |

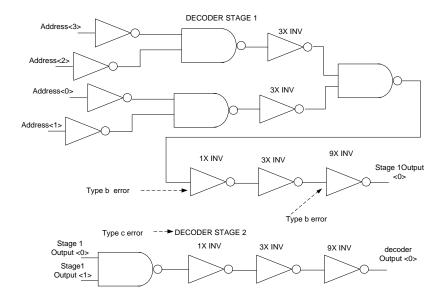

| 4.6 Main decoding path of global row decoder                                          | 61 |

| 4.7 SRAM/ROM latch for column read                                                    | 61 |

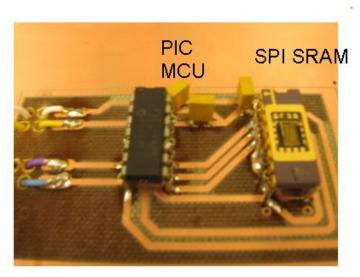

| 4.8 PIC and SRAM chips on PCB.                                                        | 65 |

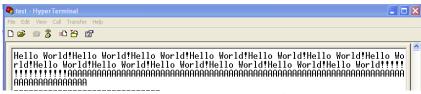

| 4.9 HyperTerminal output for PIC                                                      | 65 |

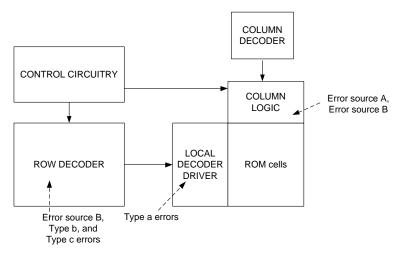

| 4.10 ROM structure with error sources.                                                | 69 |

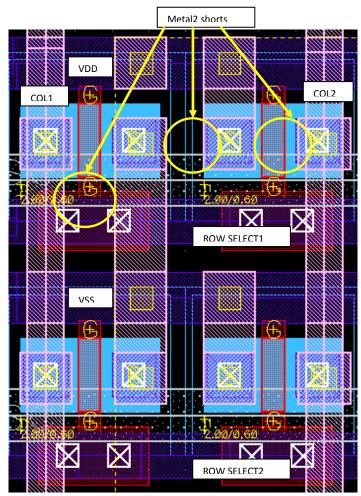

| 4.11 ROM cell layout in 2008 with possible shorts                                     | 69 |

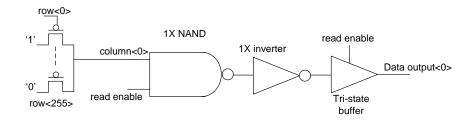

| 4.12 ROM read circuitry in 2008 design                                                | 71 |

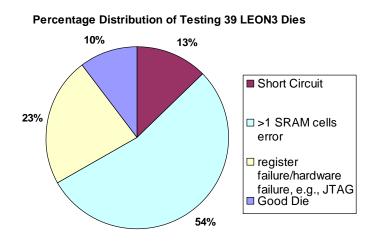

| 4.13 Percentage Distribution of Testing 39 LEON3 Die                                  | 72 |

| 5.1 Basic SRAM structure                                                              | 76 |

| 5.2 SRAM design with Encounter support                                                | 76 |

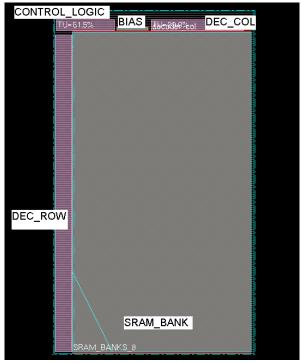

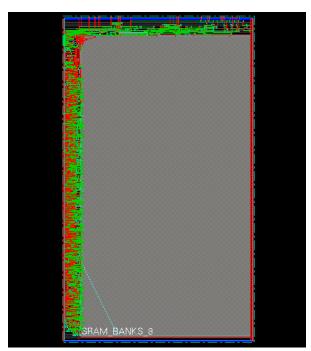

| 5.3 Floor plan of the SRAM                                                            | 78 |

| 5.4 Nanorout of the SRAM                                                              | 79 |

#### CHAPTER I

#### INTRODUCTION

#### 1.1 Research Objective

High temperature integrated circuit design is a challenge for conventional bulk-silicon integrated circuit technology. Bulk technologies are used to 150 °C for the automotive market but are generally unavailable due to increased leakage current at higher temperatures [46][47] and limited market demand. The increased leakage current is caused by substrate and well diodes, and threshold voltage roll-off at elevated temperatures. To address these issues, the 0.5um Peregrine Silicon-on-Sapphire (SOS) technology is selected to minimize the drain/source to body diode leakage. The detailed advantages and disadvantages are discussed in Section 1.3.

This dissertation describes high temperature memories for microcontroller design using 0.5 um Peregrine SOS CMOS technology, which are suitable for aerospace, well logging, solar controllers, and automotive applications. The designed memories are as part of the design for 275  $^{\circ}$ C HC11 microcontroller and 200  $^{\circ}$ C LEON3 processor [9]. For the HC11, the design simulations are over the -55  $^{\circ}$ C to 295  $^{\circ}$ C range with testing completed over the room to 295  $^{\circ}$ C range. For the LEON3, the design simulations are over the -55  $^{\circ}$ C to 200  $^{\circ}$ C range with testing completed over the room to 200  $^{\circ}$ C range. The detailed testing is discussed in CHAPTER IV.

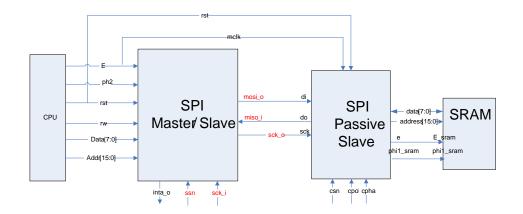

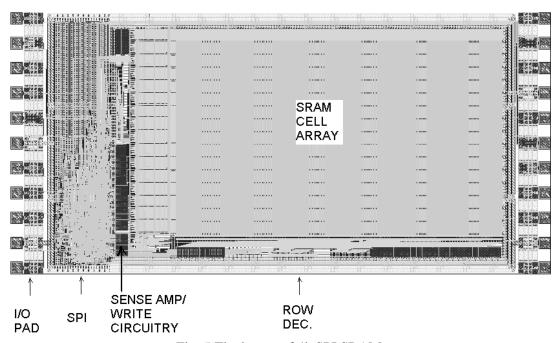

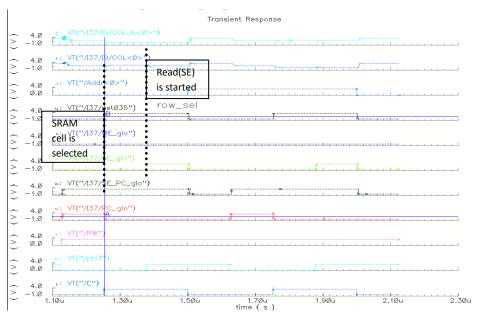

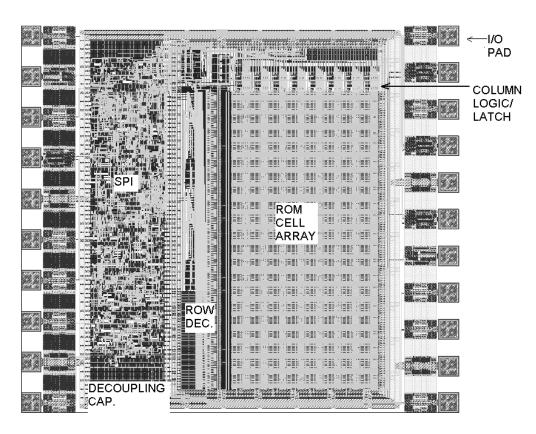

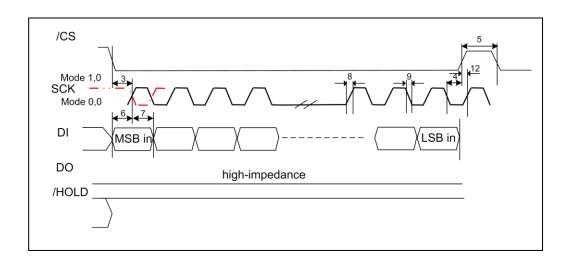

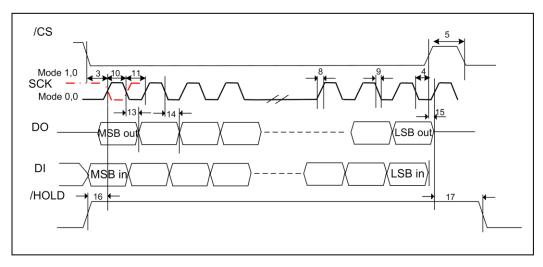

The memories having been designed include: a 4K on-chip SRAM, 512byte on-chip ROM, 4K SPI-SRAM, 2K SPI-ROM, 2K x16 off-chip SRAM, 128 x 32 cache, 32 x 32 cache, and SRAM design with Encounter support. The on-chip 4K SRAM is used to store the data and instructions executed by the HC11 microcontroller. The on-chip 512byte ROM is able to perform a sequence of the HC11 peripherals and registers self-test process; and it control the bootstrap process to boot from either SCI

or SPI interface. The 4K SPI-SRAM is used for off-chip storage of data and software routines to be uploaded and executed by the HC11. The 2K SPI-ROM is used to store a small monitor program, 68MON which is a monitor/debugger program for the HC11. Both on-chip and off-chip ROMs are the customer mask designs. The masking operation was completed separately from the other structures and programmed using a combination of Matlab and Cadence SKILL language. The offchip 2K x 16 SRAMs are used for program and data storage, and they communicate with the LEON3 using a memory controller bridge. The 128 x 32 caches are used in LEON3 for high speed data and instruction storage. The 32x32 cache is used for the register file in the LEON3. The on-chip memories were designed using hand-layout, then instantiated as cells and placed and routed with HC11 and LEON3, respectively. The SRAM design with Encounter support basically uses the Encounter tool to Place & Route SRAM, which reduces the design time from 11 weeks to 6 weeks. The HC11 microcontroller along with SPI SRAM and ROM was developed to produce a down-hole microcomputer system (DMS) for Department of Energy/National Energy Technology Laboratory (DOE/NETL). The LEON3 processor with on-chip caches was developed for the use in jet engine sensor data acquisition for NAVAIR. The detailed designs of these memories are discussed in CHAPTER III. The specifications of SPI SRAM and ROM are described in Appendix B and C.

#### 1.2 OSU cell library, HC11 and LEON3

The HC11 (operating at 275 °C, 3.3V and 3 MHz) consists of a microprocessor, arithmetic logic unit (ALU), a small boot ROM (512 bytes), 4K byte data RAM, counter/timer unit, serial peripheral interface (SPI), asynchronous serial interface (SCI), and the A, B, C, and D parallel ports (except port E). The LEON3 (operating at 200 °C, 3.3V and 18 MHz) is configured with a 128 x 16 instruction cache, a 128 x 16 data cache with tag, a 32 x 32 register file, JTAG, generic APB UART, CAN controller, interrupt controller, timer, LEON3 memory controller, an AHB controller, AHB/APB bridge, LEON3 debug support unit, general input/output ports, and analog can-driver.

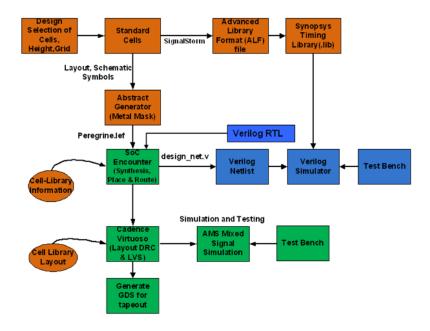

HC11 and LEON3 circuit blocks along with the standard cell libraries were designed by OSU's MSVLSI design group [9] with the assistance from Aeroflex Gaisler which maintained the LEON3 code [41]. The standard cell libraries with the timing file and abstraction file were generated using the Cadence Characterization tool; the on-chip memories were designed using hand-layout, then instantiate as cells with the timing file and abstraction file; the Cadence Ambit synthesizer took the HC11 or LEON3 code (VHDL or Verilog RTL code) and generated a netlist of the circuit implementation using the characterized cell libraries and memories. LEON3 and HC11 have gate counts of 128,839 and 50,449, respectively. Without a standard cell library based Place & Route, the designer could spend years to produce hand-layout while experience many layout errors. The SRAM design with Encounter support was also synthesized, placed and routed using the characterized standard cell library and SRAM bank. As in Fig. 1.1, the design procedures of a standard cell library are described below:

- 1) The transistor width and length are chosen as discussed in Chapter II. The geometries of the transistors in the cell library can be determined to satisfy the worst case corners. The designed library cells have sufficient I<sub>ON</sub>/I<sub>OFF</sub> ratio to avoid design errors which may be caused by inaccurate Peregrine model. Furthermore, the cell designs satisfy a beta-matched requirement providing more robust behavior.

- 2) All the schematics in the cell library are simulated using Cadence Spectre.

- Layouts in the cell library are generated as dense as possible and DRC/LVS is used to verify

if the layout has correct connection and correct transistor size.

- 4) The cells are characterized using Cadence Characterization tool. The generated .lib file has functionality, timing and power information. The .lib file is a standard format required for integrating the standard cells into digital logic. The generated .lef file is a standard format to be used in Place & Route which defines blockages of routing layers and blockages of pins.

Fig. 1.1 General flow for creating a standard cell [40].

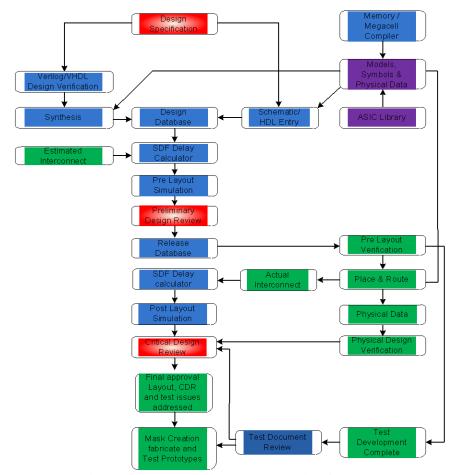

The standard cell library based ASIC design flow, Fig. 1.2 [40], categorizes the entire design procedure of HC11 and LEON3.

- 1) Cell libraries with .lib and .lef files are generated using Cadence Characterization tool. The memory cell is not able to be characterized using Cadence Characterization tool because of its complexity. However, the memory blocks can be simulated in Cadence and a .lib file can be generated manually. The input and output timings with the specified input and output capacitances are filled in the memory library file. The .lef file is generated the same as the cell library. The .v file with timing of the memory is generated with input and output timings and later used in step 3) and 4).

- 2) HC11 and LEON3 codes are finished using Verilog or VHDL at RTL level.

- 3) HC11 and LEON3 are synthesized with the cell library and the memory .v file.

- 4) Functional simulation and timing analysis are performed using the synthesized HC11 and LEON3 codes, the cell library and memory .v file.

- 5) Place & Route is performed using synthesized code, .lib file, and .lef file. Layouts and schematics are generated and timing constraints are satisfied.

- 6) Post layout simulation of HC11 and LEON3 are performed to verify the functionality of the design over all extreme process, voltage and temperature corners.

- Physical verifications (DRC, LVS, antenna check) are performed before sent the HC11 and LEON3 to semiconductor foundry for fabrication.

Fig. 1.2 Standard cell based ASIC design flow [40].

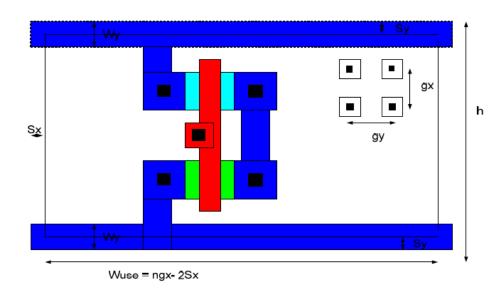

The layout and the abstraction of the cell are required for the standard cell library design. Fig. 1.3 shows the layout format of the standard cell library of Peregrine 0.5um process [49]. The layout horizontal grid and vertical grid sizes are 2.2um; the cell height used is 22um, and 22 um is exactly 10

times the grid size; 2.2um is chosen because it is the minimum distance of two contacts and 22um is used because the Encounter place & route can place the maximum contacts possible within the 22um. The required safety zones are 0.9um on the nlocos side and 0.4 um on the plocos side, the left and right sides also have safety zone of 0.4 um. The safety zones are required to avoid any DRC error when the cells are abutted to each other during the placing process.

Fig. 1.3 The layout format of the standard cell library [49].

#### 1.3 SOI and Bulk Comparison

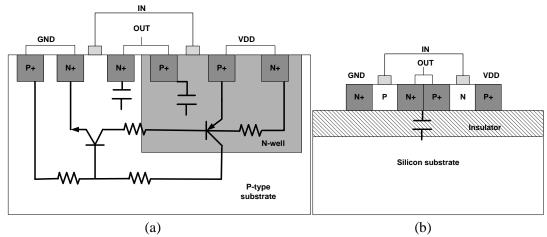

Fig 1.4 shows the cross section of bulk CMOS inverter and SOI CMOS inverter. For bulk CMOS, PMOS or NMOS is fabricated in the well or substrate. Because of the lack of isolation to the substrate, the latch-up happens to the bulk CMOS inverter. However, for the SOI CMOS inverter, the substrate is isolated by the insulator. This insulator layer brings several advantages for SOI CMOS over bulk CMOS: high speed, low power and high device density, low leakage and no latch-up. The Peregrine SOS 0.5um process is partially depleted SOI process which uses Al<sub>2</sub>O<sub>3</sub> as the insulator. The floating body effect in partially depleted SOI is well-known documented [1].

Fig. 1.4 (a). Cross section showing the latch-up path in a bulk CMOS inverter. (b). Cross section of an SOI CMOS inverter. The drain parasitic capacitances are also presented [3].

#### 1.3.1 High Speed, Low Power and High Device Density

As in Fig 1.4, bulk CMOS has a capacitance from drain/source to the P-type substrate while SOI CMOS has a capacitance from drain/source to the silicon substrate. The Al<sub>2</sub>O<sub>3</sub> insulator has relatively lower permittivity and much greater capacitance thickness compared with the bulk capacitance. This results in reduced capacitance, smaller RC delay and smaller dynamic power for modern VLSI design. This is significant in SRAM circuit design, as the column capacitances are significantly reduced resulting in higher speed and lower power design. SOI has the advantage of higher device density as well, due to well elimination. As shown in Fig.1.4, SOI has no N-well or P-well, and no contact is required for the well.

#### 1.3.2 Low Leakage

SOI has less leakage current at elevated temperatures compared with bulk CMOS because the excessive junction leakage current occurs in bulk at elevated temperatures; insulator isolation eliminates this junction leakage current in SOI. As a result, it is very difficult to use conventional bulk CMOS technology at temperatures above 150  $\,^{\circ}$ C [46][47]. The significantly reduced leakage in

SOI results in sufficient  $I_{ON}/I_{OFF}$  ratio and less leakage power for valid digital designs at elevated temperatures [9][47]. These issues will be discussed in greater detail in CHAPTER II and III.

#### 1.3.3 No Latch-Up

Fig. 1.4 shows the latch-up path in bulk which is eliminated in SOI. Latch-up happens in bulk CMOS which creates the thyristor structure [3]. Fig. 1.4(a) shows the formation of a thyristor like PNPN structure with a PNP transistor and a NPN transistor connected back to back which results in latch-up. Once the thyristor is triggered both transistors start to conduct and large amount of current flows through the transistors until the transistors are switched off. SOI CMOS eliminates the latch-up by insulator isolation [Fig. 1.4(b)].

#### 1.3.4 Floating Body Effect

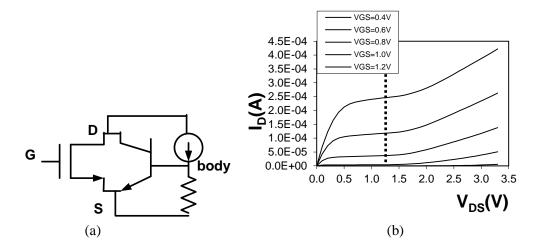

The insulator SOI structure offers several advantages but also brings disadvantage. The floating body results in a parasitic BJT which in turn results in increased  $I_D$ - $V_{DS}$  characteristics currents referred to as the kink effect [43]. In a bulk CMOS device, the base of this BJT is connected to ground through the substrate or the well contact. For the SOI device, the base of the transistor is usually floating referred as the 'floating body effect'. Fig. 1.5(a) shows the parasitic BJT structure at the body of SOI NMOS. The small signal model current is to model the BJT current which results in reduced NMOS effective output resistance. In Fig. 1.5(b), the kink effect is no existent for  $V_{DS}$  less than approximately 1.45V [27]. This late turn-on of BJT is the result of insufficient energetic carriers in the channel which is required to produce other electron-hole pairs or cause impact ionization. The kink effect is not observable until  $V_{DS}$  exceeds approximately 2V for PMOS. This effect is smaller in PMOS devices because of the lower impact ionization of holes [27]. The kink effect can be harmful to SRAM cell stability, sense amp sensing, and digital circuit delay. This issue is fully discussed in CHAPTER IV along with robust design of SRAM cell, sense amp and digital circuits in the presents of transistor kink.

Fig. 1.5 (a) Parasitic BJT inside a PD SOS NMOS transistor [27]. (b)  $I_D$ - $V_{DS}$  characteristics of High  $V_{TH}$  NMOS with width equals 16@3.6 um, length equals 2 um. Measured  $I_D$  at  $V_{DS}$  equals  $0.2V, 0.4V, 0.6V, 0.8V, V_{GS}$  equals  $0 \sim 3.6V$  at 195 °C.

In conclusion, SOI has several advantages over bulk CMOS as in Table 1.1.The disadvantages of floating body effect requires robust design to overcome the issue.

Table 1.1 Comparison of SOI and Bulk CMOS advantages and disadvantages

|                     | SOI CMOS                | Bulk CMOS                    |

|---------------------|-------------------------|------------------------------|

|                     |                         |                              |

| Speed, drain/source | Lower S/D to body       | Higher S/D to body           |

| capacitance         | capacitances and as a   | capacitances                 |

|                     | result increases the    |                              |

|                     | circuit speed           |                              |

| Latch up            | No latch up             | Latch-up problems due to     |

|                     |                         | the parasitic thyristors     |

| Device density      | Higher device density   | Lower device density due to  |

|                     | due to well elimination | well                         |

| Leakage current     | smaller leakage at      | No bulk technology           |

|                     | elevated temperatures   | available for applications   |

|                     | due to insulator        | above 150 ℃ due to large     |

|                     | isolation               | junction leakage             |

| Kink effect         | Kink effect happens due | No kink effect because the   |

|                     | to no body tie          | body tie avoid the parasitic |

|                     |                         | BJT to turn on               |

#### 1.3 Design Methodologies

In this dissertation, the design methodologies are developed for high temperature memories, cell library and the top module (HC11, LEON3, and SRAM design with Encounter support). The methodologies are highly dependent on elevated temperature data and summarized below:

- 1) The Peregrine simulation models are only characterized up to 150  $^{\circ}$ C by the vendor and as a result can be of questionable value at elevated temperatures. Device data is taken to address the issues of elevated temperature behavior in SOS. The measured data is used as an important source to support cell library and memory circuit development, design and simulation. Measured data includes  $I_{ON}$  and  $I_{OFF}$ , threshold, and mobility. With the measured data, the kink effect is observed and its effect is documented.  $I_{ONP}/I_{OFFN}$  is found to be worse than  $I_{ONN}/I_{OFFP}$ .

- 2) The standard cell library is then designed based on the measured data. A CMOS gate performance equation model is developed to determine the cell geometries and ensure circuit robustness to  $I_{ON}/I_{OFF}$  to cell variability, ensuring an adequate noise margin.

- 3) The memory designs are developed with the aid from the measured data to address write and read stability in the context of floating body effect, kink effect, and shrinking  $I_{ON}/I_{OFF}$  currents with temperatures.

- 4) Each top module can be designed with the specific standard cell library and the required memories. The on-chip memories are designed using hand-layout, then instantiated as cells with timing and abstraction files; the top module is then synthesized and placed & routed with the satisfied timing.

#### 1.4 Dissertation Organization

This dissertation describes high temperature memories as part of the design for 275  $^{\circ}$ C HC11 microcontroller and 200  $^{\circ}$ C LEON3 processor [9] using SOS technology. CHAPTER II presents the accurately measured data including  $I_{ON}/I_{OFF}$  ratio, threshold, and mobility. The kink effect is also observed from the  $I_D$  vs.  $V_{DS}$  curve. CHAPTER III presents the standard cell library design and the

memory design. The design issues of the standard cells are: functional design/able to switch, rise and fall time,  $I_{ON}/I_{OFF}$  ratio, variability, and beta-match requirement. The design issues for SOS SRAM and sense amp are:  $I_{ON}/I_{OFF}$ , floating body effect, mid-rail read,  $V_{TH}$  of the SRAM cell, and mobility. The memory device test result is presented in CHAPTER IV along with functionality across temperature corners. The testing analysis found the possible error sources, which can be useful for future SRAM design. CHAPER V discusses the SRAM layout with Encounter support to reduce the SRAM design time. And finally CHAPTER VI concludes this dissertation.

#### **CHAPTER II**

#### ACCURATE DATA FOR CELL LIBRARY AND MEMORY

#### 2.1 Measured ION/IOFF, Threshold and Mobility

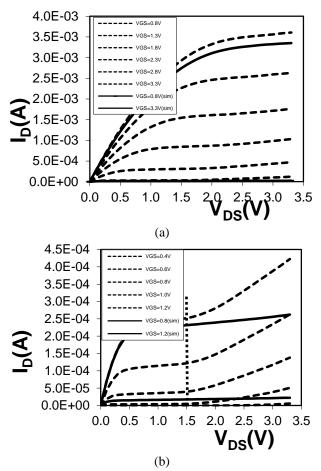

Accurate knowledge of ION/IOFF ratio, threshold (VTH) and mobility of the SOS devices versus temperature is a key to the successful design of the cell libraries and the memories for extreme temperatures. The Peregrine simulation model, characterized for below 150 °C by the vendor, can be of questionable value at elevated temperatures by observing comparison with the measured data [45]. Furthermore, the kink effect is not included in the model as well. Fig. 2.1 shows a plot of the Peregrine model versus the measured data at room temperature and the increased current is well observed from the measured data. Cell library designs for elevated temperatures (200 °C and 275 °C) characterized with the Peregrine model require further consideration to avoid design failures and/or low yield.

The kink effect as observed in Fig. 2.1(b) increases the current compared to the model; this effect happens especially at low  $V_{GS}$ . The kink effect is nonexistent for  $V_{DS}$  less than approximately 1.45V for NMOS. This late turn-on of the BJT is the result of insufficient energetic carriers in the channel and these carriers are required to produce electron-hole pairs resulting from impact ionization [27]. The kink effect occurs around  $V_{DS}$  equals 2V for PMOS. This effect is smaller in PMOS devices because of the lower impact ionization energy of holes [27].

Fig. 2.1 (a) $I_D$  vs  $V_{DS}$  for 20 x 1.4um/1.4um high  $V_{TH}$  NMOS,  $V_{DS}$ =0 to 3.3V,  $V_{GS}$ =0.8V to 3.3V in 6 steps at room temperature. (b)  $I_D$  vs  $V_{DS}$  of the same device at low  $V_{GS}$ ,  $V_{GS}$ =0.4V to 1.2V in 5 steps. Note solid data is simulated and dashed is measured.

$I_{ON}/I_{OFF}$  data is used to develop the cell library sizing rules and verify the Encounter Library Characterization tool rise/fall results with elevated temperature functional designs in mind. These data is equally important for the memory design and is the basis for validating Cadence Spectre simulation of delay, leakage current and power. The measurement equipment used is Keithley 2400 and Cascade Alessi REI-6100 semi-automatic probe station. These data is discussed in detail below.

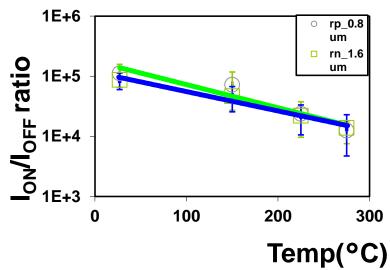

Fig. 2.2 **Error! Reference source not found.** shows the  $I_{ON}/I_{OFF}$  ratio versus temperature for high  $V_{TH}$  PMOS and NMOS, where W equals 20 x 1.4um and L equals 0.8um for PMOS, and W equals 1 x 20um and L equals 1.6um for NMOS. These high  $V_{TH}$  PMOS and NMOS are known

as 'RP' and 'RN' in the Peregrine model.  $I_{ON}$  was measured at  $V_{DS}$  equals 50mV,  $V_{GS}$  equals 3.6V and  $I_{OFF}$  was measured at  $V_{DS}$  equals 3.6V,  $V_{GS}$  equals 0V. The "EXP\_PMOS" and "EXP\_NMOS" lines are an averaged exponential fit to find the  $I_{ON}/I_{OFF}$  ratio for 10 RP and RN, respectively. The error bars are the 1-sigma standard error points. As shown in Fig. 2.2,  $I_{ON}/I_{OFF}$  ratio is degrading with temperatures. The other test results with different geometries are shown in Table 2.1; RP and RN have the lengths of 0.6um and 0.7um and 1.1um, 1.3um and 1.4um, respectively. Each data point is the average of 10 different die where each transistor is composed of 20 fingers each 1.4um in width except that RN with 1.6um length has 20um width. Typically  $I_{ON}$  and  $I_{OFF}$  can be calculated in Equation (2.1) and (2.2) [54], respectively.

$$I_D = KP \cdot \frac{W}{L} \cdot \left[ \left( V_{GS} - V_{TH} \right) \cdot V_{DS} - \frac{V_{DS}^2}{2} \right]$$

(2.1)

$$I_{D} = I_{D0} \cdot \exp\left(\frac{V_{G} - n \cdot V_{S}}{n \cdot U_{T}}\right) \left[1 - \exp\left(-\frac{V_{D} - V_{S}}{U_{T}}\right)\right]$$

$$I_{D0} = I_{S} \cdot 2 \cdot n \cdot KP \cdot \frac{W}{L} \cdot U_{T}^{2} \cdot \exp\left(\frac{-V_{TH0}}{n \cdot U_{T}}\right)$$

(2.2)

where  $KP = \mu C_{ox}$ ,  $V_{GS}$ ,  $V_{TH}$ ,  $V_{G}$ ,  $V_{D}$ ,  $V_{S}$ ,  $I_{S}$ , n take on their usual values. W is the width of the transistor. L is the length of the transistor.  $U_{T}$  is the thermal voltage.  $V_{TH0}$  is threshold voltage for zero substrate bias.  $\mu$  is the mobility.  $C_{ox}$  is the oxide capacitance.

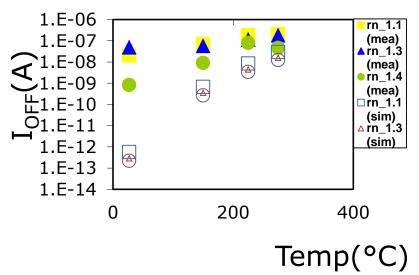

Fig. 2.3 shows the average  $I_{OFF}$  current from the measurement and the Peregrine model using the same test condition as Fig. 2.2; the measured devices are: RN with L equal 1.1um, 1.3um and 1.4um; all widths are 20 x 1.4um and the plot uses 1.4um width for convenience;  $I_{OFF}$  as observed is increased with temperature; the model data follows Equation (2.2) while the measured data has larger value than the model data because it includes both Equation (2.2) and the kink current. It is also interesting to observe from Fig. 2.1, the measured  $I_{ON}$  is consistent with the model at  $V_{DS}$  equals 50mV,  $V_{GS}$  equals 3.6V.

Fig. 2.2  $I_{ON}/I_{OFF}$  ratio over (room to 275 °C) for RP W equals 20 x 1.4um, L equals 0.8um, and RN W equals 20 x 1.4um, L equals 1.6um. Measured  $I_{ON}$  at  $V_{DS}$  equals 50mV,  $V_{GS}$  equals 3.6Vand  $I_{OFF}$  at  $V_{DS}$  equals 3.6V,  $V_{GS}$  equals 0V.

$Table~2.1 \\ I_{ON}/~I_{OFF}~ratio~and~the~variations~of~I_{ON}/~I_{OFF}~ratio$

| Device (W/L)       | $I_{\rm ON}/I_{\rm OFF}$ (27 °C) | 1σ<br>I <sub>ON</sub> /I <sub>OFF</sub><br>(27°C) | $I_{\rm ON}/I_{\rm OFF}$ (150°C) | 1σ<br>I <sub>ON</sub> /I <sub>OFF</sub><br>(150°C) | $I_{\rm ON}/I_{\rm OFF}$ (225 °C) | $1\sigma I_{\rm ON}/I_{\rm OFF}$ (225 °C) | I <sub>ON</sub> /I <sub>OFF</sub> (275 °C) | 1σ<br>I <sub>ON</sub> /I <sub>OFF</sub><br>(275 °C) |

|--------------------|----------------------------------|---------------------------------------------------|----------------------------------|----------------------------------------------------|-----------------------------------|-------------------------------------------|--------------------------------------------|-----------------------------------------------------|

| RP 20 x 1.4/0.6 um | 1.26E5                           | 4.06E4                                            | 2.08E4                           | 3.13E4                                             | 3.33E4                            | 1.18E4                                    | 4.52E4                                     | 1.37E4                                              |

| RP 20 x 1.4/0.7 um | 2.04E5                           | 1.02E4                                            | 1.03E5                           | 2.57E4                                             | 2.72E4                            | 1.31E4                                    | 1.34E4                                     | 4.54E3                                              |

| RP 20 x 1.4/0.8 um | 1.11E5                           | 4.60E4                                            | 7.04E4                           | 4.51E4                                             | 2.36E4                            | 1.40E4                                    | 0.26E4                                     | 4.89E3                                              |

| RN 20 x 1.4/1.1 um | 353                              | 262                                               | 67.5                             | 49.3                                               | 35.5                              | 14.2                                      | 29.9                                       | 9.87                                                |

| RN 20 x 1.4/1.3 um | 138                              | 88.7                                              | 93.1                             | 64.1                                               | 48.1                              | 23.6                                      | 30.1                                       | 12.5                                                |

| RN 20 x 1.4/1.4 um | 8.49E3                           | 5.47E3                                            | 401                              | 319                                                | 68.9                              | 30.7                                      | 100                                        | 55.3                                                |

| RN 1 x 20/1.6 um   | 8.66E4                           | 2.30E4                                            | 4.64E4                           | 1.83E4                                             | 2.19E4                            | 1.14E4                                    | 1.38E4                                     | 9.16E3                                              |

Fig 2.3  $I_{OFF}$  over (room to 275 °C) for NMOS L equal 1.1um, 1.3um and 1.4um. All widths are 1.4um.Measured and simulated at  $V_{GS}$  equal 0V,  $V_{DS}$  equal 3.6V.

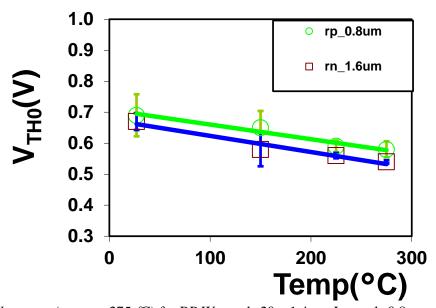

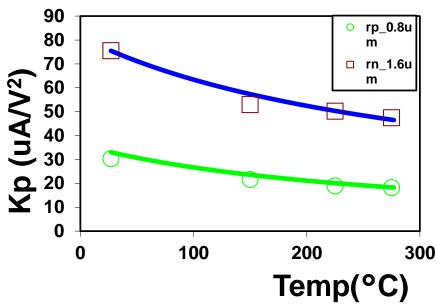

$V_{TH0}$  versus temperature is plotted in Fig. 2.4, where W equals  $20 \times 1.4$ um and L equals 0.8um for RP, and W equals  $1 \times 20$ um and L equals 1.6um for RN. The threshold voltage temperature coefficients are found to be 0.52mV/  $\mathbb C$  and 0.43mV/  $\mathbb C$  for RN and RP, respectively with  $V_{SB}$  equals zero.  $V_{TH0}$  was measured at  $V_{DS}$  equals 50mV and  $V_{GS}$  swept from 0 to 3.3V in 50mV steps [20]. The error bar indicates the 1-sigma  $V_{TH0}$  error. KP versus temperature for both RN and RP is presented in Fig. 2.5, where W equals  $20 \times 1.4$ um and L equals 0.8um for RP, and W equals  $1 \times 20$ um and L equals 1.6um for RN. KP is degrading at an exponential rate of -0.80 and -0.98 for both RN and RP, respectively. The "EXP\_NMOS" and "EXP\_PMOS" lines again are an averaged exponential fit to find the KP values for RN and RP, respectively. Equation (2.1) is used to calculate KP [31] [32]. The mobility variation is ignored in Equation due to the dominancy of  $V_{TH}$  variation [4] [30]. The other test results are shown in Table 2.2 and 2.3.

The measured  $I_{OFF}$  is more accurate as it includes both the kink effect and  $I_{OFF}$  calculation in Equation (2.2) while the vendor supplied model does not include the kink current. Moreover, the measured  $I_{ON}$  and  $I_{OFF}$  variations observed in this dissertation are larger than the  $I_{ON}$  and  $I_{OFF}$  variations projected from previously determined Pelgrom coefficients [8] as well as the vendor

model; the measured  $V_{TH}$  and KP variations are also different than the previous determined for the following reasons:

- Current variations due to kink effect were not included in the previous measurement work

[8].

- 2) Our smaller sample size of 10 leads to less accurate estimates.

- 3) Die to die variations were not considered and devices were laid out for analog matching in the previous work [8]. No common centroid geometries or dummies were included for this measurement setup. The Pelgrom coefficient previously found in [8] considered only the analog layout for improved circuit matching with the expectation that V<sub>DS</sub> would be less than 1V.

Fig. 2.4  $V_{TH0}$  over (room to 275 °C) for RP W equals 20 x 1.4um, L equals 0.8um, and RN W equals 20 x 1.4um, L equals 1.6um. Calculated at  $V_{DS}$  equals 50mV,  $V_{GS}$  equals 0 ~3.3V at 50mV each step. (Only the absolute value of  $V_{THP}$  is used in this dissertation.)

Fig. 2.5 KP over (room to 275  $\,^\circ$ C) for RP W equals 20 x 1.4um, L equals 0.8um, and RN W equals 20um x 1.4um, L equals 1.6um. Measured at  $V_{GS}$  equals 1V,  $V_{DS}$  equals 50mV.

$\label{eq:total variation} Table~2.2 \\ V_{\text{TH}}~\text{and the variations of}~V_{\text{TH}}~\text{at different temperatures}$

| Device(W/L)      | $V_{TH}$ | $1\sigma$ - $V_{TH}$ |

|------------------|----------|----------------------|----------|----------------------|----------|----------------------|----------|----------------------|

|                  | (27 ℃)   | (27 ℃)               | (150 ℃)  | (150 ℃)              | (225 ℃)  | (225 ℃)              | (275 ℃)  | (25 ℃)               |

|                  | (V)      | (V)                  | (V)      | (V)                  | (V)      | (V)                  | (V)      | (V)                  |

| RP 20@1.4/0.6 um | 0.71     | 0.12                 | 0.64     | 0.11                 | 0.60     | 0.04                 | 0.59     | 0.05                 |

| RP 20@1.4/0.7um  | 0.70     | 0.23                 | 0.62     | 0.14                 | 0.59     | 0.22                 | 0.58     | 0.22                 |

| RP 20@1.4/0.8 um | 0.69     | 0.21                 | 0.65     | 0.05                 | 0.59     | 0.02                 | 0.58     | 0.03                 |

| RN 20@1.4/1.1 um | 0.58     | 0.16                 | 0.55     | 0.18                 | 0.49     | 0.02                 | 0.47     | 0.01                 |

| RN 20@1.4/1.3 um | 0.56     | 0.16                 | 0.51     | 0.15                 | 0.48     | 0.13                 | 0.46     | 0.01                 |

| RN 20@1.4/1.4 um | 0.60     | 0.09                 | 0.55     | 0.26                 | 0.5      | 0.02                 | 0.47     | 0.01                 |

| RN 1@20/1.6 um   | 0.67     | 0.03                 | 0.58     | 0.06                 | 0.56     | 0.01                 | 0.54     | 0.01                 |

Table 2.3 KP at different temperatures

| Device(W/L)      | KP            | KP            | KP            | KP            |

|------------------|---------------|---------------|---------------|---------------|

|                  | (27 ℃)        | (150 ℃)       | (225 ℃)       | (275 ℃)       |

|                  | $(\mu A/V^2)$ | $(\mu A/V^2)$ | $(\mu A/V^2)$ | $(\mu A/V^2)$ |

| RP 20@1.4/0.6 um | 34.5          | 22.2          | 21.5          | 21.3          |

| RP 20@1 4/0.7 um | 33.5          | 21.1          | 17.2          | 15.4          |

| RP 20@1.4/0.8 um | 30.3          | 21.6          | 18.9          | 18.1          |

| RN 20@1.4/1.1 um | 53.1          | 46.8          | 42.0          | 39.9          |

| RN 20@1.4/1.3 um | 58.6          | 43.3          | 40.6          | 39.2          |

| RN 20@1.4/1.4 um | 63.8          | 39.4          | 44.6          | 37.0          |

| RN 1@20/1.6 um   | 75.5          | 52.9          | 50.2          | 47.4          |

#### 2.2 Summery

The measured  $I_{ON}$  and  $I_{OFF}$ , threshold, and mobility are used as the basis for cell library and memory designs. With these data, the kink effect is noted as being significant;  $I_{ONP}/I_{OFFN}$  (PMOS  $I_{ON}$  NMOS  $I_{OFF}$  ratio) is found to be much worse than  $I_{ONN}/I_{OFFP}$ ; measured  $I_{ON}$  is found to be consistent with the Peregrine model at 200 °C while the measured  $I_{OFF}$  is found to be greater than the model due to the kink effect. (200 °C is the LEON3 temperature corner). The worst case temperature and process variations of  $I_{ON}$  and  $I_{OFF}$  for single P and N devices for lengths of potential interest are summarized in Table 2.4. The worst case  $I_{ON}$  is at lowest  $I_{ON}$  and the worst case  $I_{OFF}$  is at largest  $I_{OFF}$  [34], or low VDD, slow process, and highest temperature. From the measured data,  $I_{ON}$  decreases with temperature and  $I_{OFF}$  increases with temperature. Frequently 2-3 sigma is defined as the process corner [25][42]. So Table 2.4 used  $\mu I_{ON}$  -3 $\sigma I_{ON}$  and  $\mu I_{OFF}$  + 3 $\sigma I_{OFF}$  as the process corner.

As shown in Table 2.4, the "minimum" geometry inverter '1X INV' and 3-input NOR 'NOR3'  $I_{ON}/I_{OFF}$  ratios in Table 2.4 show L greater than or equal 1.6um is adequate for designing with the NMOS in conjunction with an L equal 0.8um PMOS. The choice of PMOS L equals 0.8um is to maximize the noise margin and will be discussed in CHAPTER III. Other NMOS geometries

have insufficient  $I_{ON}/I_{OFF}$  which can result in slow or fail digital logic. The similar worst case corners are summarized in Table 2.5 for the HC11 at 275  $\,^{\circ}$ C temperature corner. The detailed implementation for logic gates and memories are discussed in CHAPTER III and IV.

$\label{eq:total_condition} Table~2.4$   $I_{ON}~\text{and}~I_{OFF}~\text{and}~\text{the variations}~\text{of}~I_{ON}~\text{and}~I_{OFF}~\text{at}~200~~\text{°C}$

| Device(W/L)   | $\mu I_{OFF}$ | 1σ-I <sub>OFF</sub> | I <sub>OFF</sub><br>Worst Case             | $\mu I_{ON}$ | $1\sigma$ - $I_{ON}$ | I <sub>ON</sub><br>Worst Case            | 1X INV                                              | NOR3                                                |

|---------------|---------------|---------------------|--------------------------------------------|--------------|----------------------|------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|

|               |               |                     | μI <sub>OFF</sub> +<br>3σ-I <sub>OFF</sub> |              |                      | μI <sub>ON</sub> -<br>3σ-I <sub>ON</sub> | I <sub>ON_RP_0.8um</sub> /I <sub>OFF</sub><br>ratio | I <sub>ON_RP_0.8um</sub> /I <sub>OFF</sub><br>ratio |

|               | (nA)          | (nA)                | (nA)                                       | (uA)         | (uA)                 | (uA)                                     |                                                     |                                                     |

| RP 1.4/0.6 um | 0.174         | 0.380               | 1.31                                       | 5.81         | 0.986                | 2.85                                     |                                                     |                                                     |

| RP 1.4/0.7 um | 0.152         | 0.401               | 1.36                                       | 4.85         | 1.14                 | 1.43                                     |                                                     |                                                     |

| RP 1.4/0.8 um | 0.184         | 0.113               | 0.523                                      | 4.35         | 0.628                | 2.47                                     |                                                     |                                                     |

| RN 1.4/1.1 um | 158           | 338                 | 1170                                       | 6.64         | 1.15                 | 2.94                                     | 2.11                                                | 1.67                                                |

| RN 1.4/1.3 um | 220           | 366                 | 1210                                       | 5.84         | 1.44                 | 1.52                                     | 2.04                                                | 1.66                                                |

| RN 1.4/1.4 um | 78.5          | 255                 | 843                                        | 5.41         | 1.07                 | 2.20                                     | 2.93                                                | 1.97                                                |

| RN 1.4/1.6 um | 0.176         | 0.830               | 2.67                                       | 3.87         | 0.264                | 3.08                                     | 925                                                 | 769                                                 |

$\label{eq:total condition} Table~2.5$   $I_{ON}~and~I_{OFF}~and~the~variations~of~I_{ON}~and~I_{OFF}~at~275~~ {\mbox{$^{\circ}$}} {\mbox{$^{\circ}$}}$

| Device(W/L)   | μI <sub>OFF</sub> | lσ-I <sub>OFF</sub> | $I_{OFF} \ worst$ case $\mu I_{OFF} + 3\sigma - I_{OFF}$ | μI <sub>ON</sub> | 1σ-I <sub>ON</sub> | $I_{ON} \ worst \ case \\ \mu I_{ON} - \\ 3\sigma - I_{ON}$ | 1X INV<br>I <sub>ON_RP_0.8um</sub> /I <sub>OFF</sub><br>ratio | NOR3<br>I <sub>ON_RP_0.8um</sub> /<br>I <sub>OFF</sub> ratio |

|---------------|-------------------|---------------------|----------------------------------------------------------|------------------|--------------------|-------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------|

|               | (nA)              | (nA)                | (nA)                                                     | (uA)             | (uA)               | (uA)                                                        |                                                               |                                                              |

| RP 1.4/0.6 um | 0.126             | 0.178               | 0.660                                                    | 5.84             | 0.648              | 3.90                                                        |                                                               |                                                              |

| RP 1.4/0.7 um | 0.299             | 0.489               | 1.77                                                     | 4.80             | 0.453              | 3.44                                                        |                                                               |                                                              |

| RP 1.4/0.8 um | 0.328             | 0.839               | 2.85                                                     | 4.08             | 0.584              | 2.33                                                        |                                                               |                                                              |

| RN 1.4/1.1 um | 205               | 409                 | 1430                                                     | 6.15             | 0.853              | 3.59                                                        | 1.63                                                          | 1.28                                                         |

| RN 1.4/1.3 um | 179               | 543                 | 1810                                                     | 5.40             | 0.477              | 3.97                                                        | 1.29                                                          | 1.04                                                         |

| RN 1.4/1.4 um | 46.1              | 201                 | 649                                                      | 4.36             | 0.758              | 2.09                                                        | 3.59                                                          | 2.96                                                         |

| RN 1.4/1.6 um | 0.289             | 2.53                | 7.79                                                     | 3.98             | 0.171              | 3.47                                                        | 1020                                                          | 809                                                          |

#### **CHAPTER III**

#### CELL LIBRARY AND MEMORY DESIGN

#### 3.1 Introduction

CHAPTER II discusses the accurate data for the cell library and memory design. The measured data is used to develop the cell library and verify the Encounter Library Characterization tool rise/fall results, and cell size with functional high temperature designs in mind. These data is important for the memory design for identical reasons and are the basis for calculating delay, leakage current and power. This CHAPTER discusses the cell library design and the memory design in details.

#### 3.2 Cell Library Design

The existence of high temperature cell library allows for fast design of the complex digital devices. The top modules (HC11, LEON3 and SRAM layout with Encounter support) are designed based on the cell libraries, and later placed & routed with the required timing. The design procedures of a standard cell library includes creating cells, extracting timing for each cell, and abstracting the cell for place and route; these are discussed in CHAPTER I. The vendor supplied model is not accuracy on  $I_{OFF}$ , which can cause characterization errors by using Cadence Characterization tool if the cells are not carefully designed. Here a methodology is developed to design the cells, which makes the characterization valid for all the cells. Sufficient  $I_{ON}/I_{OFF}$  ratio is important for cell functionality, this ratio is affected by the cell variability as well; with sufficient  $I_{ON}/I_{OFF}$  ratio assured from Table 2.4 and 2.5, switching of a cell under the worst case corner is known, and rise/fall times of a cell can also be assured resulting in robust

designs. Furthermore, to optimize the noise margin of a cell, the geometries need to ensure the switching threshold at VDD/2 (beta-match requirement) [18]. Equation (3.1) and (3.2) are developed to ensure sufficient  $I_{ON}/I_{OFF}$  ratio while maximizing the noise margin [18] across process:

$$\mu N \cdot \left(\frac{W_{N}}{L_{N}}\right)_{INV} = \mu P \cdot \left(\frac{W_{P}}{L_{P}}\right)_{INV}$$

$$\mu N \cdot \left(\frac{W_{N}}{L_{N}}\right)_{INV} = \mu P \cdot \left(\frac{W_{P}}{L_{P}}\right)_{INV} \cdot \left(\frac{S_{NOR}}{m_{NOR}}\right)$$

$$\mu N \cdot \left(\frac{W_{N}}{L_{N}}\right)_{INV} \cdot \left(\frac{S_{NAND}}{m_{NAND}}\right) = \mu P \cdot \left(\frac{W_{P}}{L_{P}}\right)_{INV}$$

(3.1)

$$k_{G}(INV) = \frac{\mu I_{ON} - 3 \cdot \sigma I_{ON}}{\mu I_{OFF} + 3 \cdot \sigma I_{OFF}}$$

$$k_{G}(NOR) = \frac{\mu I_{ON} - \frac{3 \cdot \sigma I_{ON}}{\sqrt{S_{NOR} \cdot m}}}{m \cdot (\mu I_{OFF} + \frac{3 \cdot \sigma I_{OFF}}{\sqrt{m}})}$$

$$k_{G}(NAND) = \frac{\mu I_{ON} - 3 \cdot \sigma I_{ON}}{S_{NAND} \cdot \mu I_{OFF} + \sqrt{S_{NAND}} \cdot 3 \cdot \sigma I_{OFF}}$$

(3.2)

where " $m_{NOR}$ " and " $m_{NAND}$ " are the numbers of the PMOS/NMOS inputs. " $\mu$ P" and " $\mu$ N" are the mobility of PMOS and NMOS, respectively. " $W_P/L_P$ " and " $W_N/L_N$ " are the 1X INV geometries for the designed PMOS and NMOS, respectively. " $S_{NOR}$ " and " $S_{NAND}$ " are the scaling factors for NOR and NAND, respectively. Equation (3.1) is developed based on the ratio r equals 1 when  $V_{TP}$  and  $V_{TN}$  are equal [18]. " $\mu$ I $_{ON}$ " and " $\sigma$ -I $_{ON}$ " are the mean and variation of single transistor I $_{ON}$ , respectively. " $\mu$ I $_{OFF}$ " and " $\sigma$ -I $_{OFF}$ " are the mean and variation of single transistor I $_{OFF}$ , respectively. " $k_G(INV)$ ", " $k_G(NOR)$ ", and " $k_G(NAND)$ " are the worst case I $_{ON}/I_{OFF}$  ratios for INV, NOR and NAND gates, respectively and evaluated by substituting  $S_{NOR}$  and  $S_{NAND}$  from Equation (3.2).  $k_G(INV)$ ,  $k_G(NOR)$  and  $k_G(NAND)$  should be  $\geq$  100 for the delay error to be independent of the leakage current. The modeled I $_{ON}$  is consistent with the data and the modeled I $_{OFF}$  is smaller than the measured I $_{OFF}$ , as observed from CHAPTER II. As the result, characterizations via Cadence timing tools can be considered valid. With Table 2.4 and 2.5, Equation (3.1) and (3.2),  $W_P/L_P$  and

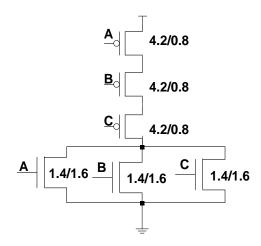

$W_N/L_N$  are such that the 1X INV which ensure  $k_G > 500$  and maximize the noise margin. As in Table 2.4 and 2.5, only NMOS length of 1.6um results in  $k_G > 500$  while shorter measured geometries have insufficient  $k_G$ . Note that Table 2.4 and 2.5 are the worst case  $I_{ON}$  and  $I_{OFF}$  for LEON3 (200 °C) and HC11 (275 °C) designs, respectively. Acceptable  $W_P/L_P$  and  $W_N/L_N$  were found to be 1.4/0.8um and 1.4/1.6um, respectively. Then NOR or NAND geometries can be found from Equation (3.1) and (3.2). Here LEON3 NOR3 is used as an example;  $S_{NOR}$  of NOR3 is found to be 3 using Equation (3.1) and (3.2); and as a result  $k_G > 500$ . NOR3 has the smallest  $k_G$  of all the cells as a result of the weak pull-up [35].  $k_G$  of NOR3 is smaller than the 1X INV, note Table 2.4; also a 2-input NOR has a larger  $k_G$  than NOR3 using Table 2.4 data and Equation (3.2). The designed NOR3 geometries are shown in Fig. 3.1. It should be noted that from Table 2.4 NMOS 1.4um/1.5um may be valid. However, these test cells were not included on the mask and for this reason are not considered.

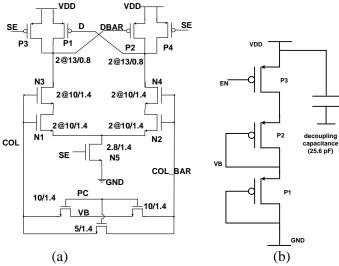

Fig. 3.1 NOR3 schematic with geometries used.

With  $W_P/L_P$  and  $W_N/L_N$ , all the cell geometries in the standard cell library are determined by solving  $S_{NOR}$  or  $S_{NAND}$  from Equation (3.1) as in Fig. 3.1. The worst case  $I_{ON}/I_{OFF}$  ratios for all cells > 500 are assured using Equation (3.2). All cells are functional designs which rise/fall times are accurately evaluated after post extraction for LEON3 and HC11 designs, respectively. Furthermore, the cell geometries maximize the noise margin. By example, a 3-input NAND uses

the following geometries where PMOS and NMOS sizes equal 1.4/0.8um and 4.2/1.6um, respectively. All the cells designed are listed in Appendix A.

#### 3.3 Memory Design

In this section, memory designs are discussed in detail. The memories designed for HC11 and LEON3 include: a 4K on-chip SRAM, 512byte on-chip ROM, 4K SPI-SRAM, 2K SPI-ROM, 2K x16 off-chip SRAM, 128 x 32 cache, and 32 x 32 cache. The on-chip 4K SRAM is used to store the data and instructions executed by the HC11. The on-chip 512byte ROM is able to perform a sequence of the HC11 peripheral and register self-test process where the ROM code controls the bootstrap process and is able to boot from either SCI or SPI interface. The 4K SPI-SRAM is used for off-chip storage of data and software routines to be uploaded and executed by the HC11. The 2K SPI-ROM is used to store a small monitor program, 68MON which is a monitor/debugger program for the HC11. Both on-chip and off-chip ROMs are customer mask designs. The masking operation was completed separately from the other structures and programmed using a combination of Matlab and Cadence SKILL language. The off-chip 2K x 16 SRAMs are used for program and data storage, and they communicate with the LEON3 using a memory controller bridge. The 128 x 32 caches are used in LEON3 for high speed data and instruction storage. The 32x32 cache is used for the register file in the LEON3.

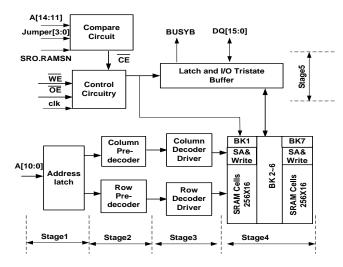

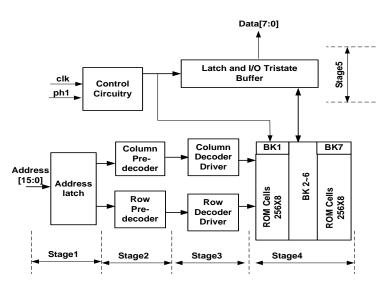

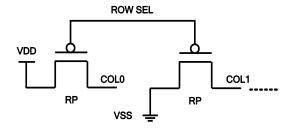

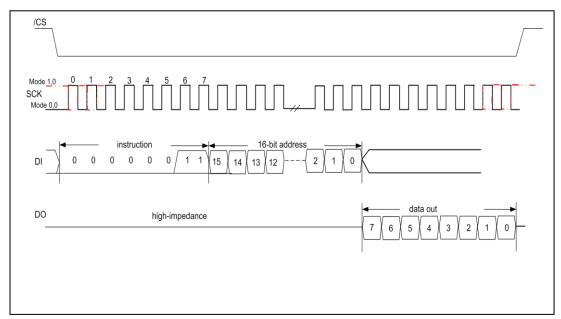

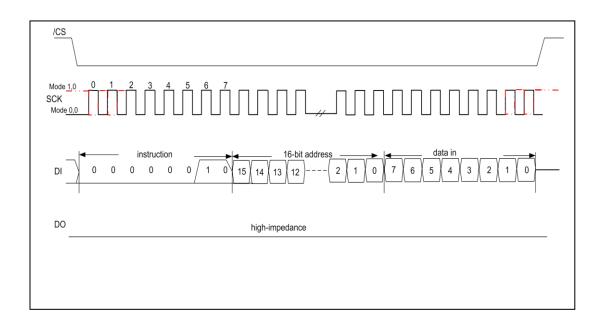

#### 3.3.1 The Architecture of the Memories

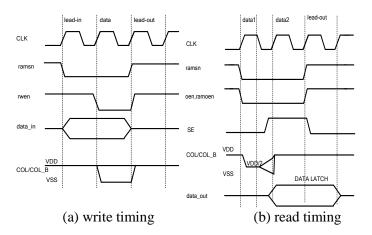

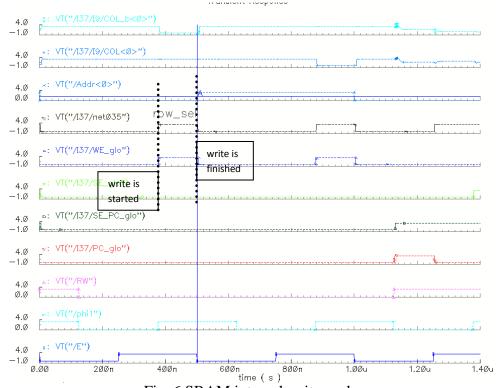

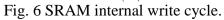

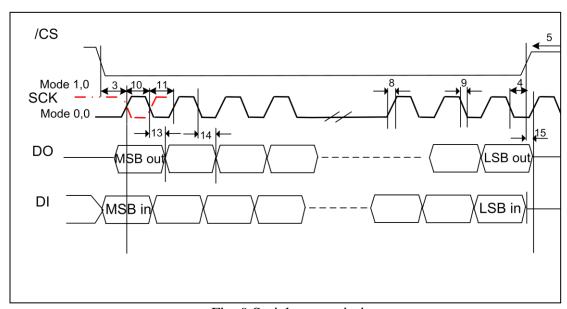

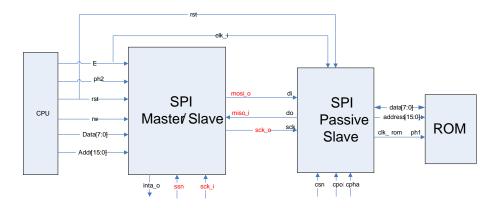

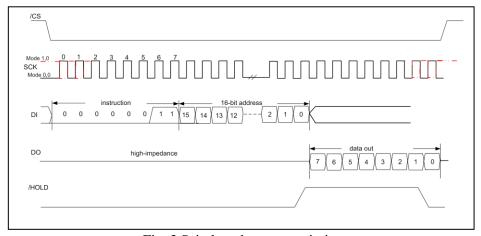

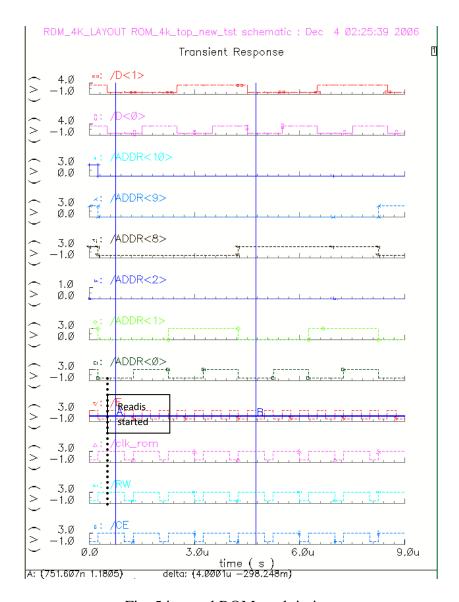

The off-chip 2K x 16 SRAM, Fig. 3.2, is constructed using a compare circuit, a control circuitry, pre-decoders, decoder drivers, latches and I/O buffers, and 8 SRAM banks. Each SRAM bank includes: RAM cells, sense amps, write circuitry all arrayed in a 256 x 16 arrangement. The SRAM is designed for low power high temperature applications up to 275 °C operating at 18MHz for LEON3. LEON3 standard write and read are shown in Fig. 3.3(a) and (b), respectively [22]. Write access to SRAM has a lead-in, data and lead-out cycle, while a write starts at the falling

edge of "rwen", as in Fig. 3.3(a). A read access to SRAM consists of two data cycles and 1 leadout cycle. Read data is latched on the rising edge of the clock on the lead-out cycle.

Fig. 3.2 The 2K x16 SRAM block diagram for LEON3.

Fig. 3.3 LEON3 write and read timing.

An identical architecture is used for the other memories. The SPI 4K-SRAM for HC11 has the same architecture as the LEON SRAM, and it is specified in Appendix B. The difference being on-chip cache has no sense amp, and no complex control circuitry required as results of 8T cell usage. For the ROM, write circuitry is removed and no sense amp is required; the 2K SPI-ROM is specified in Appendix C. In this CHAPTER, 2K x 16 SRAM for 200 °C LEON3 is discussed in

detail including: critical delay path, SRAM design issues, 6T PMOS SRAM cell design and sense amp design.

#### 3.3.2 Critical Delay Path

As in Fig. 3.2, read access time for the SRAM is limited by the delay times from five stages; address latch(stage 1), row pre-decoder(stage 2), row decoder driver(stage 3), SRAM cell and sense amp(stage 4), and latch and I/O tri-state buffer(stage 5). The latch delays of stage 1 and stage 5 are calculated as in Equation (3.3) [24]. A predecoding technique [14] is used in pre-decoder providing an efficient mechanism to trade off speed and power. Pre-decoder delay is calculated from Equation (3.4) [26]:

$$\tau_{rise\_o} = \tau_{rise}(NOR2) + \tau_{fall}(NOR2)$$

(3.3)

$$\tau_o = 2.72 \cdot \tau_i \cdot n \tag{3.4}$$

where  $\tau_{rise\_o}$  is the output rise time of SR-latch.  $\tau_{rise}(NOR2)$  and  $\tau_{fall}(NOR2)$  are the rise time and fall time of the 2-input NOR gate, respectively.  $\tau_o$  is the output delay. n is the number of stages. The logic-level time constant is  $\tau_i = C_i/g$ .  $C_i$  is the logic-level capacitance. g is the logic-level conductance.

Row decoder buffer and column decoder buffer delays are also calculated from Equation (3.4). In the 2K-SRAM implementation, the row pre-decoder has the greater delay. The stage 4 delay is discussed in Section 3.4.3 and all other stages can be designed for optimal delays equivalent to an optimal buffer design [51][52].

#### 3.3.3 General SRAM Design Issues

The design issues for SOS SRAM and sense amp are:  $I_{ON}/I_{OFF}$ , floating body effect, mid-rail read,  $V_{TH}$  of the SRAM cell, and mobility. As discussed in CHAPTER II, the worst case  $I_{ON}$  and  $I_{OFF}$

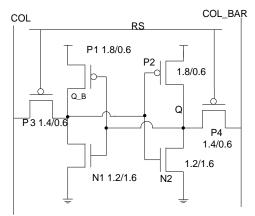

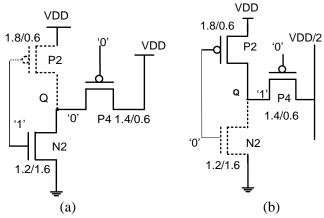

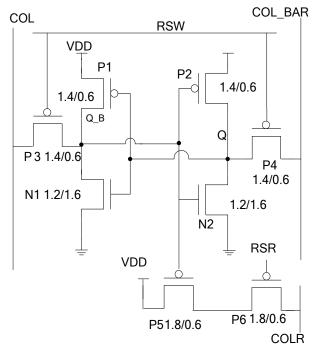

for a single device are at 200 °C. For the SRAM columns, the worst case leakage is defined by the leakage current when "reading a 1" from polarized cells of all 0's or 255 leakage paths at 200 °C.  $I_{ON} - 255I_{OFF}$  needs to be sufficient large to assure a valid read with an acceptable delay. Also I<sub>ONP</sub>/I<sub>OFFN</sub> is required to be sufficient to assure read stability. The floating body effect can affect SRAM cell write stability, read stability, and total SRAM delay if the SRAM cell and sense amp are not properly addressed. PMOS pass gates are used to eliminate/minimize the kink effect resulting from the floating body because PMOS kink is less than NMOS kink and occurs at a higher voltage, as discussed in CHAPTER II. SRAM columns are pulled to VDD when not in use and read or sensed at mid-rail. This has the effect of biasing the floating PMOS pass gate body to maximize V<sub>TH</sub>. A stacked NMOS structure is used for the sense amp to eliminate the kink effect [8]. The worst case  $V_{TH}$  occurs at 200 °C due to the reduced  $V_{TH}$  effect on SRAM read stability [29]; the V<sub>TH</sub> decreases with increasing temperature, note Fig. 2.4. The detailed calculation of SRAM V<sub>TH</sub> is required to assure reliable SRAM cell write and read. The mobility is used for calculation of write and read stability; however, mobility variation is ignored, note CHAPTER II. In summary, SRAM design methodologies developed for kinked SOS CMOS are: 1) use PMOS pass gates, 2) hold SRAM columns at VDD when not in use, 3) apply a mid-rail read, and 4) use stacked NMOS for sense amp. These are addressed in Section 3.3.4 in detail.

#### 3.3.4 PMOS SRAM Cell Design