# POWER MODELING OF CMOS DIGITAL CIRCUITS WITH A PIECEWISE LINEAR MODEL

## By

## CHENG CHIH LIU

Bachelor of Science Pittsburg State University Pittsburg, Kansas 1999

Master of Science Oklahoma State University Stillwater, Oklahoma 2001

Submitted to the Faculty of the

Graduate College of the

Oklahoma State University

in partial fulfillment of

the requirements for

the Degree of

DOCTOR OF PHILOSOPHY

May, 2007

# POWER MODELING OF CMOS DIGITAL CIRCUITS WITH A PIECEWISE LINEAR MODEL

Dissertation Approved:

| Dr. Louis G. Johnson         |

|------------------------------|

| Dissertation Adviser         |

| Dr. R. G. Ramakumar          |

| Dr. Yumin Zhang              |

| Dr. H.K. Dai                 |

| Dr. A. Gordon Emslie         |

| Dean of the Graduate College |

#### **ACKNOWLEDGMENTS**

I would like to express my gratitude to Dr. Louis G. Johnson for his five-year guidance and supports for this dissertation. Without his abundant experiences in the area of CMOS integrated circuits, I could not possibly discover this research topic and the theory behind it. Moreover, I am appreciative of his many helpful advices from design to fabrication of a working prototype of analog integrated circuit for neural recoding application.

I also would like thank Dr. R.G. Ramakumar, Dr. Yumin Zhang, and Dr. H.K. Dai for their busy time and valuable feedback with their expertise while serving as members in my committee. Their suggestions and ideas helped me complete this dissertation.

A special appreciation goes to Jian Chang, now in the Texas Instruments, in my research group for verifying the piecewise linear delay model. I am also thankful to all the members in our digital VLSI research group, and to Sameer, for discussing many questions in an energy conserving MOSFET model.

Last but not least; I appreciate my Dad, Mom, brother, and sister for their supports and encouragements. Without their support, I would not be motivated to pursue a doctoral degree. Especially, I am indebted to my wife, Chin-Huey, for her unconditional love and supports throughout my school years, and also my children, John and Amy, being good companies during my studies.

# TABLE OF CONTENTS

| CHAPTER                                                                       | Page |

|-------------------------------------------------------------------------------|------|

| 1. INTRODUCTION                                                               | 1    |

| 1.0 Purpose of the study                                                      | 1    |

| 1.1 Significance of the study                                                 |      |

| 1.2 Limitation of the proposed model                                          | 3    |

| 1.3 Introduction to the CMOS logic families.                                  | 3    |

| 1.4 Organization                                                              | 5    |

| 2. CONVENTIONAL TRANSISTOR MODELS FOR POWER EVALUATION                        | 6    |

| 2.0 Definition: Energy or Power                                               | 6    |

| 2.1 Sources of CMOS Power dissipation                                         | 7    |

| 2.1.1 Off-state leakage power of the transistor                               |      |

| 2.1.2 Switching transient power in CMOS transistors                           |      |

| 2.1.3 Glitch power dissipation in CMOS transistors                            |      |

| 2.2 Summary                                                                   |      |

| 3. A PIECEWISE LINEAR TRANSISTOR MODEL                                        | 17   |

| 3.0 Background                                                                | 17   |

| 3.1 Evaluation of average power dissipation with the piecewise linear model.  | 18   |

| 3.1.1 Piecewise linear current model                                          |      |

| 3.1.2 Channel storage charge model                                            | 24   |

| 3.2 Ramp input approximation                                                  |      |

| 3.3 Approximate solution for circuit voltage                                  |      |

| 3.3.1 Resistive connected region                                              |      |

| 3.3.2 Approximate solution for circuit voltage with nonsingular G matrix.     |      |

| 3.4 Average turn-off energy evaluation with the piecewise linear current mode |      |

| 3.4.1 Zero-order turn-off current in ohmic region                             |      |

| 3.4.2 Zero-order turn-off current in saturation region                        |      |

| 3.4.3 Zero-order turn-off current in cutoff region                            | 40   |

| 3.5 Average turn-on energy evaluation with the piecewise linear current mode  | 140  |

| 3.5.1 Zero-order turn-on current in cutoff region                             |      |

| 3.5.2 Zero-order turn-on current in saturation region                         |      |

| 3.5.3 Zero-order turn-on current in ohmic region                              |      |

| 3.5.4 Resistive connected region with steady state input                      | 42   |

| 3.5.4.1 Zero-order turn-on current in saturation region            | 42 |

|--------------------------------------------------------------------|----|

| 3.5.4.2 Zero-order turn-on current in ohmic region                 | 43 |

| 3.6 Switching energy in the Transistor parasitic capacitances      | 45 |

| 3.7 Summary                                                        |    |

|                                                                    |    |

| 4. AVERAGE POWER ANALYSIS OF INVERTER WITH THE PWLMODEL            | 49 |

| 4.0 Introduction                                                   | 49 |

| 4.1 Energy per cycle analysis of inverter driving load capacitance |    |

| 4.1.1 Turn-off energy analysis                                     |    |

| 4.1.2 Turn-on energy analysis                                      |    |

| 4.1.3 Switching energy in the transistor parasitic capacitances    | 54 |

| 4.2 Energy per cycle calculation                                   |    |

| 4.2.1 Energy per cycle evaluation from the model                   | 55 |

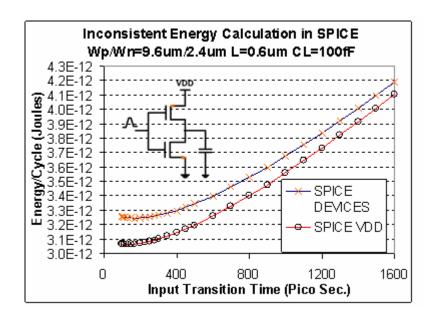

| 4.2.2 Energy per cycle simulation from SPICE                       | 57 |

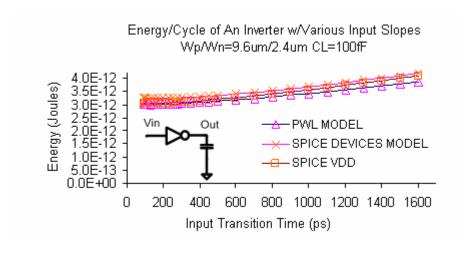

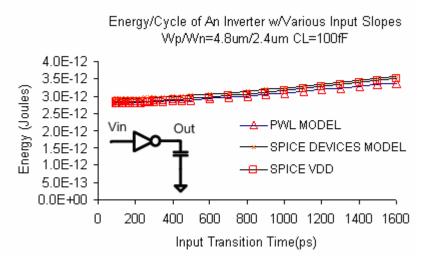

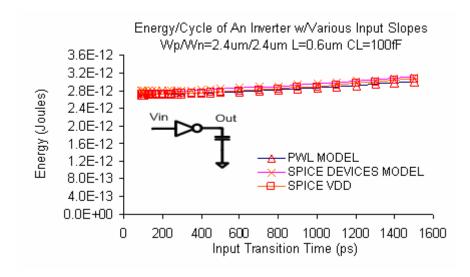

| 4.3 Model accuracy of inverter driving load capacitance            | 57 |

| 4.3.1 Model accuracy in AMI CMOS 0.5µm process                     |    |

| 4.3.2 Model accuracy in TSMC CMOS 0.18µm process                   | 60 |

| 4.4 Model accuracy of inverter driving inverter gate load          | 62 |

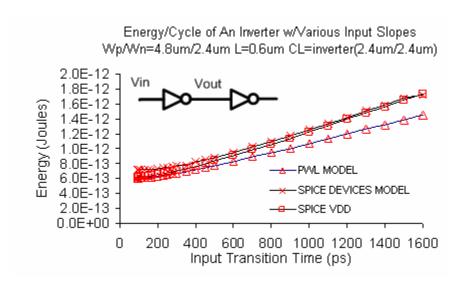

| 4.4.1 Model accuracy in AMI CMOS 0.5μm process                     |    |

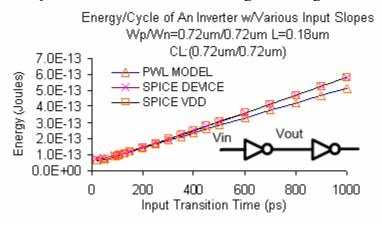

| 4.4.2 Model accuracy in TSMC CMOS 0.18μm process                   | 63 |

| 4.5 Summary                                                        | 64 |

| 5. COMPLEX GATES ANALYSIS WITH A PIECEWISE LINEAR MODEL.           | 66 |

| 5.0 Introduction                                                   | 66 |

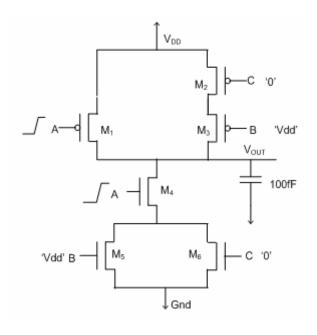

| 5.1 Average power analysis of two-input NAND gate                  |    |

| 5.1.1 Two-input NAND gate driving capacitance load                 |    |

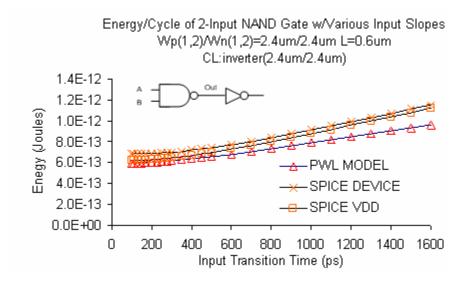

| 5.1.2 Model accuracy in NAND gate in AMI 0.5μm process             |    |

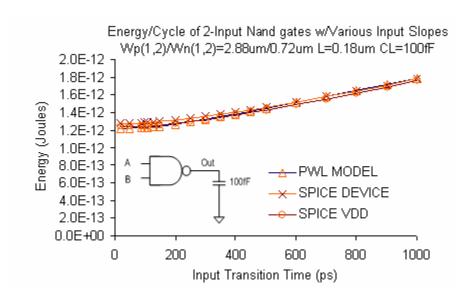

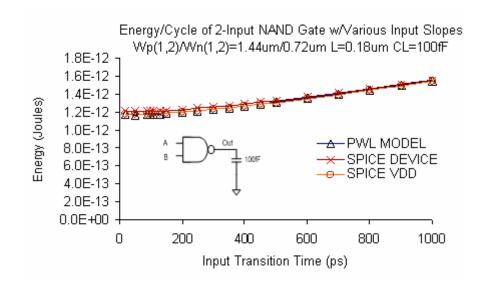

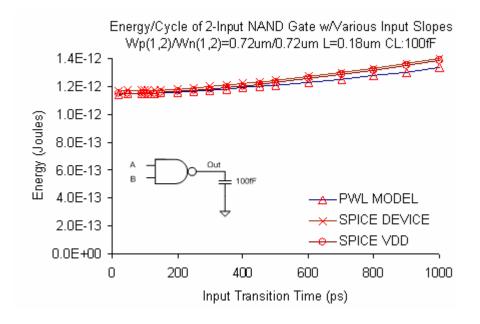

| 5.1.3 Model accuracy in NAND gate in TSMC 0.18µm process           |    |

| 5.2 Average power analysis of OAI gate                             | 73 |

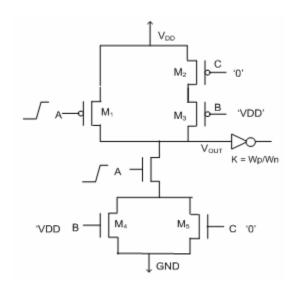

| 5.2.1 Average power analysis of OAI gate driving capacitance load  | 74 |

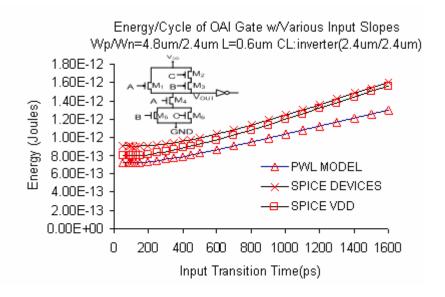

| 5.2.1.1 Accuracy of model in OAI gate in AMI 0.5µm process         |    |

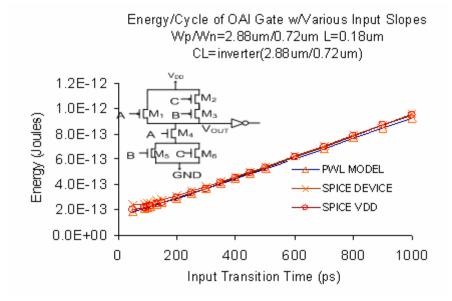

| 5.2.1.2 Model accuracy in OAI gate in TSMC 0.18µm process          | 76 |

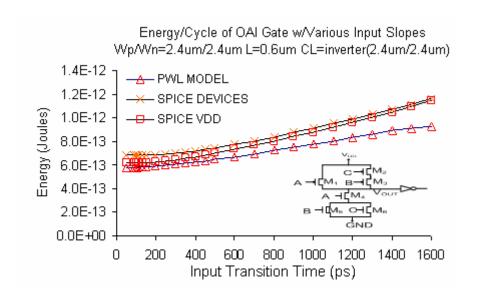

| 5.2.2 Average power analysis of OAI gate driving an inverter load  |    |

| 5.2.2.1 Model accuracy in OAI gate in AMI 0.5μm process            | 79 |

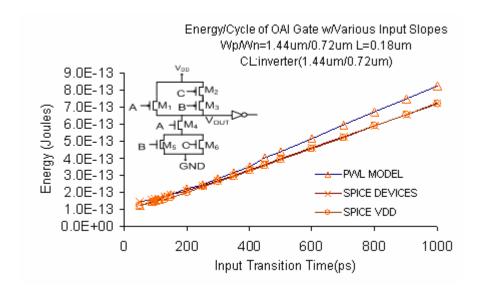

| 5.2.2.2 Model accuracy in OAI gate in TSMC 0.18µm process          | 81 |

| 6. CONCLUSION                                                      | 82 |

| BIBLIOGRAPHY                                                       | 86 |

|                                                                    |    |

# **APPENDICES**

| APPENDIX                                                    | Page |

|-------------------------------------------------------------|------|

| A Average power simulation in the SPICE SPECTRE             | 91   |

| B Model parameter extractions for AMI 0.5μm and TSMC 0.18μm |      |

| Process                                                     | 96   |

| C Coding and implementation                                 | 106  |

# LIST OF TABLES

| TABLE                                                                                                                   | Page |

|-------------------------------------------------------------------------------------------------------------------------|------|

| 1 Linearized parasitic transistor capacitance with overlap capacitance                                                  |      |

| 2 Average power simulation of inverter in Fig.4.5 using PWL model for various input transition time from 1000ps to 20ps |      |

| 3 Comparisons of average power predictions in SPICE and PWL model with various input slopes from 1000ps to 90ps         |      |

| B.1 Falling input PMOS parameters for AMI 0.5µm process                                                                 | .99  |

| B.2 Rising input PMOS parameters for AMI 0.5µm process                                                                  |      |

| B.4 Rising input NMOS parameters for AMI 0.5 µm process                                                                 | 100  |

| B.5 Falling input PMOS parameters for TSMC 0.18µm process                                                               |      |

| B.7 Falling input NMOS parameters for TSMC 0.18µm process                                                               | 102  |

# LIST OF FIGURES

| FIGURES                                                                                   | Page |

|-------------------------------------------------------------------------------------------|------|

| 1.1 CMOS inverter.                                                                        | 4    |

| 1.2 CMOS two input NAND gate.                                                             |      |

| 1.3 CMOS OAI gate                                                                         |      |

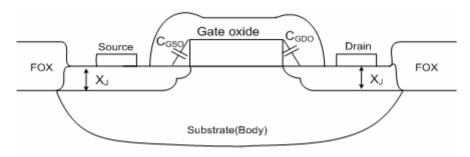

| 2.1 Four terminal MOSFET device and its parasitic capacitances                            |      |

| 2.2 Off-state currents from the transistor gate to its conducting channel                 |      |

| 2.3 Veendrick's short-circuit current model of an inverter without load                   |      |

| 3.1 Average power measurement from the power supply current                               | 20   |

| 3.2 Transistor switch-level models in ohmic, saturation, and cutoff region                | 21   |

| 3.3 Accuracy of the PWL switching current model for 2.4µm/0.6µm nFET                      | 23   |

| 3.4 Accuracy of the PWL switching current model for 4.8um/0.6um pFET                      | 23   |

| 3.5 Sign convention for zero-order piecewise linear switching current                     | 24   |

| 3.6 Channel storage charge model                                                          | 25   |

| 3.7 Sign convention for channel capacitive currents in transistors                        | 26   |

| 3.8 Gate overlap capacitances for FETs                                                    | 30   |

| 3.9 Input ramp approximation                                                              |      |

| 3.10 Piecewise linear approximation of input ramps in resistance connected region         | .32  |

| 3.11 Notation of transistor number 'm' and circuit node names                             | 34   |

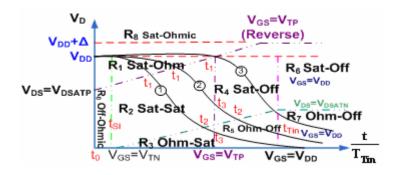

| 4.1 Inverter driving load capacitance with rising input ramp approximation                | 50   |

| 4.2 Inverter transient analysis with boundaries and operation regions                     |      |

| with rising input ramp approximation                                                      | 51   |

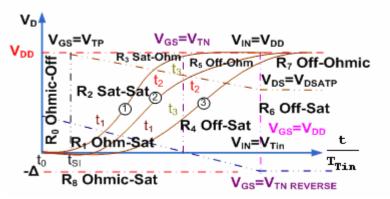

| 4.3 Inverter driving load capacitance with falling input ramp approximation               | 53   |

| 4.4 Inverter transient analysis with boundaries and operation regions                     |      |

| with falling input ramp approximation                                                     | 53   |

| 4.5 Average power calculation by the model for TSMC 0.18µm process                        |      |

| 4.6 Accuracy of the PWL model in inverter ( $K = 4$ , 0.5 $\mu$ m) driving 100fF load     |      |

| 4.7 Accuracy of the PWL model in inverter ( $K = 2, 0.5 \mu m$ ) driving 100fF load       |      |

| 4.8 Accuracy of the PWL model in inverter ( $K = 1, 0.5\mu m$ ) driving 100fF load        |      |

| 4.9 Accuracy of the PWL model in inverter ( $K = 4$ , 0.18 $\mu$ m) driving 100fF load    |      |

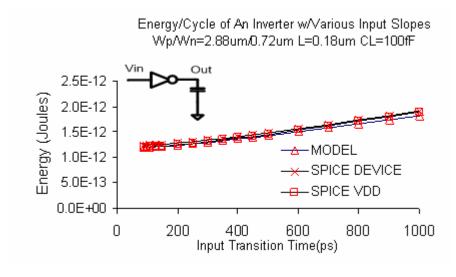

| 4.10 Accuracy of the PWL model in inverter ( $K = 2$ , 0.18 $\mu$ m) driving 100fF load   |      |

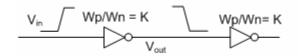

| 4.11 Inverter driving gate load capacitance                                               |      |

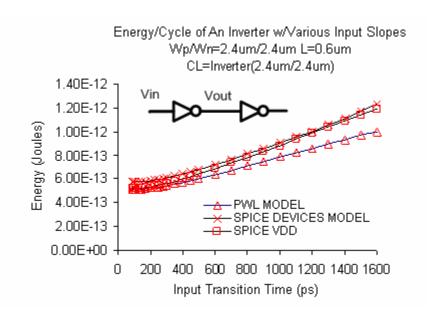

| 4.12 Accuracy of the PWL model in inverter ( $K = 2$ , 0.5 $\mu$ m) driving inverter load | 62   |

| 4.13 Accuracy of the PWL model in inverter ( $K = 1, 0.5 \mu m$ ) driving inverter load   | 63   |

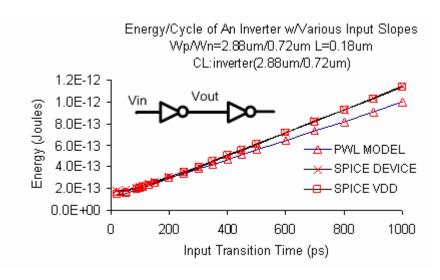

| 4.14 Accuracy of the PWL model in inverter ( $K = 4, 0.18\mu m$ ) driving inverter load    |          |

|--------------------------------------------------------------------------------------------|----------|

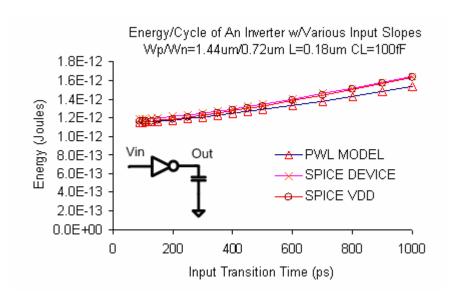

| 4.15 Accuracy of the PWL model in inverter ( $K = 2$ , 0.18 $\mu$ m) driving inverter load |          |

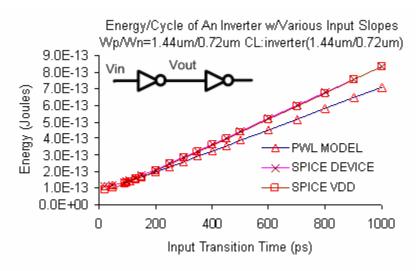

| 4.16 Accuracy of the PWL model in inverter ( $K = 1, 0.18\mu m$ ) driving inverter load    | 1.64     |

| 5.1 Two-input NAND driving load capacitance                                                |          |

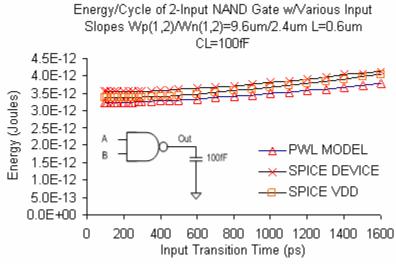

| 5.2 Accuracy of the PWL model in two-input NAND gate ( $K = 4, 0.5 \mu m$ ) driving        |          |

| 100fF load                                                                                 | 68       |

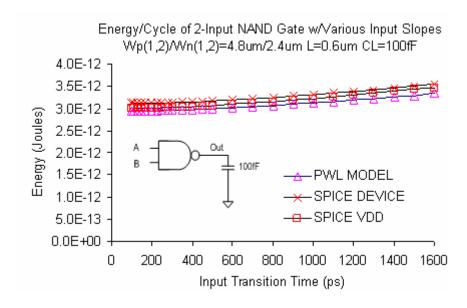

| 5.3 Accuracy of the PWL model in two-input NAND gate ( $K = 2, 0.5\mu m$ ) driving         |          |

| 100fF load                                                                                 | 69       |

| 5.4 Accuracy of the PWL model in two-input NAND gate ( $K = 2, 0.5 \mu m$ ) driving        |          |

| inverter gate load.                                                                        | 69       |

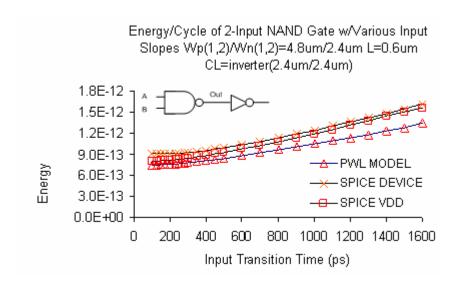

| 5.5 Accuracy of the PWL model in two-input NAND gate ( $K = 1, 0.5 \mu m$ ) driving        |          |

| inverter gate load.                                                                        | 70       |

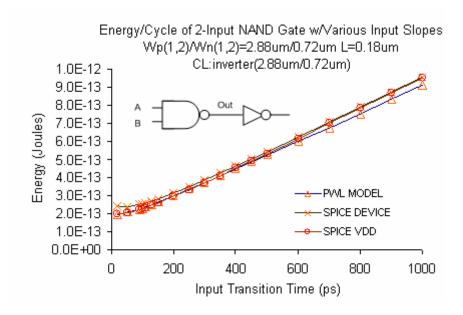

| 5.6 Accuracy of the PWL model in two-input NAND gate ( $K = 4$ , 0.18µm) driving           | <u> </u> |

| 100fF load                                                                                 | 70       |

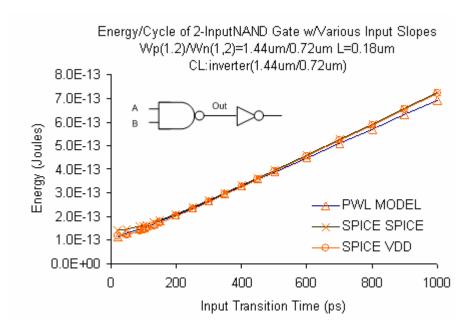

| 5.7 Accuracy of the PWL model in two-input NAND gate ( $K = 2, 0.18 \mu m$ ) driving       |          |

| 100fF load                                                                                 |          |

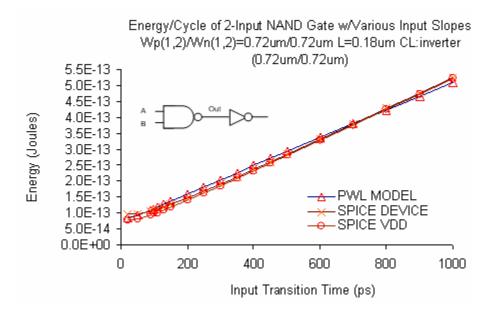

| 5.8 Accuracy of the PWL model in two-input NAND gate (K = 1, 0.18 µm) driving              |          |

| 100fF load                                                                                 | _        |

| 5.9 Accuracy of the PWL model in two-input NAND gates ( $K = 4$ , 0.18µm) driving          | 12       |

| inverter gate load.                                                                        | _        |

| 5.10 Accuracy of PWL model for a two-input NAND gate ( $K = 2, 0.18\mu m$ ) driving        |          |

| inverter gate load.                                                                        | 72       |

| 5.11 Accuracy of the PWL model in two-input NAND gate (K = 1, 0.18µm) driving              |          |

| inverter gate load.                                                                        | _        |

| 5.12 OAI Gates driving a 100fF Load                                                        |          |

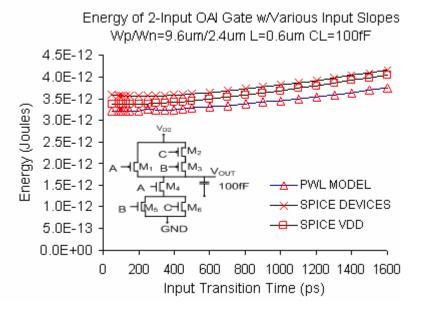

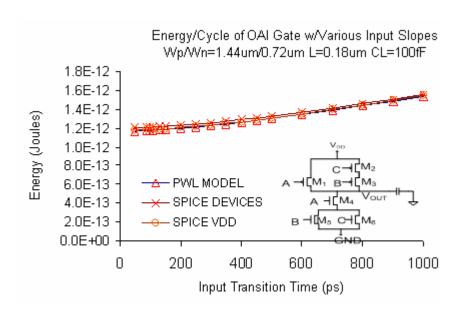

| 5.13 Accuracy of the PWL model in OAI gate ( $K = 4$ , 0.5 $\mu$ m) driving 100fF load.    | 75       |

| 5.14 Accuracy of the PWL model in OAI gate ( $K = 2, 0.5 \mu m$ ) driving 100fF load.      | 75       |

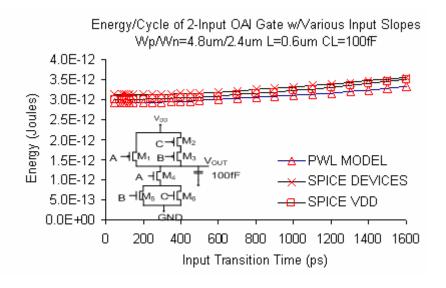

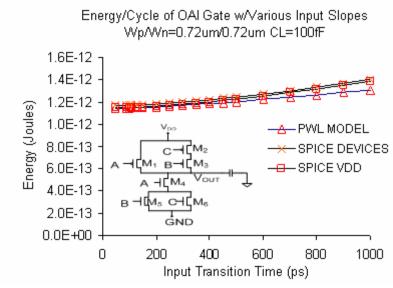

| 5.15 Accuracy of the PWL model in OAI gate (K = 1, 0.5µm) driving 100fF load.              |          |

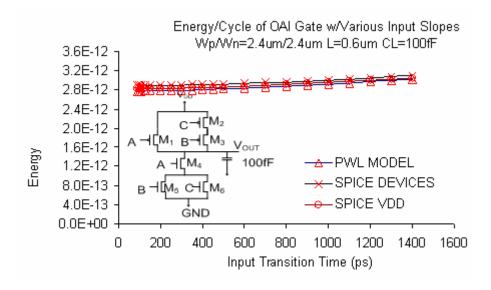

| 5.16 Accuracy of the PWL model in OAI gate ( $K = 1, 0.18\mu m$ ) driving 100fF load       |          |

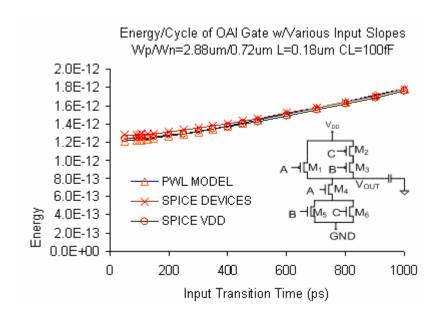

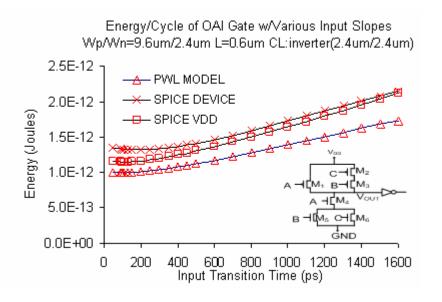

| 5.17 Accuracy of the PWL model in OAI gate ( $K = 2, 0.18\mu m$ ) driving 100fF load       |          |

| 5.18 Accuracy of the PWL model in OAI gate (K = 1, 0.18µm) driving 100fF load              |          |

| 5.19 OAI gate driving different inverter gate loads                                        |          |

| 5.20 Accuracy of the PWL model in OAI gate ( $K = 4$ , 0.5 $\mu$ m) driving inverter       | , 79     |

| 5.21 Accuracy of the PWL model in OAI gate ( $K = 2, 0.5 \mu m$ ) driving inverter         |          |

| 5.22 Accuracy of the PWL model in OAI gate ( $K = 1, 0.5 \mu m$ ) driving inverter         |          |

| 5.23 Accuracy of the PWL model in OAI gate ( $K = 4$ , 0.18µm) driving inverter            |          |

| 5.24 Accuracy of the PWL model in OAI gate ( $K = 2, 0.18\mu m$ ) driving inverter         |          |

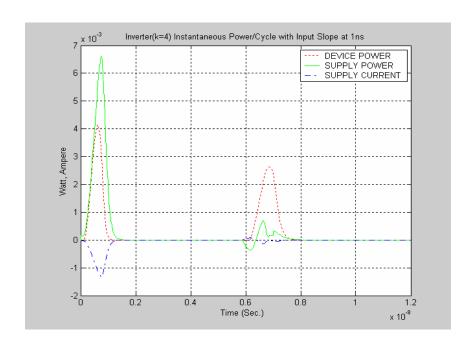

| A.1 Average power simulation of inverter in SPICE                                          |          |

| A.2 SPICE power waveform/cycle with 1ns input slope: dot in red: total device              | , _      |

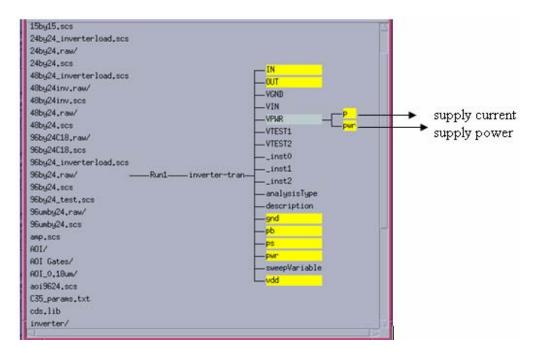

| power; solid green line: supply power dash-dot in blue: supply current                     | 93       |

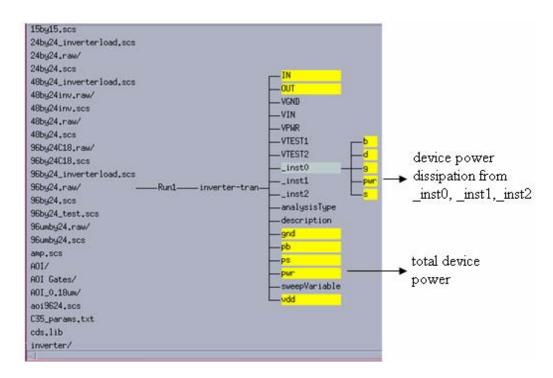

| A.3 Average power simulation in power supply in SPECTRE                                    |          |

| A.4 Average device power simulation in SPECTRE                                             |          |

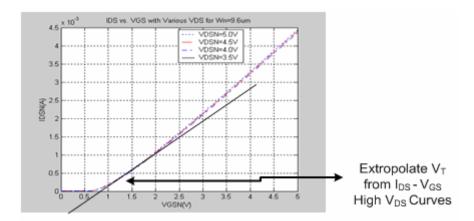

| B.1 Threshold voltage extraction from high V <sub>DSN</sub> curves in 0.5µm process        |          |

| D.1 Threshold voltage extraction from high v DSN curves in 0.3 µm process                  | フ /      |

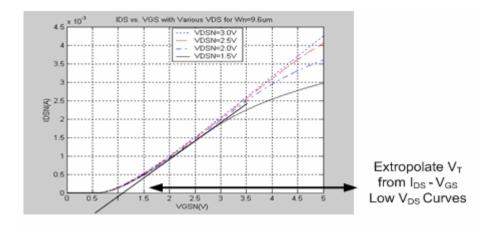

| B.2 Threshold voltage extraction from low $V_{DSN}$ curves in 0.5 $\mu$ m process | 97  |

|-----------------------------------------------------------------------------------|-----|

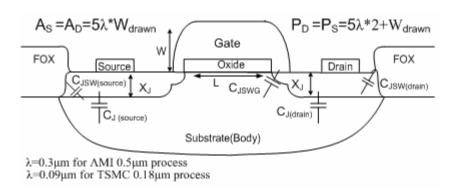

| B.3 Transistor diffusion capacitance model                                        | 103 |

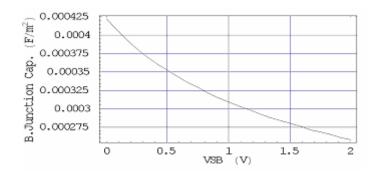

| B.4 Source junction capacitance versus body bias                                  |     |

## LIST OF PHYSICAL CONSTANTS AND PROCESS PARAMETERS

$$\varepsilon_0 = 8.85 \times 10^{-14} \, \text{F/m}$$

$$\varepsilon_{\text{ox}}$$

= 3.97 for silicon dioxide

$$k = 1.3803 \times 10^{-23} \text{ Joule}_{0} \text{ K}$$

kT =

$$4.1409 \times 10^{-21}$$

Joule for room temp. at  $27^{\circ}$

q =

$$1.6 \times 10^{-19}$$

Coulomb

$$C_{\text{ox}} = \frac{\varepsilon_{\text{ox}} \cdot \varepsilon_0}{t_{\text{ox}}} = \frac{3.51 \times 10^{-11} \text{ F/m}}{t_{\text{ox}}(\text{m})} \quad \text{(for the gate oxide on silicon)}$$

$$\beta_{n} = \mu_{n} \cdot C_{ox}$$

$$\beta_{p} = \mu_{p} \cdot C_{ox}$$

# LIST OF SYMBOLS

| Symbo               | l Meaning                                                                    | Unit              |

|---------------------|------------------------------------------------------------------------------|-------------------|

| a <sub>n</sub>      | Ratio of conductance and trans-conductance for the nMOS transistor           |                   |

| a<br>p              | Ratio of conductance and transconductance for the pMOS transistor            |                   |

| β                   | Effective transistor strength                                                | $A.V^{-2}$        |

| C                   | Capacitance matrix                                                           | F                 |

| $C_d$               | Depletion layer capacitance                                                  | F                 |

| $C_{GG}$            | Linearized parasitic capacitance on the gate of the transistor               | F                 |

| $C_{GS}$            | Linearized parasitic capacitance on the gate-source of the transistor        | F                 |

| $C_{gdo}$           | Voltage independent gate-drain overlap capacitance per unit gate width       | F.m <sup>-1</sup> |

| $C_{gso}$           | Voltage independent gate-source overlap capacitance per unit gate width      | F.m <sup>-1</sup> |

| $C_{ox}$            | Oxide capacitance per unit area                                              | $F.m^{-2}$        |

| $E_{I_{vdd}}$       | Energy dissipation due to the short-circuit current and dynamic current      | J                 |

| E <sub>ivdd</sub>   | Energy dissipation due to the first-order channel capacitive currents        | J                 |

| $G_{m}$             | Conductance of the m-th transistor                                           | S                 |

| G                   | Conductance matrix                                                           | S                 |

| E/T                 | Energy dissipation per switching cycle                                       | J/S               |

| $\epsilon_0$        | Permittivity of vacuum                                                       | F.m <sup>-1</sup> |

| $\epsilon_{\rm ox}$ | Relative permittivity of oxide                                               |                   |

| I <sub>vdd</sub>    | Zero-order power supply current in the piecewise linear transistor model     | A                 |

| i<br>vdd            | First-order power supply current in the piecewise linear transistor model    | A                 |

| $I_{Sm}$            | Zero-order piecewise linear switching source current of the m-th transistor  | ·A                |

| $i_{\mathrm{Sm}}$   | First-order piecewise linear switching source current of the m-th transistor | A                 |

| $I_{Dm}$            | Zero-order piecewise linear switching drain current of the m-th transistor   | A                 |

| $i_{\mathrm{Dm}}$   | First-order piecewise linear switching drain current of the m-th transistor  | A                 |

| $I_{SC}$            | Short-circuit current                                                        | A                 |

| k                                                                                                              | Boltzman's constant                                                    | J.K <sup>-1</sup>   |

|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------|

| τ                                                                                                              | Delay time                                                             | second or s         |

| $\tau_{\rm r}$                                                                                                 | Delay time for rising signal                                           | second or s         |

| $\tau_{\mathrm{f}}$                                                                                            | Delay time for falling signal                                          | second or s         |

| $\mu_{n}$                                                                                                      | Channel electron mobility                                              | $m^2 V^{-1} s^{-1}$ |

| $\mu_{P}$                                                                                                      | Channel hole mobility                                                  | $m^2 V^{-1} s^{-1}$ |

| Pavg                                                                                                           | Average power dissipation                                              | W                   |

| P <sub>dynami</sub>                                                                                            | <sub>c</sub> Dynamic power dissipation                                 | W                   |

| $P_{SC}$                                                                                                       | Short circuit power dissipation                                        | W                   |

| $P_{OFF}$                                                                                                      | Off-state leakage power dissipation                                    | W                   |

| $I_T$                                                                                                          | Zero-order quasi-static current in the transistor channel              | A                   |

| $i_T$                                                                                                          | First-order quasi-static current in the transistor channel             | A                   |

| $V_{DSsat}$                                                                                                    | Drain-source saturation voltage of the transistor                      | V                   |

| $V_{T}$                                                                                                        | Transistor threshold voltage                                           | V                   |

| $	ilde{	ext{V}}$                                                                                               | Approximated output voltage in the steady state                        | V                   |

| $	ilde{	ilde{V}} \ 	ilde{	ilde{	ilde{V}}} \ 	ilde{	ilde{	ilde{V}}} \ 	ilde{	ilde{	ilde{V}}} \ 	ilde{	ilde{V}}$ | First-order terms for the approximated output voltage                  | V                   |

| $\ddot{	ilde{	ilde{V}}}$                                                                                       | Second-order terms for the approximated output voltage                 | V                   |

| V                                                                                                              | Output voltage of the resistive connected node                         | V                   |

| S                                                                                                              | Sub-threshold slope                                                    | mV/decade           |

| $T_{Tin}$                                                                                                      | Input transition time                                                  | S                   |

| $t_{ox}$                                                                                                       | Gate oxide thickness                                                   | m                   |

| X <sub>Part</sub>                                                                                              | Parameter for the channel charge partition                             |                     |

| $\phi_{\mathrm{B}}$                                                                                            | Built-in potential of the bottom wall junction capacitance             | V                   |

| $\phi_{\rm BSW}$                                                                                               | Built-in potential of the isolation side sidewall junction capacitance | V                   |

| $\phi_{\rm BSWG}$                                                                                              | Built-in potential of the gate side sidewall junction capacitance      | V                   |

#### CHAPTER 1

#### INTRODUCTION

#### 1.0 Purpose of the Study

Power dissipation is one of the major concerns for high speed very large scale integrated circuits (VLSI) design. Power dissipative components in CMOS circuits consist of off-state leakage power, glitch power, and switching transient power. This paper presents a piecewise linear modeling of switching transient power of CMOS digital circuits, which includes the short-circuit power, dynamic power, and switching power of parasitic capacitors. The piecewise linear power model takes a simplified approach to compute average power (or energy per cycle) without solving differential equations with large matrices. Even thought SPICE (Stanford Program for Integrated Circuit Emulation) can handle the accurate and nonlinear behaviors of transistors with more than one hundred fitting parameters, it usually takes a great amount of computation time for a large circuit simulation. Another competing circuit simulator is the switch level simulator, IRSIM, which is a tool for simulating digital circuits. It is a switch-level simulator, because the transistors are treated as ideal switches, and the extracted capacitances and resistances are used to find the RC time constants for the ideal switches

to predict the relative timing events [34]. Thus, it is an ideal transistor model, and is not accurate in computing transient switching power. The proposed piecewise linear model, as an improved switch resistor model, closes the performance gap between SPICE and switch-level simulators in power estimation.

## 1.1 Significance of the Study

Dynamic power dissipation is well known and defined for CMOS digital circuits. Analytical works, more recently, for power modeling are focused on short-circuit power modeling with slope effects, velocity saturation and gate-to-drain capacitive coupling effects, propagation delay and short channel effects. Analytical works in off-state leakage power modeling are also popular as the transistor size shrinks into the deep submicron realm. However, channel capacitive currents induced power dissipation is not addressed in other transistor models [4] [6] [7] [13]. Therefore, the proposed piecewise linear model not only includes the first-order capacitive currents but also takes into account the effect of the slope of the input waveform in average power estimation. Most fast simulators [34] [39] assume a step input, so that the piecewise linear model is at least an improved yet simplified nonlinear transistor model to replace the traditional resistor model in fast simulators. The piecewise linear model is verified in the submicron AMI CMOS 0.5μm and deep submicron TSMC 0.18μm process.

#### 1.2 Limitation of the Piecewise Linear Model

The model is constructed with *I-V* and *C-V* models approximating the complex BSIM (Berkeley Short-Channel Insulated gate field effect transistor Model) model [4] for CMOS transistors as switches. The current–voltage (*I–V*) model describes the zero–order (dc) behavior of a quasi-static current between the source and drain terminals, and the capacitance–voltage (*C–V*) model describes the first-order dynamic behavior of channel capacitive currents associated with transistor parasitic capacitances. The piecewise linear *I–V* model approximates the physical transistor current with different piecewise linear regions in cutoff, ohmic, and saturation. The proposed model shows that its accuracy is within 3 to 5 % of SPICE for fast inputs in AMI 0.5μm and TSMC 0.18μm processes, and the accuracy may reach 15 to 20 % error for input transition times greater than 2000 pico-second in AMI 0.5μm process and 1000 pico-second in TSMC 0.18μm process. However, very slow input occurs not very often in submicron technologies and can usually be speeded up with circuit design techniques.

#### 1.3 Introduction to the CMOS logic families

#### 1) Standard CMOS logic gates

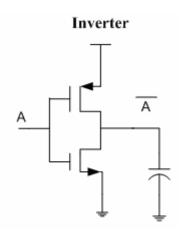

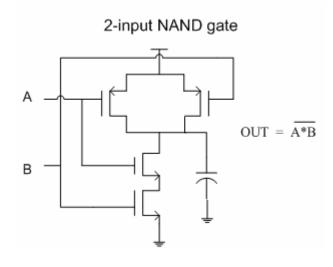

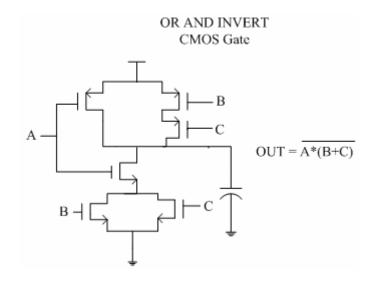

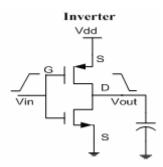

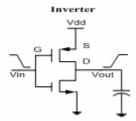

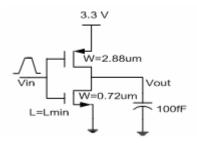

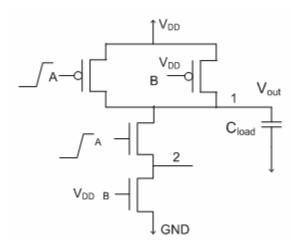

A standard CMOS logic gate has the same number of pFETs and nFETs with the transistors connected in a complementary manner. A standard CMOS inverter, NAND, and NOR may be designed with different sizes to meet speed and power requirements. Most power dissipation of CMOS circuits comes from the switching transient power, which includes the short-circuit power, and dynamic power. A piecewise linear model to calculate the average power dissipation of a CMOS inverter (Fig.1.1), a two-input NAND

gate (Fig.1.2), and a three-input OAI (Or-And-Invert) digital circuit (Fig.1.3) driving a constant capacitor or driving various sizes of inverter loads, are chosen to compare modeling accuracy with the average power of the power supply as predicted by SPICE.

Figure 1.1 CMOS inverter

Figure 1.2 CMOS two input NAND gate

Figure 1.3 CMOS OAI gate

#### 1.4 Organization

In chapter two, conventional power models are introduced along with literature reviews of off-state leakage power, short circuit power, glitch power, and dynamic power models. In chapter three, the piecewise linear switching current–voltage (I-V) model and channel storage charge or channel capacitance–voltage (C-V) model are introduced. I-V and C-V models in the piecewise linear model are used to demonstrate the model in computing average power from the power supply currents. In chapter four, computing average power with the piecewise linear model is coded in C++ language for an inverter. In chapter five, more complex circuits are chosen. Average power evaluations for two-input NAND and Or-And-Inverter (OAI) with various transistor sizes and loads are presented. Findings and conclusion are presented in chapter six.

#### **CHAPTER 2**

#### CONVENTIONAL TRANSISTOR MODELS FOR POWER ESTIMATION

#### 2.0 Definitions: Energy or Power

The use of power as a performance measure is often misleading. In battery operated devices, the amount of energy needed for operations may be a more useful measure because a battery stores a finite amount of energy, not power [35]. Energy per operation or average power is often used to evaluate energy efficiency of CMOS circuits. Definition of instantaneous power and average power (or energy per cycle), is summarized as follows.

The instantaneous power P(t) is proportional to the power supply current  $I_{vdd}(t)$  and the supply voltage [8], which is written as

$$P(t) = I_{vdd}(t) \cdot V_{dd}$$

(2.1)

The average power dissipation  $P_{avg}$  is defined as an integration of instantaneous power P(t) over some time interval T. Also, the average power dissipation is equivalent to the energy consumed over some interval T [8] and is written as

$$P_{avg} = \frac{1}{T} \int_{0}^{T} I_{vdd}(t) \cdot V_{dd} dt = \frac{E}{T}$$

(2.2)

Energy 'E' is calculated from the integration of instantaneous power supply current during the period when the instantaneous power supply current enters the circuit [8].

### 2.1 Sources of CMOS Power Dissipation

Transistor dissipative power is mainly due to the currents from the channel inversion layer traveling in a resistive channel between source and drain terminals. Unfortunately, the power supply current into the transistor channel is a nonlinear function of terminal voltages. Transistor channel currents are, in fact, space-averaged quasi-static currents in the channel [6], which includes the voltage-dependent quasi-static current component and a time-varying charging current component [25]. Conventional transistor models [25] show that quasi-static currents in the channel consist of the following components.

$$I_{T} = h_{T}(V_{D}, V_{G}, V_{B}, V_{S})$$

(2.3)

$$i_T(t) = h_T(v_D(t), v_G(t), v_B(t), v_S(t))$$

(2.4)

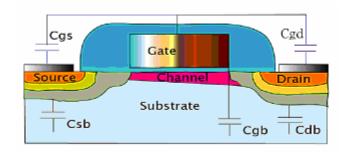

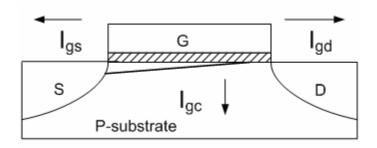

The channel current  $I_T$  expressed in (2.3) is a function of the terminal voltage on the gate, source, drain, and substrate of the transistor [25] without time-varying voltages. Thus, the expression for  $I_T$  is, in fact, a zero-order quasi-static DC model. Channel capacitive currents which are equivalent to "charging currents" [25] in (2.4) are function of the time derivatives of the channel charge storage, which depends on the time-varying voltages associated with each terminal [25] [33], therefore, it is the first-order quasi-static capacitive currents associated with voltage-dependent parasitic capacitances. Figure 2.1 illustrates the FET device with parasitic capacitances. Five distinct types of transistor current contribute to the power dissipation of a CMOS circuit.

Figure 2.1 Four terminal MOSFET device and its parasitic capacitances

- I. Transistor off-state sub-threshold leakage currents

- II. Switching transient currents, which include

- 1) Load capacitor charge and discharge through pFET and nFET network.

- 2) Short-circuit current conduction between the power and ground nodes through both FET's simultaneously.

- III. Channel capacitive currents due to switching transistors

- IV. Glitch currents due to unequal arrival of signals to the circuit.

#### 2.1.1 Off-State Leakage Power of the Transistor

For CMOS logic families and memory circuits, the performance factors include the ratio of off-state leakage current (sub-threshold conduction current) to turn-on current ( $I_{OFF}$  /  $I_{ON}$ ), power, delay, and reliability [15]. Leakage current comes from gate, source, and drain terminals. Gate leakage occurs due to the scaling of gate oxide thickness and the resulting tunneling current from the gate to channel in the transistor as illustrated in Figure 2.2. A study [15] has shown that the gate oxide thickness  $T_{OX}$  can be thinned down to 2nm before the leakage current becomes unacceptable for CMOS circuits.

Figure 2.2 Off-state currents from the transistor gate to its conducting channel

The other concern for scaling oxide thickness thinner than 2 nm is that threshold voltage  $V_T$  can not be scaled down proportionally with the channel length. The primary barrier is a leakage current dependent sub-threshold slope, S, which is a measure of transistor turn-off rate from the gate voltage versus sub-threshold leakage current. S should be small in order to reduce leakage current. The sub-threshold slope is written as

$$S \cong \left(\frac{d}{dV_{G}}(\log \cdot I_{DS})\right)^{-1} = \frac{\ln 10(kT)}{q} \left(1 + \frac{C_{D}}{C_{OXIDE}}\right)$$

(2.5)

where q denotes the electron charge,  $k = 1.38 \cdot 10^{-23}$  (J/K) Boltzmanns constant, T the absolute temperature in Kelvin,  $C_D$  the incremental capacitance of the depletion layer per unit area, and  $C_{OXIDE}$  is the capacitance of the gate oxide per unit area. The depletion capacitance is a non-linear function of the gate to bulk voltage. When  $V_{GB}$  increases, the value of  $C_D/C_{OXIDE}$  may become negligible. In other words, the sub-threshold slope is largely driven by thermally excited electrons in the channel and has no physical controllability from the manufacturing process. Even though CMOS scaling causes offstate power to increase, a study has shown that the off-state power is 0.01% of active power dissipation in a 1um process while 10% in a 0.1um process [15]. Although off-state power is not included in the piecewise linear approximation in this research, the simple off-state transistor power from equation (2.6) [15] can be approximated with the

currents of the transistors connected to the power supply for each piecewise linear region of operation, where  $W_{TOTAL}$  is the total turned-off transistors width with  $V_{DD}$  across them, and  $I_0$  is the parameter for off-state current per device width, and  $V_T$  is the worse case threshold voltage.

$$P_{OFF} \cong W_{TOTAL} \cdot V_{DD} \cdot I_0 \cdot exp(\frac{-qV_T}{kT})$$

(2.6)

## 2.1.2 Switching Transient Power in CMOS Transistors

There are two components to the switching transient power: dynamic power dissipation and short-circuit power dissipation [8] [28], and the models are reviewed as follows.

### 1. Dynamic Power Dissipation in CMOS Transistors

Dynamic switching power occurs when the pFETs connected to the power supply turns on and a direct current path is established from the power supply to load capacitances. For standard CMOS circuits, the dynamic current consumption is dominated by the power supply current necessary to charge up node capacitances, and the dynamic power consumption  $P_{dynamic}$  is proportional to the power supply current and the square of the supply voltage [8].  $P_{dynamic}$  is expressed as (2.7) [28].

$$P_{dynamic} = \frac{1}{T_{sw}} \int_{0}^{T_{sW}} i_{vdd}(t)v(t)dt$$

$$= \frac{1}{T_{sw}} \int_{0}^{T_{sw}} I_{Dp}V_{DSp}dt + \frac{1}{T_{sw}} \int_{T_{sw}}^{T_{sw}} I_{Dn}V_{DSn}dt$$

(2.7)

where

$$I_{Dp} = -C_{load} \frac{dV_{out}}{dt}$$

(2.8)

$$V_{DSp} = -(V_{dd} - V_{out})$$

$$(2.9)$$

$$I_{Dn} = -C_{load} \frac{dV_{out}}{dt}$$

(2.10)

$$V_{DSn} = V_{out} (2.11)$$

Therefore, average dynamic power is the sum of power computed from the power supply current charging the load capacitance by the pull-up pFET network and discharging the same current by the pull-down nFET network for the second half of cycle. Such that,

$$\begin{split} P_{dynamic} &= \frac{1}{T_{sw}} \int_{0}^{T_{sw}} C_{load} \frac{dV_{out}}{dt} (V_{dd} - V_{out}) dt + \frac{1}{T_{sw}} \int_{T_{sw}}^{T_{sw}} -C_{load} \frac{dV_{out}}{dt} dt \\ &= \frac{1}{T_{sw}} \int_{0}^{V_{dd}} C_{load} (V_{dd} - V_{out}) dV_{out} + \frac{1}{T_{sw}} \int_{V_{dd}}^{0} -C_{load} V_{out} dV_{out} \\ &= \frac{C_{load}}{T_{sw}} V_{dd}^{2} \end{split} \tag{2.12}$$

For a general circuit topology with transistors and capacitors only, total dynamic power dissipation is often computed for switching of all of the nodes according to the switching activity ( $\alpha_i$ ) at the i<sup>th</sup> capacitive node within a circuit, such that

$$P_{\text{dynamic}} = \frac{1}{T_{\text{sw}}} \sum_{i=1}^{N} \alpha_i \cdot C_i \cdot (V_i^{t_1} - V_i^{t_0})^2$$

(2.13)

Dynamic power dissipation assumes that  $v_i^{t_0}$ ,  $v_i^{t_1}$  are full swing signal between ground and  $V_{dd}$  during a complete charge-discharge cycle. Since most gates do not switch every

clock cycle, it is convenient to write the switching frequency as switching activity factor times the clock frequency  $f_{sw}$  [8].

$$P_{dynamic} = \frac{1}{T_{sw}} \cdot V_{dd}^{2} \cdot \sum_{i=1}^{N} C_{i} \cdot \alpha_{i} = f_{sw} \cdot V_{dd}^{2} \cdot \sum_{i=1}^{N} C_{i} \cdot \alpha_{i}$$

(2.14)

## 2. Short Circuit Power Dissipation in CMOS Transistors

Short-circuit power is usually neglected in power calculations by switch-level simulators [34] [39], which often assume a step input response for fast simulation. Due to the intrinsic resistance and parasitic capacitances in a transistor channel, any transistor circuit takes a finite time to rise or fall to its final value at any given node. Therefore, real circuits are usually driven by input with a finite transition time, and consequently, short-circuit power can be as significant as the dynamic power [17] and cannot be neglected in power calculation. The short circuit power dissipation component is proportional to the input transition time and the load capacitance when a direct current path is established between the power supply and ground. Evaluation of the short circuit power component requires information about input transition times (input rise and fall times), transistor sizes, and the load driven by the circuit.

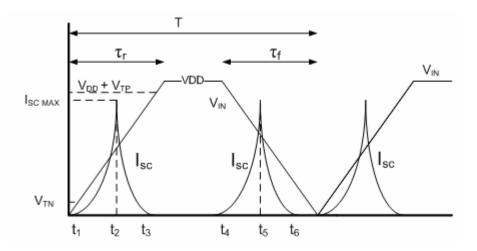

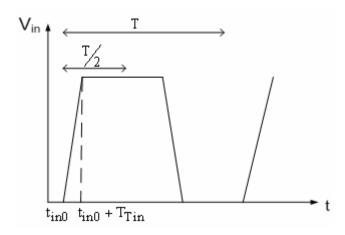

There are many analytical evaluations of the short-circuit power dissipation component for a simple inverter gate [17], [18], [19], and [20]. The first closed-form expression for the short-circuit power component for a CMOS inverter without load capacitor was from Veendrick in 1984 [17] [23]. The short-circuit power expression Veendrick derived assumed that the short-circuit current was symmetric for each input transition with a matched transistor's mobility and threshold voltage, with equal input rise and fall time  $\tau$  in a periodic signal T as shown in Fig. 2.4.

Figure 2.3 Veendrick's short-circuit current model of an inverter without load

Under Veendrick's assumption, short-circuit current component in an inverter was approximated by transistors in the saturation, such that

$$I = \frac{\beta}{2} (V_{IN} - V_T)^2 \qquad 0 \le I \le I_{SC MAX}$$

(2.15)

Since the inverter is symmetric about  $t_2$ ,  $I_{SC\,MAX}$  occurs at half of the supply voltage. The mean short circuit current is determined by integrating the instantaneous current from 0 to time T and divided by T.  $\frac{2}{T}$  is the average number of transition per second.

$$I_{\text{MEAN}} = \frac{1}{T} \int_{0}^{T} I(t)dt = 2\frac{2}{T} \int_{t_{1}}^{t_{2}} \frac{1}{2} \beta (V_{\text{IN}}(t) - V_{T})^{2} dt$$

$$= 2\frac{2}{T} \int_{t_{1}}^{t_{2}} \frac{\beta}{2} (\frac{V_{\text{DD}}}{\tau} t - V_{T})^{2} d(\frac{V_{\text{DD}}}{\tau} t - V_{T})$$

$$= \frac{1}{12} \frac{\beta}{V_{\text{DD}}} (V_{\text{DD}} - 2V_{T})^{3} \cdot \frac{\tau}{T}$$

(2.16)

where

$$\beta_N = \beta_P = \beta$$

$$\boldsymbol{\tau}_r = \boldsymbol{\tau}_f = \boldsymbol{\tau}$$

$$V_{Tn} = - |V_{Tp}| = V_T$$

$$V_{IN}(t) = \frac{V_{DD}}{\tau}t$$

$$t_1 = \frac{V_T}{V_{DD}} \cdot \tau$$

$$t_2 = \frac{\tau}{2}$$

Therefore, following is the short-circuit power of a CMOS inverter with no load capacitance:

$$P_{SC} = \frac{\beta}{12} (V_{DD} - 2 \cdot V_T)^3 \cdot \frac{\tau}{T}$$

(2.17)

The short circuit power expression (2.17) was solved as a function of the input rising and falling transition time ( $\tau$ ) without a load capacitance, and the result may lead to a pessimistic prediction of the short-circuit power dissipation, because Veendrick's short circuit power model assumed transistors operated in saturation region only, which cannot accurately predict short-circuit current as transistors in ohmic region. However, formula (2.17) clearly illustrates that the short-circuit power is proportional to design parameters  $\beta$  and input transition times ( $\tau$ ) of an inverter's input signal. For an inverter with a load capacitance, the transistor  $\beta$  values are determined by the required output rise and fall times [8]. Therefore, dependency of short-circuit power on the input rise and fall times is still valid when an inverter drives a load capacitance. More recently (1996), a closed form expression presented by Bisdounis et al. for short-circuit power dissipation was based on an output waveform expression with a square-law current transistor model [17]. Instead of using a square-law current model, Sakurai and Newton [22] suggested an  $\alpha$ -power

model for the evaluation of short-circuit power dissipation component. Afterward, Vemuru and Scheinberg [23] developed a short-circuit power equation by adopting Sakurai and Newton's α-power MOS model. α-power model and the square law model were proved to be fairly accurate power models, but implementing the higher-order current model takes a fairly large computation time. Hirata, A., et al., [24] reported a piecewise linear function for the short-circuit power dissipation component in an inverter, but the model can not be extended to predict short-circuit power for other circuit topologies.

#### 2.1.3 Glitch Power Dissipation in CMOS Transistors

It is well known that dynamic power dissipation is directly related to the number of signal transitions in full swing, but spurious transitions (or glitches) caused by unequal arrivals of propagation delays of input signals to the gate often occur in many static ICs [42]. Glitch power is often modeled by using the dynamic power dissipation model as equation (2.13) where  $(V_i^{t_1} - V_i^{t_0})$  is the incomplete transition during a complete charge-discharge cycle [40] [41] [42]. Power estimation tools can simulate glitches at the gate level for medium size circuits, but the accuracy of glitch power predictions for large circuits is inadequate [42].

#### 2.2 Summary

Modeling average power dissipation in CMOS circuits, at least, should include the following components for CMOS technologies.

- I. Short-circuit power.

- II. Dynamic power.

- III. Switching power of parasitic capacitances.

Not all transistor models are capable of computing each power dissipation component. For instance, the switch-resistor model in IRSIM [13] [39] simulator can evaluate dynamic power dissipation only. Surprisingly, the HSPICE simulator, one of the most accurate SPICE circuit simulators, does not include the power dissipation caused by nonlinear parasitic capacitors [3]. Many researchers [19] [20] [22] [23] [24] [31] extend the  $\alpha$ -power model to compute short-circuit power dissipation component, but none of the models has addressed the significance of channel capacitive currents in a power evaluation. Besides, the  $\alpha$ -power model usually has a non-integer value for  $\alpha$ , which is not efficient enough to be implemented in a fast simulator. The main difference of the proposed piecewise linear model from previous models in the literature is to compute the average power supply current provided to the circuit instead of evaluating individual power dissipative components for each transistor. In order to compute average power from the power supply current, including channel capacitive currents for a fast simulator, an efficient yet simple transistor model is essential. A simplified (piecewise linear) zeroorder quasi-static switching current model and channel storage charge model are developed to serve the goal and are presented in the following chapter.

#### CHAPTER 3

#### A PIECEWISE LINEAR TRANSISTOR MODEL

## 3.0 Background

The circuit simulator, SPICE, was designed primarily to evaluate circuit performance during the explosive growth of integrated circuits in the late 1960's and early 1970's [38]. A fast simulator, RSIM, was built in the late 1980's and early 1990' became competitive with SPICE for its efficiency but not accuracy in simulating large integrated circuits [39]. The RSIM is a switch-level simulator with speedups of over three orders of magnitude over SPICE [13] [39]. Unfortunately, the switched-resistor model used by RSIM renders it incapable of simulating certain CMOS digital circuits [39] and does not compute power dissipation components other than dynamic power [34]. More recently, a piecewise linear gate modeling of CMOS circuits [36] has improved the switched-resistor model by incorporating a piecewise linear saturation current model and the effects of short-circuit current and channel capacitive currents into gate delay modeling. Also, the model with a fast algorithm for circuit dynamic analysis can predict gate delay within 10% average error of SPICE regardless of circuit topologies [36]. The goal of this research is to extend the same piecewise linear model to compute average power dissipation in CMOS circuits by evaluating average power supply current. The piecewise linear switching current model and part of the circuit dynamic analysis [36] are reviewed in the following section as an essential step to power estimation.

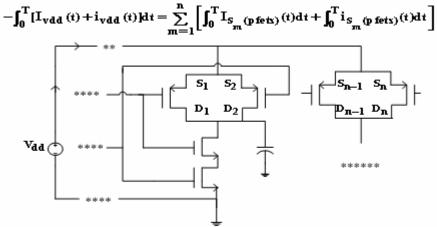

#### 3.1 Evaluation of Average Power Dissipation with the Piecewise Linear Model

Rather than attempting to evaluate instantaneous power from each transistor device for each power dissipation component described at the end of chapter two, the proposed piecewise linear model evaluates average power by evaluating average power supply current from transistor(s) connected to the power supply. With the zero-order switching current-voltage (I-V) model and the channel charge storage or capacitance-voltage (C-V) model introduced in the following section, the average power from the power supply current is evaluated instead of evaluating each transistor with instantaneous current and voltage as functions of time.

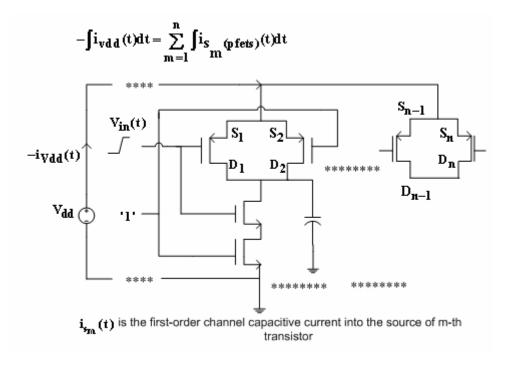

During switching transients that turn off transistors connected to the power supply, only short-circuit current is included in  $I_{vdd}(t)$  calculation because the discharging current for the node capacitance flows through the turn-on nFET network. In contrast, the sum of the dynamic current and the short-circuit current is included in  $I_{vdd}(t)$  calculation when the transistors connected to the power supply turn on, because the charging current from the power supply for the node capacitance flows through the turned-on pFET network and the short-circuit current from the turning-off nFET network flows simultaneously. The switching power of any implicit parasitic capacitance is estimated from  $i_{vdd}(t)$  with the channel storage charge (C-V) model. The power supply current is, in fact, the sum of the currents of every transistor and any explicit capacitance that is directly connected to the power supply. The instantaneous power, P(t), in (2.1) is re-written as (3.1) for the average power evaluation from the piecewise linear model (3.2).

$$P(t) = \left[ I_{vdd}(t) + i_{vdd}(t) \right] \cdot V_{dd}$$

(3.1)

$$P_{avg} = \frac{1}{T} \int_{0}^{T} \left[ I_{vdd}(t) + i_{vdd}(t) \right] dt = \frac{E}{T}$$

(3.2)

The notation  $I_{vdd}$  is used to indicate the power supply current which contributes power dissipation due to the short-circuit current and dynamic current in CMOS circuits [10].  $i_{vdd}$  will be used to indicate the power supply current which comes from the first-order switching power due to any implicit parasitic capacitance from transistors connected to the power supply.

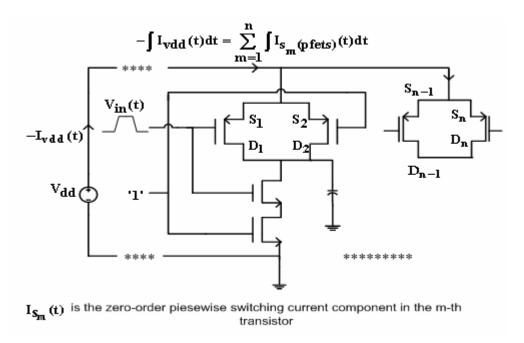

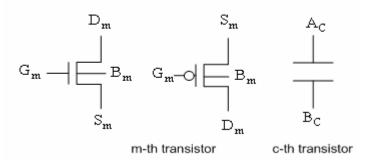

$I_{vdd}(t)$  is evaluated by the model from the sum of each individual transistor source current  $I_{S_m}$ , which represents the short-circuit current (or turn-off current) during input  $(0 \rightarrow 1)$  transitions and also represents the power supply current required to charge the node capacitance (or turn-on current). Whereas  $i_{vdd}(t)$  is estimated from the sum of the individual channel capacitive currents,  $i_{S_m}$ , of each switching transistor connected to the power supply. The subscript stands for the source terminal of m-th transistor(s) connected to the power supply. The turn-off current and turn-on current will be used throughout the paper when the average power supply current is approximated with the piecewise linear model in each switching cycle. The method of computing average power dissipation can be extended for any multi-stage circuit that is partitioned into individual sub-circuit as shown in Figure 3.1.

I<sub>Sm</sub>(t) is the zero-order piecewise linear switching current of m-th p-FET connected to the power supply

Figure 3.1 Evaluation of average power from the power supply current

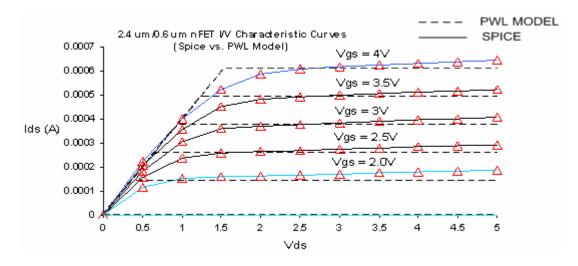

# 3.1.1 Piecewise Linear Switching Current Model

The piecewise linear model for transistor switching is a voltage controlled switch with a series resistance. The simple linear model simplifies the circuit dynamics once the switches have reached their final states. Although the switched resistor model [13] has been used very successfully in circuit simulation [39], it is not adequate to describe the finite time required to switch the transistors on to off. Also, the saturation behavior of the transistors has a significant impact on the switching waveform and average power evaluation. Unfortunately, there is no linear model that can include cutoff, ohmic, and saturation behaviors simultaneously. Complex transistor behavior is simplified to three piecewise linear regions of operation as shown in Figure 3.2. The piecewise linear model is as follows.

is<sub>m</sub> (t) is the piecewise linear first-order capacitive current of m-th p-FET connected to the power supply

Figure 3.2 Transistor switch models in ohmic, saturation, and cutoff region respectively

The zero-order quasi-static switching current denoted as  $I_{Dm}$  and  $I_{Sm}$  (Fig. 3.2) for the drain and source terminal of the m-th transistor connected to the power supply and has the following properties.

$$I_{D_m} = -I_{S_m} \tag{3.3}$$

$$I_{G_{m}} = I_{B_{m}} = 0 (3.4)$$

Equations (3.4) assumes that there is no leakage current flowing through the substrate and gate. Therefore, zero-order quasi-static switching current has the following definitions in the cutoff, ohmic and saturation region for the nFET and pFET transistor in (3.5) and (3.6).

$$\begin{pmatrix} I_{Dm}(off) \\ I_{Dm}(ohmic) \\ I_{Dm}(sat) \end{pmatrix} = \begin{pmatrix} 0, & V_{GSN} < V_{Tn} \\ (a_n \cdot G \cdot V_{DSN})_m, & V_{GSN} > V_{Tn}, V_{DSN} < V_{DSsatn} \\ [G \cdot (V_{GSN} - V_{Tn})]_m, V_{GSN} > V_{Tn}, V_{DSN} > V_{DSsatn} \end{pmatrix}, V_{DSSatn} = \frac{V_{GSN} - V_{Tn}}{a_n}$$

(3.5)

$$\begin{pmatrix} I_{Dm}(off) \\ I_{Dm}(ohmic) \\ I_{Dm}(sat) \end{pmatrix} = \begin{pmatrix} 0, & V_{GSP} > V_{Tp} \\ (a_p \cdot G \cdot V_{DSP})_m, & V_{GSP} < V_{Tp}, V_{DSP} > V_{DSSatp} \\ [G \cdot (V_{GSP} - V_{Tp})]_m, & V_{GSP} < V_{Tp}, V_{DSP} < V_{DSSatp} \end{pmatrix}, V_{DSSatp} = \frac{V_{GSP} - V_{Tp}}{a_p}$$

(3.6)

$$\begin{pmatrix} a_n \\ a_p \end{pmatrix} = \begin{pmatrix} \frac{G_{\text{nohmic}}}{G_{\text{nSat}}} \\ \frac{G_{\text{pohmic}}}{G_{\text{pSat}}} \end{pmatrix}$$

(3.7)

$(a_P\cdot G)_m$  is the conductance of the m-th pFET transistor in the ohmic region and the  $G_{\rm m}$  is the trans-conductance of the m-th transistor in the saturation region. The sign of transistor current at the drain given by (3.5) and (3.6) is determined by the terminal voltages of the transistor. Current going into a terminal indicates a positive drain current and negative current if the current exits from the terminal.  $a_n, a_p, V_{Tn}$ , and  $V_{Tp}$  are process constants and process dependent variables. All parameters are positive except the threshold voltage  $\boldsymbol{v}_{Tp}$  .  $\boldsymbol{a}_n$  ,  $\boldsymbol{a}_p$  are greater than one. Conductance of the pFET and nFET transistor for G<sub>ohmic</sub> and G<sub>sat</sub> are determined from average sheet resistance extrapolated from I/V curves from the transistors used in the test circuits. The piece-wise linear model is a reasonably good approximation to current in saturation, and less accurate for current in the ohmic region as shown in Fig 3.3 and 3.4 when comparing the piecewise linear switching currents with SPICE simulation. However, as illustrated in [39], modeling errors in regions of low drain current usually produce smaller timing errors than errors in regions of high drain current. Therefore, the current mismatch errors in regions of low drain current is not critical for the timing accuracy of the piecewise linear transistor model. Furthermore, additional accuracy for the low drain current can be obtained by adding more piecewise linear regions to better approximate the transistor current in the ohmic region, but adding more regions to the model makes solving for circuit dynamics more time-consuming because the node voltage must be checked at each moment in time to decide which piecewise linear model to use for each transistor in a circuit. The piecewise model is at least a more accurate switching current model than the traditional switched resistor model [13].

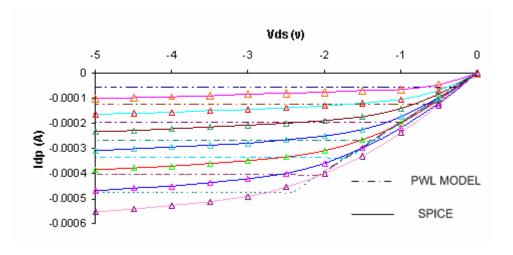

Figure 3.3 Accuracy of the piecewise linear switching current model for  $2.4\mu\text{m}/0.6\mu\text{m}$  nFET

Figure 3.4 Accuracy of the piecewise linear switching current model for 4.8μm/0.6μm pFET

As illustrated in Figure 3.1, the averaged power dissipation is computed from the sum of the switching current of every pFET connected to the power supply. Figure 3.5 illustrates the sign convention for the zero-order quasi-static switching current component into the transistors. The first-order channel capacitive currents into the transistor(s) connected to the power supply are evaluated separately by the channel storage charge model presented in the following section.

Figure 3.5 Sign convention for zero-order switching in transistors

# 3.1.2 Channel Storage Charge Model

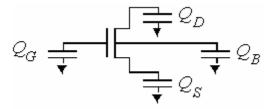

Besides the zero-order quasi-static switching current in the transistor channel, channel currents also contain a first-order channel capacitive current, which come from the channel charge stored in the nonlinear parasitic capacitances. Channel capacitive currents are denoted as  $i_D$ ,  $i_S$ ,  $i_G$ , and  $i_B$  in order to differentiate from the zero-order quasi-static switching current for  $I_D$ ,  $I_S$ ,  $I_G$ , and  $I_B$ . Most transistor models [4] [5] [7] [26] are

not energy conserving due to the neglect of the first-order channel capacitive currents when calculating power consumption [37], and therefore, parasitic capacitances of the transistor are treated as normal capacitors, which do not dissipate power. Particularly, a SPICE simulator assumes that parasitic capacitors are normal capacitors in nature and do not include them in a power calculation [3]. In order to correct the problem by including the nonlinear channel capacitive currents in a power calculation, the channel storage charge is partitioned as seen in Figure 3.6 between the source and drain to obtain a simple lumped parameter model for the dynamic behavior of the transistor. Charge conservation requires that the total channel charge to be conserved, such that

Figure 3.6 Channel storage charge model

$$Q_{G} = -(Q_{S} + Q_{D} + Q_{B})$$

(3.8)

It should be emphasized that these are not linear capacitances since the charges are functions of all of the transistor terminal voltages. Channel capacitive currents can be written in terms of time derivatives of the channel storage charge on each transistor terminal. It is convenient to use these equations written in terms of the individual terminal voltages  $V_G$ ,  $V_S$ ,  $V_D$ , and  $V_B$ .

$$i_{G} = \frac{dQ_{G}}{dt} = C_{GG} \frac{dV_{G}}{dt} - C_{GS} \frac{dV_{S}}{dt} - C_{GD} \frac{dV_{D}}{dt} - C_{GB} \frac{dV_{B}}{dt}$$

(3.9)

$$i_{S} = \frac{dQ_{S}}{dt} = -C_{SG}\frac{dV_{G}}{dt} + C_{SS}\frac{dV_{S}}{dt} - C_{SD}\frac{dV_{D}}{dt} - C_{SB}\frac{dV_{B}}{dt}$$

(3.10)

$$i_{D} = \frac{dQ_{D}}{dt} = -C_{DG}\frac{dV_{G}}{dt} - C_{DS}\frac{dV_{S}}{dt} + C_{DD}\frac{dV_{D}}{dt} - C_{DB}\frac{dV_{B}}{dt}$$

(3.11)

$$i_B = -(i_G + i_S + i_D)$$

(3.12)

$C_{ij}$  ( $i \neq j$ ) are all non-linear capacitors and functions of the terminal voltages given by

$$C_{ij} = \frac{\partial Q_i}{\partial V_{ij}} \quad i, j = G, D, S, B$$

(3.13)

where

$$C_{GG} = C_{GS} + C_{GD} + C_{GB}$$

(3.14)

$$C_{SS} = C_{SG} + C_{SD} + C_{SB} \tag{3.15}$$

$$C_{DD} = C_{DG} + C_{DS} + C_{DB}$$

(3.16)

The sign convention used for the first-order channel capacitive current (3.10) into the source terminal of transistor(s) connected to the power supply is shown in Figure 3.7.

Figure 3.7 Sign convention for channel capacitive currents in transistors

In digital applications, the substrate terminal is biased at a constant voltage so that the last column in equations (3.9)-(3.11) can be ignored. Integration of the channel capacitive current equations gives the channel charge expressions (3.17)-(3.19), which make the evaluation of channel storage charge convenient for piecewise linear approximations of the first-order channel capacitive currents into each transistor terminal.

$$\Delta Q_{G} = C_{GG} \Delta V_{G} - C_{GS} \Delta V_{S} - C_{GD} \Delta V_{D} - C_{GB} \Delta V_{B}$$

$$(3.17)$$

$$\Delta Q_{S} = -C_{SG}\Delta V_{G} + C_{SS}\Delta V_{S} - C_{SD}\Delta V_{D} - C_{SB}\Delta V_{B}$$

(3.18)

$$\Delta Q_{D} = -C_{DG}\Delta V_{G} - C_{DS}\Delta V_{S} + C_{DD}\Delta V_{D} - C_{DB}\Delta V_{B}$$

(3.19)

The channel storage charge model (3.17)-(3.19) requires linearized capacitances in each linear region of operation in order to evaluate average power dissipated by parasitic capacitors. The following is a piece-wise linear approximation of the BSIM capacitance model.

Ohmic Region:

$$Q_{Gohm} = C_{ox}(V_{GS} - V_T) - (a_S + a_D)C_{ox}V_{DS} + b_{SB}C_{ox}(V_{SB} + V_T - V_{FB})$$

(3.20.1)

$$-Q_{Sohm} = \frac{1}{2}C_{ox}(V_{GS} - V_{T}) - a_{S}C_{ox}V_{DS}$$

(3.20.2)

$$-Q_{Dohm} = \frac{1}{2}C_{ox}(V_{GS} - V_{T}) - a_{D}C_{ox}V_{DS}$$

(3.20.3)

Saturation Region:

$$Q_{Gsat} = b_{GS}C_{ox}(V_{GB} - V_{FB}) + b_{SB}C_{ox}(V_{SB} + V_{T} - V_{FB})$$

(3.21.1)

$$-Q_{Ssat} = (1 - x_{part})b_{GS}C_{ox}(V_{GS} - V_{T})$$

(3.21.2)

$$-Q_{Dsat} = x_{part}b_{GS}C_{ox}(V_{GS} - V_T)$$

(3.21.3)

Cutoff Region:

$$Q_{Goff} = b_{SB}C_{ox}(V_{GB} - V_{FB})$$

(3.22.1)

$$-Q_{Soff} = 0 \tag{3.22.2}$$

$$-Q_{\text{Doff}} = 0 \tag{3.22.3}$$

Using continuity of charge at the ohmic-saturation boundary, we find

$$a_{S} = a(\frac{1}{2} - (1 - x_{part})b_{GS})$$

(3.23)

Similarly,

$$a_{\rm D} = a(\frac{1}{2} - x_{\rm part}b_{\rm GS})$$

(3.24)

Using continuity of charge at the cutoff-saturation boundary, we find

$$Q_{G} = b_{SB}C_{ox}(V_{GB} - V_{FB}) = b_{GS}C_{ox}(V_{GS} - V_{T}) + b_{SB}C_{ox}(V_{SB} + V_{T} - V_{FB})$$

(3.25)

is satisfied when  $V_{GS} = V_T$ , putting the values for  $a_S$  and  $a_D$  back into (3.20) gives

$$Q_{Gohm} = C_{ox}(V_{GS} - V_T) - a(1 - b_{GS})C_{ox}V_{DS} + b_{SB}C_{ox}(V_{SB} + V_T - V_{FB})$$

(3.26.1)

$$-Q_{Sohm} = \frac{1}{2}C_{ox}(V_{GS} - V_{T}) - a(\frac{1}{2} - (1 - x_{part})b_{GS})C_{ox}V_{DS}$$

(3.26.2)

$$-Q_{Dohm} = \frac{1}{2}C_{ox}(V_{GS} - V_T) - a(\frac{1}{2} - x_{part}b_{GS})C_{ox}V_{DS}$$

(3.26.3)

The charge storage currents are:

$$i_{Goff} = \frac{dQ_{Goff}}{dt} = b_{SB}C_{ox}\frac{dV_{G}}{dt}$$

(3.27.1)

$$i_{Gohm} = C_{ox} \left[ \frac{dV_G}{dt} - (1 - b_{SB} - a(1 - b_{SB})) \frac{dV_S}{dt} - a(1 - b_{GS}) \frac{dV_D}{dt} \right]$$

(3.27.2)

$$i_{Sohm} = C_{ox} \left[ -\frac{1}{2} \frac{dV_{G}}{dt} + (\frac{1}{2} - a(\frac{1}{2} - (1 - x_{part})b_{GS})) \frac{dV_{S}}{dt} + a(\frac{1}{2} - (1 - x_{part})b_{GS}) \frac{dV_{D}}{dt} \right]$$

(3.27.3)

$$i_{Dohm} = C_{ox} \left[ -\frac{1}{2} \frac{dV_G}{dt} + (\frac{1}{2} - a(\frac{1}{2} - x_{part}b_{GS})) \frac{dV_S}{dt} + a(\frac{1}{2} - x_{part}b_{GS}) \frac{dV_D}{dt} \right]$$

(3.27.4)

$$i_{Gsat} = b_{GS}C_{ox}\frac{dV_G}{dt} - (b_{GS} - b_{SB})C_{ox}\frac{dV_S}{dt}$$

(3.27.5)

$$i_{Ssat} = C_{ox} \left[ -(1 - x_{part})b_{GS} \frac{dV_G}{dt} + (1 - x_{part})b_{GS} \frac{dV_S}{dt} \right]$$

(3.27.6)

$$i_{Dsat} = C_{ox} \left[ -x_{part} b_{GS} \frac{dV_G}{dt} + x_{part} b_{GS} \frac{dV_S}{dt} \right]$$

(3.27.7)

Comparing the derivatives of (3.27) with (3.9)-(3.12) gives the following linearized results for the transistor capacitances.

Table 1 Linearized Parasitic Transistor Capacitances with Overlap Capacitance

|                 | Cutoff                                                                        | Ohmic                                              | Saturation                                                                           |

|-----------------|-------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------|

| $C_{GG}$        | $\begin{array}{c} b_{SB} C_{OX} + C_{GSO} + \\ C_{GDO} + C_{GBO} \end{array}$ | $C_{OX} + C_{GBO}$                                 | $\begin{array}{c} b_{GS}  C_{OX} +  C_{GSO}  + \\ C_{GDO}  + \! C_{GBO} \end{array}$ |

| $C_{GS}$        | $C_{GSO}$                                                                     | $(1 - b_{SB} - a(1 - b_{GS}))C_{OX} + C_{GSO}$     | $(b_{GS}-b_{SB})C_{OX}+C_{GSO}$                                                      |

| $C_{GD}$        | $C_{GDO}$                                                                     | $(1 - b_{GS})aC_{ox} + C_{GDO}$                    | $C_{\mathrm{GDO}}$                                                                   |

| $C_{SG}$        | $C_{ m GSO}$                                                                  | $(1/2)C_{\rm ox} + C_{\rm GSO}$                    | $\begin{array}{c} (1-x_{part})b_{GS} C_{OX} + \\ C_{GSO} \end{array}$                |

| C <sub>SS</sub> | $C_{GSO}$                                                                     | $(1/2 - a(1/2 - (1-Xpart)b_{GS}))C_{OX} + C_{GSO}$ | $(1 - x_{part})b_{GS} C_{OX} + $ $C_{GSO}$                                           |

| $C_{SD}$        | 0                                                                             | $-a(1/2 - (1 - x_{part}b)b_{GS})C_{OX}$            | 0                                                                                    |

| $C_{DG}$        | $C_{GDO}$                                                                     | $(1/2)C_{ox} + C_{GDO}$                            | $x_{part}b_{GS} C_{OX} + C_{GDO}$                                                    |

| $C_{DS}$        | 0                                                                             | $(-1/2 + a(1/2 - x_{part}b)) C_{ox}$               | $-X_{part}b_{GS}$ $C_{OX}$                                                           |

| $C_{DD}$        | $C_{\mathrm{GDO}}$                                                            | $a(1/2 - X_{part}b_{GS}) C_{OX} + C_{GDO}$         | $C_{\mathrm{GDO}}$                                                                   |

The gate to drain and gate to source overlap capacitances shown in Figure 3.8 are becoming more significant in submicron and deep submicron technologies, therefore gate overlap capacitances are included in the linearized capacitance model in Table 1. The gate to substrate overlap capacitance,  $C_{GBO}$ , is negligible in modern processes but is included for the sake of completeness. The BSIM model for the overlap capacitance is

$$C_{GSO} = WC_{gSO}$$

(3.28)

which must be added to C<sub>GG</sub>, C<sub>GS</sub>, C<sub>SS</sub>, and C<sub>SG</sub> to the previous expression (3.27), so

$$C_{GDO} = WC_{gdo}$$

(3.29)

which must be added to C<sub>GG</sub>, C<sub>GD</sub>, C<sub>DD</sub>, and C<sub>DG</sub> to the previous expression (3.27), so

$$C_{GBO} = 2LC_{gbo}$$

(3.30)

which must be added to  $C_{GG}$  to the previous expression (3.27).

Figure 3.8 Gate overlap capacitances for FETs

With the linearized capacitance model, average power supply current into the parasitic capacitances can be evaluated by integrating the first-order channel capacitive currents into the transistor(s) connected to the power supply, which is usually the transistor source current(s). From the linearized capacitance model, it is essential to understand that the linearized capacitances are valid only within each piecewise linear region while the first-order channel capacitive current into the source node of the transistors is computed. Therefore, the initial and final terminal voltages in each piecewise linear region, associated with the transistor(s) connected to the power supply, must be computed before the average power dissipation can be evaluated. Approximate solutions for circuit dynamics has been used very successfully in predicting instantaneous

voltage waveforms [36], and the approximate solution for circuit voltage is extended beyond the gate delay predictions to compute the average power dissipated from the power supply with the piecewise linear switching current–voltage (I-V) model and capacitance–voltage (C-V) model.

#### 3.2 Ramp Input Approximation

Rather than attempt an arbitrary input, the piecewise linear model assumes the input signal is a simple ramp with finite transition time as show in Figure 3.9.

$$V_{in}(t) = \begin{cases} V_{in}(t_{in0}) & t < t_{in0} \\ V_{in}(t_{in0}) + \dot{V}_{in}(t - t_{in0}) & t_{in0} < t < t_{in0} + t_{Tin} \\ V_{in}(t_{Tin}) & t > t_{in0} + t_{Tin} \end{cases}$$

(3.31)

where the slope of a ramp input is

$$\dot{V}_{in} = \frac{V_{in}(t_{in0} + t_{Tin}) - V_{in}(t_{in0})}{t_{Tin}}$$

(3.32)

Figure 3.9 Input ramp approximations

Under Veendrick's assumption, the short-circuit power is proportional to the input rise and fall times and the load capacitance. Hence, it is essential to approximate the input

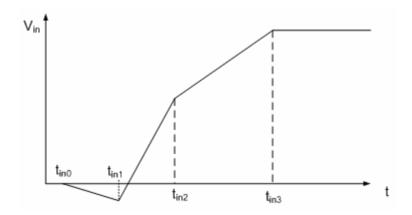

signal with a ramp approximation to evaluate short-circuit current induced power dissipation. Also, the simple ramp approximation includes the short-circuit current into the gate delay evaluation, which is essential to predict rise and fall time at any capacitive node [19] [36]. For a more general input approximation than the input expression of (3.31), the input to each resistance connected region is approximated as a series of piecewise linear segments as shown in Figure 3.10.

Figure 3.10 Piecewise linear approximation of input ramps in resistance connected regions

$$V_{in}(t) \approx \begin{cases} V_{in}(t_{in_0}) & t < t_{in_0} \\ V_{in}(t_{in_k}) + \frac{V_{in}(t_{in_{k+1}}) - V_{in}(t_{in_k})}{t_{in_{k+1}} - t_{in_k}} (t - t_{in_k}) & t_{in_k} < t < t_{in_k} + t_{in_{k+1}} \\ V_{in}(t_{in_k max}) & t > t_{in_k max} \end{cases}$$

(3.33)

$V_{in}(t_{in_k})$  is determined by approximating the input waveform at a finite number of times,  $t_{in_k}$ . The accuracy of the approximation increases with the number of time points. However, adding time points increases the amount of calculation necessary to

determine the voltages in the resistance connected region. First, we will find the approximate solution for circuit voltage with a ramp input (3.31).

## 3.3 Approximate Solution for Circuit Voltage

#### 3.3.1 Resistive Connected Regions

A resistive connected region is defined as a set of circuit nodes connected by paths through the source or drain terminals of transistors in the ohmic region of operation. A resistive connected region can be described with a conductance matrix,  $\mathbf{G}$ , when the zero-order switching current is calculated.  $\mathbf{G}$  is a matrix for a resistive connected region and should not be confused with trans-conductance  $G_m$  for the m-th transistor. When the m-th transistor is in saturation, it is modeled as gate voltage controlled current source between the drain and source and has the effect of decoupling source and drain into separate resistive connected regions [36].

The steady state solution of circuit voltage in delay modeling encompasses non-singular **G** and singular **G** cases [36]. However, solving for the steady state solution of circuit voltage when the **G** matrix is singular can be avoided in computing average power dissipation, because the power supply current into the transistor(s) in saturation is determined by gate controlled current source, which is independent of drain-source bias. Thus, the approximate solution for circuit voltage at each drain node is considered only with a non-singular **G** matrix only for average power estimate.

Instead of solving for all circuit node voltages at once, the complexity of the circuit is reduced by approximating the solution in each resistive connected region connected to the power supply.

# 3.3.2 Approximate Solution for Circuit Voltage with Non-Singular G Matrix

It is assumed that the circuit of interest consists of transistors and capacitors only. The m-th transistor is connected to circuit nodes  $S_m$ ,  $G_m$ , and  $D_m$ , and the c-th capacitor is connected to nodes  $A_C$  and  $B_C$  as shown in Figure 3.11.

Figure 3.11 Notation for transistor number "m" and circuit node names

Large CMOS circuits can be partitioned into many resistively connected groups of nodes. Using the ramp approximation from equation (3.31) for the input nodes, the circuit dynamic equation can be generalized regardless of circuit topologies [36].

$$\mathbf{C}\frac{dV}{dt} + C_{in}\dot{V}_{in} + \mathbf{G}V + G_{in}(V_{in}(t_0) + \dot{V}_{in}(t - t_0)) + G_{Tn}V_{Tn} + G_{Tp}V_{Tp} + G_{dd}V_{dd} = 0$$

(3.34)

where  ${\bf G}$  and  ${\bf C}$  in bold letters represent two-dimensional matrices and  $C_{in}$ ,  $G_{in}$ ,  $G_{Tn}$ ,  $G_{Tp}$ , and  $G_{dd}$  are column vectors. It helps to simplify the circuit dynamic equation if the column vectors  $I_{in}(t_0)$  and  $\dot{I}_{in}$  are defined as

$$I_{in}(t_0) = C_{in}\dot{V}_{in} + G_{in}V_{in}(t_0) + G_{Tn}V_{Tn} + G_{Tp}V_{Tp} + G_{dd}V_{dd}$$

(3.35)

$$\dot{\mathbf{I}}_{in} = \mathbf{G}_{in} \dot{\mathbf{V}}_{in} \tag{3.36}$$

The circuit dynamic equation (3.34) can be re-written as

$$C\frac{dV}{dt} + GV + I_{in}(t_0) + \dot{I}_{in}(t - t_0) = 0$$

(3.37)

where the G matrix is now the on-diagonal sub-block for a single resistance connected region and the C matrix is rectangular in general, and includes capacitive coupling from nodes inside the resistance connected to all other circuit nodes including those inside and outside the resistance connected region [36]. The steady state solution,  $\tilde{V}$ , after the exponential components die out has the form of equation (3.38).

$$\tilde{V}(t) = \tilde{V}(t_0) + \dot{\tilde{V}}(t - t_0) + \ddot{\tilde{V}}\frac{(t - t_0)^2}{2}$$

(3.38)

The steady state solution for a general circuit must satisfy the dynamic equation which can be written as

$$\mathbf{G}\tilde{\mathbf{V}} = -\left[\mathbf{C}\frac{\mathrm{d}\tilde{\mathbf{V}}}{\mathrm{d}t} + \dot{\mathbf{I}}_{\mathrm{in}} + \mathbf{I}_{\mathrm{in}}(\mathbf{t}_{0})\right]$$

(3.39)

Collecting terms of the same power of t, which leads to

$$\ddot{\mathbf{G}}\ddot{\mathbf{V}} = \mathbf{0} \tag{3.40}$$

$$\mathbf{G}\dot{\tilde{\mathbf{V}}} = -(\mathbf{C}\ddot{\tilde{\mathbf{V}}} + \dot{\mathbf{I}}_{in}) \tag{3.41}$$

$$\mathbf{G}\tilde{\mathbf{V}}(\mathbf{t}_0) = -(\mathbf{C}\dot{\tilde{\mathbf{V}}} + \mathbf{I}_{in}(\mathbf{t}_0)) \tag{3.42}$$