# MODELING, ANALYSIS AND DESIGN OF RELIABLE DIGITAL IMAGING SYSTEM

By

#### BYOUNGJAE JIN

Bachelor of Science in Electrical Engineering HanYang University Seoul, Korea 1992

Master of Science in Electrical Engineering HanYang University Seoul, Korea 1994

> Submitted to the Faculty of the Graduate College of Oklahoma State University in partial fulfillment of the requirements for the Degree of DOCTOR OF PHILOSOPHY July, 2007

COPYRIGHT © By BYOUNGJAE JIN July, 2007

# MODELING, ANALYSIS AND DESIGN OF RELIABLE DIGITAL IMAGING SYSTEM

Dissertation Approved:

Dr. Nohpill Park

Dissertation Advisor

Dr. K. M. George

Dr. Venkatesh Sarangan

Dr. Guoliang Fan

Dr. A. Gordon Emslie

Dean of the Graduate College

#### ACKNOWLEDGMENTS

I would like to acknowledge many people for helping me during my doctoral work. I would especially like to thank my advisor, Dr. Nohpill Park, for his generous time and commitment. Throughout my doctoral work he encouraged me to develop independent thinking and research skills. He continually stimulated my analytical thinking and greatly assisted me with scientific writing.

I am also very grateful for having an exceptional doctoral committee and wish to thank Dr. K.M. George, Dr. V. Sarangan and Dr. G. Fan for their continual support and encouragement.

Finally, I'd like to thank my family. My father gave me his true love and endless trust. I hope he could live to see his grandson's college admission ceremony. My mother was a constant source of support. I thank my sisters for their encouragement and enthusiasm. I would like to give my special thanks to parents-in-law and sistersin-law. I'm especially grateful to my wife Bongran and my beloved son Luke(2) for their patience and for helping me keep my life in proper perspective and balance.

### TABLE OF CONTENTS

| Cł       | Chapter Page                    |                                                 |    |

|----------|---------------------------------|-------------------------------------------------|----|

| 1        | INTRODUCTION                    |                                                 | 1  |

| <b>2</b> | CCD Yield Model and Soft-Repair |                                                 | 7  |

|          | 2.1                             | Introduction                                    | 7  |

|          | 2.2                             | Review and Preliminaries                        | 11 |

|          | 2.3                             | The Proposed Soft-Test/Repair Process           | 14 |

|          | 2.4                             | Parametric Analysis                             | 23 |

|          | 2.5                             | Discussion and Conclusions                      | 29 |

| 3        | CC                              | D Clustered fault                               | 31 |

|          | 3.1                             | Introduction                                    | 31 |

|          | 3.2                             | Review and Preliminaries                        | 34 |

|          | 3.3                             | The Proposed Soft-Test/Repair Model             | 37 |

|          | 3.4                             | Parametric Simulation                           | 46 |

|          | 3.5                             | Discussion and Conclusions                      | 48 |

| 4        | BIS                             | T/BISR Design for the Proposed Soft-Test/Repair | 51 |

|          | 4.1                             | Design of the Proposed Soft-Testing Circuitry   | 52 |

|          |                                 | 4.1.1 Proposed BIST for the Soft-Testing        | 53 |

|          |                                 | 4.1.2 Proposed Base Testing Algorithm           | 59 |

|          |                                 | 4.1.3 Proposed Various Testing Algorithms       | 61 |

|          |                                 | 4.1.4 Performance Analysis                      | 66 |

|          | 4.2                             | Scanning Sequence Analysis                      | 71 |

| Bl | BLI  | OGRAPHY                                      | 115 |

|----|------|----------------------------------------------|-----|

| 5  | Disc | cussion and Conclusions                      | 112 |

|    | 4.8  | Discussion                                   | 111 |

|    | 4.7  | Real Image Simulations                       | 100 |

|    | 4.6  | Reliability                                  | 98  |

|    | 4.5  | Parametric Simulations                       | 92  |

|    |      | 4.4.2 Proposed Base Repair Algorithm         | 86  |

|    |      | 4.4.1 Proposed BISR for Soft-Repair          | 85  |

|    | 4.4  | Design of the Proposed Soft-Repair Circuitry | 84  |

|    | 4.3  | Input Image Analysis                         | 79  |

## LIST OF TABLES

| Table |                                             | Page    |

|-------|---------------------------------------------|---------|

| 4.1   | Peak Signal-To-Noise Ratio (PSNR) of Images | <br>101 |

### LIST OF FIGURES

| Figure |                                                         | Page |

|--------|---------------------------------------------------------|------|

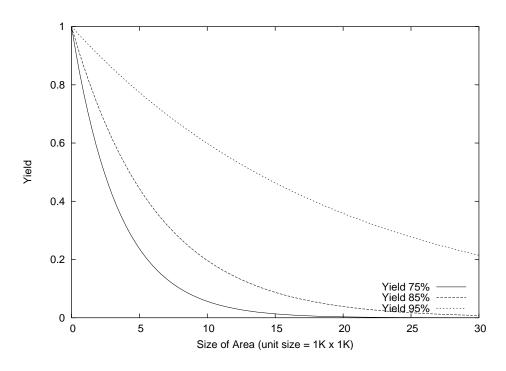

| 1.1    | Yield by N times area                                   | 2    |

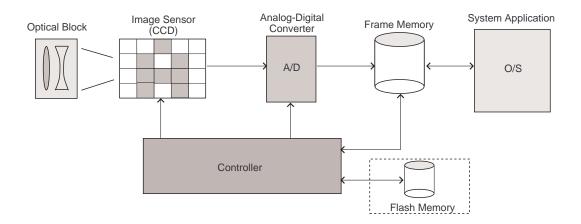

| 2.1    | Block Diagram of Digital X-ray CCD System               | 11   |

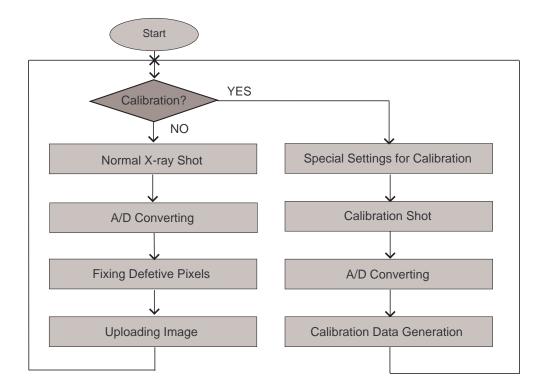

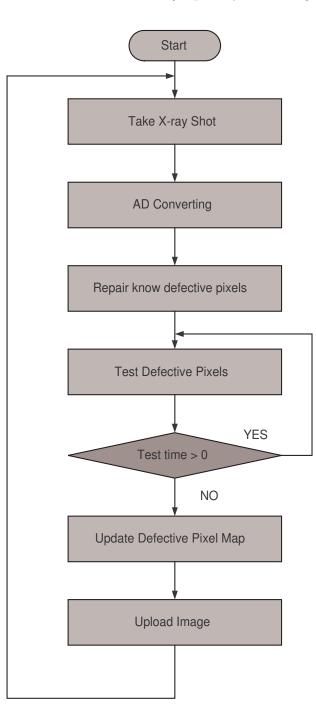

| 2.2    | Flow Chart of the Calibration CCD System                | 15   |

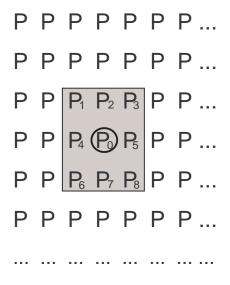

| 2.3    | an example of $3 \times 3$ Filter                       | 16   |

| 2.4    | Flow Chart of Proposed the Caching CCD System           | 17   |

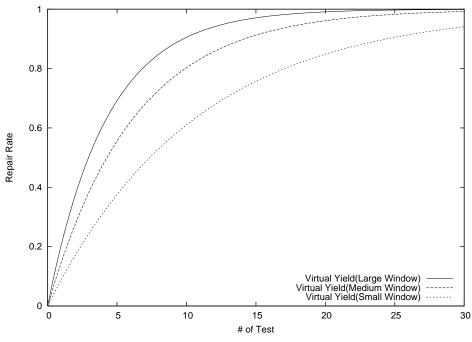

| 2.5    | Repair Rate (Hard-Yield 90%)                            | 26   |

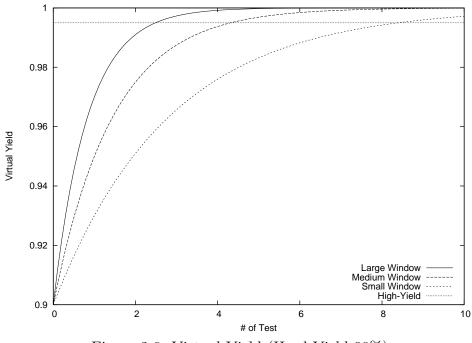

| 2.6    | Virtual Yield (Hard-Yield 90%)                          | 26   |

| 2.7    | Repair Rate (Hard-Yield 93%)                            | 27   |

| 2.8    | Virtual Yield (Hard-Yield 93%)                          | 27   |

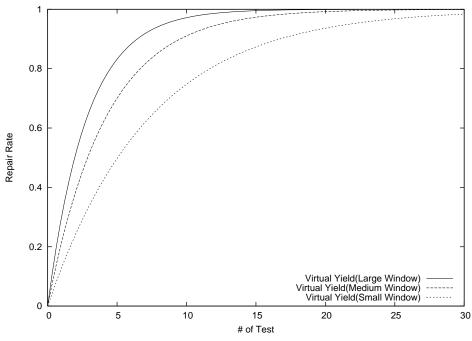

| 2.9    | Repair Rate (Hard-Yield 97%)                            | 28   |

| 2.10   | Virtual Yield (Hard-Yield 97%) $\ldots$                 | 28   |

| 3.1    | Block Diagram of CCD System                             | 34   |

| 3.2    | Electron (Potential) Well                               | 37   |

| 3.3    | State Diagram of CCD                                    | 37   |

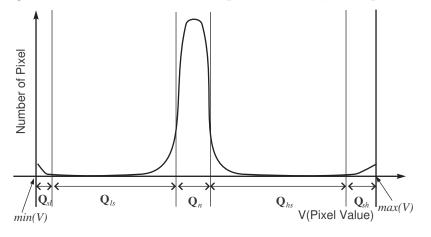

| 3.4    | Distribution of CCD pixel values; $Q_{sh}$ is separated | 41   |

| 3.5    | Distribution of CCD pixel values; $Q_{sl}$ is separated | 41   |

| 3.6    | Distribution of CCD pixel values; all combined.         | 41   |

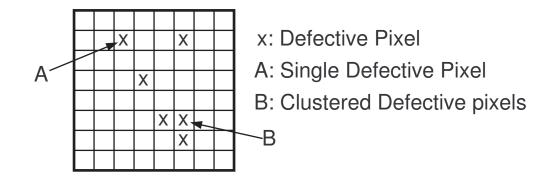

| 3.7    | Clustered Fault Pixels and Single Fault Pixels          | 42   |

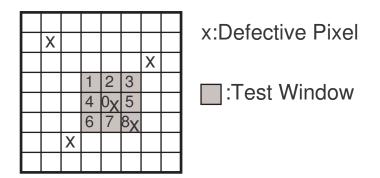

| 3.8    | Repairing of Clustered Fault                            | 44   |

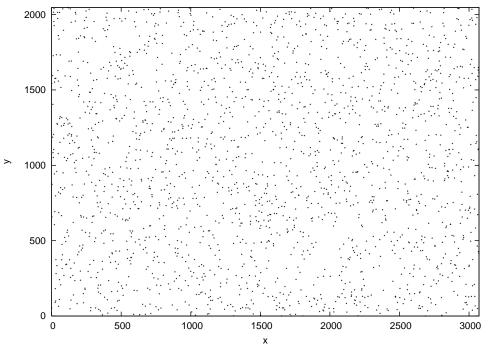

| 3.9    | Defective Pixel Map                                     | 49   |

| 3.10   | Repair Rate                                             | 49   |

| 3.11 | Virtual Yield                                                      | 50 |

|------|--------------------------------------------------------------------|----|

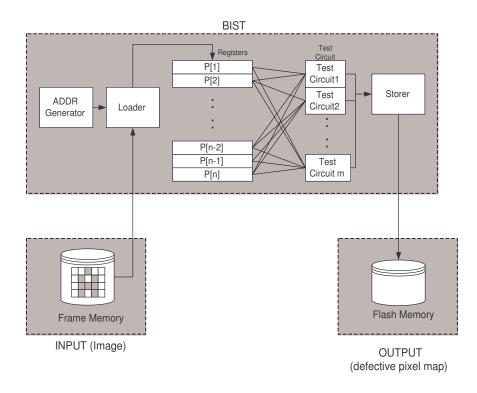

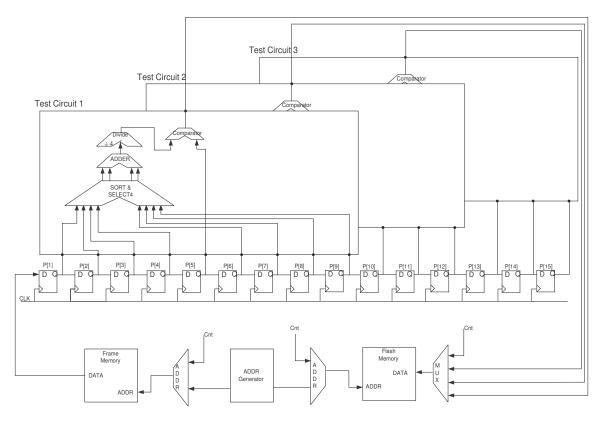

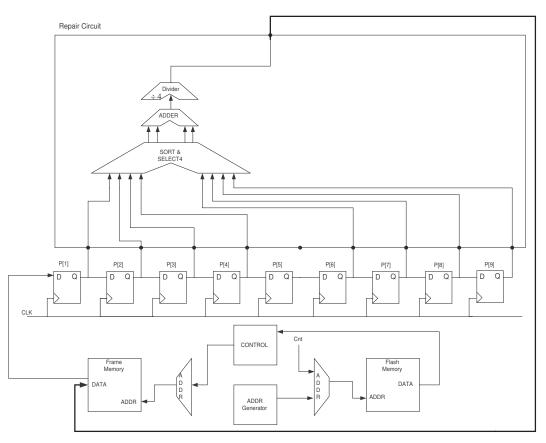

| 4.1  | BIST/BISR Architecture                                             | 55 |

| 4.2  | The proposed architecture for the soft-testing                     | 56 |

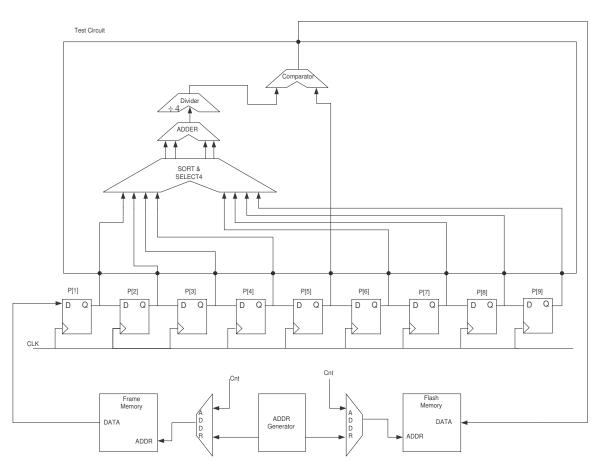

| 4.3  | The proposed BIST circuit                                          | 58 |

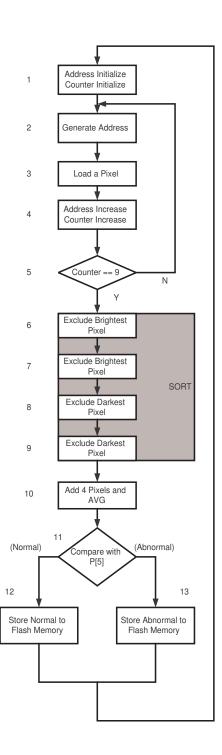

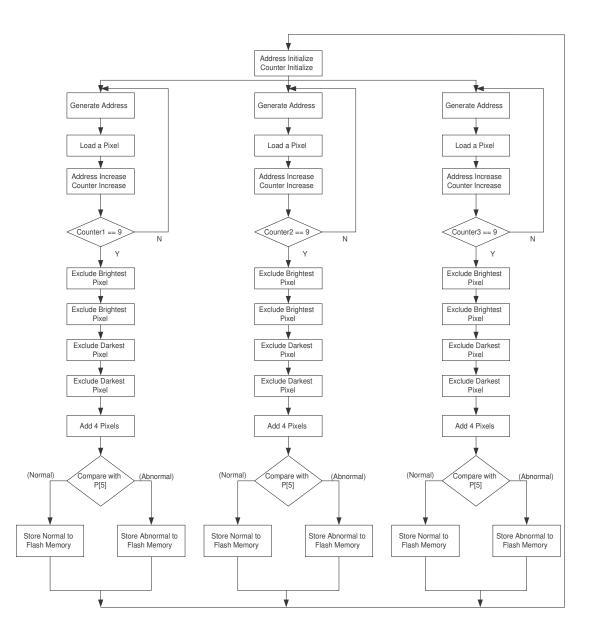

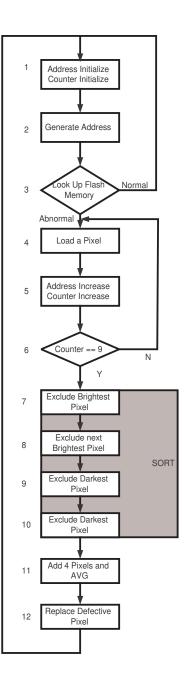

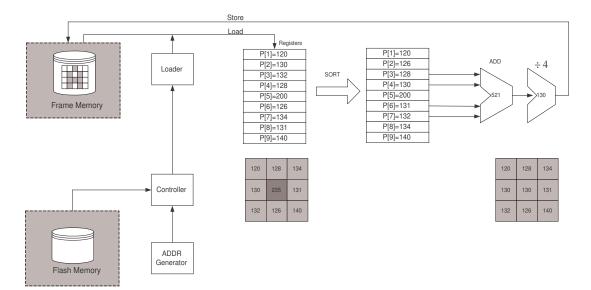

| 4.4  | The soft-testing flow in the proposed testing circuitry            | 62 |

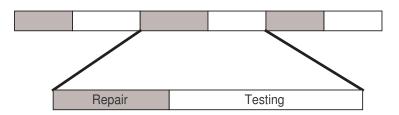

| 4.5  | Sequence of combined soft-testing/repair cycles                    | 63 |

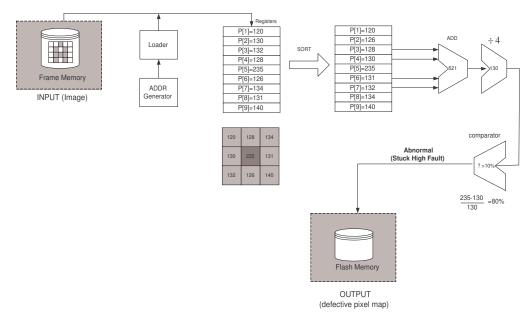

| 4.6  | Detection of stuck high defective pixel                            | 64 |

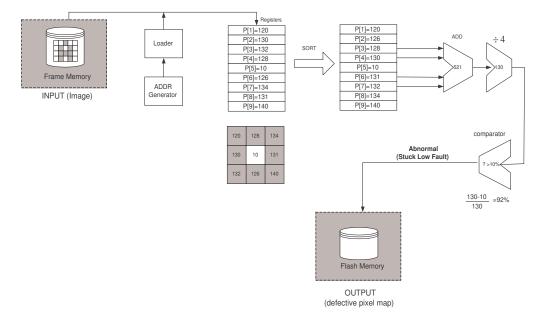

| 4.7  | Detection of stuck low defective pixel                             | 64 |

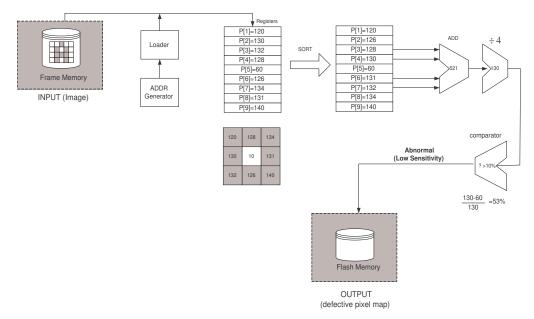

| 4.8  | Detection of Low Sensitive pixel                                   | 65 |

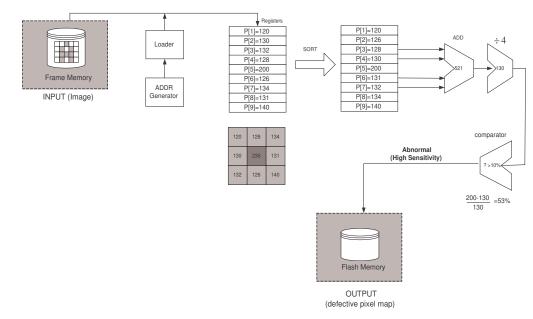

| 4.9  | Detection of High Sensitive pixel                                  | 65 |

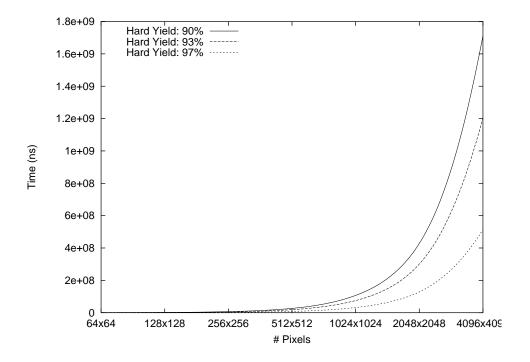

| 4.10 | Testing Time of pixels by Test Circuits                            | 67 |

| 4.11 | The proposed BIST circuit (3 Test Circuit)                         | 68 |

| 4.12 | BIST 3 Test Circuit Flow Chart                                     | 69 |

| 4.13 | Pixel Loading Sequence (3 Test Circuits)                           | 70 |

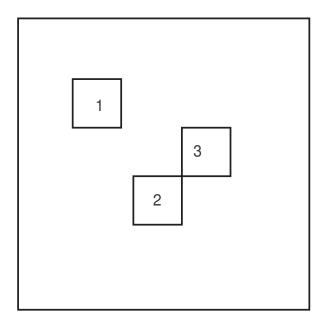

| 4.14 | Coarse Random Scanning Sequence                                    | 73 |

| 4.15 | Medium Random Scanning Sequence                                    | 73 |

| 4.16 | Fine Random Scanning Sequence                                      | 74 |

| 4.17 | Round Robbin Scanning Sequence                                     | 74 |

| 4.18 | Random Avoidance Scanning Sequence                                 | 75 |

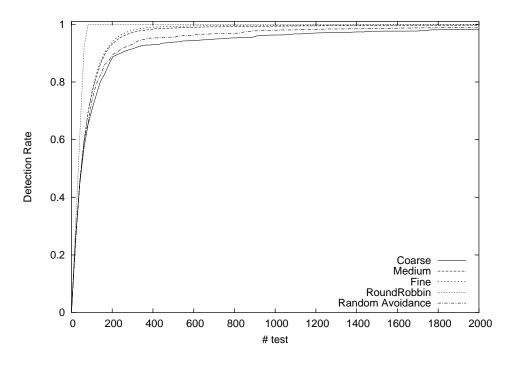

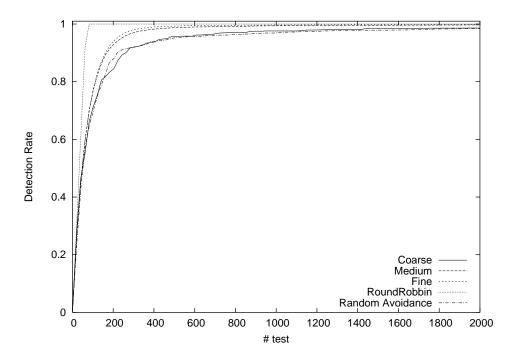

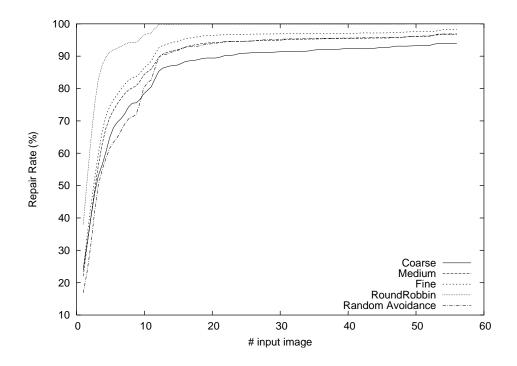

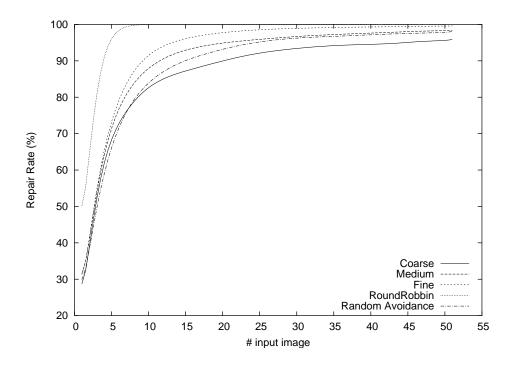

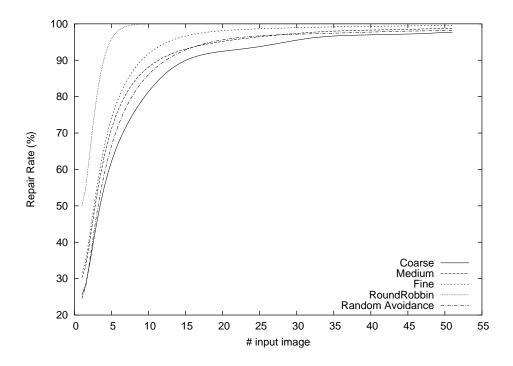

| 4.19 | Scanning Sequence (Hard Yield 90%, $4K \times 4K$ )                | 75 |

| 4.20 | Scanning Sequence (Hard Yield 93%, $4K \times 4K$ )                | 76 |

| 4.21 | Scanning Sequence (Hard Yield 97%, $4K \times 4K$ )                | 76 |

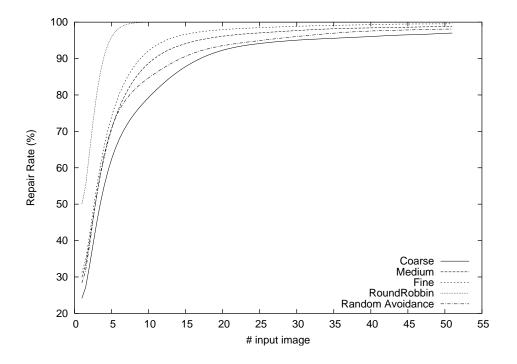

| 4.22 | Scanning Sequence by Real Image (Hard Yield 90%, $4K\times 4K)$    | 77 |

| 4.23 | Scanning Sequence by Real Image (Hard Yield 93%, $4K\times 4K)$    | 77 |

| 4.24 | Scanning Sequence by Real Image (Hard Yield 97%, $4K\times 4K)$    | 78 |

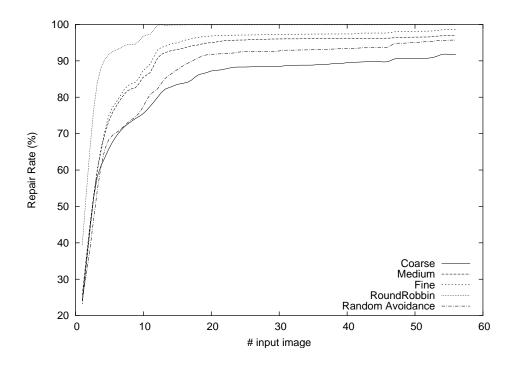

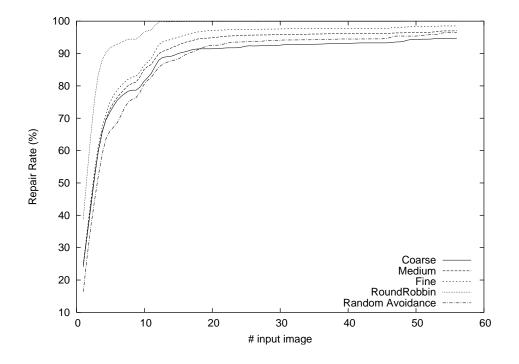

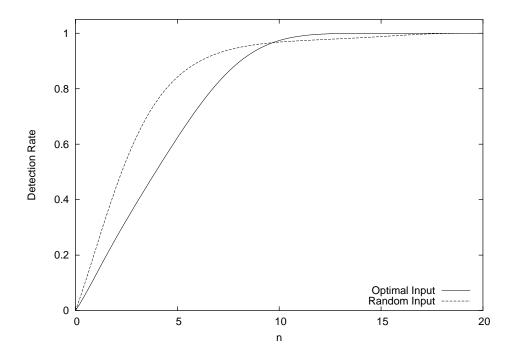

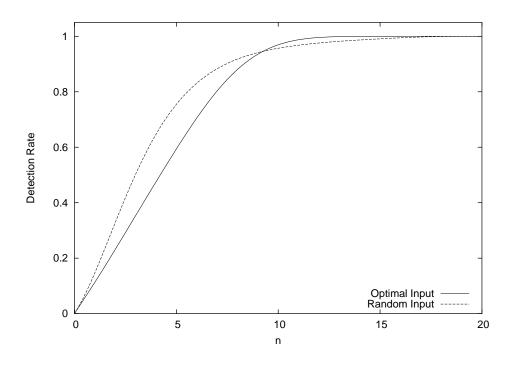

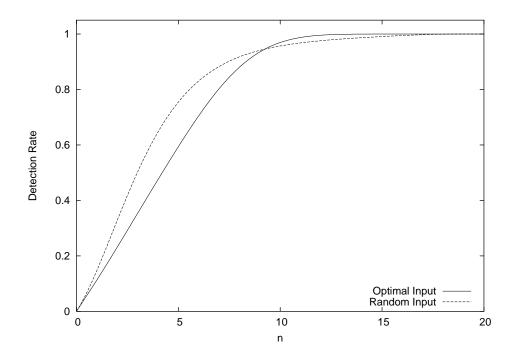

| 4.25 | Optimal Input and Random Input (Hard Yield 90%, $1K\times 1K)$ $~$ | 80 |

| 4.26 | Optimal Input and Random Input (Hard Yield 93%, $1K\times 1K)$     | 81 |

| 4.27 Optimal Input and Random Input (Hard Yield 97%, $1K\times 1K)$ | 81  |

|---------------------------------------------------------------------|-----|

| 4.28 Optimal Input and Random Input (Hard Yield 90%, $1K\times 1K)$ | 82  |

| 4.29 Optimal Input and Random Input (Hard Yield 93%, $1K\times 1K)$ | 82  |

| 4.30 Optimal Input and Random Input (Hard Yield 97%, $1K\times 1K)$ | 83  |

| 4.31 The proposed architecture for the soft-repair                  | 86  |

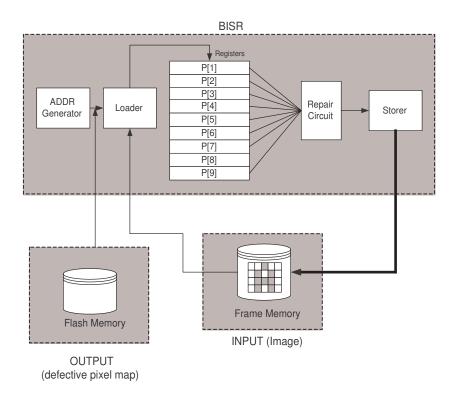

| 4.32 BISR Architecture                                              | 87  |

| 4.33 BISR Flow Chart                                                | 90  |

| 4.34 Repair of defective pixel                                      | 91  |

| 4.35 Repair Time by Number of defective pixels                      | 91  |

| 4.36 Test and Repair (Single Test Circuit and Hard Yield=90%)       | 93  |

| 4.37 Test and Repair (Single Test Circuit and Hard Yield=93%)       | 94  |

| 4.38 Test and Repair (Single Test Circuit and Hard Yield=97%)       | 94  |

| 4.39 Test and Repair (3 Test Circuit and Hard Yield=90%) $\ldots$   | 95  |

| 4.40 Test and Repair (3 Test Circuit and Hard Yield=93%) $\ldots$   | 95  |

| 4.41 Test and Repair (3 Test Circuit and Hard Yield=97%) $\ldots$   | 96  |

| 4.42 Test and Repair (5 Test Circuit and Hard Yield=90%) $\ldots$   | 96  |

| 4.43 Test and Repair (5 Test Circuit and Hard Yield=93%) $\ldots$   | 97  |

| 4.44 Test and Repair (5 Test Circuit and Hard Yield=97%) $\ldots$   | 97  |

| 4.45 Reliability                                                    | 99  |

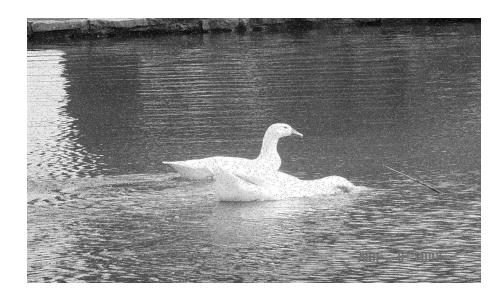

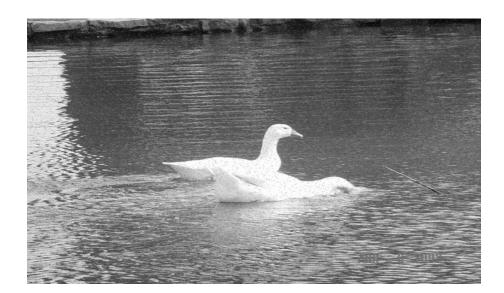

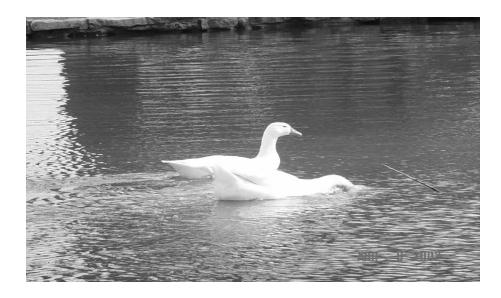

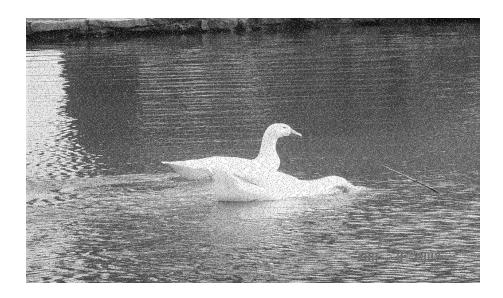

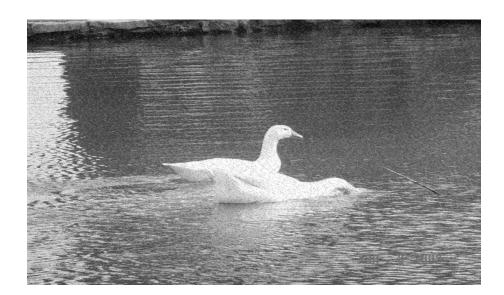

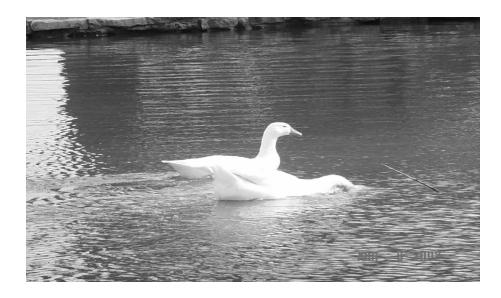

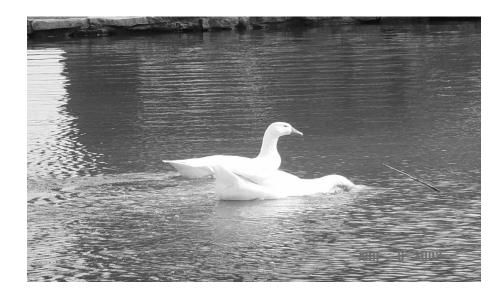

| 4.46 Faulty Image (H.Yield = $97\%$ )                               | 103 |

| 4.47 Image repaired by average filter (H.Yield = $97\%$ )           | 103 |

| 4.48 Image repaired by median filter (H.Yield = $97\%$ )            | 104 |

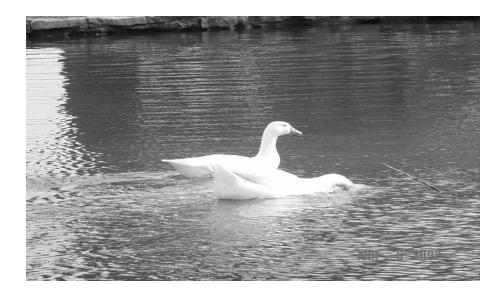

| 4.49 Image repaired by proposed algorithm (H.Yield = $97\%$ )       | 104 |

| 4.50 Faulty Image (H.Yield = $93\%$ )                               | 105 |

| 4.51 Image repaired by average filter (H.Yield = $93\%$ )           | 105 |

| 4.52 Image repaired by median filter (H.Yield = $93\%$ )            | 106 |

| 4.53 Image repaired by proposed algorithm (H.Yield = $93\%$ )       | 106 |

|                                                                     |     |

| 4.54 | Faulty Image (H.Yield = $85\%$ )                         | 107 |

|------|----------------------------------------------------------|-----|

| 4.55 | Image repaired by average filter (H.Yield = $85\%$ )     | 107 |

| 4.56 | Image repaired by median filter (H.Yield = $85\%$ )      | 108 |

| 4.57 | Image repaired by proposed algorithm (H.Yield = $85\%$ ) | 108 |

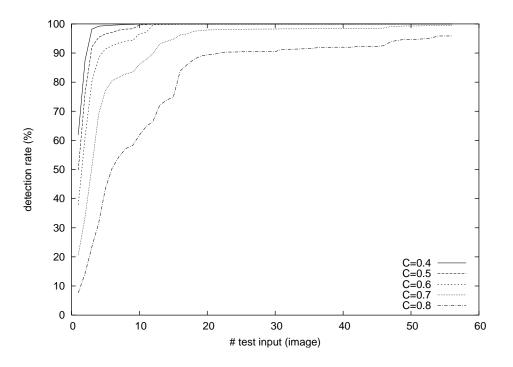

| 4.58 | Detection Rate by C=0.4, $0.5, 0.6, 0.7, 0.8$            | 109 |

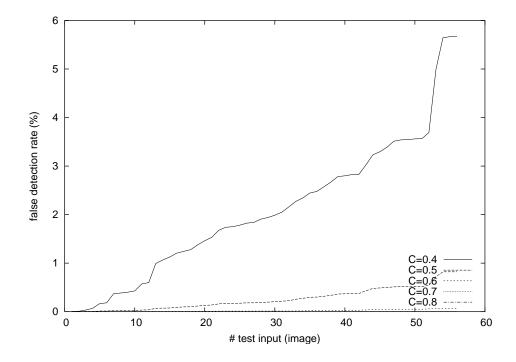

| 4.59 | False Detection Rate by C= $0.4, 0.5, 0.6, 0.7, 0.8$     | 109 |

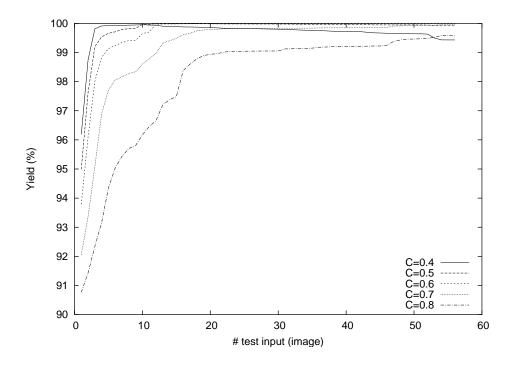

| 4.60 | Yield of False Detection by C= $0.4, 0.5, 0.6, 0.7, 0.8$ | 110 |

#### CHAPTER 1

#### INTRODUCTION

Digital imaging systems have replaced film-based photographic systems in most scientific or commercial application areas such as digital x-ray systems, electronic microscopes, space telescopes, military vision systems, and digital cameras. The digital camera has prevailed in the current market over the film based camera.

As the need for higher resolution and more sensitive Image Sensors grows, high yield and solid reliability are becoming stringent requirements for Image Sensors. In this context, the soft-test/repair method is proposed in this dissertation in order to achieve a high yield and reliability for Image Sensors[1][2][3][7][11][12].

Emerging as stringent requirements increases in chip size and number of pixels as well as decreases in noise level and manufacturing costs are works of modern semiconductor technology.

Charge Coupled Devices (CCD) are widely used in scientific, medical or special purpose imaging systems due to the high dynamic ranges, high quantum efficiencies, low dark noise and large sensing areas. Because of the powerful image sensor characteristics (i.e., high performance), CCD is popularly used in high-end image sensing device such as digital cameras, digital camcorders and digital x-ray diagnosis systems.

Recently Active Pixel Sensor (APS) or Complementary-Symmetry Metal Oxide Semiconductor (CMOS) Image Sensors are replacing low-end and consumer products such as digital cameras or cheap camera systems because it is based on CMOS technology that is cost-efficient for mass production.

The quantum efficiency is determined by the physical dimensions of an image

pixel. In order to keep both a pixel size large and an increase the number of pixels, the die should be large. Increased die size lowers the yield of image sensors. This is the dilemma of high-end imaging systems such as digital x-ray systems or scientific aerospace telescopes.

The yield of an image sensor by size is given as follows [33]:

$$Y_N = Y_{SA}^N \tag{1.1}$$

where Y means yield and  $Y_N$  is expected yield for N times larger than small area  $Y_{SA}(1K \times 1K)$ .

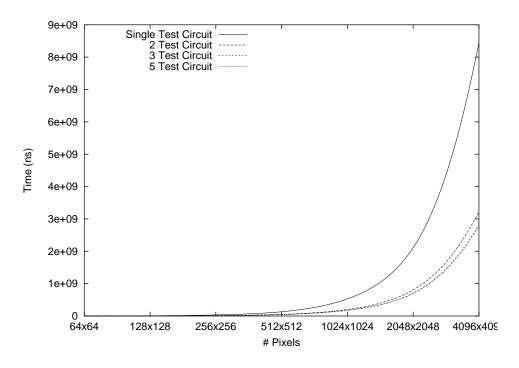

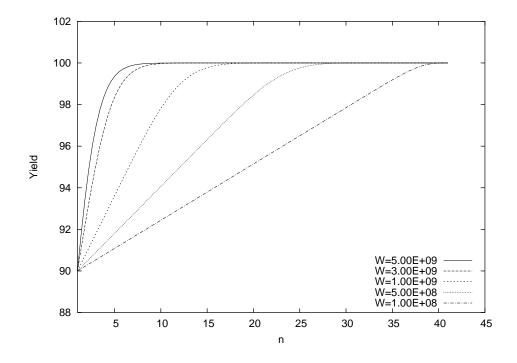

Figure 1.1: Yield by N times area

Figure (1.1) could be drawn from the Equation (1.1). If the size of image sensor is 16 times of  $Y_{SA}$  (i.e.,  $Y_N = 4K \times 4K$ ), then the anticipated yield from the graph is less than 10% (when  $Y_{SA} = 85\%$ ), and the yield is not affordable for mass production. In other words, the manufacturers can fabricate  $1K \times 1K$  image sensors in adequate yield (i.e. above 85%), however, it is hard to get a high yield for large size image sensors such as  $4K \times 4K$  image sensors without reducing the pixel size. • Soft-test/repair in CCD based Digital X-ray system

Modern x-ray imaging systems are evolving toward digitization for reduced cost, faster time-to-diagnosis and improved diagnostic confidence. For digital x-ray systems, CCD technology is commonly used to detect and digitize optical x-ray images. This work presents a novel soft-test/repair approach to overcome the defective pixel problem in CCD-based digital x-ray systems through theoretical modeling and analysis of the test/repair process. There are two possible solutions to cope with the defective pixel problem in CCD; one is the hard-repair approach and another is the proposed soft-test/repair approach. The hard-repair approach employs a high-yield, expensive CCD to minimize the impact of hard-defects on the CCD., These occur in the form of noise propagated through the A/D converter to frame memory. Therefore, less work is needed to filter and correct the image at the end-user level while it may be exceedingly expensive to practice. On the other hand, the proposed soft-test/repair approach detects defective pixels at the digitized image level; therefore it is inexpensive in practice and on-line repairs can be done for non-interrupted service. It tests the images to detect detective pixels and filter noise at the frame memory level, and it caches them in flash memory in the controller for future repair. The controller cache keeps accumulating all of the noise coordinates, and preprocesses the incoming image data from the A/D converter by repairing them. The proposed soft-test/repair approach is particularly devised to facilitate hardware level implementation ultimately for real-time tele-diagnosis. Parametric simulation results demonstrate the speed and virtual yield enhancement by using the proposed approach. Therefore highly reliable, yet inexpensive soft-test/repair of CCD-based digital x-ray systems can be ultimately realized.

• Clustered faults and repair in CCD

Pixels on a CCD may suffer from defective or faulty pixels due to numerous causes such as imperfect fabrication, excessive exposure to light, radiation and sensing element aging to mention a few. As the use of high-resolution CCDs increases, defects and fault tolerances of such devices demand immediate attention. In this context, this study proposes a testing and repair technique for defects/faults in such devices with inability of on-device fault tolerance, referred to as off-device fault tolerance. Digital image sensor devices such as CCD can, by their nature, not readily utilize traditional on-device fault tolerance techniques because each pixel on the device senses a unique image pixel coordinate. No faulty pixel can be replaced nor repaired by a spare pixel as any displacement of an original pixel coordinate can not sense the original image pixel. Therefore, to effectively provide and enhance the reparability of such devices with inability of on-device fault tolerance, a novel testing and repair method for defects/faults on CCD is proposed based on the *soft testing/repair* method proposed in Chapter 2 under both single and clustered distribution of CCD pixel defects. Due to unwanted diffusion clustered fault models should be considered as a practical models and compared with single fault models. Also, a novel defect/fault propagation model is proposed to effectively capture the on-device defects and faults off of the device for an effectiveness and practicality of testing and repair process. The efficiency and effectiveness of the method is demonstrated with respect to yield enhancement by the soft-testing/repair method under a clustered fault model as well as single fault model, referred to as *soft yield*. Extensive numerical simulations are conducted.

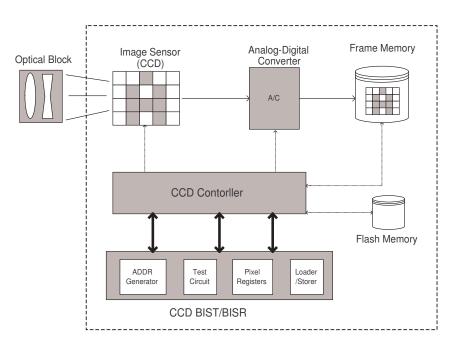

#### • BIST/BISR design for soft-test/repair

Built-in self-test (BIST) is an upcoming testing method that makes a circuit test itself without using expensive ATE. BISTs could have more advantages than ATEs in many aspects such as having a larger test bandwidth, being more suitable for stress testing, and eliminating complicated patterns preparation, and functional testing. Defective pixels of CCD are one of the troublesome problems since no CCDs may be free from them. Moreover, the number of defective pixels could be increased by mechanical and/or electrical shock during the normal operation or operation in harsh conditions such as under radiation. In order to efficiently test and repair the defective pixels in CCDs, BIST/BISR architecture and design is proposed and implemented by the soft-test/repair algorithm. The proposed BIST/BISR is designed without increasing complexity and cost by reusing and sharing existing the functional logics with the CCD controller. As the proposed BIST/BISR operates concurrently with normal CCD operations, overall testing and repair performance are enhanced. Furthermore, BIST employs a parallel testing architecture in order to reduce testing time for bulky data. Verilog HDL simulation is performed in order to validate the design and architecture of BIST/BISR. The efficiency and effectiveness of the proposed BIST/BISR is demonstrated by an enhancement of yield and various simulation results.

The main objective of this work is to propose soft-test and repair methods for defective pixels in imaging sensor system, thereby realizing more reliable and costeffective imaging sensor Systems. The following specific problems will be addressed and resolved.

- Soft-Test/Repair : Soft-Test and Repair techniques for image sensor systems will be proposed to model and evaluate the yield improvement. This technique can be used in both CCD and CMOS image sensors.

- *BIST/BISR Design and Simulation* : Cost efficient and reasonable performance BIST/BISR design and architecture is proposed for imaging sensor system and the performance of the designed BIST/BISR is analyzed through verilog HDL simulation.

• False detection technique is proposed and verified through real image simulations.

The organization of this dissertation is as follows. In Chapter 2, generalized CCD defective pixel models and repair methods are proposed. Theoretical and practical soft-test methods are employed to improve CCD yield and reliability. In Chapter 3, clustered defective pixel model and repairing methods are proposed. It proposes how to test and find clustered defective pixel, and repair methods will be proposed. Then in Chapter 4, a cost efficient BIST/BISR for CCD will be proposed. Unlike conventional BIST, the proposed BIST/BISR concurrently operates with other CCD control circuitry. Finally, the Discussion and Conclusions is presented in the last chapter.

#### CHAPTER 2

#### CCD Yield Model and Soft-Repair

#### 2.1 Introduction

Modern x-ray imaging systems evolve toward digitization for reduced imaging cost and higher diagnostic confidence [2]. To provide faster and efficient processing and manipulation of image data, digitization of image data is emerging as a promising alternative technology over conventional analog data-based image processing technology [3]; examples include digital x-ray-based systems such as flat panel, CR (Computed Radiography), and DR (Digital Radiography). Digital x-ray technology is rapidly replacing conventional film-based x-ray techniques. Today's filmless digital imaging technology is emerging as a standard in medical applications such as telemedicine and *teleradiology*, due to its promising perspectives such as cost-effectiveness, improved lifetime, reliability, and maintainability [4]. For example, military medical systems require convenient, real-time and efficient medical imaging solutions for their stringent mission-critical purposes [4]. Conventional x-ray films require huge amount of storage, which is very sensitive and vulnerable to temperature and humidity, and hazardous chemical processing for x-ray film development, which also may result in toxic environmental contamination. Furthermore, exposure of patients to x-ray is limited to certain angular setups, which further limits the effectiveness of conventional film-based x-ray medical imaging. Therefore, migration to digital x-ray technology is highly desired.

One of the most critical issues in CCD-based imaging system such as digital xray system is how to detect and repair *dark current* (or so-called *black noise*) to assure quality of service [5, 6]. Generally, digital x-ray system operates an electric or mechanical shutter for about 1000 milli-seconds and sometimes even for longer than 1 second. During that time period, the dark current could accumulate in CCD pixels without flushing; the phosphor cannot properly emit enough light so that the corresponding analog signal becomes too weak to sensor. As a result, the black noise can appear on the resulting x-ray image. Therefore, the dark current should be kept as low as possible by cooling or choosing a better quality and more expensive CCD with low dark current characteristics.

Timely x-ray film read/processing is also one of the most critical requirements to provide high quality service. Under certain harsh environments such as geographical isolation and tactical emergency, x-ray films should be remotely sent to radiologist for timely diagnosis. Filmless digital x-ray system can solve this problem by efficiently transmitting digital x-ray image data over the network to radiologist virtually in real time. Hence, filmless digital x-ray systems provide a promising solution especially for processing and delivery of time-sensitive medical cases, still yet a few problems to be resolved such as hardware reliability and slow software level calibration.

Besides the speed factor of x-ray processing, another critical factor is the *reliability* of the image for higher diagnostic confidence. Excessive x-ray exposure possibly damages CCD pixels and make them defective [7, 8]. Hence, it is required for digital x-ray systems to be maintained regularly by using costly and time-consuming software-based image calibration and tuning. Once a defective pixel hit by all means, the pixel creates a salt-and-pepper noise on target image, since it cannot receive and sense any photon; therefore, a noticeable darker noise point than any other image pixels becomes visible [9, 10]. The reliability is determined either by software or hardware factor. In reality, most CCDs suffer from defective pixels; therefore performance degradation is also experienced consequentially [10]. High-yield CCDs with less defects help resolve this problem at excessive cost in conjunction with complex calibration procedure

[11]. The calibration procedure is generally practiced on software level and off-line for detecting/correcting defective pixels and performing optical corrections such as barrel correction. The approach proposed in [10] removes defective pixels on CCD of a digital camera by periodically executing new off-line calibrations to update old calibration results under a new exposure. However, conventional off-line softwarelevel calibration may create an excessive delay on digital x-ray image processing, which may not be acceptable under stringent processing constraints of today's digital x-ray applications [12, 13].

There also have been a few works proposed to build a reliable CCD-based digital signal processing system from hardware's standpoint in [14, 15, 9, 16]. Digital camera uses high resolution color CCD. In [9], it was proposed that defects on color CCD can be detected and repaired such that a defective CCD pixel can be detected by checking which color has been corrupted among the three colors (i.e., red, green and blue) and repair the pixel by replacing with a spare CCD pixel provided. The approaches relying on spare rows and columns of CCD pixels and, hence, are impractical to implement since it imposes additional cost to the already expensive CCDs [16, 9]. In [14, 15], a self correcting hardware design was presented, in which, unlike the global replacement of defective CCD pixels, spare pixels can replace defective or dead pixels located only on locally neighboring rows or columns. Since each CCD pixel is a sensing device with its predetermined image position to receive a photon from, replacement of a CCD pixel with a spare pixel will result in an irrelevant image data reception after all; thus, serious post image reconstruction must be done.

Cost- and performance-effective testing and repair of CCD pixel defects are critical and essential requirements to realize high quality digital x-ray systems. Currently, the capacity of black and white CCD for a digital x-ray has reached larger than 6 mega pixels resulting in geometric increase in processing speed requirement, even with a simple filtering algorithm. For effective and efficient processing of huge amount of digital x-ray image pixel data, digital x-ray systems require ultra-high speed data processing with low noise-rate.

This work has been partially presented in [12, 13].

The main objective of this work is to propose a new cost and performance-effective approach to detect and repair CCD hardware pixel defects by proposing a novel yet effective theoretical model for yield and repair rate. Unlike the legacy hard-repair approaches, the proposed repair approach mainly depends on post-processing of the digitized x-ray image data in a real-time processing environment implemented on a FPGA (Field Programmable Gate Arrays). Performance characteristics of the proposed CCD soft-repair approach and benefits from implementation of the proposed hardware-oriented approach will be also investigated through extensive parametric simulations. Note that the proposed work is not to develop new filtering or calibration algorithms, but to propose a hardware-oriented image quality enhancement approach with respect to speed and hardware reliability-driven quality of service. For implementation purpose, any off-the-shelf image processing algorithms can be employed and realized on hardware level. An ultimate implementation plan would be on single chip-level fabrication (i.e., System-on-chip (SoC)) to utilize the performance benefits of SoC technology. Fast run-time dynamic filtering of digital image data on SoC-level is the ultimate goal of the proposed approach.

This work is organized as follows. In the next section (Section 2.2), previous works are reviewed, and basic principles of the proposed approach are introduced. In Section 2.3, the proposed soft-testing and repair process is evaluated. In Section 2.4, a parametric analysis with respect to CCD yield and soft-repair rate is provided. Conclusions and discussions are presented in Section 2.5.

#### 2.2 Review and Preliminaries

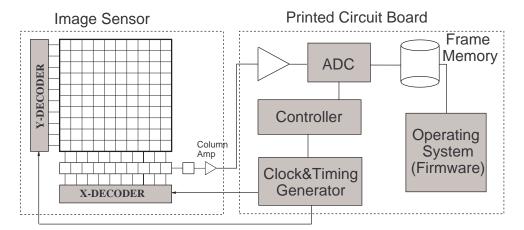

A typical digital x-ray system is shown in Figure (2.1). The optical block captures the light generated by phosphor which emits light when it receives x-ray. The CCD image sensor contains numerous pixels and each of which senses photons using electronic well. CCD converts accumulated photons in the electronic well to a corresponding voltage. Then, an analog amplifier, such as OP-Amp, amplifies the signals before it directs the signals to A/D converter for digitization. Thereafter, the sensed image data is propagated all the way to the frame memory through the A/D converter under the coordination of the controller. The size of the frame memory is determined by the required digital image quality. For example, if a 1 Mega pixel CCD is used, 2M byte RAM is needed for the frame memory when gray-scale color depth of 16 bits is required (i.e.,  $1024 \times 1024 = 1Mpixel$ , each pixel needs 16 bit (2 Byte), therefore 2 M Bytes needs for 1 M pixel).

Figure 2.1: Block Diagram of Digital X-ray CCD System

Unfortunately, CCDs are not free from hardware defects. Imperfect fabrication and improper processing may induce defects (referred to as *hard-defects*) on the photosensitive pixels and supporting system components in CCD. In [15], the main causes of CCD hard-defects are categorized as follows.

- 1. Failure of row/column pixels (either line or readout/control transistors/circuit).

- 2. Failure of row select/reset shift register.

- 3. Failure of column sense amplifiers.

- 4. Failure of A/D converter.

- 5. Failure of buffers.

- 6. Failure of read-out/reset transistors on each photo-diode.

In practice, all the defects of the above mentioned types affect the quality of the raw image data on the frame memory, since the hard-defects that propagated all the way from the CCD to the frame memory through the A/D converter as shown in Figure (2.1). The effect of a hard-defect observed on the frame memory is referred to as *soft-defect*. Notably, a soft-defective pixel on the frame memory usually shows an abnormal value compared to its neighboring pixel values. Without loss of generality, one-on-one correspondence between a hard-defect on the CCD and a soft-defect on the frame memory can be assumed, unless other component failures than CCD failures are taken into account. In this context, it is feasible to test and repair (i.e., soft-testing/repair) CCD hard-defects on soft memory-mapped level in the form of soft-defects on the frame memory. This work only deals with *permanent* CCD hard-defects.

The A/D converter reads analog image data (i.e., voltage) and convert it to corresponding digital values onto the frame memory storage. In reality, CCDs may contain the mega-scale number of pixels, and they may be either bad or defective (e.g. dead) pixels. In safety-, mission-, and deadline-critical applications, defective pixels may result in devastating consequences. However, defective CCD pixels cannot be effectively replaced by using traditional approach which relies on redundant defect-free pixels, because each CCD pixel can sense only the image pixel on its exact and unique physical position. Therefore, reliability and quality enhancement efforts should be practiced on some other level such as A/D converter or frame memory [10]. Once the raw image data is stored in the frame memory, it is more efficient to manipulate the image data in digital form since post data processing techniques such as calibration, filtering and image processing algorithms can be applied. A few image processing algorithms have been proposed for the digitized images with defective pixels. In the proposed soft-repair process of the pixels with soft-test,  $3 \times 3$  average filter (or 3x3mean filter) is considered. A non-volatile flash memory is employed in the proposed approach to cache and cumulate defect locations, referred to as noise history data map. By using the noise history data map stored in the flash memory, the repair process for soft-defect pixels hit on the frame memory can be implemented in a few different ways such as hardware, software, or firmware-level. In the proposed system, SoC-based hardware implementation is considered for the performance benefits of the SoC technology. the proposed approach can be effectively extended[12, 13].

The main idea of the proposed approach is to capture and detect noises (i.e., softdefects) hit on the frame memory in digital x-ray system, which have been propagated all the way from CCD (i.e., hard-defects) through A/D converter to frame memory as shown in Figure (2.1). A run-time writable flash memory is also used to store and keep track of up-to-date and cumulative *noise history data map*, which is used to pre-process incoming image data to enable skipping testing and repairing previously identified noise pixel positions. The proposed soft-testing and repair approach can be performed in a dynamic manner, since the proposed approach dynamically updates the pixel noise map on flash memory cache, while conventional software-level calibration or filtering approaches can be categorized as static. Thus, the dynamic pixel noise map in the flash memory can be constructed in an acceptable amount of execution time referred to as *pixel noise saturation time*. Having the proposed approach implemented on hardware, especially the whole system implemented on a single chip, the critical issues, such as processing speed and yield of CCD as a measure of the reliability of the hardware structure of digital x-ray system as addressed before, can be effectively circumvented. The improvements due to the proposed hardware implemented soft-repair approach is referred to as *virtual CCD yield enhancement* and it can be implemented at a minimal hardware cost of flash memory caching without costly extra calibration procedures.

#### 2.3 The Proposed Soft-Test/Repair Process

#### Notations

| $D_n$              | number of defective pixels at the $n_{th}$ test/repair cycle    |

|--------------------|-----------------------------------------------------------------|

| $D_T$              | total number of soft-defects hit on the frame memory            |

| $F_{sh}$           | number of stuck high pixels                                     |

| $F_{sl}$           | number of stuck low pixels                                      |

| $F_{hs}$           | number of high sensitive pixels                                 |

| $F_{ls}$           | number of low sensitive pixels                                  |

| $F_{fault}$        | number of defective pixels                                      |

| $F_{repair}$       | number of repaired pixels                                       |

| $F_{test}$         | number of tested pixels                                         |

| p                  | insensitivity ratio                                             |

| P(n)               | $n_{th}$ pixel under test and repair                            |

| $r_{defect}$       | decrease ratio of the number of defects after each repair cycle |

| $R_n$              | number of repaired pixels during the $n'th$ repair cycle        |

| $r_{repair}$       | repair ratio                                                    |

| $T_{test}$         | test time                                                       |

| $T_{repair}$       | repair time                                                     |

| $T_{net \ repair}$ | time for repairing a defective pixel                            |

| $W_T$              | window (i.e., time for test and repair)                         |

| $Y_H$              | hard yield                                                      |

#### $Y_V$ virtual yield

A general calibration process in digital x-ray systems considered in this work is shown in Figure (2.2).

Figure 2.2: Flow Chart of the Calibration CCD System

Based on the reference calibration process shown in Figure (2.2), the main characteristics of the proposed soft-repair process are summarized as follows.

- 1. The hard-defects on the pixels on CCD is assumed to follow the Poisson distribution (i.e.,  $e^{-\lambda t}$ ). Note that clustered defects are not considered in this work.

- 2. It is assumed that only CCD contains defective pixels (i.e., dead pixels or hard-defects), and all other components (i.e., the A/D converter, the frame memory and the flash memory) are assumed to be defect-free.

- 3. Without loss of generality, it is also assumed that the defective pixels are prop-

agated from the CCD to the frame memory (i.e., soft-defects) through the A/D converter.

In this work, a simple mean filter as a criterion is used as shown in Figure (2.3).

Figure 2.3: an example of  $3 \times 3$  Filter

The proposed soft-test equation is given as follows.

$$\left|\frac{\sum_{k=1}^{N} P(k)}{N} - P(0)\right| \le C$$

(2.1)

where  $P(1) \cdots P(N)$  are the surrounding pixels of the tested pixel P(0). The constant C is the threshold for determining whether it is defective or not in testing (e.g., 10%). This means the average value and the tested pixel value have almost same value. If Equation (2.1) holds, then the tested pixel is diagnosed as normal, otherwise it is a defective pixel. It indicates that the tested pixel is too bright or too dark compared to its neighboring pixels. Actually, only a defective pixel cannot be too much bright or dark than their neighboring pixels because of the Gaussian effect (i.e., each nine pixel contains each other's shading information).

After testing and repair process completed, the controller updates the noise history data map in the cache (i.e., non-volatile memory such as flash memory or  $E^2$ PROM).

The proposed noise history data map caching technique allows for at-speed repair with minimal overhead as shown in soft-test/repair cycles in Figure (2.4).

Figure 2.4: Flow Chart of Proposed the Caching CCD System

Equation (2.1) may not effectively take into account some defective pixels if they

are adjacent to pixels of similar gray-scale colors. Since different input images are to be stored and processed in the frame memory at each test cycle successively, the defective pixels, in general, can be detected within a certain finite number of test/repair cycles.

There are generally three possible failure modes such as low sensitivity, stuck low, and stuck high [16]. On the frame memory, defective pixels are relatively brighter or darker to result in relatively larger or smaller digitized data words compared to its neighboring pixels, which can be used for testing purpose.

Each pixel on the frame memory can be cached in two bits of flash memory. The states of caching a pixel on the flash memory can be defined as follows.

1. 00 state : stuck low (i.e.,  $F_{sl}$ )

Ex) Photodiode shorted, gate to photodiode path cut, transistor stuck off

2. 01 state : low sensitivity (i.e.,  $F_{ls}$ )

Ex) something covered part on photodiode, leakage in the photodiode, poor transfer characteristic of the transistor, etc

3. 10 state : stuck high (i.e.,  $F_{sh}$ )

Ex) Photodiode always charged because of the malfunction of flushing circuit, transistor stuck on

4. 11 state : high sensitive (i.e.,  $F_{hs}$ )

Ex) bad lens above the part on photodiode, too high gain of the transistor, etc.

The co-relation between each type of defective pixels and the total number of defective pixels, i.e.  $F_{fault}$ , can be defined as follows.

$$F_{fault} = F_{sl} + F_{ls} + F_{sh} + F_{hs} \tag{2.2}$$

The detection approaches and threshold equations for different type of defective pixel can be shown as follows. 1. 00 state: the stuck low pixels can be detected by the following two equations:

$$\left|\frac{\sum_{k=1}^{N} P(k)}{N}\right| \ge C_{011} \tag{2.3}$$

$$P(0) \le C_{012} \tag{2.4}$$

where  $C_{011}$  and  $C_{012}$  are 50% and 10% respectively. This means that the stuck low pixels displays near zero range yet the average value displays more than 50% of the range. The constant value could be changed smaller value for tight detection. Basically, this constant value depends on the characteristic of system. If both Equation (2.3) and (2.4) hold, the pixel can be categorized as a stuck low pixel.

2. 01 and 11 state: low and high sensitive pixels can be detected by the following equation.

$$\left|\frac{\sum_{k=1}^{N} P(k)}{N} - P(0)\right| \ge C \tag{2.5}$$

where C = 10%. 10% means 10% of the maximum digital value converted from A/D converter, (e.g. in case of 16 bit A/D converter, the 10% is 65535/10). This means that a low sensitive pixel displays out of the range of the average value over 10% tolerance. This constant value depends on the characteristic of system. If Equation (2.5) holds, then the pixel can be categorized as a low sensitive pixel.

3. 10 state: the stuck high pixels can be detected by the following equation.

$$\left|\frac{\sum_{k=1}^{N} P(k)}{N}\right| \le C_{101} \tag{2.6}$$

$$P(0) \ge C_{102} \tag{2.7}$$

where the reference  $C_{101}$  and  $C_{102}$  are 50% and 90% respectively. The constant value can be varied from the give value depending on the system and quality level. If both Equation (2.6) and (2.7) hold, then the pixel can be tested as a stuck high pixel.

Stuck low and stuck high pixels (i.e., State 00 and 10) can be repaired by replacing the defective pixel values by using the following equation. Since a defective pixel does not have any repair information, the defective pixel value is to be replaced by the average value of its neighboring pixel values.

$$P(0) = \frac{\sum_{k=1}^{N} P(k)}{N}$$

(2.8)

Note that the repair for a defective pixel defect of the state 01 depends on how much the pixel is insensitive. Thus, the following equation can be used to take into account the insensitivity.

$$P(0) = (1-p) \cdot \frac{\sum_{k=1}^{N} P(k)}{N} + P(0)$$

(2.9)

where p  $(0 \le p \le 1)$  is the insensitivity ratio of the defective pixel under test. The insensitivity ratio p can be defined as following equation.

$$p = \frac{P(0)}{\frac{\sum_{k=1}^{N} P(k)}{N}}$$

where the denominator  $\left(\frac{\sum_{k=1}^{N} P(k)}{N}\right)$  is the reference value.

The proposed CCD soft-testing/repair process scans for the soft-defects on the frame memory for a certain amount of time (i.e., referred to as  $T_{test}$ ). The proposed soft-test/repair process repeats as many times as the total number of pixels within a temporal window of the process (i.e., within time  $T_{test}$  in Equation (2.10)). The pixels on the frame memory detected as soft-defects are repaired, and then the locations are cached and accumulated in the flash memory. The time for each test/repair process cycle is referred to as window ( $W_T$ ), and can be expressed as follows.

$$W_T = T_{test} + T_{repair} \tag{2.10}$$

where  $T_{test}$  is the time for testing and detecting the defective pixels and  $T_{repair}$  is the time for repairing defective pixels. Within a certain number of test/repair cycles, all pixels will be tested (and repaired, if needed). If the system capacity allows, it can test and repair all pixels in one cycle (i.e., if  $W_T$  is long enough to test and repair all pixels captured and stored on the frame memory).

The image data is stored in the frame memory, pixel by pixel.  $D_n$  is the number of defective pixels propagated from the CCD at the  $n_{th}$  test/repair cycle, and can be calculated as follows.

$$D_n = D_T \cdot r_{defect}^{n-1} \tag{2.11}$$

where  $D_T$  is the total number of soft-defects hit on the frame memory, and  $r_{defect}$ is the decrease rate of  $D_n$  after each repair cycle. Since  $D_T$  is the total number of defective pixels, the following equation can be derived as well.

$$D_T = D_n + R_n \tag{2.12}$$

where  $R_n$  is the number of repaired pixels which are detected by the soft-test, and  $D_T$  is a constant assumed to be a known characteristic of the CCD. On the other hand,  $F_{test}$  is the number of pixels that can be tested within the test time  $T_{test}$ , and  $W_T$  is the window size (i.e.,  $T_{repair} + T_{test}$ ). Also, the number of defective pixels (i.e.,  $F_{fault}$ ) can be expressed as follows.

$$F_{fault} = F_{test} \cdot (1 - Y_H) \tag{2.13}$$

Therefore, the  $F_{repair}$  can be expressed by dividing  $T_{repair}$  by  $T_{net \ repair}$  as follows.

$$F_{repair} = \frac{W_T - T_{test}}{T_{net \ repair}} \tag{2.14}$$

where  $T_{net\ repair}$  is the repair time for a defective pixel, and  $F_{repair}$  is the number of repaired pixels that can be repaired within  $W_T - T_{test}$ . From Equation (2.13) and (2.14), the repair ratio (i.e.,  $r_{repair}(n)$ ) can be expressed as follows.

$$r_{repair}(n) = \frac{min(F_{repair}, F_{fault})}{F_{fault}}$$

(2.15)

$$= \frac{\min(F_{repair}, F_{fault})}{F_{test} \cdot (1 - Y_H)}$$

(2.16)

The decrease ratio  $r_{defect}$  can be defined as follows.

$$r_{defect} = 1 - r_{repair}(n) \tag{2.17}$$

Then, the number of repaired pixels after n cycles,  $R_n$  of the CCD system can be given as follows.

$$R_n = \sum_{k=1}^{n} (D_{k-1} - D_k)$$

$$= (D_{\pi} - D_{\pi} \cdot r_{1,n-1}) + (D_{\pi} \cdot r_{1,n-1} - D_{\pi} \cdot r_{1,n-2}) + (D_{\pi} \cdot r_{1,n-2} - D_{\pi} \cdot r_{1,n-3})$$

(2.18)

$$= (D_T - D_T \cdot r_{defect}) + (D_T \cdot r_{defect} - D_T \cdot r_{defect}) + (D_T \cdot r_{defect} - D_T \cdot r_{defect})$$

$$+ \cdots + (D_T \cdot r_{defect}^n - D_T \cdot r_{defect}^{n-1})$$

(2.19)

$$= (D_T + defect - D_T + defect - (2.13))$$

$$= D_T (1 - r_{defect}^{n-1})$$

(2.20)

Also, Equation (2.20) can be derived from Equation (2.11) and (2.12). By definition of normalization,  $\overline{R}_n$  can be formulated as follows.

$$\overline{R}_n = \frac{Number \ of \ Repaired \ Pixel}{Total \ Number \ of \ defective \ Pixel}$$

(2.21)

$$= \frac{D_T (1 - r_{defect}^{n-1})}{D_T}$$

(2.22)

$$= 1 - r_{defect}^{n-1} \tag{2.23}$$

From Equation (2.17) and (2.16), the repair rate can be calculated as follows.

$$\overline{R}_n = 1 - \left[1 - \frac{\min(F_{repair}, F_{fault})}{F_{test} \cdot (1 - Y_H)}\right]^{n-1}$$

(2.24)

$$= 1 - \left[1 - \frac{\min(F_{repair}, F_{sl} + F_{ls} + F_{sh} + F_{hs})}{F_{test} \cdot (1 - Y_H)}\right]^{n-1}$$

(2.25)

Therefore, the virtual yield  $Y_V$  is given by

$$Y_V(n) = Y_H + (1 - Y_H) \cdot C_{st} \cdot \overline{R_n}$$

(2.26)

$$= Y_H + (1 - Y_H) \cdot C_{st} \cdot (1 - r_{defect}^{n-1})$$

(2.27)

where  $Y_H$  is the CCD Hard Yield, and  $C_{st}$  is the Soft-Test Coverage (i.e., the rate of detecting defective pixels out of the total number of actual defective pixels). Therefore, from Equation (2.17) and (2.16), the overall virtual yield can be re-expressed as follows.

$$Y_{V}(n) = Y_{H} + (1 - Y_{H}) \cdot C_{st} \cdot \left[ 1 - \left( 1 - \frac{\min(F_{repair}, F_{fault})}{F_{test} \cdot (1 - Y_{H})} \right)^{n-1} \right]$$

(2.28)

=  $Y_{H} + (1 - Y_{H}) \cdot$

$$C_{st} \cdot \left[ 1 - \left( 1 - \frac{\min(F_{repair}, F_{sl} + F_{ls} + F_{sh} + F_{hs})}{F_{test} \cdot (1 - Y_H)} \right)^{n-1} \right]$$

(2.29)

#### 2.4 Parametric Analysis

In this section, the effect of the proposed soft-test/repair process on the virtual yield of CCD will be evaluated through numerical simulations based on  $Y_V$  derived in the previous section.

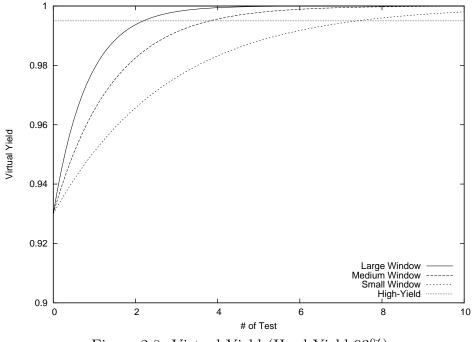

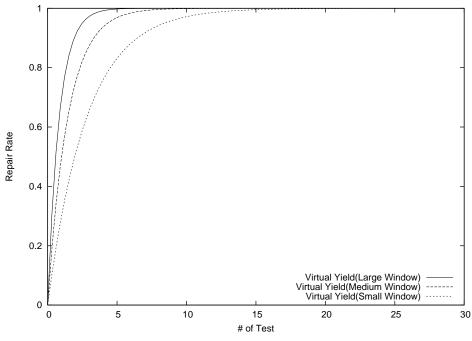

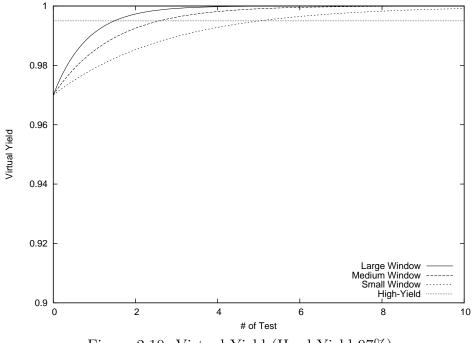

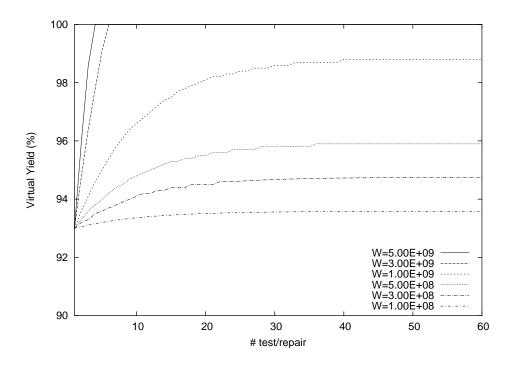

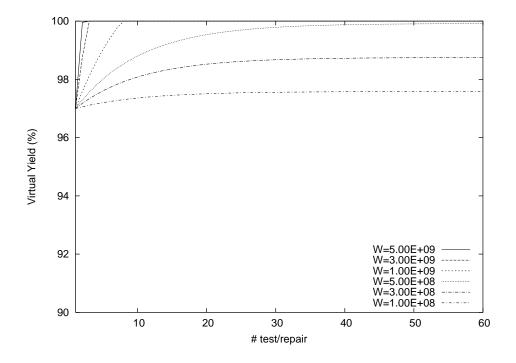

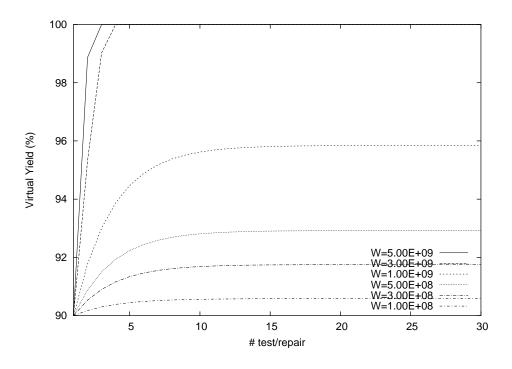

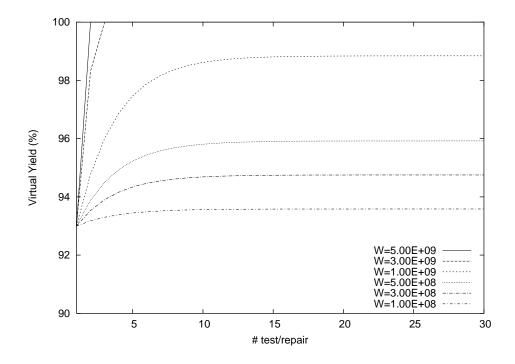

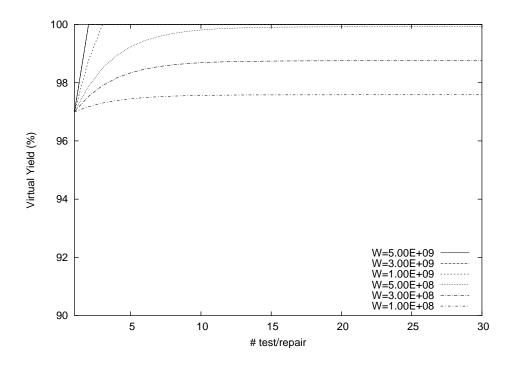

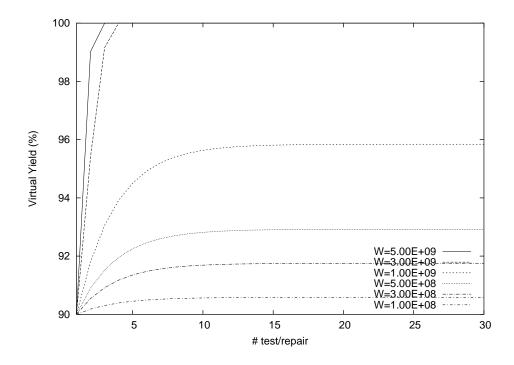

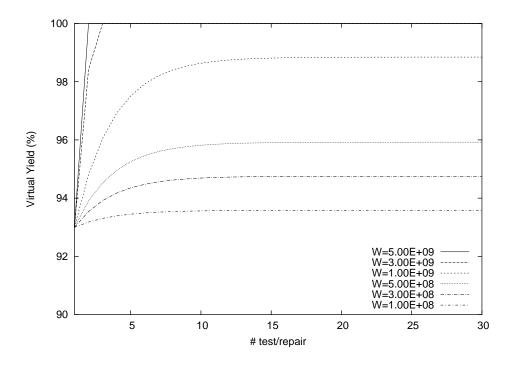

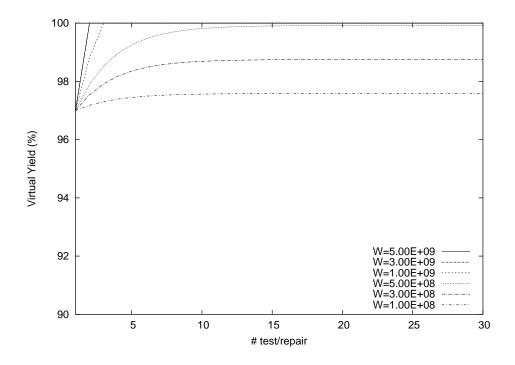

CCDs of 6 Mega pixels (2K×3K) are assumed in this simulation. Three CCDs containing 10%, 7% and 3% defected pixels are considered, respectively (i.e., 10% is  $(2048 \times 3072)/10$ ). From Equation (2.23), the repair rates are calculated as shown in the Figures (2.5), (2.7), and (2.9).  $Y_H = 90\%$ ,  $Y_H = 93\%$  and  $Y_H = 97\%$  CCDs are used for Figures (2.5), (2.7), and (2.9), respectively. Also, the CCDs of  $Y_H = 90\%$ ,  $Y_H = 93\%$  and  $Y_H = 97\%$  are used for Figures (2.6), (2.8), and (2.10), respectively based on Equation (2.27). Note that three CCDs with 90%, 93% and 97% hard yields are also considered for the purpose of comparison.

For the simulation, we assumed that the large window size is given by the time to scan and fix defective pixels for 30% of total pixel (i.e.,  $2048 \times 3072$ ). In the same way, the medium window size is given for 20% and the small window size is given for 10%.

A very *High Yield* (i.e, 99.5%) CCD is adopted for the purpose of comparison in Figures (2.6), (2.8), and (2.10). Note that the conventional method uses a defective

pixel map on PC or workstation not in hardware level. So, we compare proposed soft-test repair approach with very High Yield(99.5%) without repair.

By comparing the results of Figures (2.5)-(2.10), the following observations can be drawn.

- 1. The proposed soft-test/repair approach is beginning to outperform the conventional calibration approach after a certain number of test/repair cycles in terms of virtual yield. In Figure (2.9), the repair rate approaches 100% at n=5 with large window size. Therefore, just a certain number of initial image shots are needed to repair the defective pixels building a complete noise history data map on the cache. Thereafter, it will be just a matter of preprocessing incoming image data with reference to the complete noise history data map on the cache. In Figure (2.5), the convergence to 100% is delayed to n = 20 with large window size. The increase rate of the repair rate is determined by  $r_{defect}$  based on Equation (2.23).

- 2. The proposed approach achieves high Virtual Yield after a certain point compared to the conventional approach regardless of the Hard-Yield and expensive CCDs being used in the conventional approach, as shown in Figures (2.6), (2.8), and (2.10) in which the CCDs have  $Y_H = 90\%$ ,  $Y_H = 93\%$  and  $Y_H = 97\%$ , respectively. In Figure (2.6), the virtual yield of the proposed repair process with small window size is starting to exceed the repair rate of high yield with large window at n=8. After the number of repair cycles exceeds n=8, the virtual yield converges to 100%. It is higher than the high yield CCD (i.e., 99.5%) and improved by 10%. This is very significant virtual yield enhancement by all means, which is very desirable in high resolution digital x-ray systems.

- 3. In Figures (2.5), (2.7), and (2.9), the hard yield  $Y_H$  affects the repair rate. All the yields approach up to 100% regardless of the low initial hard yields.

However, this does not mean that any low hard yield such as  $Y_H = 30\%$  can virtually be enhanced to 100%. CCDs may or may not have reparable defects (i.e., not clustered defects). Actually, the criterion of acceptable image depends on the requirement of the system such as the resolution of system (i.e., lpm (Line Per Millimeter) or dpi (Dot Per Inch)), since some systems cannot tolerate clustered defective pixels. However, most medical systems use the binning mode (i.e., combining the pixel by hardware or software) for gathering more photons and increasing the image quality.

- 4. In Figures (2.5), (2.7), and (2.9), the increase rate of the repair rate is shown and it depends on the window size. The higher hard-yield CCD quickly approaches 100% repair rate. However, even the small window size can achieve 100% repair rate just in a few more repair cycles. From this result, even if new defective pixels hit, the repair rate can achieve 100% by using the proposed soft-test/repair process. In practice, a CCD price depends on its grade which is determined by the number of defective pixels. Therefore, this approach can reduce the cost of products while increasing the image quality.

- 5. The resulting virtual yields are shown in Figures (2.6), (2.8), (2.10) based on Equation (2.27). The hard yields determine the initial virtual yields. After a certain number of repair cycles, all the virtual yields converge to 100%.

From the results and findings shown so far, it can be concluded that the harddefects which mapped on the frame memory can be effectively repaired by the proposed soft-test/repair approach. Also, the repair rates and the virtual yields approach 100% in a small number of repair cycles. Furthermore, the proposed approach can enhance the repair rate as high as up to 100%, even though new defective pixels hit due to physical shocks or exposing to excessive x-ray.

Figure 2.5: Repair Rate (Hard-Yield 90%)

Figure 2.6: Virtual Yield (Hard-Yield 90%)

Figure 2.7: Repair Rate (Hard-Yield 93%)

Figure 2.8: Virtual Yield (Hard-Yield 93%)

Figure 2.9: Repair Rate (Hard-Yield 97%)

Figure 2.10: Virtual Yield (Hard-Yield 97%)

#### 2.5 Discussion and Conclusions

This work has presented a soft-test/repair approach for CCD-based digital x-ray systems through sound establishment of a novel theoretical modeling and analysis of the proposed test/repair procedure. It has been revealed that the yield of the CCD is one of the most critical components affecting the QoS (Quality of Service) of a digital X-ray system. There are two possible solutions to cope with the defective pixel problem in CCD; one is the hard-repair approach and another is the proposed soft-repair approach. The proposed soft-repair approach is to circumvent defective pixels at the digitized image level; thereby it is inexpensive to practice and on-line repair can be done for non-interrupted service. It tests the images to find the defective pixels and filter the defects at the frame memory level, and caches them in a flash memory in the controller for future use. The controller cache keeps accumulating all the noise coordinates, and preprocesses the incoming image data from the A/Dconverter by repairing them. The algorithms can be implemented on hardware level (i.e., on the controller) to speed up the process. Unlike the calibration approaches shown in [9, 10], the proposed approach stores the noise history map dynamically on hardware level and always keeps the up-to-date data within proper window size. Numerical simulations have revealed that the proposed soft/hard approach using the proposed soft-testing and repair process will outperform the conventional hard approach after a certain break-even point in terms of virtual yield, thereby ultimately realizing high QoS of digital x-ray systems.

In the following Chapter 3, clustered fault models of CCDs and repair methods will be studied with simulation. In Chapter 4, practical designs and implementations regarding soft-test/repair will be presented. In addition, various parametric simulations such as testing and repair time analysis and parallel testing processing will be presented in verilog HDL level.

# CHAPTER 3

### CCD Clustered fault

## 3.1 Introduction

Many applications of digital imaging technology can be found in such system as digital cameras, digital camcorders and digital x-ray diagnosis systems to mention a few. Among the currently available digital optical sensing devices, CCDs and APSs (Active Pixel Sensors) are the two most commonly used ones. In practice, pixels on such digital image sensing devices may contain defective pixels due to various causes such as improper fabrication, excessive exposure to light and radiation, and aging of sensing element. Therefore, in high-resolution digital imaging sensors, defect and fault tolerance is stringently required to assure quality of service.

Extensive works have been conducted on defect modeling, testing, and repair in semiconductor devices which in general, 2-dimensional array architecture can be assumed to model such devices. Traditionally, most of the techniques employ a method of replacement of faulty cells or blocks with spare cells or blocks, respectively. However, the traditional technique cannot be effectively employed for image sensing devices for testing and repair. No displacement is allowed for CCD pixels because each pixel has a unique x-y coordinate that cannot be backed up or replaced in case of a defect. Thus, the traditional redundancy-based repair techniques for memory systems cannot be applied to digital image sensing devices.

Our previous work [12] for testing and repairing defective CCD pixels is an efficient and practical method for testing and repairing faulty CCDs. There also have been a few hardware-based methods proposed to design a reliable CCD based on digital signal processing system [14, 15, 16, 9]. Digital cameras employ high resolution color CCD for high resolution image sensing. [9] proposed that defects on color CCD can be detected by checking which color is corrupted among the three colors (i.e. red, green and blue), and repaired by replacing a faulty color pixel with a spare CCD pixel provided. These hardware redundancy-based approaches rely on spare row and column-replacement of CCD pixels, and are thus impractical to be practiced for the displacement of image sensing pixels and the additional cost to the already expensive CCDs [16, 9].

Unlike traditional test/repair methods, the proposed soft-test/repair of CCDs is performed by software yet targetting at hardware-defect/fault testing/repair. The overall yield enhancement of CCD has been demonstrated by the soft-test/repair methods with efficiency and effectiveness from our previous work [12].

In this work, a propagation of the hardware-defects/faults (i.e., defective pixels) from CCD to frame memory is modeled based on practical *clustered defective pixels* in comparison with the single defect/fault model in our previous work [12, 17, 13]. Clustered defect/fault model for testing and repair process is to be considered for realistic and practical faulty pixels. The objective of this work is to propose a testing and repair method for CCD imaging system with inability of on-device repair (i.e., off-device fault tolerance) under clustered CCD pixel defect/fault model. To effectively capture the on-device pixel defects and faults off the device intact, a novel propagation-tracing method of the defects and faults is proposed. The efficiency and effectiveness of the proposed methods is demonstrated by enhancement of yield (i.e., soft-yield) under clustered defect/fault model as well as single fault model.

This work has been partially presented in [17].

This work is organized as follows. In the next section (Section 3.2), previous works are reviewed, and basic principles of the proposed approach are introduced. In Section 3.3, the proposed soft-testing and repair process for single and clustered faulty pixels is evaluated. In Section 3.4, parametric simulations with respect to CCD yield, soft-repair rate are shown. Then, conclusions and discussions are presented in Section 3.5.

# 3.2 Review and Preliminaries

Figure 3.1: Block Diagram of CCD System

In this work, a CCD imaging system will be modeled considering not only single faults but also clustered faults. CCDs are the most widespread image sensors for digital imaging systems and are becoming more prevalent these days, because of its many advantages such as high-resolution, manufacturability and image quality, to mention a few. Unfortunately, CCDs are not free from hardware faults like other semiconductors and the faults could increase the overall cost (i.e., both manufacturing and maintenance costs). Imperfect fabrication and improper processing may induce defects (referred to as *hard-defects*) on the photo-sensitive pixels and supporting system components in CCDs. In [15], the main causes of CCD hard-defects are categorized as follows.

- 1. Failure of row/column pixels (either line or readout/control transistors/circuit).

- 2. Failure of row select/reset shift register.

- 3. Failure of column sense amplifiers.

- 4. Failure of A/D converter.

- 5. Failure of buffers.

#### 6. Failure of read-out/reset transistors on each photo-diode.

In practice, all the defects of the above-mentioned types affect the quality of the raw image data on the frame memory, since the hard-defects that propagated all the way from the CCD to the frame memory through the A/D converter as shown in Figure (3.1). The effect of a hard-defect observed on the frame memory is referred to as *soft-defect*. Notably, a soft-defective pixel on the frame memory usually shows an abnormal value compared to its neighboring pixel values. Without loss of generality, one-on-one correspondence between a hard-defect on the CCD and a soft-defect on the frame memory can be assumed, unless other component failures than CCD failures are taken into account. In this context, it is feasible to test and repair (i.e. soft-testing/repair) CCD hard-defects on soft memory-mapped level in the form of soft-defects on the frame memory.

From our previous work [12], following equations were derived.

$$Y_{V}(n) = Y_{H} + (1 - Y_{H}) \cdot C_{st} \cdot \left[ 1 - \left( 1 - \frac{\min(F_{repair}, F_{fault})}{F_{test} \cdot (1 - Y_{H})} \right)^{n-1} \right]$$

(3.1)

$$= Y_{H} + (1 - Y_{H}) \cdot C_{st} \cdot \left[1 - \left(1 - \frac{\min(F_{repair}, F_{sl} + F_{ls} + F_{sh} + F_{hs})}{F_{test} \cdot (1 - Y_{H})}\right)^{n-1}\right]$$

(3.2)

where  $Y_H$  is the CCD Hard Yield,  $Y_V$  is the CCD virtual Yield,  $C_{st}$  is the Soft-Test Coverage,  $F_{test}$  is the number of tested pixels and  $F_{repair}$  is the number of repaired pixels.  $F_{sl}$ ,  $F_{ls}$ ,  $F_{sh}$ , and  $F_{hs}$  are the number of stuck low pixels, the number of low sensitive pixels, the number of stuck high pixels, and the number of stuck high sensitive pixels, respectively.

The previous model just handled with single faults. Hence, in case of clustered faults, it is indispensable to consider clustered fault model for more precise modeling. Next section will describe the proposed soft-test/repair model extended to clustered

fault model.

## 3.3 The Proposed Soft-Test/Repair Model

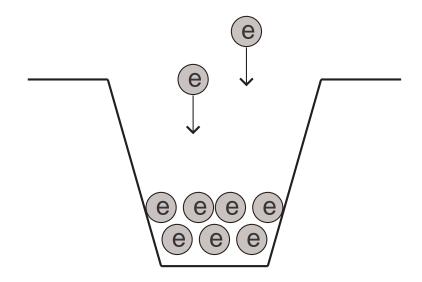

Each pixel of image sensors can be modeled as an electron well in Figure (3.2) in general. Photons (i.e. light) are accumulated in electron well when it light come through the window. By electric field, the potential wells are controlled.

Figure 3.2: Electron (Potential) Well

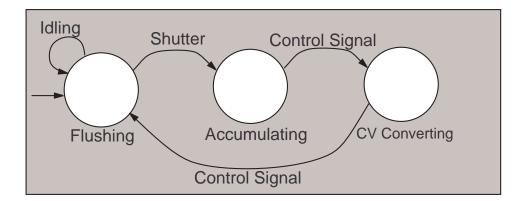

Figure 3.3: State Diagram of CCD

In general, CCD operation can be modeled as shown in Figure (3.3). Initially, CCD is in the flushing state where it is discharging electrons before accumulating for next shot. During the flushing state, CCD cannot accumulate electrons as shown in Figure (3.2). Then, by electronic or mechanical shutter operation, the electrons are being accumulated in an electron (potential) well during exposure time. The number of accumulated electrons, Q, can be expressed as follows.

$$Q(x, y, t) = \int_0^t \left[ n(x, y, t) \cdot e \right] dt$$

(3.3)

where n(x, y, t) is the number of electrons at each pixel, e is a unit electron (photon), xand y are the coordinates of the electronic well, and t is the exposure time manipulated by the shutter (from 0 to t). Once the exposure is completed, the charged electrons are transfer to the column amplifier from the electron wells (i.e., pixels) by the controller as shown in Figure (3.1). The charged electrons in each pixel are then converted to a voltage value by column amplifier as follows.

$$v(x,y) = Q(x,y,t) \cdot A_c \tag{3.4}$$

where v(x, y) is the voltage (i.e., analog) value of a pixel (i.e., electron well), and  $A_c$ is the gain of charge-to-voltage converter. By the ADC (Analog to Digital Converter), each pixel voltage value is converted to a digital value V(x, y) as follows.

$$V(x,y) = v(x,y) \cdot A_d \tag{3.5}$$

where  $A_d$  is the analog to digital gain determined by the characteristics of the image sensors. Note that v(x, y) is a floating number and V(x, y) is an integer number. From Equation (3.3),(3.4) and (3.5), the final digitized voltage value can be derived as followings.

$$V(x,y) = A_c \cdot A_d \cdot \int_0^t \left[ n(x,y,t) \cdot e \right] dt$$

(3.6)

V(x, y) of each pixel is propagated to and then stored in the frame memory as shown in Figure (3.1). V(x, y) can be characterized into five sets. 1.  $Q_{sh} = \{V | V \text{ is high-stuck-pixels}\}$

A high-stuck-pixel cannot sense the amount of electrons and always display high value even for dark light.

2.  $Q_{sl} = \{V|V \text{ is low-stuck-pixels}\}$

A low-stuck-pixel cannot sense the amount of electrons and always display low value even for bright light.

3.  $Q_{hs} = \{V | V \text{ is over-sensitive-pixels}\}$

A over-sensitive-pixel can sense the amount of electrons but too sensitive (i.e., out of tolerance). In this case, compare to other normal pixels, it has always higher value than normal pixel.

4.  $Q_{ls} = \{V | V \text{is under-sensitive-pixels}\}$

A under-sensitive-pixel can sense the amount of electrons but less sensitive (i.e., out of tolerance). In this case, compare to other normal pixels, it has always lower value than normal pixel.

5.  $Q_n = \{V|V \text{ is normal pixel}\}$

A normal pixel can sense exact (i.e., within tolerance) amount of electrons.

Each set of pixels can be tested as follows.

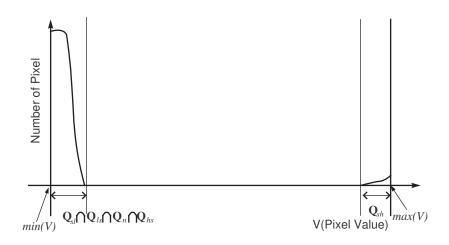

1.  $Q_{sh}$ : Test Input : No light to CCD and take a shot.

Test Output : Raw Image

All the pixel values V should be min(V). Others can be classified as high-stuckpixels in Figure (3.4). In the figure, only the high-stuck-pixels can clearly be decided. The found defective pixel map should be saved on non-volatile memory such as flash memory for later use.

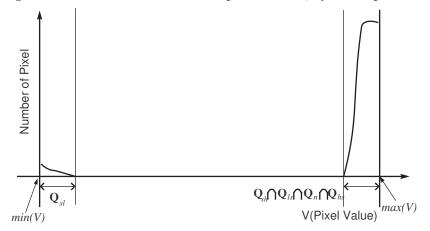

2.  $Q_{sl}$ : Test Input : Use very bright light and take a shot. Test Output : Raw Image All the pixel values V should be near max(V). Others can be classified as lowstuck-pixels in Figure (3.5). In the figure, only the low-stuck-pixels can surely be decided. The found defective pixel map should be saved on non-volatile memory such as flash memory for later use.

3.  $Q_{hs}$ : Test Input : Use mid light and take a shot.

Test Output : Raw Image

In this case, the pixel value distribution should be like in Figure (3.6). For detecting over-sensitive-pixels, very high quality light source is needed such as parallel and even light. In the figure, the over-sensitive-pixel is out range, especially right bound, of the normal value. The found defective pixel map should be saved on non-volatile memory such as flash memory for later use.

4.  $Q_{ls}$ : Test Input : Use mid light and take a shot.

Test Output : Raw Image

In this case, the pixel value distribution should be like in Figure (3.6). For detecting under-sensitive-pixels, very high quality light source is needed such as parallel and even light. In the figure, the under-sensitive-pixel is out of range of the normal value. The found defective pixel map should be saved on non-volatile memory such as flash memory for later use.

5.  $Q_n$ : Test Input : Use mid light and take a shot.

# Test Output : Raw Image

In this case, the pixel value distribution should be like in Figure (3.6). For detecting under-sensitive-pixels, very high quality light source is needed such as parallel and even light. In the figure, the window of normal value should be generally 10% of (max(V) - min(V)). It is depend on the light source and optical characteristics of CCD.

In addition, V(x,y) can be divided into two clustering categories.

Figure 3.4: Distribution of CCD pixel values;  $Q_{sh}$  is separated.

Figure 3.5: Distribution of CCD pixel values;  $Q_{sl}$  is separated.

Figure 3.6: Distribution of CCD pixel values; all combined.

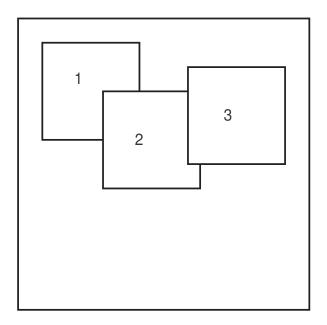

Figure 3.7: Clustered Fault Pixels and Single Fault Pixels

- 1. Clustered Fault : a pixel has any kind of functional fault and its adjacent pixels also have kinds of functional fault like label B in Figure (3.7).

- 2. Single Fault : a pixel has any kind of functional fault yet its neighboring pixels have no functional faults. In Figure (3.7), label A is an example.

It is important because clustered faults cannot be repaired perfectly.

From the union of functional and clustering categories, there will be four kinds of fault as follows.

$$Q_{sl} = Q_{sl,c} \cup Q_{sl,r} \tag{3.7}$$

$$Q_{sh} = Q_{sh,c} \cup Q_{sh,r} \tag{3.8}$$

$$Q_{ls} = Q_{ls,c} \cup Q_{ls,r} \tag{3.9}$$

$$Q_{hs} = Q_{hs,c} \cup Q_{hs,r} \tag{3.10}$$

(3.11)

where  $Q_{sl,c}$  is a set of low stuck and clustered pixels (i.e., each of pixel in the set of  $Q_{sl,c}$  is not only a defective pixel but also having at least a neighboring defective pixel). The subscript c stands for clustered and r stands for single pixels. Theoretically, the following three equations can be formulated as follows.

$$Q_c = Q_{sl,c} \cup Q_{sh,c} \cup Q_{ls,c} \cup Q_{hs,c} \tag{3.12}$$

$$Q_r = Q_{sl,r} \cup Q_{sh,r} \cup Q_{ls,r} \cup Q_{hs,r}$$

$$(3.13)$$

$$Q = Q_c \cup Q_r \cup Q_n \tag{3.14}$$

From the definition of the yield, the hard yield  $Y_H$  can be expressed as follows.

$$Y_{H} = \frac{\int_{sectionQ_{n}} P(V)dV}{\int_{min(V)}^{max(V)} P(V)dV}$$

$$= 1 - \frac{|Q_{sl,c}| + |Q_{sh,c}| + |Q_{ls,c}| + |Q_{hs,c}|}{|Q|}$$

$$- \frac{|Q_{sl,r}| + |Q_{sh,r}| + |Q_{ls,r}| + |Q_{hs,r}|}{|Q|}$$

(3.15)

$$= 1 - \frac{|Q_c| + |Q_r|}{|Q|} \tag{3.17}$$

where P is the distribution of pixel number.

Repair methods should be considered both the single and clustered faults. Followings are just for single fault repairing. Clustered faults will be explained later.

• Stuck-low and stuck-high pixels (i.e.  $Q_{sl}$  and  $Q_{sh}$ ) can be repaired by replacing the defective pixel scale values. Since a defective pixel does not have any significant information, the defective pixel value is to be replaced by the average value of its neighboring pixel values.

$$V(0) = \frac{\sum_{k=1}^{N} V(k)}{N}$$

(3.18)

where V(0) is the center pixel which is tested, the  $\sum_{k=1}^{N} V(k)$  means the sum of neighboring pixel and the N is the number of neighboring pixel in Figure (3.8).

• The repair for a defective pixel of in  $Q_{hs}$  and  $Q_{ls}$  depends on how much the pixel is insensitive or oversensitive. Thus, the following equation can be used to take into account the insensitivity and oversensitive.

$$V(0) = p \cdot V(0)$$

(3.19)

where p is a gain factor for fixing pixels in  $Q_{hs}$  and  $Q_{ls}$ . To fix the pixel in  $Q_{hs}$ and  $Q_{ls}$ , the gain factor has to be stored in memory in advance.

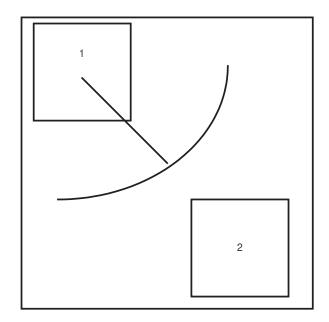

Figure 3.8: Repairing of Clustered Fault

Repair of the clustered fault should be considered the neighboring pixels whether they are defective or not. Otherwise, the repairing results in diffusion of the defective area because of fake repair. In Figure (3.8), the repairing pixel V(0) should not be replaced by Equation (3.18). Instead, it should be replaced by following equation.

$$V(0) = \frac{\sum_{k=1}^{8} V(k) - V(8)}{N - 1}$$

(3.20)

To generalize this equation, it can be expressed as follows.

$$V(0) = \frac{\sum_{k=1}^{N} V(k) - \sum_{l=1}^{M} D(l)}{N - M}$$

(3.21)

where N is the number of pixel in testing area and M is the number of defective pixels in testing area. M is referred to as *Acceptance Level (AL)*. AL means how many defective pixels will be accepted for testing area. As see in Equation (3.21), M should not equal to N, which means the repairing pixel cannot be repaired from all defective pixels because no other pixels have any information about repairing pixel. Proper AL should be smaller than 4, which means at least half of the pixels in testing area are normal. Note that the defective pixel values (i.e., D(l) is removed (i.e., subtracted) for preventing diffusion effect.

The soft yield  $Y_S$  can be derived as follows. Single defective pixels can be repaired by soft-repair method. Therefore, the single defective pixel repair ratio can be 1.

$$Y_S = 1 - \frac{|Q_{sl,c}| \cdot (1 - R_{sl,c}) + |Q_{sh,c}| \cdot (1 - R_{sh,c})}{|Q|}$$

$$-\frac{|Q_{hs,c}| \cdot (1 - R_{hs,c}) + |Q_{ls,c}| \cdot (1 - R_{ls,c})}{|Q|} - \frac{|Q_{sl,s}| \cdot (1 - R_{sl,s}) + |Q_{sh,s}| \cdot (1 - R_{sh,s})}{|Q|} - \frac{|Q_{ls,s}| \cdot (1 - R_{ls,s}) + |Q_{hs,s}| \cdot (1 - R_{hs,s})}{|Q|}$$

(3.22)

$$= 1 - \frac{|Q_{sl,c}| \cdot (1 - R_{sl,c}) + |Q_{sh,c}| \cdot (1 - R_{sh,c})}{|Q|} - \frac{|Q_{ls,c}| \cdot (1 - R_{ls,c}) + |Q_{hs,c}| \cdot (1 - R_{hs,c})}{|Q|}$$

(3.23)

$$= Y_{H} + \frac{|Q_{s}|}{|Q|} + \frac{|Q_{sl,c}| \cdot R_{sl,c} + |Q_{sh,c}| \cdot R_{sh,c}}{|Q|} + \frac{|Q_{ls,c}| \cdot R_{ls,c} + |Q_{hs,c}| \cdot R_{sh,c}}{|Q|}$$

(3.24)

### 3.4 Parametric Simulation

The impact of the clustered fault model on the soft yield (i.e.,  $Y_S$ ) is shown in this section by using the proposed off-device testing/repair methods. In the simulation the defect/fault propagation model is used to capture the impact of the on-device defects and faults off the device intact.

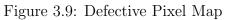

A CCD of 6 Mega pixels  $(2K \times 3K)$  is assumed in this simulation. Three CCDs of such capacity and each of which 8%, 5% and 2% defective pixels are considered respectively (i.e. 5% is  $(2048 \times 3072)/20$ ). For the simulation, a map of defective pixels is generated using a single defect/fault model as shown in Figure (3.9).

The defective pixel map is generated by single number generation of built-in function in C language. The consecutive two random numbers are assigned to the coordinate of the defective pixel. This process continues until the number of defect pixel meets. If the generated pixel is out of bound or duplicated with other pixels already mapped then the generated pixel is discarded.

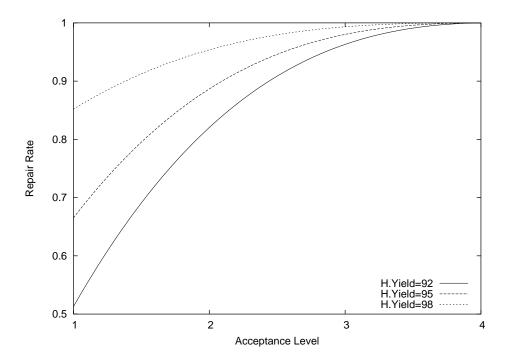

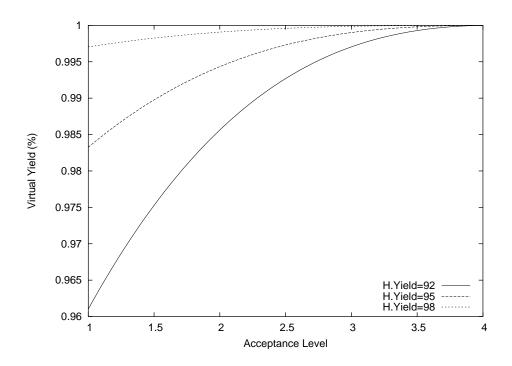

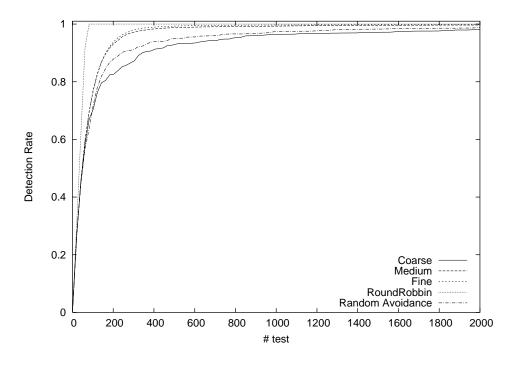

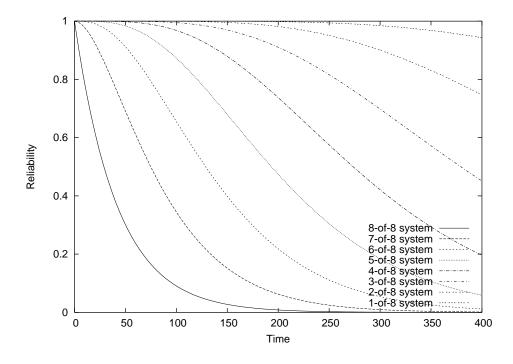

From the results in Figure (3.10)-(3.11), the following observations can be drawn.

- Figure (3.10)-(3.11) show not only the single faults (i.e., AP=1) but also clustered fault (i.e., AP > 1). Where AL (Acceptance Level) is the number of defective pixel contained in testing window except the testing pixel.

- 2. Repair rate of single defective pixels (exclude clustered defective pixels) was 51% for 92% hard yield CCD, 66% for 95% hard yield CCD, and 85% for 98% hard yield CCD. Where the single defective pixel means a pixel which has no other defective pixels in the test window (i.e., 3X3 in this simulation) like the pixel labeled A in Figure (3.7). From this simulation and theoretically, high yield CCDs have less clustered defective pixel.

- 3. Repair rate for just single defective pixel is too low than the expectation. In

other words, 49% for 92% hard yield CCD, 44% for 95% hard yield CCD, and 15% for 98% hard yield CCD are clustered fault. This means that there exist many clustered defective pixels and considering the clustered fault model is indispensable.

- 4. AL (Acceptance Level) = 4 for the size of 3 × 3 window is enough for achieving perfect repairing in the clustered model for high yield CCDs. It is very important factor in clustered fault model. If it were impossible and had to use larger filter, the detect/repair time would be increased exponentially. If the AL=4 were not secured, adopting larger testing window would be unavoidable.

- 5. From the simulation results, the size of  $3 \times 3$  of the area under test is still very sufficient for repairing clustered faults. This means real time implementation is possible in low performance hardware.

- 6. Soft-test/repair results in increase the soft yield. From Figure (3.10), all test model secured 100% repair rate from AL=3. Optimal yield (i.e., reparable by soft-test/repair) CCD could be used more widely and decrease the cost of CCD without degrading image quality.

## 3.5 Discussion and Conclusions