# A STUDY ON THE MAXIMUM SPEED AND RELIABILITY

### ASSURANCE IN WAVE PIPELINE-BASED

### COMBINATIONAL CIRCUITS

By

### TAO FENG

Bachelor of Science Northwest A&F University Xi'an, China 1996

Master of Science Oklahoma State University Stillwater, Oklahoma 2003

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of DOCTOR OF PHILOSOPHY December, 2006

# COPYRIGHT

By

Tao Feng

December, 2006

# A STUDY ON THE MAXIMUM SPEED AND RELIABILITY

# ASSURANCE IN WAVE PIPELINE-BASED

# COMBINATIONAL CIRCUITS

Thesis Approved:

Dr. Nohpill Park Thesis Advisor

Dr. K. M. George

Dr. Venkatesh Sarangan

Dr. Guoliang Fan

Dr. A. Gordon Emslie Dean of the Graduate College

#### ACKNOWLEDGMENTS

I sincerely thank my research advisor, Dr. Nohpill Park, for his excellent advice, guidance, and direction. Also I gratefully acknowledge all the members of my committee, Dr. K.M. George, Dr. Venkatesh Sarangan, and Dr. Guoliang Fan for their valuable advice. I would also like to give special thanks to my family for their love, support, and guidance: my wife, Melissa Feng; my parents, Guangsheng Feng and Sumei Wang; and my parents in-law, Mark and Nancy Torbert.

# TABLE OF CONTENTS

| 1 | INT<br>1.1 | RODUCTION         Conventional Pipeline                             | 1<br>4   |

|---|------------|---------------------------------------------------------------------|----------|

|   | 1.2        | Wave Pipeline                                                       | 5        |

|   | 1.3<br>1.4 | Clockless Wave Pipeline                                             | 8<br>12  |

| 2 | FAU        | LT MODELS AND YIELD MODELING/ASSURANCE                              | 15       |

|   | 2.1        | Intra-Wave Fault and Yield                                          | 15       |

|   | 2.2<br>2.3 | Inter-Wave Fault and Yield       Request Signal Fault and Yield     | 18<br>24 |

| 3 | FAU        | LT TOLERANT DESIGN FOR REQUEST SIGNAL FAULTS                        | 26       |

|   | 3.1        | Possible Effects of Crosstalk Noise on the Datawaves                | 27       |

|   |            | 3.1.1 High Request Signal with Crosstalk Noise to Pass N Switch     | 27       |

|   |            | 3.1.2 High Request Signal with Crosstalk Noise to Pass P Switch     | 30       |

|   |            | 3.1.3 Low Request Signal with Crosstalk Noise to Pass P Switch      | 31       |

|   |            |                                                                     | 32       |

|   | 3.2        | Fault Tolerant Design Approaches                                    | 33       |

|   | 3.3        | Reliability Calculation                                             | 35       |

|   |            | 3.3.1 Effectiveness of Multiple Request Signal Lines on Reliability | 35       |

|   |            |                                                                     | 36       |

|   |            |                                                                     | 38       |

|   | 3.4        | 1                                                                   | 39       |

|   | 3.5        | Conclusions                                                         | 41       |

| 4 |            |                                                                     | 44       |

|   | 4.1        |                                                                     | 44       |

|   | 4.2        | 1                                                                   | 46       |

|   | 4.3        | 1                                                                   | 51       |

|   | 4.4        |                                                                     | 52       |

|   | 4.5        | Conclusions and Discussion                                          | 63       |

| 5 |            | E PROPOSED NEW WAVE PIPELINE FOR MAXIMUM CIRCUIT SPEED AND          |          |

|   | REL        | JABILITY ASSURANCE                                                  | 66       |

|   | 5.1        |                                                                     | 67       |

|   | 5.2        | 1 2                                                                 | 69       |

|   |            | 1 5 5                                                               | 71       |

|   |            | 1                                                                   | 78       |

|   |            | 5.2.3 Conventional Wave Pipeline                                    | 79       |

|   |            |                                                                     |          |

|   | 5.3        | The Proposed Maximum Circuit Speed Based on the New Wave Pipeline         | 80                |

|---|------------|---------------------------------------------------------------------------|-------------------|

|   |            | 5.3.1 The Proposed New Wave Pipeline                                      | 80                |

|   |            | 5.3.2 The Clock Cycle for the Proposed Maximum Speed Circuit              | 83                |

|   |            | 5.3.3 Output Delay Buffers                                                | 94                |

|   | 5.4        | The Simulation and Verification of the proposed new wave pipeline         | 99                |

|   |            | 5.4.1 Simulation Algorithm                                                | 100               |

|   |            | 5.4.2 Experimental Results                                                | 101               |

|   | 5.5        | Conclusion                                                                | 110               |

|   |            |                                                                           |                   |

|   |            |                                                                           |                   |

| 6 | MOI        | DELING AND ANALYSIS ON MTTF AND RELIABILITY                               | 113               |

| 6 | MOI<br>6.1 | DELING AND ANALYSIS ON MTTF AND RELIABILITY<br>Reliability Model Analysis |                   |

| 6 |            |                                                                           | 114               |

| 6 | 6.1        | Reliability Model Analysis                                                | 114<br>115        |

| 6 | 6.1<br>6.2 | Reliability Model Analysis                                                | 114<br>115<br>118 |

# LIST OF TABLES

| 3.1 | Fault cases                                                                                                                                        | 33  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Truth table                                                                                                                                        | 34  |

| 4.1 | Statistic of ISCAS C432 path delays in the original design (ps)                                                                                    | 54  |

| 4.2 | Statistic of ISCAS C432 path delays in the fault tolerant design with $np =$                                                                       |     |

|     | $0.6, \gamma = 0.6 \text{ (ps)} \dots \dots$ | 54  |

| 4.3 | Statistic of ISCAS C499 path delays in the original design (ps)                                                                                    | 55  |

| 4.4 | Statistic of ISCAS C499 path delays in the fault tolerant design with $np =$                                                                       |     |

|     | $0.6, \gamma = 0.6 \text{ (ps)} \dots \dots$ | 55  |

| 4.5 | Statistic of ISCAS C880 path delays in the original design (ps)                                                                                    | 56  |

| 4.6 | Statistic of ISCAS C880 path delays in the fault tolerant design with $np =$                                                                       |     |

|     | $0.6, \gamma = 0.6 \text{ (ps)} \dots \dots$ | 56  |

| 5.1 | Basic information of benchmark circuits                                                                                                            | 102 |

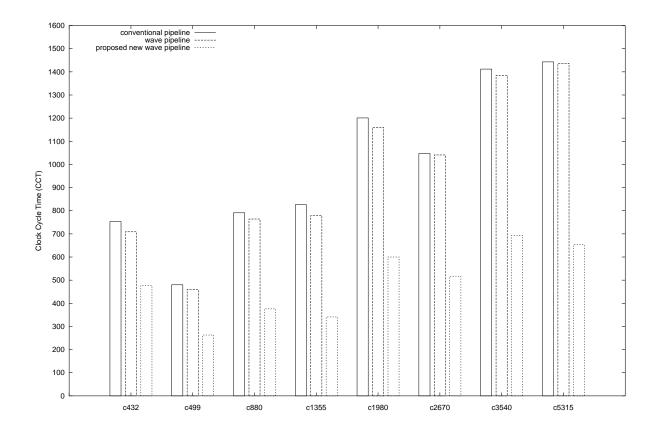

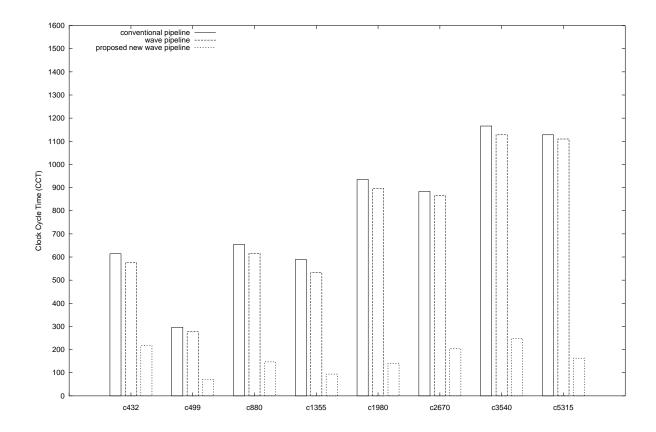

| 5.2 | Comparison of clock cycle times of the benchmark circuits                                                                                          | 107 |

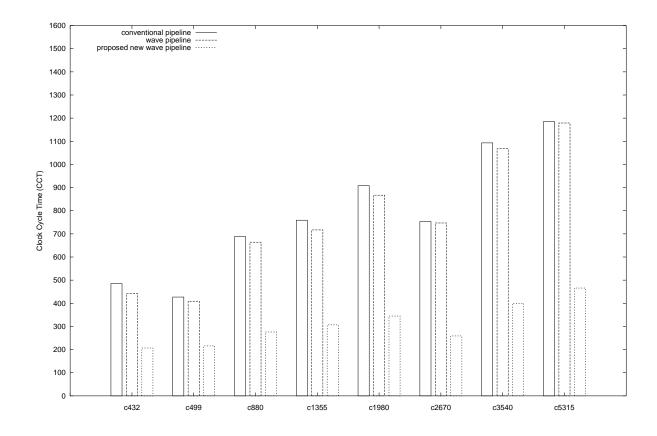

| 5.3 | Comparison of clock cycle times of the benchmark circuits if only considering                                                                      |     |

|     | rising delay                                                                                                                                       | 108 |

| 5.4 | Comparison of clock cycle times of the benchmark circuits if only considering                                                                      |     |

|     | falling delay                                                                                                                                      | 110 |

| 6.1 | Statistical analysis of path delays and reliability of benchmark circuits                                                                          | 119 |

|     |                                                                                                                                                    |     |

# LIST OF FIGURES

| 1.1  | Conventional pipeline                                                                 | 5  |

|------|---------------------------------------------------------------------------------------|----|

| 1.2  | Conventional synchronous linear instruction pipeline                                  | 5  |

| 1.3  | Instruction wave pipeline                                                             | 7  |

| 1.4  | Typical synchronous wave pipeline                                                     | 8  |

| 1.5  | Two-phase asynchronous wave pipeline [23]                                             | 9  |

| 1.6  | Transparent switch                                                                    | 10 |

| 1.7  | Opaque switch                                                                         | 10 |

| 2.1  | Intra-wave fault rate                                                                 | 16 |

| 2.2  | Detailed intra-wave fault                                                             | 17 |

| 2.3  | Relative position between the request signal and datawave                             | 17 |

| 2.4  | Inter-wave fault as horizontal delay fault                                            | 19 |

| 2.5  | Signal transition diagram of inter-wave fault                                         | 20 |

| 2.6  | Inter-wave fault as a subset of intra-wave fault                                      | 20 |

| 2.7  | Two bits, A (in falling transition) and B (in rising transition) on the same datapath | 21 |

| 2.8  | Probability for two bits on the same datapath causing an inter-wave fault             | 22 |

| 3.1  | Crosstalk noise on a high request signal with the N switch                            | 28 |

| 3.2  | Broken data on the N switch causing intra-wave fault                                  | 29 |

| 3.3  | Crosstalk noise on a high request signal with P switch                                | 31 |

| 3.4  | Crosstalk noise on a low request signal with P switch                                 | 32 |

| 3.5  | Broken data on P switch causing intra-wave fault                                      | 33 |

| 3.6  | Modified two-phase asynchronous wave pipeline with redundant request signal           |    |

|      | lines                                                                                 | 35 |

| 3.7  | MTTG is decreasing when the crosstalk noise rate increases                            | 38 |

| 3.8  | System reliability with 1,2,3,4 request signal lines                                  | 40 |

| 3.9  | Circuit implementation of the fault tolerant technique                                | 41 |

| 3.10 | Simulation of crosstalk noise on a low request signal masked by AND gate on           |    |

|      | P switch                                                                              | 42 |

| 3.11 | Simulation of crosstalk noise on a high request signal masked by OR gate on N         |    |

|      | switch                                                                                | 43 |

| 4.1  | Architecture of the reliability enhanced 2-phase clockless wave pipeline              | 45 |

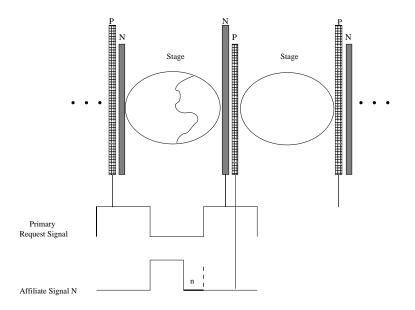

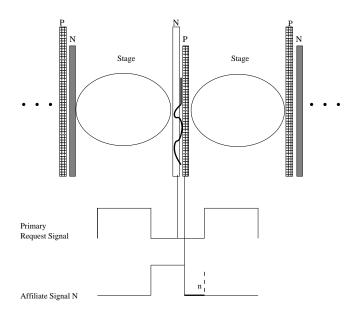

| 4.2  | Before passing the middle N-switch and P-affiliated switch                            | 46 |

| 4.3  | Passing the middle N-switch and P-affiliated switch                                   | 47 |

| 4.4  | After passing the middle N-switch and P-affiliated switch                             | 47 |

| 4.5  | Path delay with bipolar switches vs. without                                          | 48 |

| 4.6  | Inverse function                                                                      | 49 |

| 4.7  | Probability density function of the path delay with bipolar switches                  | 50 |

| 4.8  | Statistic of ISCAS C432 path delays in the original design                            | 54 |

| 4.9        | Statistic of ISCAS C432 path delays in the fault tolerant design with $np =$                                                                        |              |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|            | $0.6, \gamma = 0.6$                                                                                                                                 | 54           |

| 4.10       | Statistic of ISCAS C499 path delays in the original design                                                                                          | 55           |

| 4.11       | Statistic of ISCAS C499 path delays in the fault tolerant design with $np =$                                                                        |              |

|            | $0.6, \gamma = 0.6$                                                                                                                                 | 55           |

| 4.12       | Statistic of ISCAS C880 path delays in the original design                                                                                          | 56           |

| 4.13       | Statistic of ISCAS C880 path delays in the fault tolerant design with $np =$                                                                        |              |

|            | $0.6, \gamma = 0.6$                                                                                                                                 | 56           |

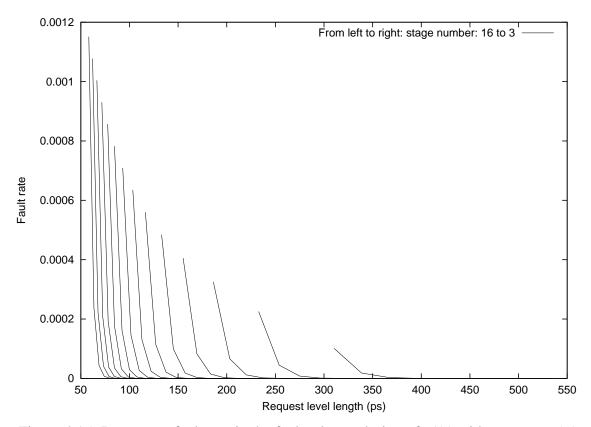

| 4.14       | Intra-wave fault rate in the original design of $c432$                                                                                              | 58           |

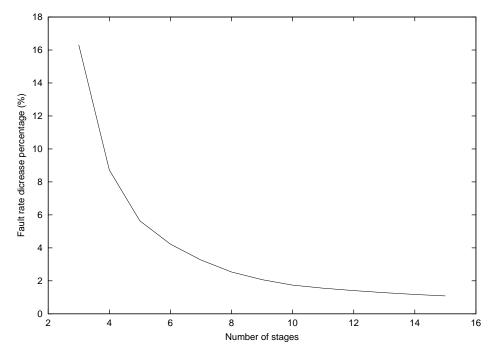

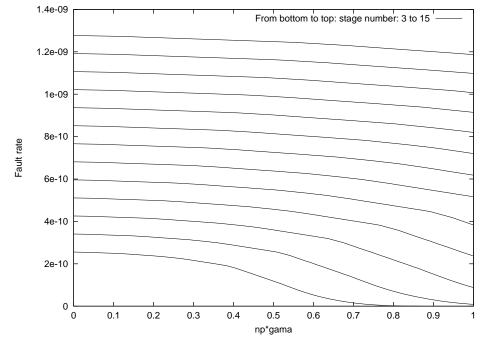

| 4.15       | Intra-wave fault rate in the fault tolerant design of $c432$ with $np = \gamma = 0.8$                                                               | 59           |

| 4.16       | Decreased intra-wave fault rate with the fault tolerant design of $c432$ , $\alpha = 0.5$ ,                                                         |              |

|            | $np = \gamma = 0.6$                                                                                                                                 | 59           |

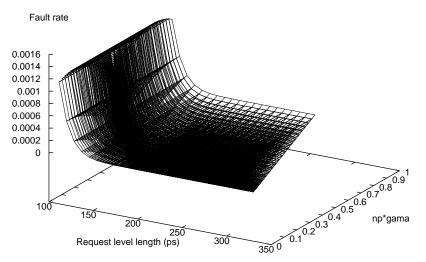

| 4.17       | Effectiveness of $np \times \gamma$ and $\alpha$ in the fault tolerant design of $c432$ with stage                                                  |              |

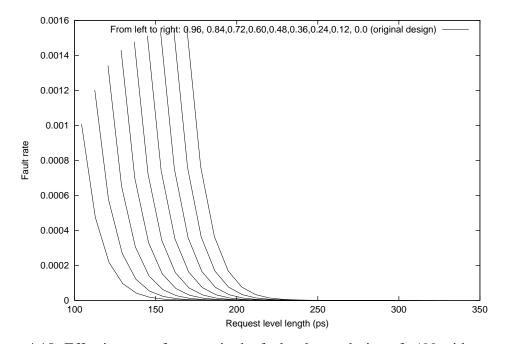

|            | $number = 5 \dots \dots$                            | 60           |

| 4.18       | Effectiveness of $np \times \gamma$ in the fault tolerant design of $c432$ with stage number                                                        |              |

|            | $= 5  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots $                                                                               | 61           |

| 4.19       | Effectiveness of $np \times \gamma$ in the fault tolerant design of $c432$ with $\alpha = 0.8\Delta$                                                | 62           |

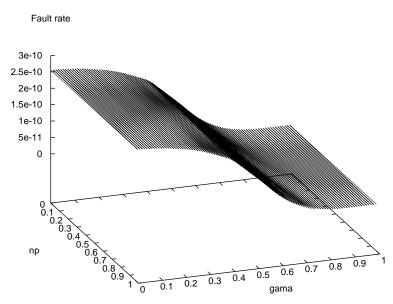

| 4.20       | Effectiveness of $np$ and $\gamma$ in the fault tolerant design of $c432$ with stage number                                                         |              |

|            | $= 3, \alpha = 0.8\Delta$                                                                                                                           | 63           |

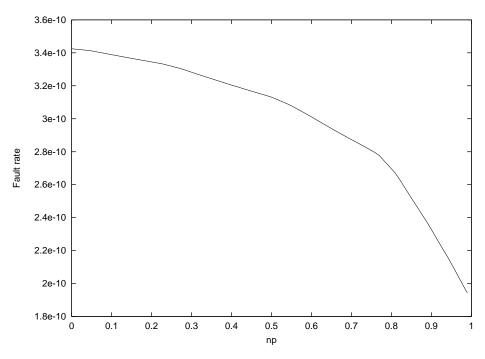

| 4.21       | Effectiveness of $np$ in the fault tolerant design of $c432$ with stage number = 3,                                                                 |              |

|            | $\alpha = 0.8\Delta$ , and $\gamma = 0.5$                                                                                                           | 63           |

| <b>c</b> 1 |                                                                                                                                                     | 70           |

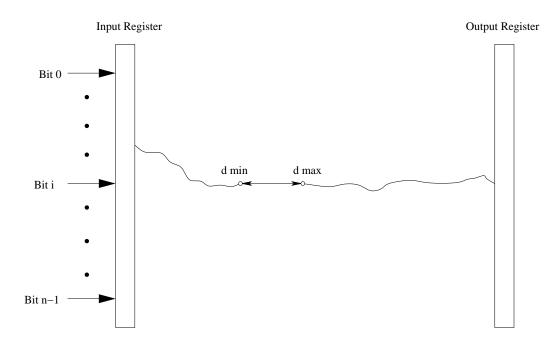

| 5.1        | Bounded delay for a single bit                                                                                                                      | 72           |

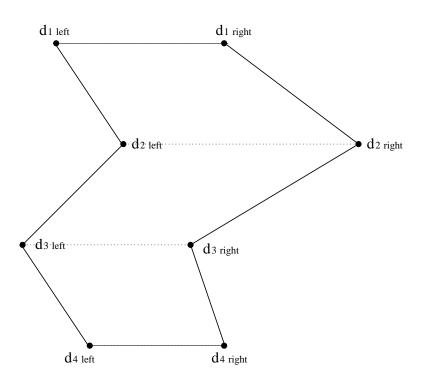

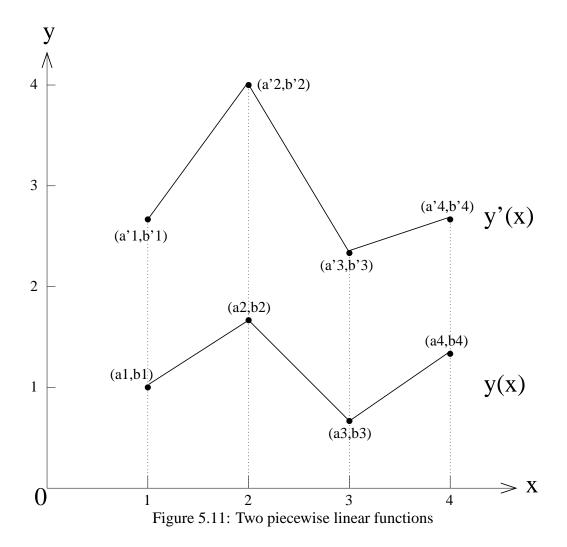

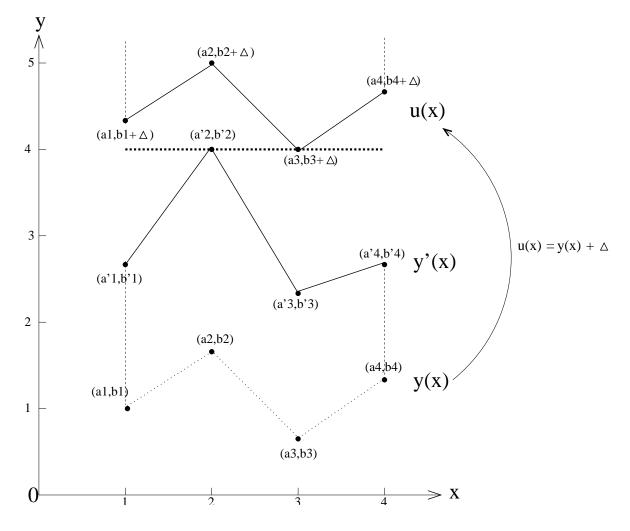

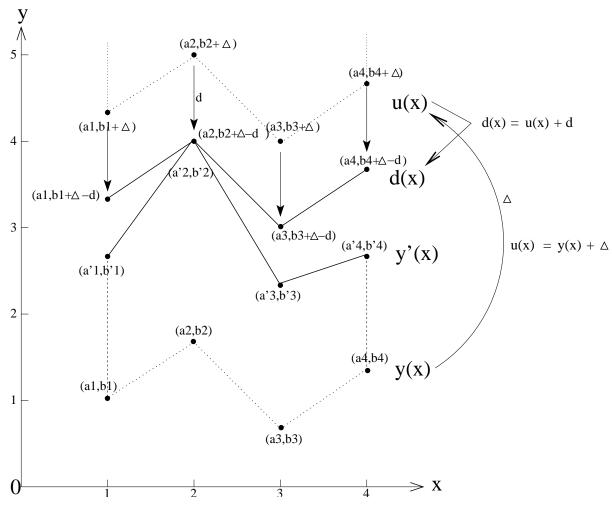

| 5.2        | Polygon representation of a datawave                                                                                                                | 74           |

| 5.3        | Example of a combinational circuit at gate level                                                                                                    | 76           |

| 5.4        | Extracted temporal bounded system delay model                                                                                                       | 77           |

| 5.5        | Extracted spatial bounded system delay model                                                                                                        | 77           |

| 5.6        | Conventional pipeline in the spatial bounded system delay model                                                                                     | 78           |

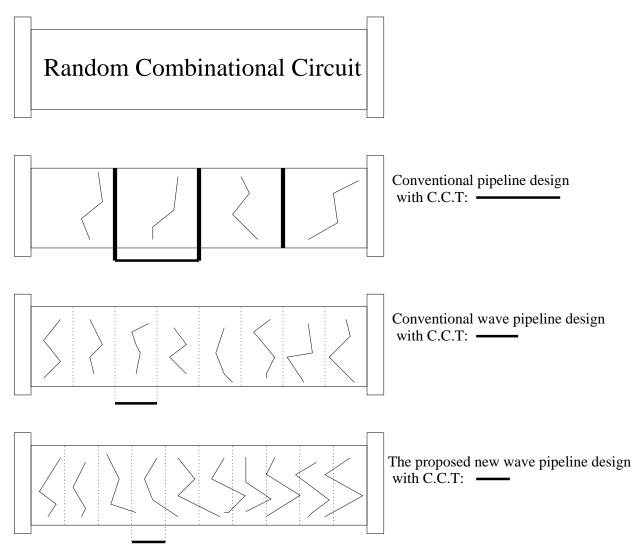

| 5.7        | Conventional wave pipeline in the temporal bounded system delay model<br>Concept comparison between conventional wave pipeline and the proposed new | 81           |

| 5.8        |                                                                                                                                                     | 82           |

| 5.9        | wave pipeline                                                                                                                                       | 82<br>82     |

|            |                                                                                                                                                     | 84<br>84     |

|            | Two-sided borders of the global maximum polygon                                                                                                     | 85           |

|            | Repositing $y(x)$ to the starting point of pushing                                                                                                  | 88           |

|            |                                                                                                                                                     |              |

|            | The final step of the functions reposition                                                                                                          | 90<br>93     |

|            | Best case of the proposed wave pipelining                                                                                                           | 93<br>94     |

|            | Proposed new wave pipeline-based architecture output delay buffers                                                                                  | 94<br>96     |

|            | Applying the output buffer to the proposed new wave pipeline                                                                                        | - 90<br>- 98 |

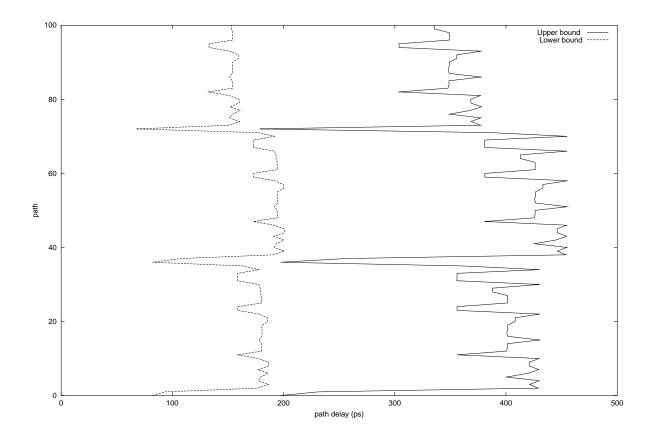

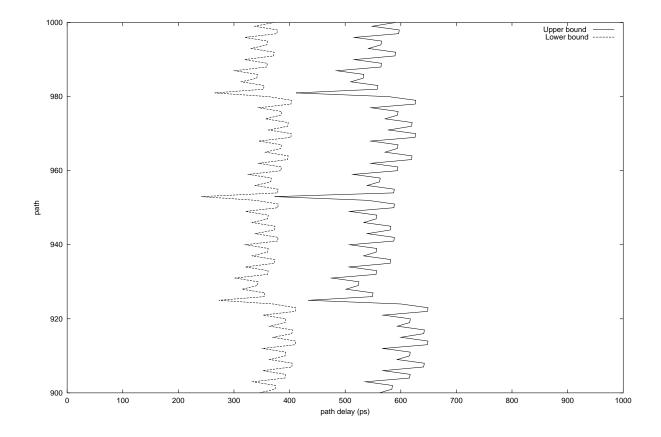

|            | GMP for the first 100 paths of ISCAS c432 circuit                                                                                                   | 98<br>103    |

|            | GMP for the first 100 paths of ISCAS c432 circuit considering only rising delay                                                                     | 103          |

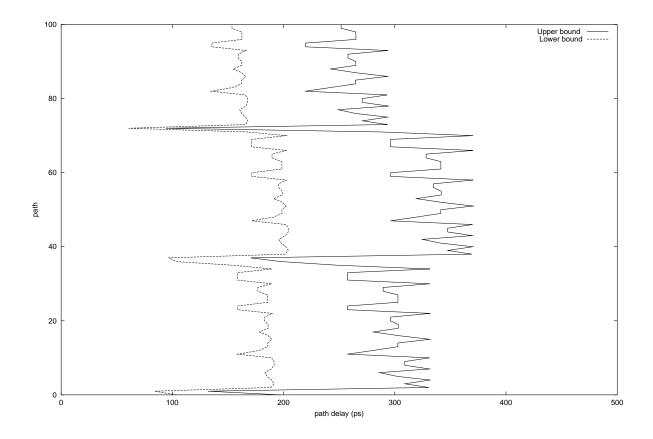

| 5.19       | with an assumption of 10% delay uncertainty                                                                                                         | 104          |

| 5 20       | GMP for the first 100 paths of ISCAS c432 circuit considering only falling                                                                          | 104          |

| 5.20       | delay with an assumption of 10% delay uncertainty                                                                                                   | 105          |

|            | deray with an assumption of 1070 deray uncertainty                                                                                                  | 105          |

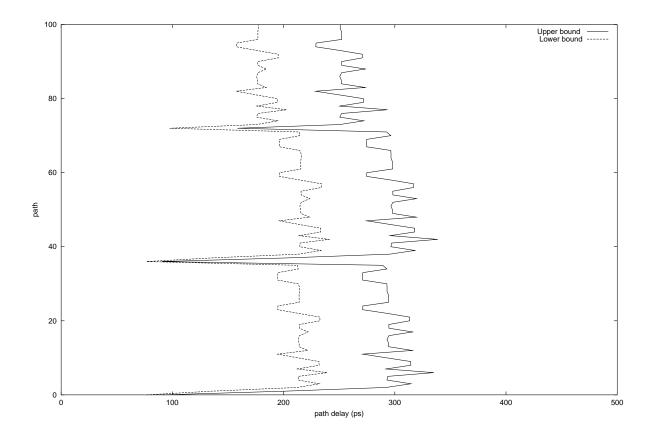

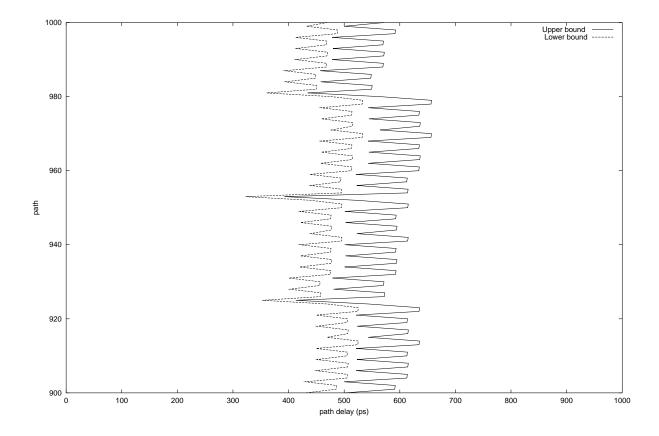

| 5.21 | GMP for the first 100 paths of ISCAS c2670 circuit                          | 106 |

|------|-----------------------------------------------------------------------------|-----|

| 5.22 | GMP for the first 100 paths of ISCAS c2670 circuit considering only rising  |     |

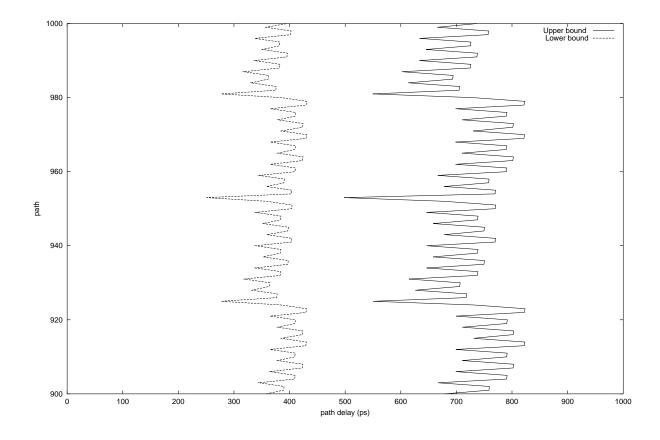

|      | delay with an assumption of 10% delay uncertainty                           | 107 |

| 5.23 | GMP for the first 100 paths of ISCAS c2670 circuit considering only falling |     |

|      | delay with an assumption of 10% delay uncertainty                           | 108 |

| 5.24 | Valid clock cycle time if considering both falling and rising delay         | 109 |

| 5.25 | Valid clock cycle time if considering rising delay only                     | 110 |

| 5.26 | Valid clock cycle time if considering falling delay only                    | 111 |

| 6.1  | Comparison of clock cycle time for different pipeline designs               | 114 |

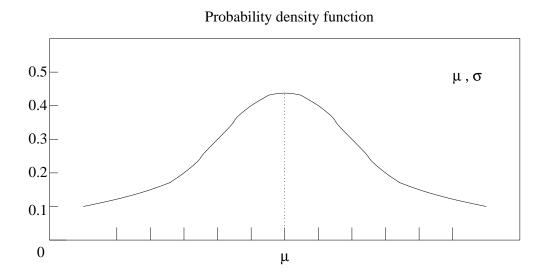

| 6.2  | Statistical analysis of path delays                                         | 115 |

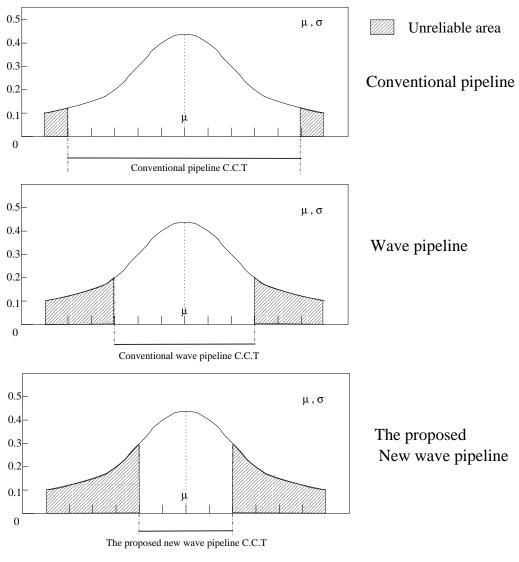

| 6.3  | Reliability comparison                                                      | 116 |

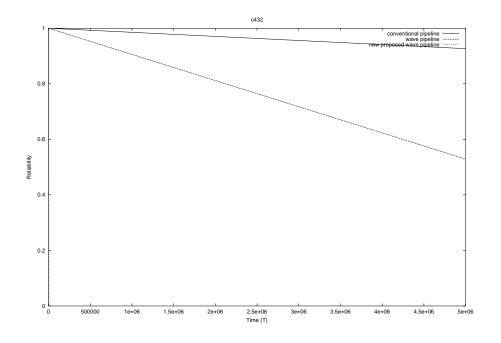

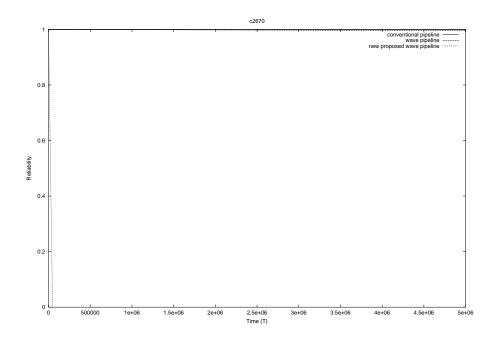

| 6.4  | Reliability function of the circuit c432                                    | 122 |

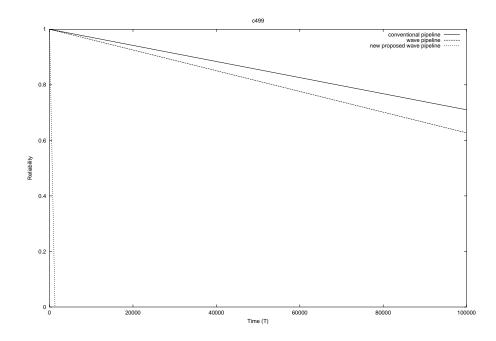

| 6.5  | Reliability function of the circuit c499                                    | 123 |

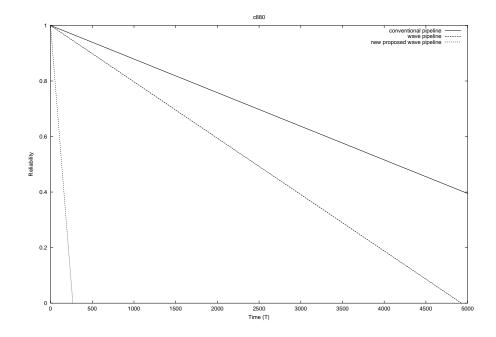

| 6.6  | Reliability function of the circuit c880                                    | 123 |

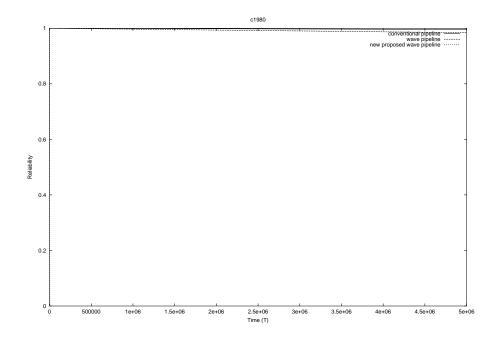

| 6.7  | Reliability function of the circuit c1980                                   | 124 |

| 6.8  | Reliability function of the circuit c2670                                   | 124 |

#### CHAPTER 1

#### INTRODUCTION

Clockless wave pipeline is a cutting-edge and innovative technology as an alternative to traditional pipeline, and a promising computing model moving towards ultra-high throughput and speed. The basic computational components of a clockless wave pipelines are data waves in association with request signals and switches as proposed in [23]. The key to success of clockless wave pipeline is how to coordinate and ensure the processing of datawaves throughout the pipeline in association with the request signals without relying on any intermediate access points under clocked control. Due to the complication of clockless operations, an efficient and effective method to model and analyze the confidence level (referred to as reliability or yield) of clockless operations within wave pipeline is exigently demanded. However, this has not yet been adequately addressed on an integrated level, such as datawaves in association with request signals, leaving this an innovative challenge. The confidence level is primarily determined by the reliability of the clockless orchestration of datawaves and their associated request signals under switch arrangements for datawave alignment.

In this regard, out-of-orchestration between datawaves and request signals, referred to as delay fault, is the major concern in assuring and optimizing the reliability of the system. New faults, referred to as Intra-Wave Fault [13], Inter-Wave Fault [14], and further Request Signal Faults [15], have been proposed and addressed in this dissertation. The proposed new fault models help reveal fundamental yet essential characteristics of the reliability of the clockless

wave pipeline, and enable efficient and effective reliability assurance and optimization. The intra/inter-wave faults are used as the primary drivers to maneuver the evaluation method of the fault impacts on the reliability with respect to extensive delay-sensitive design parameters such as delay distribution, delay variation, crosstalk noise, intra/inter-wave of datawaves, request signal, and other elements. This dissertation specifically addresses and resolves the followings for clockless wave pipeline: extensive and practical clockless-induced datawave fault modeling, yield and reliability modeling, assurance and optimization, and clockless-oriented fault tolerant design methods. The proposed methods will establish a sound and adequate theoretical foundation for development of innovative yet practical test/diagnosis/fault-tolerant design methods in the early design stages of clockless wave pipeline-based logic.

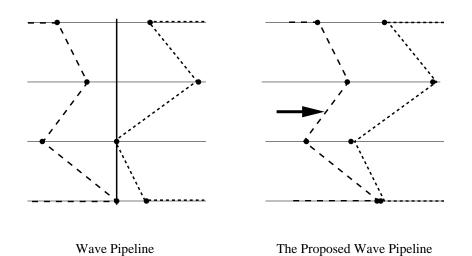

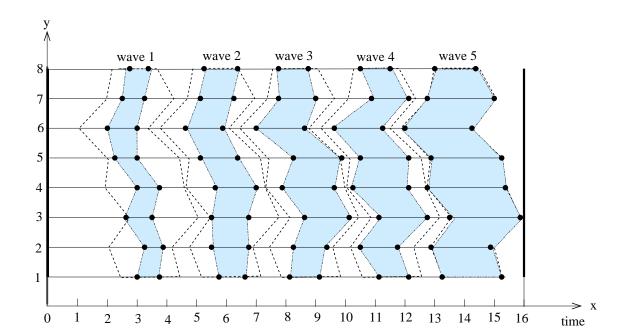

All conventional wave pipeline techniques have been practiced within the long-believed theoretical and technological constraint limited by  $D_{max} - D_{min}$ , where  $D_{max}$  and  $D_{min}$  stands for maximum and minimum path delay in a combinational circuit, respectively; however, we concluded that this limit is a very passive and loose constraint and our proposed new wave pipeline technique can further push the limit farther beyond that level.

A new approach to dramatically enhance the circuit speed is proposed in the context of wave pipeline. The proposed approach is based on the fact that there is more temporal space in combinational circuits to push the frequency of datawaves by allowing superimposition between adjacent datawaves. By allowing the datawave-superimposition, still with the high assurance and certainty of mutual exclusion between adjacent datawaves, a faster clock frequency with the clock cycle equals to  $D_{max} - D_{min} - \delta_{push}$  is achieved in the proposed new wave pipeline, where  $\delta_{push}$  stands for the amount of space that can be further pushed between adjacent datawaves.

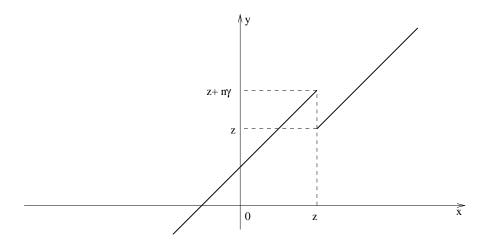

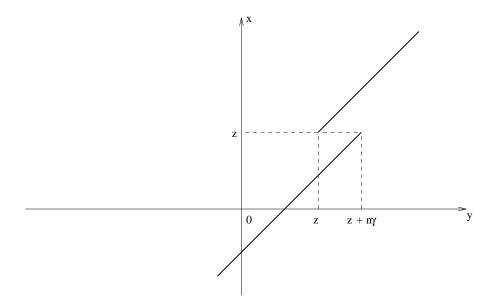

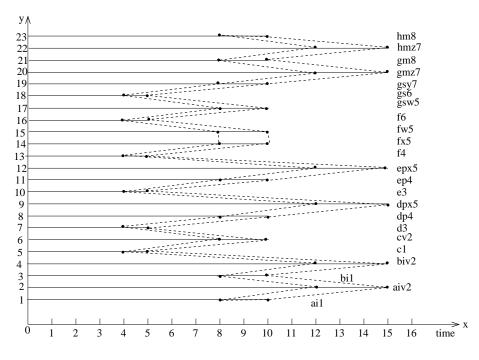

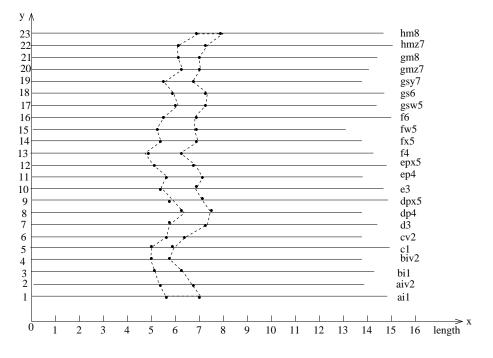

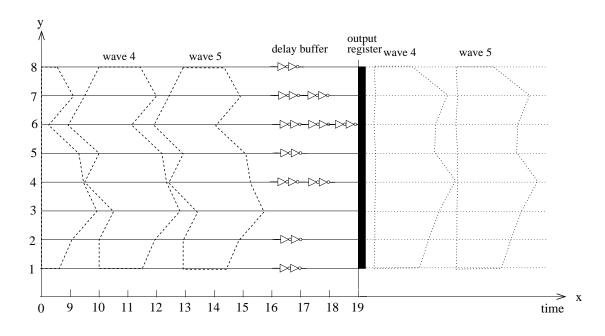

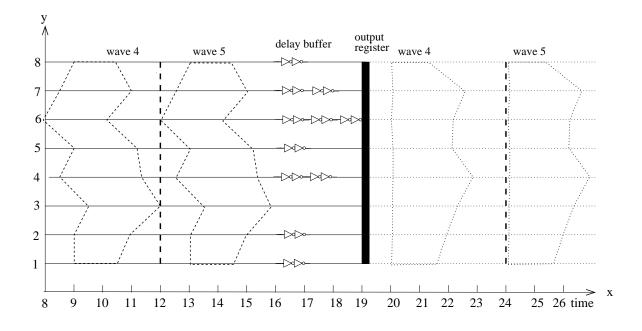

Also, a temporal/spatial bounded system delay model, which expands the current bounded path delay model into the system level and into spatial area, is proposed in order to fully address the practical circuit-delay issues and adequately characterize the datawave processing in the context of wave pipeline. The complete set of paths existed in the circuit are extracted out and relocated into a 2-dimensional coordinate system, with the y-axis representing the path delays and x-axis representing the order of paths. Each datawave can be represented by a polygon within the system, and the Global Maximum Polygon (GMP) is the very last polygon in the system. A new output register architecture with delay buffers is designed and presented in order to achieve the resulting performance and reliability of the proposed approach.

The performance advantage of the proposed technique over conventional wave pipeline is theoretically demonstrated with the cost for a higher reliability requirement. The simulation and verification of the proposed new wave pipeline are experimented against the ISCAS benchmark circuits. The results obtained have shown a faster frequency circuit achieved by the proposed new wave pipeline technology. A MTTF (mean time to failure) model and a reliability model for pipelining circuits are theoretically proposed and applied to conventional pipeline, conventional wave pipeline, and the proposed new wave pipeline. They are also experimented against ISCAS benchmark circuits. The simulation results have shown that the new proposed wave pipeline has a much higher reliability requirement compared with conventional pipeline and conventional wave pipeline.

The specific objectives of this dissertation are:

1. To establish clockless wave pipeline-specific fault models as the primary drivers for yield and reliability modeling, assurance and optimization.

- 2. To demonstrate a theoretical yet thorough characterization and parameterizations of the representative clockless wave pipeline-specific faults (intra-wave fault, inter-wave fault, and request signal fault).

- 3. To demonstrate fault tolerant design methods with respect to datawave faults and request signal faults. Also, to derive a novel yet solid yield model for the proposed fault tolerance for efficient and effective manipulation of extensive fault tolerance.

- 4. To propose the new bounded system delay model based on the current bounded path delay model, and to further propose the new wave pipeline-based architecture, by allowing the datawave-superimposition between adjacent datawaves, which can theoretically yet practically push the performance of of wave pipeline to its limit.

- 5. To conduct the reliability analysis of the proposed new wave pipeline, and compare it with the reliability of conventional pipeline and conventional wave pipeline.

The following sections in this chapter provide a general introduction to and review of the current wave pipeline techniques and others related.

### 1.1 Conventional Pipeline

In computing, a pipeline is a set of data processing elements connected in series. The output of one element is being processed as in the input of the next one. The elements of a pipeline are executed in parallel or in time-sliced fashion.

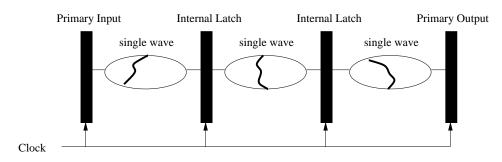

In conventional pipeline, there are registers or latches between any two stages. At any instant of time, there is at most one data active in a single stage as shown in Figure 1.1.

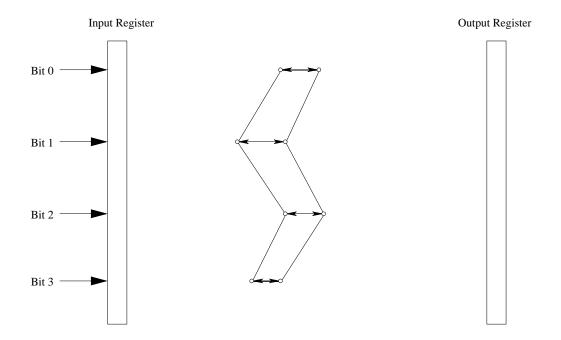

Figure 1.1: Conventional pipeline

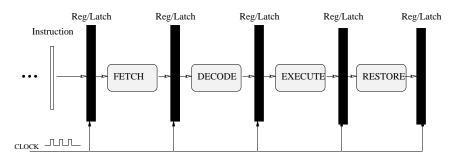

As a concrete example of conventional pipeline, instruction pipeline is a realization of linear synchronous pipeline in which performance is improved through instruction-level parallelism by allowing to start execution of an instruction before the previous ones already in the pipeline are finished. The architecture of conventional synchronous linear instruction pipeline is shown in Figure 1.2.

Figure 1.2: Conventional synchronous linear instruction pipeline

### 1.2 Wave Pipeline

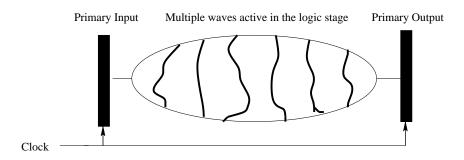

Wave pipeline is a pipeline processing technique that can increase the throughput without increasing internal storage space and power consumption [18, 48, 51]. Multiple datawaves can propagate through the wave pipeline from the PI (Primary Input) to the PO (Primary Output) simultaneously without internal latching. It can ideally achieve the theoretical maximum performance, and draws lots of attentions in the industry today.

The wave pipeline technology was introduced by Cotton [7] in 1969 in order to increase the throughput of the pipeline. This pipeline was also referred to as the maximum rate pipeline. Cotton observed that the rate at which logic can propagate through the circuit depends not on the longest path delay, but on the difference between the longest and the shortest path delays. Hence, by removing the internal latches, balancing all the logic paths within the circuit, and allowing multiple waves, the logic bits can propagate through the combinational circuit in each stage without any delay for register-latching. Thus, a clock period much shorter than the one for the longest path in the circuit can be obtained. To achieve this it must be guaranteed that no fast datawave overruns a previous slow datawave that would result in data loss. Hence, it is critical and the major challenge in wave pipeline design that all paths in the combinational logic be well balanced. The balancing of paths can be implemented in two ways: rough tuning and fine tuning. Rough tuning is to equalize path delays by inserting delay elements to the fast path, and fine tuning is by adjusting gate delays to achieve path equivalence.

Wave pipeline has been extensively researched in both academic and industrial sectors [27], and three to four times of speed-up has been reported in [18]. A few research efforts of wave pipeline have been focused on synchronous wave pipeline (SWP), which is a wave pipeline using clock to control the latches operating in parallel. Many works have been done to research and enhance SWP into an effective and reliable computer technology [76], such as modeling and analysis of correct timing [51], [17]; development of logic synthesis and computer-aided design (CAD) tools for SWP circuits [74],[58]; and development of new wave pipeline-specific circuit [39].

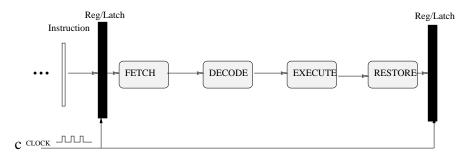

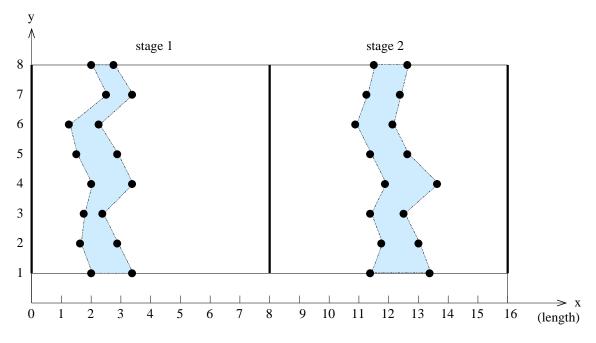

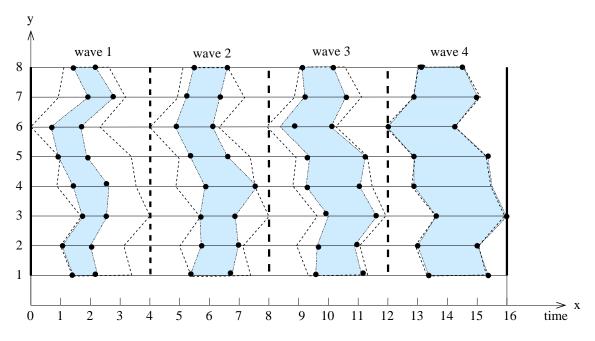

A conventional synchronous instruction wave pipeline architecture is shown in Figure1.3. Each active instruction in the pipeline can be regarded as a wave of input data. By removing the internal register-latches, multiple instructions can propagate through the same logic stage simultaneously at a higher clock frequency. Note that this wave pipeline is still synchronous because the primary input (PI) and the primary output (PO) operate synchronously under the control of the clock.

Figure 1.3: Instruction wave pipeline

In conventional pipeline, there are registers or latches between any two stages. At any instant of time, there is at most one data active in a single stage as shown in Figure1.1. Whereas, in wave pipeline, the internal registers or latches are removed, and multiple data can be active in the same logic stages simultaneously as shown in Figure1.4. The clock cycle time in conventional pipeline is determined by the maximum stage delay, that is  $T_{ck} \ge D_{max}$  (where  $T_{ck}$  is the clock cycle time and  $D_{max}$  is the maximum stage delay). In wave pipeline, the time constraint is more stringent. The clock cycle time is determined not by  $D_{max}$  but by the relative difference between  $D_{max}$  and  $D_{min}$ , that is  $\frac{T_{max}}{N} < T_{ck} < \frac{T_{min}}{N-1}$  [19] (where N is the number of waves in the circuit,  $T_{max}$  is the maximum path delay and  $T_{min}$  is the minimum path delay.

A wave pipeline can be built either in a synchronous or an asynchronous manner. Synchronous wave pipeline uses a clock signal to synchronize the movement of datawave bits. It

Figure 1.4: Typical synchronous wave pipeline

has been successfully deployed in several commercial processors such as the floating point unit of IBM 360/91 [1] and external caches in the HP PA8000 [33].

### 1.3 Clockless Wave Pipeline

Asynchronous wave pipeline uses request and acknowledgement signals (or only a request signal) instead of a global clock to serve as a reference signal. Asynchronous wave pipeline is relatively more difficult to deploy than synchronous wave pipeline due to its explorativeness and a few technological hurdles as mentioned before.

Clockless wave pipeline circuits have only been experimented in non-commercial sectors such as the two-phase clockless wave pipeline, which uses only a single request signal line [26, 23]. The specific architectural model investigated in this dissertation is the two-phase clockless wave pipeline [23]. To the best of our knowledge, it is known to be the best in the context of clockless wave pipeline.

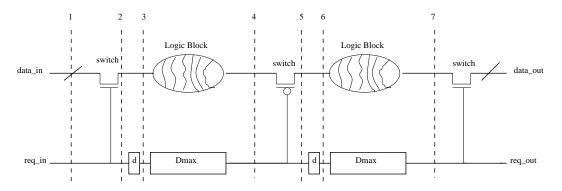

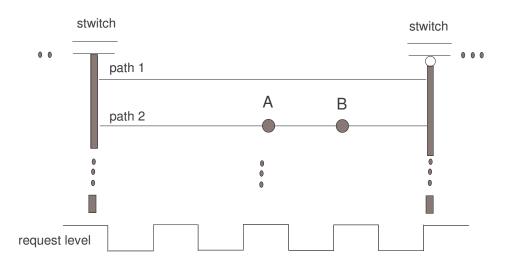

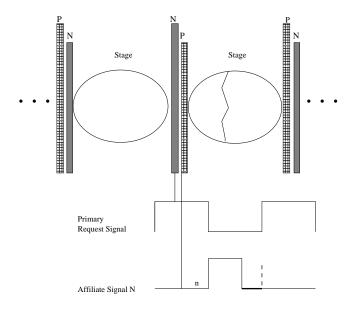

The *two-phase asynchronous wave pipeline* was proposed by Hauck and Huss in [23] as shown in Figure(1.5), which has the two-phase operation by alternating positive and negative level-sensitive switches, and it employs a request signal only, no acknowledgement signal. Note that the asynchronous wave pipeline with request signal only is referred to as clockless wave

pipeline in this dissertation.

Figure 1.5: Two-phase asynchronous wave pipeline [23]

As shown in Figure(1.5) [23], two types of switches, namely positive and negative switches, logically and physically partition the circuit into several pipeline stages for datawave progress alignment purposes, and a request signal controls the switches. A pair of a datawave and a request signal level (either a high or low pulse of the request signal) enters the clockless wave pipeline at the same time in full association, and they must stay so throughout the propagation of the datawave.

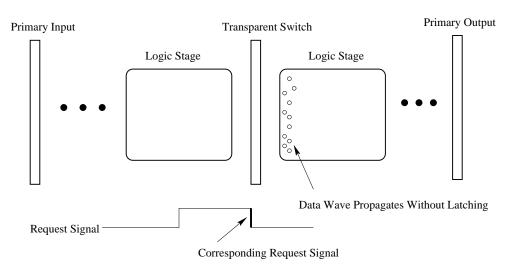

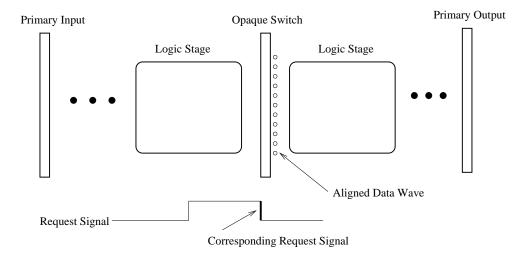

The switch can be opaque or transparent to the datawaves. If opaque, the switch latches the datawave and, if transparent, the datawave passes the switch without latching. Specifically, *N*-type switches (negative switches) are made to be opaque to the datawaves associated with a low request signal, and transparent to those associated with a high request signal. Symmetrically, *P*-type switches (positive switches) are made to be transparent to the datawave associated with a low request signal, and opaque to those associated with a high request signal. The propagation of the datawave within a pipelined circuit is intermittent. Once the datawave enters the circuit, it is assigned a request signal, at either high or low level. Then, by the design rule, as defined, the datawave associated with a high request stopping

for alignment, but has to be latched at P switches. Symmetrically, the datawave associated with a low request signal propagates through P switch without stopping, but has to stop and be latched at N switches. Figure(1.6) depicts the case of a datawave passing through a transparent switch, and Figure(1.7) the case where a datawave is aligned at an opaque switch.

Figure 1.6: Transparent switch

Figure 1.7: Opaque switch

Ideally, there are multiple datawaves populated and propagating through the combinational circuit simultaneously, and traditional delay-fault testing, modeling and assurance techniques

are not readily able to handle and evaluate the faults of successive transitions at the datawave level in the circuit. Therefore, assurance and optimization of delay-oriented yield and reliability is exigently demanded, and a key to the success of clockless wave pipeline technique. Ideally, all path delays from PI to PO are to be equally or near-equally balanced. However, equal-balancing of path delays is hard to realize even with the help of extensive tuning [68] for various fabrication and runtime variations (such as power consumption, thermal distribution and design errors to mention a few) to account for delay variations. Furthermore, clock skews due to variations in the rise/fall time and the setup and hold time of the storage elements will limit the clock frequency to within an increase only by a factor of 2 to 3, even by using the best known design tuning method [75].

Two most representative delay-fault models for synchronous wave pipeline are as follows. These fault models provide an important basis and guidance to theoretical characterization and parameterization of delay faults for clockless wave pipeline in this dissertation as well as that of wave pipeline in general. There have been a few works proposed on synchronous wave pipeline design for reliability [57, 45, 12, 77], in which testing, characterization and parameterization of datapath-oriented delay faults were proposed. However, there is no adequate and extensive characterization and parameterization of the faults and yield for synchronous wave pipelines, nor for clockless wave pipelines either. This is a great hurdle for reliable wave pipelines to be realized. Therefore, it is imperative to develop formal methods for adequate and extensive modeling of delay-faults precisely from a datawaves' standpoint and at an integrated datawave level to be able to assure and optimize the yield in early design stage. Without such theoretical reliability assurance and optimization methods, ones precisely on integrated system level with

focus on the datawaves, there is no efficient and effective way of designing a reliable wave pipeline with fault tolerance.

### 1.4 Other Asynchronous/Clockless/Delay-Insensitive Circuit Design Techniques

Today, ever increasing attention is being paid to clockless circuits for the following outstanding advantages: saving on circuit area due to no global clock-timing; reduced power and heat dissipation; eliminating clock skew and global timing constraints; potentially improved performance over synchronous worst-case; and potentially more efficient migration and adaptation to new technology.

Various techniques have been proposed and researched to realize clockless (or asynchronous, delay-insensitive) circuits. Some of the most outstanding techniques are reviewed in the following.

Null-Convention-Logic is a technique to completely cover the entire range of signal state by introducing null state in addition to conventional true and false states. Having null state incorporated, NCL defines a new Boolean logic such that if any of inputs to a device is sensed as inactive (as defined by null state), its result outputs an inactive or null signal. This way, data signals can be self-synchronized by being able to discriminate active (or valid) and inactive (or null) data without reference to a clock (i.e., asynchronously) [44, 11, 40, 60, 36].

Self-Resetting is a technique to control data-in and out of latches via a self-resetting feedback signal self-generated by combinational circuit instead of via a clock-controlled synchronization signal. In entry-latch, a reset and reset-detection circuitry is placed to coordinate datain into the combinational circuit, and a feedback line is connected from exit-latch at the end of the combinational circuit [41, 69, 46, 53, 32, 39].

Opportunistic-Time-Borrowing is a semi-asynchronous technique to maximize the utilization of clock signals. Having clock-latch and no-clock-latch laid out alternately for data-signal synchronization, clock-latch (no-clock-latch) borrows a certain extent of no-clock (clock) period of time from subsequent no-clock-latch (clock-latch) as needed if the subsequent no-clocklatch (clock-latch) requires less no-clock (clock) period of time. To maintain the original functionality intact, any borrowed clock (no-clock) period of time is supposed to be paid back [21, 3, 9, 37, 62].

Micro-pipeline is a wave-pipeline technique to overcome the theoretical limit in speed and throughput of conventional clock-synchronous pipeline technique. The basic asynchronous operation is accomplished by a handshaking protocol in which two main signal lines (i.e., request and acknowledgement) coordinate and control datawaves without relying on any main clock. This technique is more widely understood and practiced for its simplicity of control [22, 55, 35, 64, 61, 63, 4, 47]; however, the overhead for heavy signaling for handshaking and only marginal performance gain opens an opportunity for the clockless wave pipeline technique under investigation in this chapter to achieve ultra-high performance through more technical challenge.

Regardless of the outstanding benefits asynchronous circuits can offer, there are still a few problems to be resolved before asynchronous circuits are extensively deployed in the commercial market. The following are the hurdles for asynchronous circuit designers to address and overcome: signaling overhead and complication for handshaking protocol in generic-type asynchronous circuits such as micropipelines [63]; less availability of CAD tools and standard for design, testing, and manufacturing, which hinders the asynchronous circuit design paradigm from extensive deployment and expansion [49, 50, 59]; potential algorithmic and hardware overhead and complication to resolve hazards for asynchronous and non-monotonic processing; lack and difficulty of theoretical method development to adequately address, assure, and optimize the performance; and no adequate theoretical modeling and assurance of reliability of asynchronous process on integrated system SoC level. The modeling, assurance and optimization technique for reliability in early design phase is key to the success of asynchronous circuits. In this context, this dissertation gives a great emphasis on the reliability modeling, assurance, and optimization of clockless circuits integrated at the datawave level in the early design phase.

#### **CHAPTER 2**

#### FAULT MODELS AND YIELD MODELING/ASSURANCE

In order to efficiently and effectively depart from the delay fault models of conventional synchronous wave pipelines, we propose two new fault models. The proposed Intra-Wave Fault Model is based on the Pulse Fault Model as proposed in our previous work [13]. Based on the intra-wave fault model, we further propose the Inter-Wave Fault Model [16] to provide a comprehensive yet essential understanding of the fault mechanism of a clockless wave pipeline. The proposed fault models are used as the theoretical basis for the proposed yield modeling, assurance and optimization method. Also, we take into account a synergistic fault model, in which specifically, delay faults on request signal lines are modeled together with the datawave delay faults, because correct association between datawaves and their request signals primarily determines the delay-oriented yield and reliability.

#### 2.1 Intra-Wave Fault and Yield

The path delay of a partial path can be represented as x. Suppose there are n such partial paths (i.e.  $x_1, \ldots x_n$ ) and assume those partial paths are assumed to be well balanced in the clockless wave pipeline under investigation. Also, without loss of generality, we may assume the path delay for  $x_i$  follows a Gaussian distribution with a mean  $\mu$  and a standard deviation  $\sigma$  as follows  $x \sim N(\mu\sigma^2)$ , relying on each path being composed of at least several logic elements contributing delay. Let  $\bar{x}$  be the sample mean, and s be the sample standard deviation.

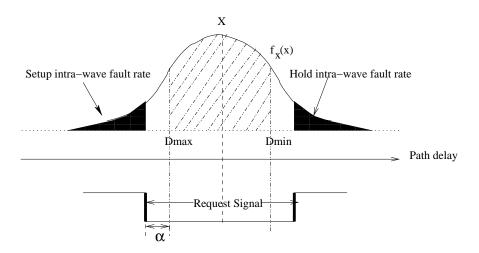

Then,  $\mu$  and  $\sigma$  can be substituted for with  $\bar{x}$  and s, respectively, because  $\bar{x}$  and s are unbiased estimators of  $\mu$  and  $\sigma x \sim N(\bar{x}s^2)$ . Suppose  $f_x(x)$  is the *p.d.f.* (probability density function) of x as follows,  $f_x(x) = \frac{1}{\sqrt{2\pi s}}e^{-\frac{(x-\bar{x})^2}{2s^2}}$ . By definition, the intra-wave fault is the probability that some bits in the datawave proceed too fast and then overstep their associated request level (i.e., the probability of a setup time fault); or some bits in the datawave are so slow that they lag behind the associated request level (i.e. a hold time fault) leaving some bits out of the range of the supposed-to-be-associated request level interval. Figure 2.1 shows the rate of the intra-wave fault as the integral of the shaded areas.

Figure 2.1: Intra-wave fault rate

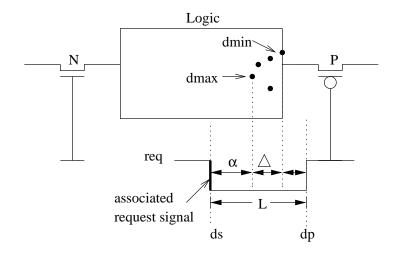

The request signal and all the data bits enter the circuit at the same time, and for proper operation the request signal should be slower than the slowest bit of the datawave, and reach the switch after the slowest bit. Likewise, the previous request signal should reach the switch before the fastest bit of the associated datawave. The data skew (represented by  $\triangle$  in Figure 2.3) is supposed to be covered by the associated request level properly. Therefore, the coverage of  $\triangle$  by the request level—i.e., the relative position between the datawave and its associated

Intra-Wave Fault

Figure 2.2: Detailed intra-wave fault

Figure 2.3: Relative position between the request signal and datawave

low or high request level-may influence the intra-wave fault rate to a great extent.

$\alpha$  refers to the difference of propagation time between the slowest bit of the datawave and the request level as shown in Figure 2.3. Thus, the associated request signal propagation delay (denoted as  $d_s$ ) can be expressed as  $d_s = d_{max} + \alpha$ . The propagation delay of the request signal pulse through the switch (denoted as  $d_p$ ) is  $d_p = d_{min} - (L - \alpha - \Delta)$ . Thus,  $L = d_s - d_p$ . The intra-wave fault rate at switch *i* is as follows:

$$P_{i} = 1 - \int_{d_{min_{i}} - (L - \alpha_{i} - \Delta_{i})}^{d_{max_{i}} + \alpha_{i}} \frac{1}{\sqrt{2\pi s}} e^{\left(-\frac{(x - \bar{x})^{2}}{2s^{2}}\right)} dx$$

(2.1)

Placing n switches in the circuit, each of which with  $P_i$ , the intra-wave fault rate at each switch where  $1 \le i \le n$ , the total intra-wave fault rate  $(P_{total})$  is as follows:

$$P_{total} = 1 - \prod_{i=1}^{n} (1 - P_i) = 1 - \prod_{i=1}^{n} (1 - \int_{d_{min_i} - (L - \alpha_i - \Delta_i)}^{d_{max_i} + \alpha_i} \frac{1}{\sqrt{2\pi s}} e^{(-\frac{(x - \bar{x})^2}{2s^2})} dx) \quad (2.2)$$

Therefore, the overall yield  $Y = 1 - P_{total}$ . Also, note that by using the proposed yield model, at each switch *i*, we see that theoretical optimum is achieved by setting  $\alpha_i$  to  $\frac{1}{2}(L - \Delta_i)$ .

#### 2.2 Inter-Wave Fault and Yield

In order to extensively assure and optimize the reliability of the clockless wave pipeline, delay faults between datawaves must be characterized and parameterized beyond the scope of the Intra-Wave Fault. A preliminary result was reported in [14]. The proposed inter-wave fault model reveals the effect of the proposed intra-wave fault in association with other primary delay-oriented factors, such as the request signal and inter-datawave relation.

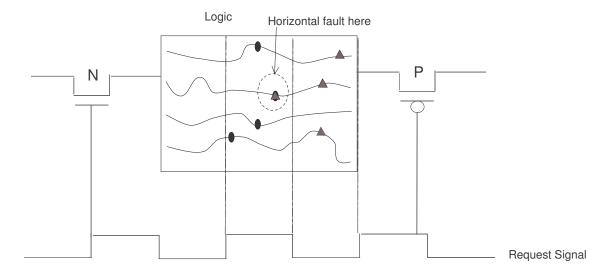

Delay faults can be viewed and modeled either vertically or horizontally at the moment when the bits of a datawave reach the opaque switches. Vertically, datawave-delay faults can occur within the scope of a datawave if its associated request signal goes out of association; this has the effect of an intra-wave fault. Horizontally along each data-path, if path delay faults occur, then data bits of two adjacent datawaves may collide and get invalidated across the scopes of the datawaves; this type of fault is referred to as Inter-Wave Fault, as proposed here.

The inter-wave fault observes the bits of datawaves at each switch, and thus facilitates the controllability and observability of datawave testing. Figure 2.4 demonstrates a snapshot of an occurrence of a delay fault hit on two adjacent bits on a data path (horizontally)—that is, an inter-wave fault.

Figure 2.4: Inter-wave fault as horizontal delay fault

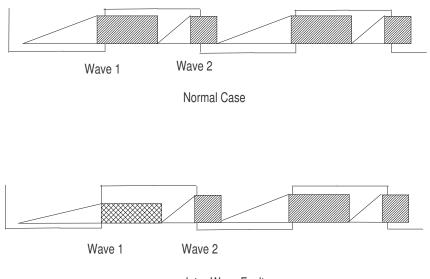

Figure 2.5 demonstrates a detailed occurrence of an inter-wave fault in a data signal pulse diagram between two datawaves (i.e., wave 1 and wave 2). Some bits of datawave 1 are overlapped with some other bits of datawave 2. Consequently the shape of datawave 1 becomes smaller than normal indicating that these bits are invalidated and lost. Notice that as shown in Figure 2.5, all the bits of datawave 1 arrive at the observation point (i.e., a switch) before the request signal arrives. Hence, the shrink in the shape of the datawave is not caused by out-of-

Figure 2.5: Signal transition diagram of inter-wave fault

Figure 2.6: Inter-wave fault as a subset of intra-wave fault

association between the datawave and its request signal, but by the as-observed overlapping of the bits in opposite transition. This distinguishes the inter-wave fault from the intra-wave fault, which is an out-of-association between a datawave and its supposed-to-be-associated request signal.

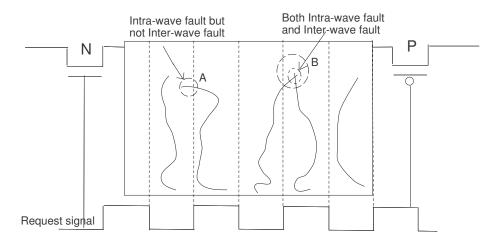

Notice that according to the theoretical definition of intra and inter-wave faults, we may

state that existence of an intra-wave fault is a necessary but not sufficient condition for an inter-wave fault to occur (i.e., inter-wave fault is a subset of intra-wave fault). Therefore, an accurate modeling and analysis of the co-relation and co-effect between the two datawave faults is needed for efficient and effective clockless wave pipeline design decisions and performance optimizations. If an inter-wave fault occurs, some of the faulty bits have to be out of association with its request level. This is illustrated in Figure 2.6. At A, the case where the intra-wave fault doesn't cause any inter-wave fault. At B, the two datawaves collide and cross each other to cause an inter-wave fault, where some bits of the datawave on the left hand side run too fast and break the association with its request signal and moreover collide and cross its neighboring datawave on the right had side.

Figure 2.7: Two bits, A (in falling transition) and B (in rising transition) on the same datapath

In Figure 2.7, we show two bits A and B on a data path, each of which belongs to a different datawave respectively and those two datawaves are adjacent in their sequence. Suppose bit A is the front-most bit in the datawave which is supposed to propagate behind the datawave with bit B as its rear-most bit. Then, a collision between bits A and B is equivalent to the Inter-Wave

Figure 2.8: Probability for two bits on the same datapath causing an inter-wave fault

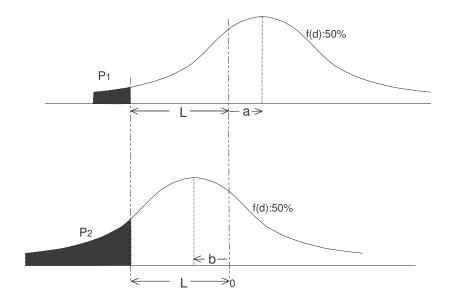

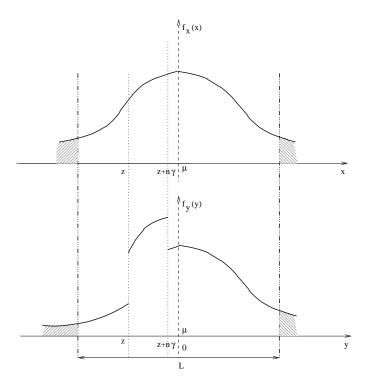

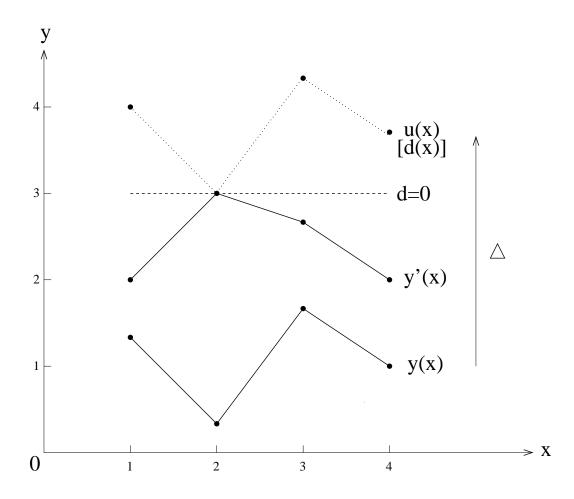

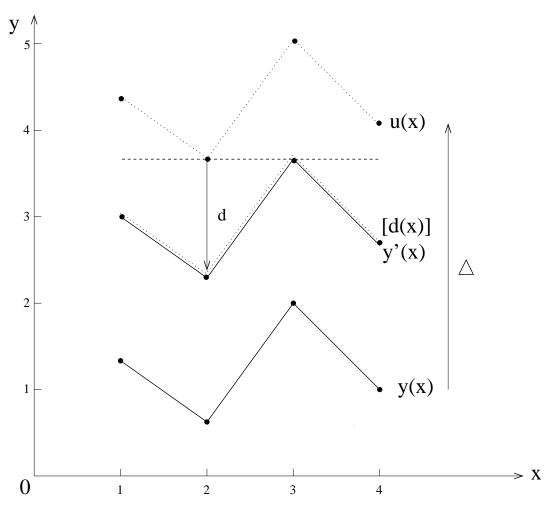

Fault by our definition. Without loss of generality, we make an assumption that the probability for each switch to observe an Inter-Wave Fault is independent from each other since inter-wave fault depends on the path delays through each partial circuit in between switches and the partial circuits are functionally and physically independent. Under the assumption, we can assume a random variable x with a Gaussian distribution to represent the delay of bit A; and another random variable y also with a Gaussian distribution to represent the delay of bit B. Then based on x and y, we can further assume a random variable d = x - y, and d also follows a Gaussian distribution without loss of generality. Thus, d represents the status of collision between bits A and B such that: (a) if d > 0 it indicates that there is no collision between bits A and B; (b) if d = 0 it indicates that bits A and B just collide at the intersection of the two datawaves they belong to; and (c) if d < 0 it indicates bit A surpasses bit B resulting in overlap between the two datawaves they belong to, that is the Inter-Wave Fault we propose.

Given the above random variables assumed, Figure 2.8 demonstrates the probability density

functions for inter-wave fault. Notice that the p.d.f. on the top represents the probability distribution to have the two bits A and B getting farther from each other due to an arbitrary delay variation as indicated by the shift of the average point in the positive direction from the original point at 0 by a; while the p.d.f. on the bottom represents the probability distribution to have the two bits A and B coming closer to each other due to another arbitrary delay variation as indicated by the shift of the average point in the negative direction from the original point at 0 by b. The L indicates the maximum difference, or the maximum value d, between bits A and B, either in positive or negative direction. Also, note that each p.d.f. accounts for 50% of the entire probability because without loss of generality we can assume that the probabilities for the two bits to get farther or closer are equal unless otherwise specified. The dark area in the p.d.f. on the top (i.e.,  $P_1$ ) represents the probability that bit B is going beyond the left-edge of its request level in the negative direction and thus will intersect and overlap with bit A; and vice versa (i.e.,  $P_2$ ) in the p.d.f. on the bottom. Thus, it shows that the farther the two bits get away, the smaller is the probability for inter-wave fault; and vice versa. Therefore, summation of the dark areas of each p.d.f. represents the total probability for the inter-wave fault (i.e., Pr(Inter-wave fault/switch) at each switch. The probability for inter-wave fault in the p.d.f. on the top is  $f_x(d_1) = \frac{1}{\sqrt{2\pi}S_{d_1}}e^{-\frac{(d_1-\bar{d_1})^2}{2S_{d_1}^2}}$  and that in the p.d.f. on the bottom is  $f_x(d_2) = \frac{1}{\sqrt{2\pi}S_{d_2}}e^{-\frac{(d_2-\bar{d_2})^2}{2S_{d_2}^2}}$ where note that  $d_1$  and  $d_2$  represent the d in each p.d.f.). Thus,  $P_1$  and  $P_2$  are as follows:  $P_1 = \int_{-\infty}^{-L-a} \frac{1}{\sqrt{2\pi}S_{d_1}} e^{-\frac{(d_1 - \bar{d_1})^2}{2S_{d_1}^2}} dd_1 \text{ and } P_2 = \int_{-\infty}^{-L+b} \frac{1}{\sqrt{2\pi}S_{d_2}} e^{-\frac{(d_2 - \bar{d_2})^2}{2S_{d_2}^2}} dd_2.$

Therefore, the total probability  $Pr(Interwave \ fault/switch) = P_1 + P_2$ . Suppose there are *n* such paths in a partial circuit, then the total probability for the inter-wave fault in each partial circuit (i.e.,  $Pr(Inter-wave \ fault/partial \ circuit)$ ) can be expressed as follows: Pr(Inter-

wave fault/partial circuit) =  $\prod_{i=1}^{n} P_i$  because delays on each data path are independent. Further, suppose there are m such partial circuits and let the Pr(Inter-wave fault/partial circuit) be  $P_j$ , then the total probability for the inter-wave fault in the whole clockless wave pipeline can be expressed as  $\Pr(Interwave fault/pipeline) = 1 - \prod_{j=1}^{m} (1 - P_j)$ . Therefore, the resulting yield  $Y = 1 - \Pr(Interwave fault/pipeline)$ .

#### 2.3 Request Signal Fault and Yield

Correct operation of a clockless wave pipeline is mainly determined not only solely by intra/interwave fault but also by the request signal faults. Datawaves are guided by the request signal; aligned at and by the P- and N-switches; and hence the request signal determines the correct propagation of datawaves. Therefore, the request signal is the primary signal in control of clockless wave pipeline processing. Any incorrect control over datawaves by request signal may cause a fatal error leading to data corruption. Hence, ensuring a fault-free request signal is a key to the successful realization of reliable clockless wave pipeline.

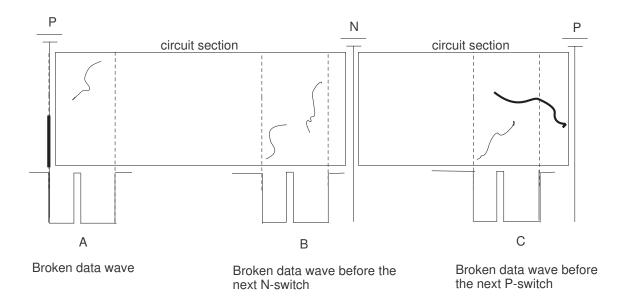

The Request Signal Fault of our interest is a glitch hit on the request signal due to crosstalk or power pulse noises [2, 17, 30]. In [23], it was reported that glitches can hit on the request signal created by a request signal generator. A glitch on a request signal breaks the datawave in association with it (either transient, permanently, or intermittently); the faulty request signal may instantaneously break the datawave at the instant the glitch hits, and let the head portion of the broken datawave propagate through the next switch where the broken datawave will be released earlier than the normal switch-blocking period of time. This broken datawave will Likewise, the tail portion of the broken datawave may suffer from any glitch hit on the request signal associated with the following datawave, also resulting in another inter-wave fault. The yield with consideration of the inter-wave fault caused by request signal faults can be evaluated by extending the proposed inter-wave fault model in the previous section. In this context and based on the proposed fault models and yield modeling/assurance methods, a solid method to ensure a fault-free request signal is proposed in the following section.

#### CHAPTER 3

#### FAULT TOLERANT DESIGN FOR REQUEST SIGNAL FAULTS

We propose two fault tolerant designs for clockless wave pipeline [15]: one targeting at request signal faults because the request signal is the most critical element for correct control over the datawaves and overall computation; and the other targeting at datawave faults because intra/inter-wave faults may still hit on the datawaves due to delay variations independent of request signal faults. The fault tolerant design for request signal will be addressed in Chapter 3, and the one for datawaves will be addressed in Chapter 4. The efficiency and effectiveness will be demonstrated by the proposed novel reliability and yield modeling and assurance techniques.

Request signal is a crucial control part of the pipeline. In practice, a request signal is highly sensitive and vulnerable to electronic crosstalk or power pulse noise (referred to as glitch). As the technology allows ultra-smaller device geometries, millions of closely spaced interconnections, and higher switching speeds, electronic crosstalk noise is very likely to occur; and it appears to be a major problem in the development of next generation high-speed integrated circuits [42][72][78] [79]. In general, the request signals are caused by various electrical and environmental factors such as voltage, temperature, humidity, etc. Crosstalk noises on request signals could be permanent, transient, or intermittent. Any type of glitch on the request signal is deleterious and may result in fatal datawave corruption.

In this chapter, inspired by the intrinsic properties of the two-phase pipeline, a unique, simple, but effective and low overhead technique is proposed to fault tolerate crosstalk noises

on request signal lines, to ensure fault-free request signals. Redundant hardware are introduced. Theoretical formulations are probed and explored to explain the technique mathematically and the simulation is conducted to demonstrate the effect of the proposed fault tolerance technique at the end.

# 3.1 Possible Effects of Crosstalk Noise on the Datawaves

In clockless wave pipeline circuit, crosstalk noises can occur on low or high request signals, and they could effect the regular control of request signal to N or P switches. There are four possible combinations between types of switch and noise altogether. In this section, each possible combination and their effects is analyzed in-depth, thus the solution proposed later to solve this request signal introduced fault problem can be easily comprehended.

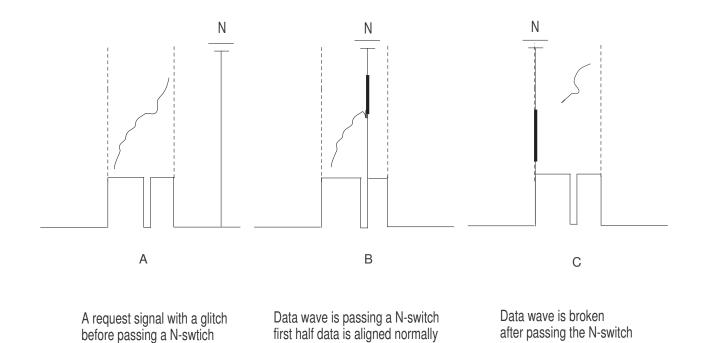

### 3.1.1 High Request Signal with Crosstalk Noise to Pass N Switch

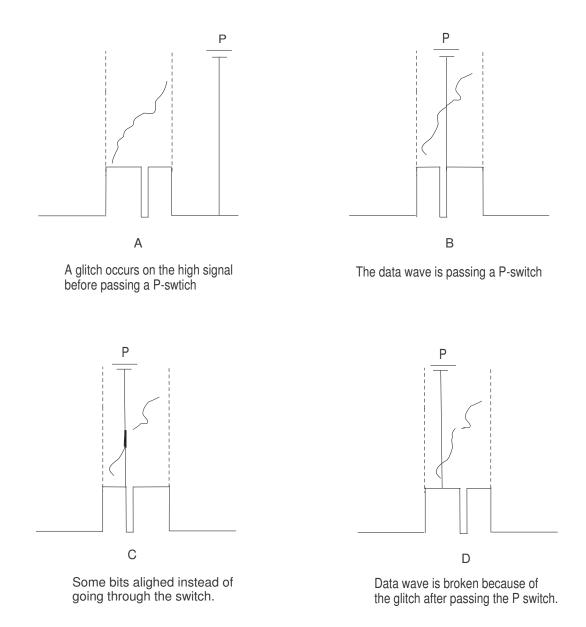

Figure 3.1 shows the instance of crosstalk noise resided high request signal and its associated datawave propagating a N switch. Part A depicts the fault-free situation before the datawave and request signal propagating through the N switch. As mentioned earlier, datawave associated with high request signal has to be latched at N switch, hence at part B in Figure 3.1, part of data bits are latched as normal until the crosstalk noise reach the N switch. The crosstalk noise has the complementary electronic signal value to the regular request signal and it mislead the switch, therefore, the switch switches from opaque state to transparent state immediately. Then the latched first half bits of the datawave are permitted to start to propagate in the next stage of circuit, which is improper since the first half bits start to propagate a lot earlier than designed. At this time, these bits could invalidate the previous datawave because the present bits propagation

Figure 3.1: Crosstalk noise on a high request signal with the N switch

conflicted with the design specification.

The width of crosstalk noises are very short compared with the length of request signal level, so the control signal switches back to normal request signal swiftly. The switch becomes opaque again and the remaining bits of the current datawave are latched by the opaque switch. At the end of this process, half of the data bits are propagating through the next circuit stage and half of them are latched at the current switch. There is a big gap between them and this data broken could causes fault because there may exist bits dependent in the process of bits propagation. Part C in Figure 3.1 portray this situation.

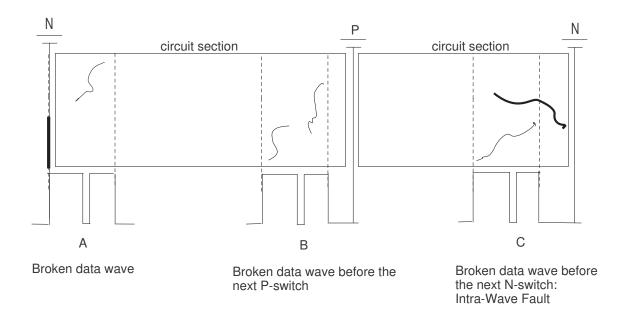

Broken datawave with big gap eventually causes Intra Wave Fault [13] (the CWP delay fault caused by improper cover of the datawave by the associated request signal level). Figure

Figure 3.2: Broken data on the N switch causing intra-wave fault

3.2 traces the broken datawave propagation from the break point to the fault point. Site A is position where the broken datawave was generated as discussed earlier. Site B displays the situation where the broken datawave reaches the next switch: a transparent P switch. Site C portrays the intra wave fault situation, where the first half datawave propagates too far and goes beyond its limit because of the unexpected earlier startup. Thus it can not be covered by its associated request signal level properly. The more specific explanation is that the first half data wave starts to propagate earlier than designed and its propagation speed remains unchanged despite the crosstalk noise and data broken, thus it reaches the next N switch earlier than normal after propagating through two circuit sections, while in the normal case, all data bits must arrive after the arrival of the frontier of the high request signal.

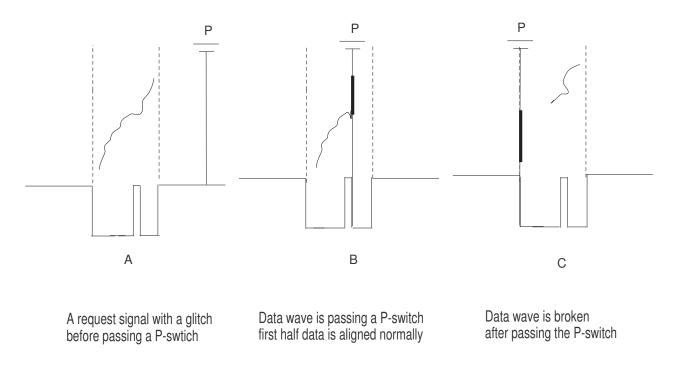

### 3.1.2 High Request Signal with Crosstalk Noise to Pass P Switch

The second combination is the crosstalk noised resided high request signal and P switch. Figure3.3 traces the propagation process. The crosstalk noise occurs at site A, before the datawave propagating through the P switch. According to the clockless wave pipelined circuit design rules, the P switch is transparent to the datawaves associated with high request signals. Thus, at site B, the datawave is propagating through the P switch without being latched. Site C depicts that the P switch switches to opaque to data wave and recovers rapidly since the crosstalk noise take the control of the P switch instantaneous. The temporary opaque section results a very small section of momentary data latching as shown in the site C, and in site D, this small section of latching datawave causes the tiny datawave broken.

It is important to notice that this tiny broken data does not bring any faults. The difference between this and the situation in the first combination is that this broken is caused by temporary latching other than temporary transparent, and temporary latching does not produce datawave's earlier startup as been discussed in the previous part. Since the width of the crosstalk noise is really small, the gap between the two parts of the datawave is also too small to cause any faults, even if bit dependence applied.

Note also if the crosstalk noises rate becomes excessive high, multiple single noises may unite into one big glitch. In that case, the temporary latching time is enlarged, and consequently the gap between the two parts of the broken data is broadened, then intra-fault could be possibly occurs. Fortunately, in reality crosstalk noise density is hardly to be so high. So, in this chapter, this combination is considered to be faulty free.

Figure 3.3: Crosstalk noise on a high request signal with P switch

# 3.1.3 Low Request Signal with Crosstalk Noise to Pass P Switch

This combination can cause fault. It is very similar to the first combination. Datawave associated with low request signal is latched by the P switch, and the crosstalk noise can broken the datawave with a big gap because of temporary transparent. At the next successive P switch, intra-wave fault and bits dependent fault then occur. This combination is described in Figure

3.4 and 3.5.

Figure 3.4: Crosstalk noise on a low request signal with P switch

### 3.1.4 Low Request Signal with Crosstalk Noise to Pass N Switch

The case is similar with the second combination. Crosstalk noise on low request signal before a N switch does not cause fault since temporary latching does not produce datawave's earlier startup and the tiny datawave broken does not cause bits dependent fault unless extremely excessive crosstalk noise density. The figure depicting this situation are omitted since it is same as Figure 3.3 except using N switch and low request signal instead of P switch and high request signal.

Up till now, the complete four combinations of request signals and the switches are investigated carefully, two of them, which are high request signal combined with N switch, low request

Figure 3.5: Broken data on P switch causing intra-wave fault

| Table 3.1: Fault cases                 |            |            |  |  |  |  |  |

|----------------------------------------|------------|------------|--|--|--|--|--|

| - N-switch P-switch                    |            |            |  |  |  |  |  |

| Crosstalk noise at high request signal |            | not faulty |  |  |  |  |  |

| Crosstalk noise at low request signal  | not faulty | faulty     |  |  |  |  |  |

signal combined with P switch are suspicious to results faults in the present of crosstalk noise. The other two combinations, which are high request signal combined with P switch, low request signal combined with N switch are reluctant to generate any faults even crosstalk noises stand on the request signal. This is summarized in Table 3.1.

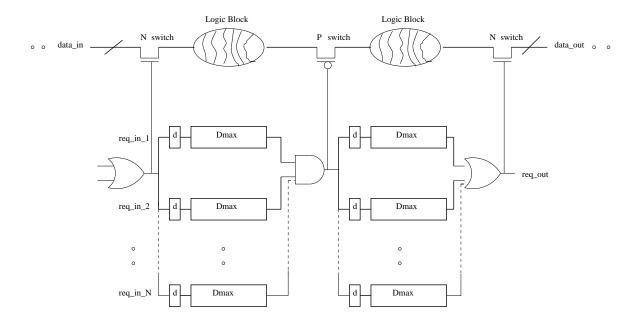

# 3.2 Fault Tolerant Design Approaches

According to the discussion of the interactive behavior of the data waves and switches under the present of faulty crosstalk noise in the previous section, redundant request line are introduced into the two-phase asynchronous wave pipeline architecture to mask the occurred crosstalk noise. The proposed method to ensure a fault-free request signal is Fault-Masking. The fault-

| Table 3.2: Truth table |                          |        |         |  |  |  |  |  |

|------------------------|--------------------------|--------|---------|--|--|--|--|--|

| А                      | В                        | A OR B | A AND B |  |  |  |  |  |

| (regular signal)       | (crosstalk noise signal) |        |         |  |  |  |  |  |

| high                   | low                      | high   | Х       |  |  |  |  |  |

| low                    | high                     | X      | low     |  |  |  |  |  |

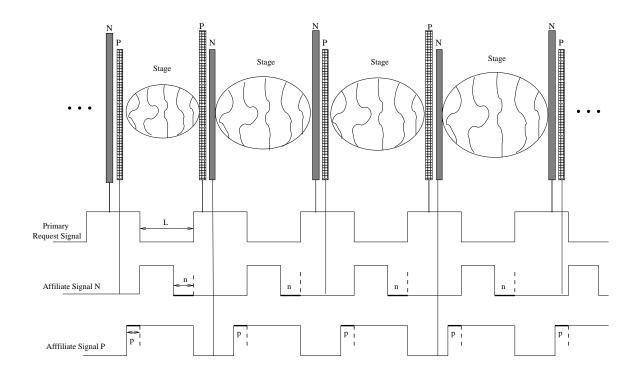

masking method is to employ redundant request signal lines and an AND and OR gate at each P and N switch, respectively. An implementation of the fault-masking architecture is shown in Figure 3.6.

An AND gate at a P switch will control the incoming datawave such that any low-glitch hit on the request signal is masked to the normal (i.e., high) value unless every request signal is hit by a low-glitch exactly at the same time (as illustrated in the upper row in Table 3.2; and vice versa in the case of an OR gate at an N switch (as illustrated in the lower row in Table 3.2. Note that the probability for an original request signal and all redundant ones to be hit by the glitches exactly at the same time is practically negligible. Hence, the proposed simple yet powerful fault-tolerant request signal method by using the fault-masking technique is efficient and effective.

Note not all crosstalk noises on the request signal can be hidden by this. The only condition where this fault mask technique fails is that both of the request signal A and B has crosstalk noises at the same time. In that case, another request line with accurate signal is needed to achieve a higher fault tolerance rate and more reliable system. By this means, the number of request line is expended to N so that the modified pipeline's reliability can be described and calculated theoretically in the next section.

Figure 3.6: Modified two-phase asynchronous wave pipeline with redundant request signal lines

# 3.3 Reliability Calculation

Assume  $\lambda$  is the rate that the crosstalk noise occurs on any request signal line from the signal entering the circuit to the signal arrives at the primary output of the circuit and assume the primary request signal line and redundant request signal lines share the same crosstalk noise rate.

### 3.3.1 Effectiveness of Multiple Request Signal Lines on Reliability

After the application of the redundant request signals, the crosstalk noises are masked away except crosstalk noises occurs at every request signal at the same time. so, the final fault rate on

the redundant request signal is:

$$\lambda_{total} = (\lambda \times \frac{l}{L})^N \tag{3.1}$$

where l is the minimum valid crosstalk noise width, and L is the length of one request signal section.

Thus, the total reliability of the request signal module is:

$$R(t) = e^{-(\lambda \times \frac{l}{L})^N \times t}$$

(3.2)

# 3.3.2 MTTG, $\lambda$ , and L

We propose a reliability model to thoroughly verify the effectiveness of the proposed faultmasking method. The model employs the Mean Time to Glitch (MTTG) to take into account and demonstrate the effect of the fault-masking on request signals at different levels of redundancy. Assume  $\lambda$  is the rate that a glitch hits on a request signal line during the period of time from the instant of time when the signal was submitted into the primary input of the circuit to the instant of time when the signal arrives at the primary output of the circuit. Also, assume that the primary request signal line and redundant request signal line(s) have the same glitch rate without loss of generality. Having the redundant request signal line(s) employed, the glitch can be masked off except when the glitches hit on all the request signals respectively at the same time.

Thus, the overall fault rate of the primary and redundant request signal(s) is  $\lambda_{effective} = (\lambda \times \frac{l}{L})$ , where *l* is the mean time width of a glitch's effect, and *L* is the length of the request signal; and the relative width  $(\frac{l}{L})$  of a glitch hit on the request signal pulse *L*, is practically

considered. Therefore, the effective reliability of N request signals inclusive of the primary and redundant one(s) is  $R(t) = e^{-(\lambda \times \frac{l}{L})^N \times t}$ . MTTG is the mean time for a high or low signal to propagate normally through the circuit before the first glitch hits. Hence, the MTTG can be modeled as follows:

$$MTTG = \int_0^\infty R(t)dt$$

=  $\int_0^{kL} R(t)dt$

=  $\int_0^{kL} e^{-\lambda t}dt$

=  $-\frac{1}{\lambda}e^{-\lambda kL} - (-\frac{1}{\lambda}e^{-\lambda(0)})$

=  $\frac{1}{\lambda}(1 - e^{-kL\lambda})$  (3.3)

where k is the *depth of wave-pipeline*, i.e., the number of request signal cycles needed for a data signal to propagate through a partial circuit before being aligned at a switch; thus kL is the total length of a request signal path within the partial circuit. Note that according to Equation (3.3) the glitch rate can impact MTTG significantly, and L can be derived as  $L = \frac{\ln(\lambda \times MTTG-1)}{k\lambda}$ . The expression for L can be used as a theoretical bridge between MTTG-induced request signal faults and intra/inter-wave faults; and is used as a primary driver to optimize the intra/inter-wave fault rate with respect to a request signal fault.

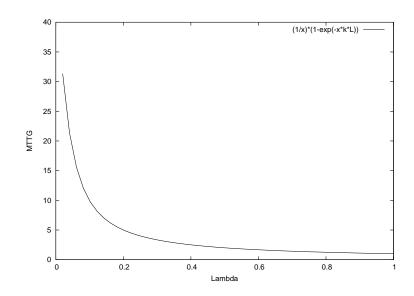

Equation 3.3 shown that crosstalk noise rate can influence MTTG in a great extents, the following Figure 3.7 is plotted based on equation 3.3 with the assumption of known parameter K, L, and it shows the decreasing trends of MTTG when the crosstalk noise rate increases.

Figure 3.7: MTTG is decreasing when the crosstalk noise rate increases

# 3.3.3 Reliability of the Redundant Request Signal Part at MTTG

The reliability of a single request signal at the time t is:

$$R(t) = e^{-\lambda t} [31] \tag{3.4}$$

Having MTTG theoretically identified, the reliability of a single request signal at MTTG [31] can be expressed as follows:

$$R(MTTG) = R(\frac{1}{\lambda}(1 - e^{-kL\lambda}))$$

$$= e^{-\lambda(\frac{1}{\lambda}(1 - e^{-kL\lambda}))}$$

$$= e^{(e^{-\lambda kL} - 1)}$$

(3.5)

The reliability of the request signal part of the whole circuit with N request signal lines is:

$$R_{total} = \sum_{i=1}^{N-1} \times N \times R^{N-i} \times (1-R)^{i} \times (1-P)$$

(3.6)

where  $P = \lambda^N$ .

The reliability of the whole request signal part at time point MTTG can be obtained by combining equation 3.5 and 3.6 and displays as follows.

$$R(MTTG) = \sum_{i=1}^{N-1} \times N \times R^{N-i} \times (1-R)^{i} \times (1-P)$$

=

$$\sum_{i=1}^{N-1} \times N \times (e^{(e^{-\lambda kL}-1)})^{N-i} \times (1-(e^{(e^{-\lambda kL}-1)}))^{i} \times (1-\lambda^{N}) \quad (3.7)$$

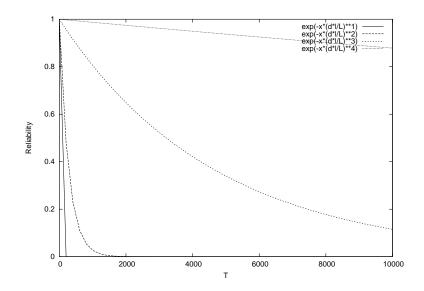

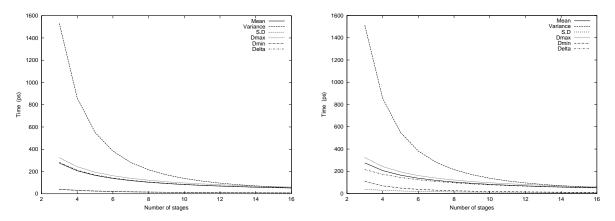

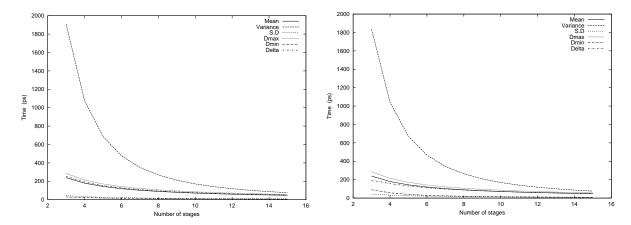

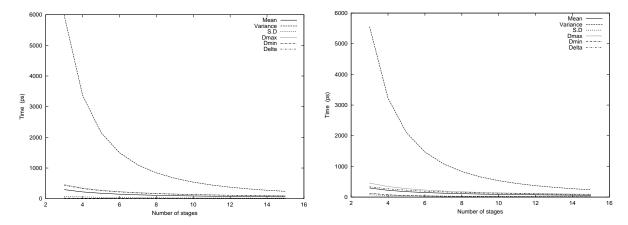

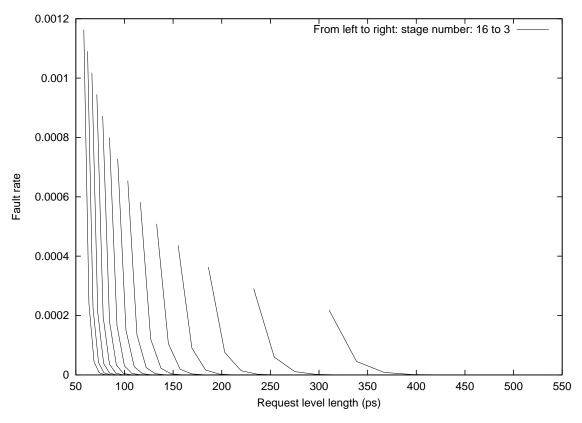

In Figure(3.8)  $R(MTTG)_{overall}$  is plotted for 1, 2, 3, and 4 request signal lines, respectively, and each with  $\lambda_{effective} = 0.06$ . It shows that the overall reliability is enhanced exponentially as the number of the redundant request signal lines increase. In practice, inclusion of an AND or OR gate, and widening that gate to accommodate more request signal lines, would mean a slight increase in the variance of the timing of the request signal, as perceived at a switch. So, this increase in variance would eventually limit how worthwhile the Fault Masking is.

# 3.4 Implementation Result

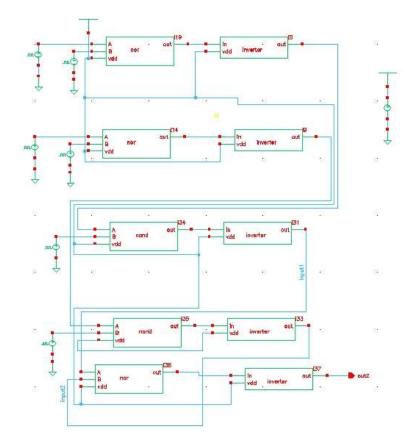

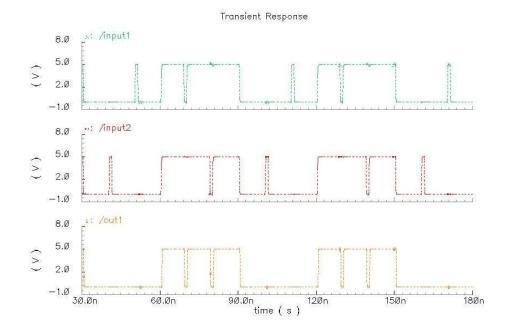

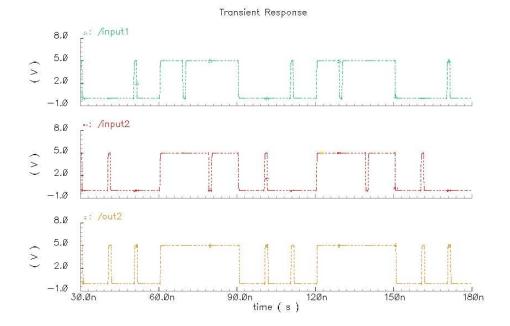

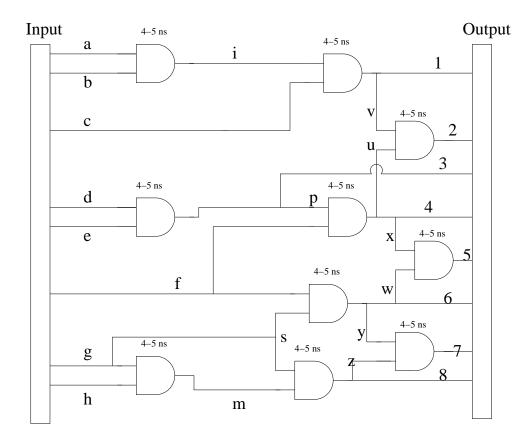

The circuit implementation is conducted using Cadence to verify the proposed fault tolerant technique. Two request signal lines with crosstalk noises are filtered by AND gate and OR gate respectively. They are then extracted and simulated using Spectre. The designed circuit is shown in Figure 3.9.

Figure 3.8: System reliability with 1,2,3,4 request signal lines

In Figure 3.10, *input*1 and *input*2 are the signals of the two request signal lines and crosstalk noises reside on them. The out signal shows that noises resided on the low request signal are successfully masked away by the AND gate. Although the noise density on the high request signal level double, as discussed in section 3.1, noises on the high request signal level for a P switch is harmless until the crosstalk noise density goes extremely high and in reality, that is hardly occur. Meanwhile the crosstalk noises accumulation can not happen since all the noises resided on high request signal level, including the original noises and the AND gate introduced noises, will be discard by the OR gate in the next successive N switch as shown in Figure 3.11. So there is no other faulty risk introduced by this technique.