### UNIVERSITY OF OKLAHOMA

## GRADUATE COLLEGE

# DIGITAL SIGNAL PROCESSOR BASED REAL-TIME PHASED ARRAY RADAR BACKEND SYSTEM AND OPTIMIZATION ALGORITHMS

A DISSERTATION

## SUBMITTED TO THE GRADUATE FACULTY

in partial fulfillment of the requirements for the

Degree of

DOCTOR OF PHILOSOPHY

By

XINING YU Norman, Oklahoma 2017

## DIGITAL SIGNAL PROCESSOR BASED REAL-TIME PHASED ARRAY RADAR BACKEND SYSTEM AND OPTIMIZATION ALGORITHMS

## A DISSERTATION APPROVED FOR THE SCHOOL OF ELECTRICAL AND COMPUTER ENGINEERING

BY

Dr. Yan Zhang, Chair

Dr. Robert Palmer

Dr. Nathan Goodman

Dr. Joseph Havlicek

Dr. S. Lakshmivarahan

© Copyright by XINING YU 2017 All Rights Reserved.

## Acknowledgements

I extend deep thanks to my academic advisor, Professor Zhang Yan (Rockee), for his invaluable insight and guidance during my entire graduate study at the University of Oklahoma. In Chinese, there is an old saying—One day as a teacher, father for life. Dr. Zhang is a reasonable explanation of those words. He uses his thoughtful, kindness, and wisdom guiding his fresh-off-the-boat students when they arrived on this new continent. It would be my pleasure to know Dr. Zhang, and learn from him both in academic and daily life.

As members of the Intelligent Aerospace Radar Team in the Advanced Radar Research Center (ARRC), Pan Yu, Sudantha Perera, and Nepal Ramesh provided valuable insight in conversations about our research. Many thanks go out to the rest of my faculty committee: Robert Palmer, Joseph Havlicek, Nathan Goodman, and Sivaramakrishnan Lakshmivarahan. This research was funded by NOAA-NSSL and conducted in ARRC. The state-of-art equipment and comfort working environment provide by ARRC would also be a supportive factor that makes sure our research going well.

In the end, I would also like to recognize the support and encouragement of my parents and my wife. They are my beloved ones.

## **Table of Contents**

| 1. | Int  | troduction                                                 | . 1 |

|----|------|------------------------------------------------------------|-----|

|    | 1.1. | Introduction of Phased Array Radar                         | . 1 |

|    | 1.2. | Challenge and Requirements of Multi-functional PAR Backend | .4  |

|    | 1.3. | Emerging Technologies for Digital Backend System           | 10  |

|    | 1.4. | Comparison of DSP, FPGA, and GPGPU                         | 13  |

|    | 1.5. | Outline of Dissertation                                    | 15  |

| 2. | Sig  | gnal Processing Algorithms and Processing Chain            | 19  |

|    | 2.1. | Introduction                                               | 19  |

|    | 2.2. | Digital Beamforming                                        | 23  |

|    | 2.3. | Pulse Compression                                          | 29  |

|    | 2.4. | Doppler Processing and Data Corner Turn                    | 31  |

|    | 2.5. | Weather and Air-surveillance Data Products                 | 32  |

|    | 2.5  | 5.1. Mean Velocity Estimation                              | 32  |

|    | 2.5  | 5.2. Spectrum Width Estimation                             | 33  |

|    | 2.5  | 5.3. Target Tracking                                       | 34  |

|    | 2.6. | Advanced Algorithms                                        | 42  |

|    | 2.6  | 5.1. Model-Based Algorithms and System Optimizations       | 42  |

|    | 2.6  | 6.2. Compressive Sensing for Channel Data Rate Reduction   | 45  |

|    | 2.6  | 5.3. System Optimizations                                  | 50  |

|    | 2.6  | 5.4. Target Direction Estimation                           | 62  |

| 3. | Sy   | stem Architectures                                         | 69  |

|    | 3.1. | Parallelization Model                                      | 72  |

|    | 3.2. | Data Transportation and Backend Protocol       | 78  |

|----|------|------------------------------------------------|-----|

|    | 3.3. | Processing Units                               | 86  |

|    | 3.4. | System Synchronization                         | 89  |

|    | 3.4  | I.1. General Calibration Procedure             | 89  |

|    | 3.4  | I.2. Backend Synchronization                   | 92  |

|    | 3.5. | System Performance Evaluations                 | 96  |

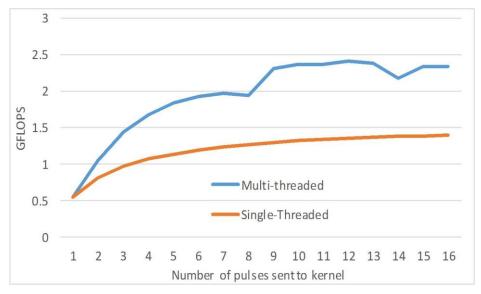

|    | 3.5  | 5.1. FFT performance                           | 98  |

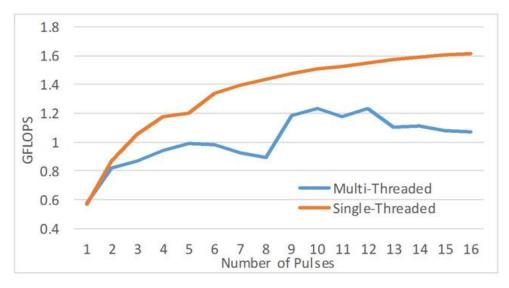

|    | 3.5  | 5.2. Weighted Dot Multiplication               | 101 |

|    | 3.5  | 5.3. Data Corner Turn                          | 106 |

| 4. | An   | Example System Implementation                  | 109 |

|    | 4.1. | Architecture Design Considerations             | 109 |

|    | 4.2. | Vendor Selections                              | 113 |

|    | 4.3. | Processing Chain Implementation Details        | 115 |

|    | 4.4. | Benchmark Results                              | 118 |

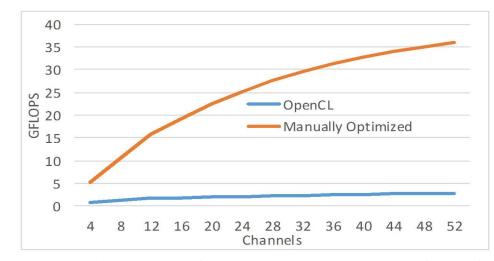

|    | 4.5. | Comparison with OpenCL                         | 119 |

|    | 4.6. | Summary                                        | 122 |

| 5. | Su   | mmary and Future Plans                         | 125 |

|    | 5.1. | Considerations of Future Architecture Design   | 127 |

|    | 5.1  | .1. System fault-tolerance                     | 128 |

|    | 5.1  | .2. Scalability                                | 130 |

|    | 5.1  | .3. Cost                                       | 131 |

|    | 5.2. | Future Works                                   | 132 |

|    | 5.2  | 2.1. Optimal task and communication scheduling | 133 |

|    |      |                                                |     |

|       | 5.2.2. Cognitive Radar | 134 |

|-------|------------------------|-----|

| 6.    | References             | 137 |

| Abbre | viation                | 149 |

## List of Tables

| Table 2.1: Computational Complexity for Signal Processing Kernels    |

|----------------------------------------------------------------------|

| Table 2.2: Doppler filtering performance measured in GFLOPS per core |

| Table 2.3: Tracking simulation parameters    39                      |

| Table 2.4: Parameters used in the MUSIC    65                        |

| Table 2.5: Assumption parameters used in the DOA algorithms    66    |

| Table 3.1: Typical COTS Interconnection Fabrics                      |

| Table 3.2: DSP core performance after mitigating cache misses    105 |

| Table 3.3:Time consumption of corner turn for one beam               |

| Table 4.1: Example of PAR system parameters    111                   |

| Table 4.2: Communication Data Rate per Stage    111                  |

# List of Figures

| Figure 1.1: Simplified TR channel diagram for a PAR system                                 |

|--------------------------------------------------------------------------------------------|

| Figure 1.2: CPPAR demonstrator operated by OU-ARRC                                         |

| Figure 1.3: Cost-effectiveness and power efficiency comparison                             |

| Figure 2.1: Canonical front-end and back-end architecture of an HPEC application 19        |

| Figure 2.2: Overview of data cube processing chain in a general PAR 20                     |

| Figure 2.3 : Illustration of large-scale PAR overall software system diagram               |

| Figure 2.4: Output SNR of the new beamforming method versus SNR of traditional             |

| beamforming method                                                                         |

| Figure 2.5: Output SNR versus loading level                                                |

| Figure 2.6: Reconstruction error vs SNR using CS algorithm                                 |

| Figure 2.7: Computational time comparison of two CS algorithms on AMD Opteron              |

| 6128/MATLAB regarding to different degrees of signal sparsity                              |

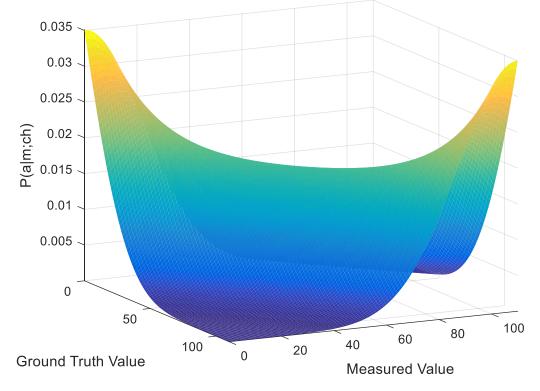

| Figure 2.8: Initialization example for <i>Pam; ch</i>                                      |

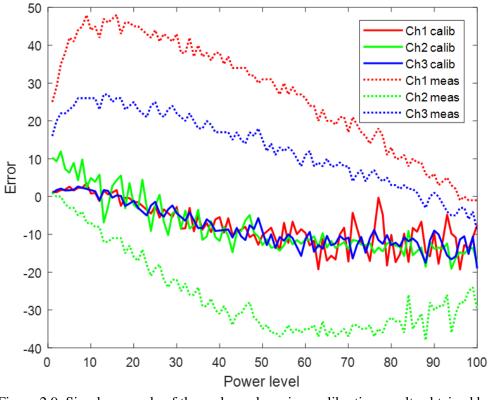

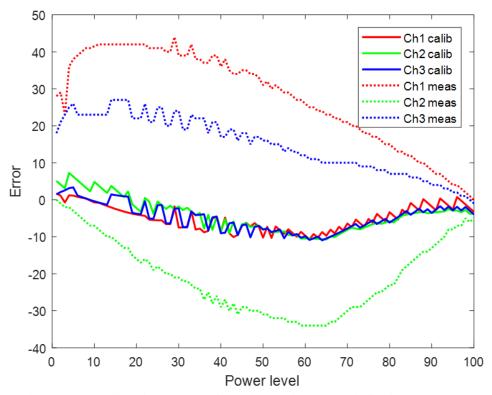

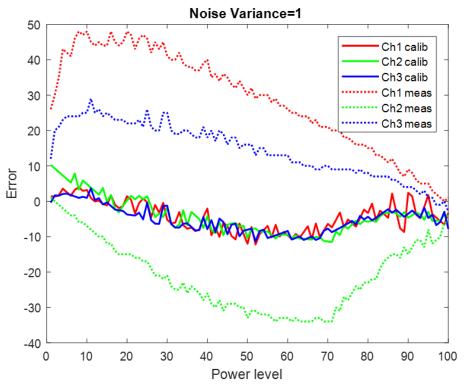

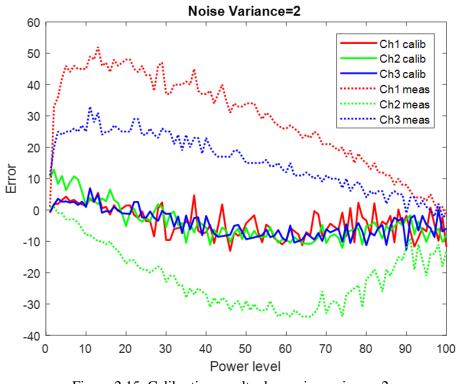

| Figure 2.9: Simple example of three-channel receiver calibration results obtained by       |

| using EM self-calibration algorithm                                                        |

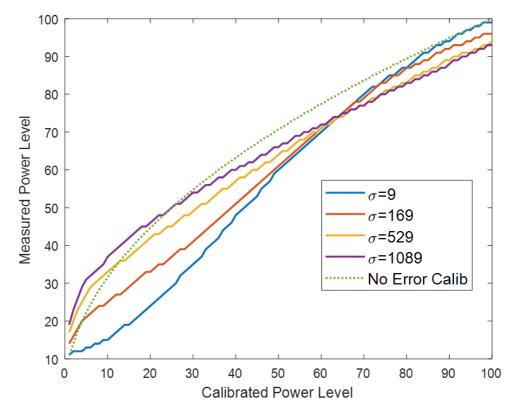

| Figure 2.10: Comparison of calibration results based on various initial conditions. (The   |

| dash line is the measurement value vs truth level. The solid line is the measured level vs |

| calibration result from three different values of $\sigma$ .)                              |

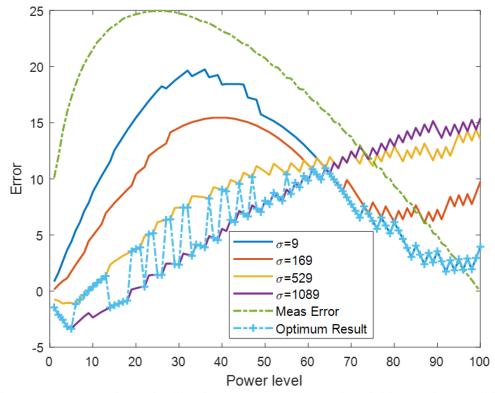

| Figure 2.11 Optimization Procedure                                                         |

| Figure 2.12: Comparison of calibration results based on various initial starting condition |

| and optimum finding result                                                                 |

| Figure 2.13: Calibration results after using optimum result finding procedure              |

| Figure 2.14: Calibration result when noise variance=1                                    |

|------------------------------------------------------------------------------------------|

| Figure 2.15: Calibration result when noise variance=2                                    |

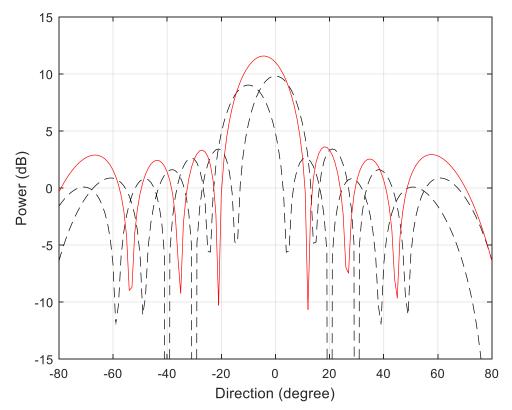

| Figure 2.16: Composite beam response for two signals at 10 and 0 degree. The dashed      |

| curves are the responses to the individual signals, and solid curve is the composite     |

| response                                                                                 |

| Figure 3.1: Top-level system digital array system concept                                |

| Figure 3.2: Illustration of the MTCA architecture in a PAR71                             |

| Figure 3.3: (a) Partition input and output matrices into $2 \times 2$ submatrices. (b) A |

| decomposition of matrix multiplication into four tasks based on (a)                      |

| Figure 3.4: Example of Parallel Quicksort                                                |

| Figure 3.5: Ping-Pong Buffering Mechanism74                                              |

| Figure 3.6: Examples of round-robin and pipeline scheduling75                            |

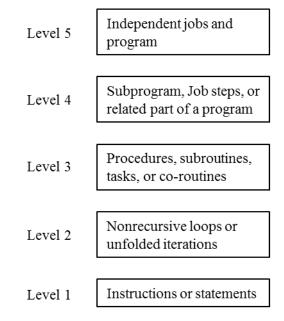

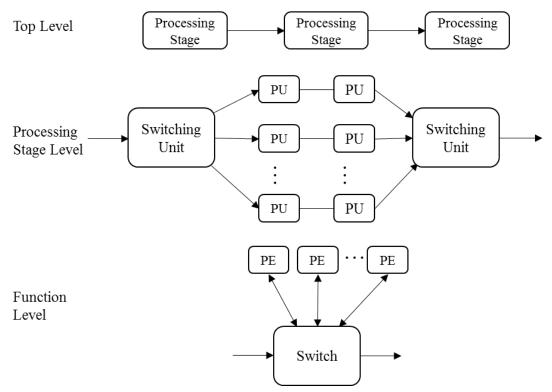

| Figure 3.7: Levels of parallelism                                                        |

| Figure 3.8: Typical interconnection fabric                                               |

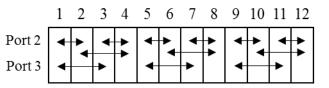

| Figure 3.9: MTCA backplane configuration                                                 |

| Figure 3.10: point to point connectivity between port 2 and 3                            |

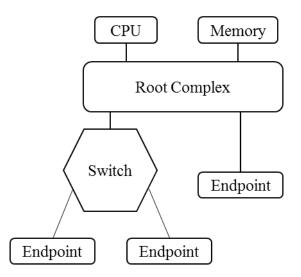

| Figure 3.11: Typical PCI Express system topology                                         |

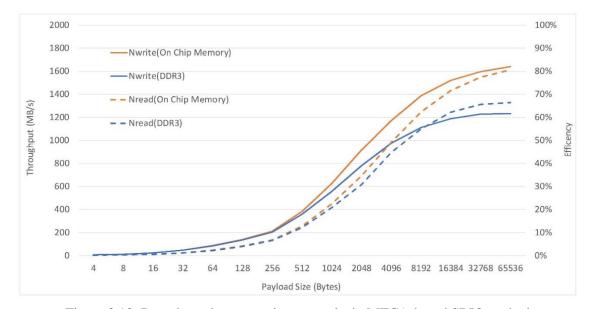

| Figure 3.12: Data throughput experiment results in MTCA-based SRIO testbed               |

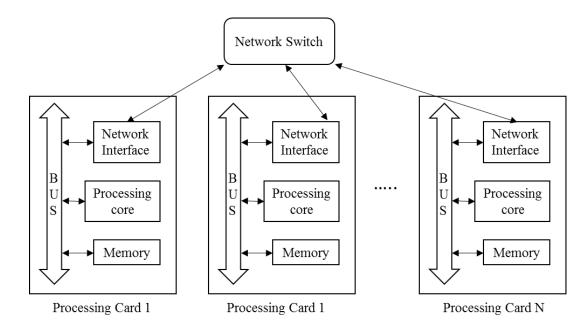

| Figure 3.13: MTCA based processing unit                                                  |

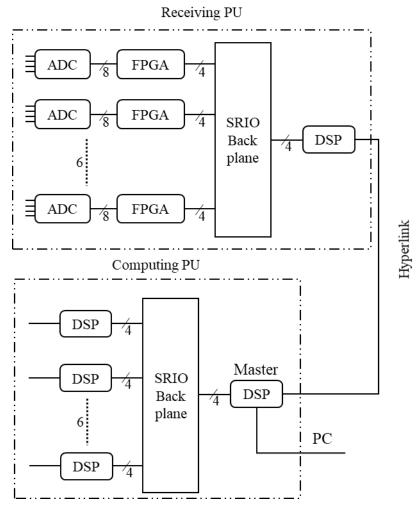

| Figure 3.14: Simple example of a PU-based architecture                                   |

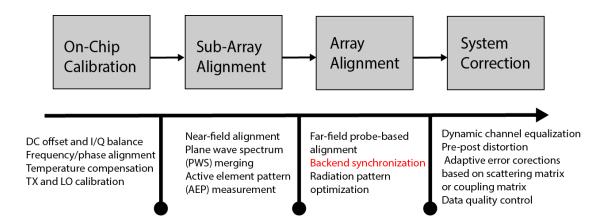

| Figure 3.15: General system calibration procedure for DAR and the focus of this work     |

|                                                                                          |

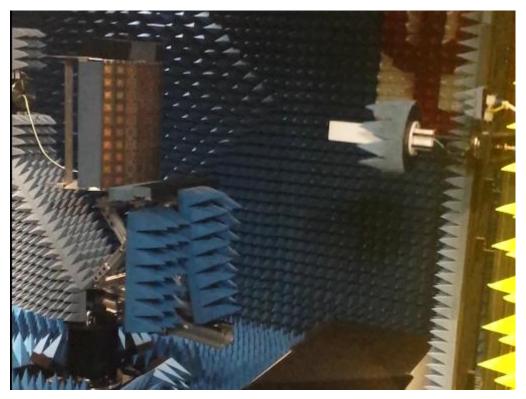

| Figure 3.16: Measurement of radiation pattern from a phased array antenna at the near- |

|----------------------------------------------------------------------------------------|

| field range                                                                            |

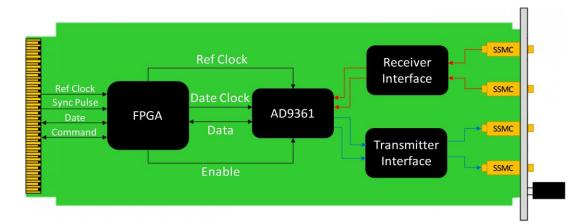

| Figure 3.17: PU frontend AMC module architecture                                       |

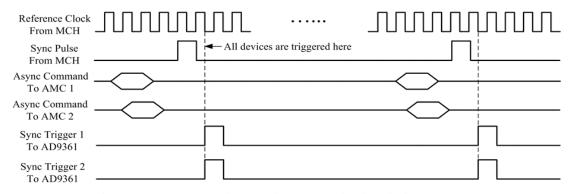

| Figure 3.18: Frontend in-chassis synchronization timing sequence                       |

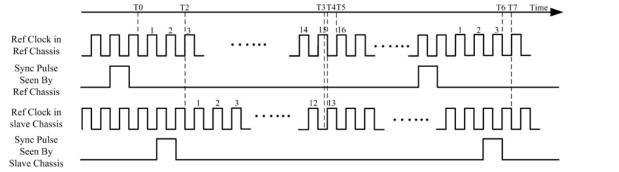

| Figure 3.19: Example timing sequence of multi-chassis synchronization                  |

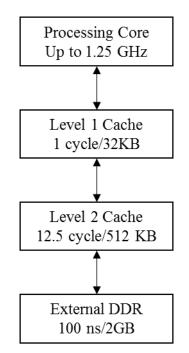

| Figure 3.20: TI C66x DSP Hierarchical Cache                                            |

| Figure 3.21: FFT performance for different range gate numbers                          |

| Figure 3.22: L1D cache architecture 102                                                |

| Figure 3.23: Weighted Dot Product Example 103                                          |

| Figure 3.24: Memory Layout after two iterations 104                                    |

| Figure 3.25: Computing performance of a DSP-core versus the number of range gates      |

|                                                                                        |

| Figure 3.26: An illustration of front-end data transmission strategy 107               |

| Figure 4.1: System Network Topology 109                                                |

| Figure 4.2: Clock Synchronization classification112                                    |

| Figure 4.3: An example of front-end processing platform 115                            |

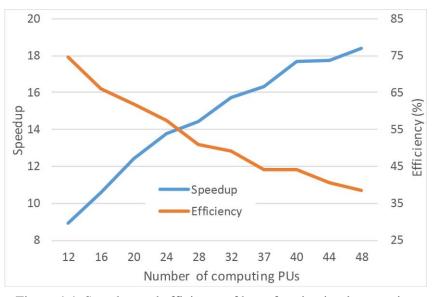

| Figure 4.4: Speedup and efficiency of beamforming implementation 117                   |

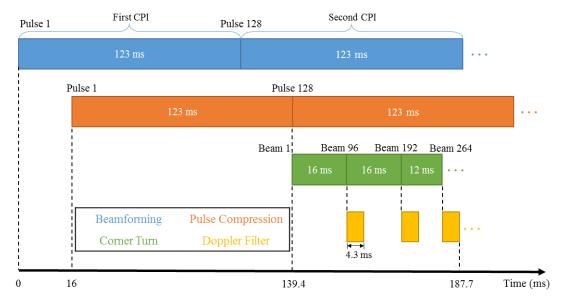

| Figure 4.5: Real-time system timeline for the example backend system 118               |

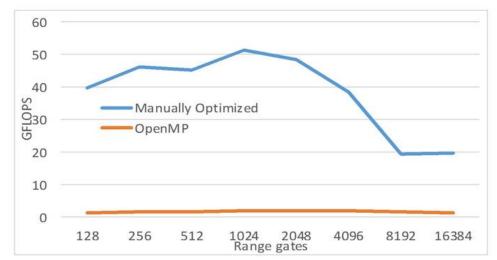

| Figure 4.6: Beamforming kernel performance using Open CL 120                           |

| Figure 4.7: Comparing OpenCL performance to manually optimized code for                |

| beamforming121                                                                         |

| Figure 4.8: Pulse compression performance using OpenCL (8192 range gates) 122          |

| Figure 4.9: Comparing OpenCL performance to manually optimized code | for pulse |

|---------------------------------------------------------------------|-----------|

| compression                                                         | 122       |

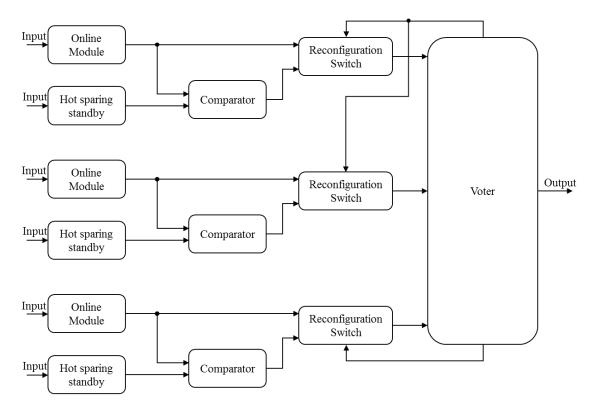

| Figure 5.1: The triple-duplex approach to redundancy                | 129       |

| Figure 5.2: Data flowing graph in PAR frontend                      | 131       |

| Figure 5.3: Processing cycle of a cognitive radar                   | 135       |

#### Abstract

This dissertation presents an implementation of multifunctional large-scale phased array radar based on the scalable DSP platform.

The challenge of building large-scale phased array radar backend is how to address the compute-intensive operations and high data throughput requirement in both front-end and backend in real-time. In most of the applications, FPGA or VLSI hardware are typically used to solve those difficulties. However, with the help of the fast development of IC industry, using a parallel set of high-performing programmable chips can be an alternative. We present a hybrid high-performance backend system by using DSP as the core computing device and MTCA as the system frame. Thus, the mapping techniques for the front and backend signal processing algorithm based on DSP are discussed in depth.

Beside high-efficiency computing device, the system architecture would be a major factor influencing the reliability and performance of the backend system. The reliability requires the system must incorporate the redundancy both in hardware and software. In this dissertation, we propose a parallel modular system based on MTCA chassis, which can be reliable, scalable, and fault-tolerant.

Finally, we present an example of high performance phased array radar backend, in which there is the number of 220 DSPs, achieving 7000 GFLOPS calculation from 768 channels. This example shows the potential of using the combination of DSP and MTCA as the computing platform for the future multi-functional large-scale phased array radar.

### 1. Introduction

#### 1.1. Introduction of Phased Array Radar

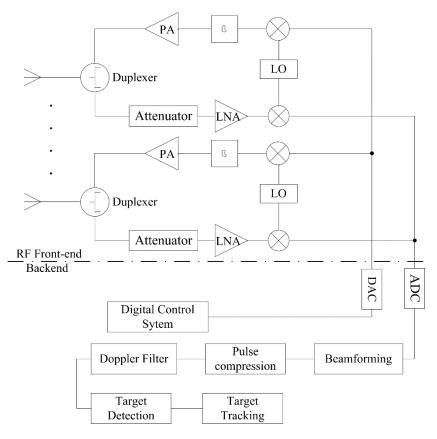

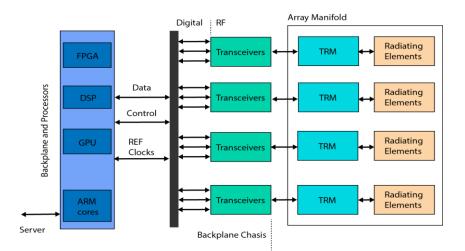

Phased Array Radar (PAR) is an electronically scanned array with multiple numbers of antennas. Compared with traditional mechanical beam steering radar, PAR can generate a focused beam by applying a weight to each antenna and the beam direction can be steered by adjusting the weights. Figure 1.1 shows a simplified transmit-receive (TR) channel diagram for a modern PAR. The overall PAR system comprises three sections: a phased array antenna manifold, an RF front-end, and a processing backend. The array manifold contains a number of radiating elements, which can be different types of antennas. The shape of array manifold can be linear, planar, or conformal. The linear and

Figure 1.1: Simplified TR channel diagram for a PAR system

planar arrays have been widely used in military and civilian applications for many years, which is more mature than the conformal array. However, circular or cylindrical arrays have found many applications in communications, direction finding, missile guidance and recently in weather radars. RF front-end is responsible for the signal generating, signal transmitting and receiving, and up/down converting. In digital PAR systems, the radar pushes the backend system closer to the antennas. Such front-end systems are mixed-signal systems responsible for transmitting and receiving radio frequencies (RF), digital in-phase and quadrature (I/Q) sampling, and channel equalization that improves the quality of signals. An example application is the Space Fence test facility built by Lockheed Martin. The radar system in this facility is fully digital array composed by multiple numbers of front-end transmit-and-receive line-replaceable unit [1]. Meanwhile, digital PAR backend systems control the overall system, prepare to transmit waveforms, transform received data for use in a digital processor, and process data for other functions, including real-time calibration, beamforming, and target detection/tracking.

As the RF front-end becomes more digitalized and the increased performance of backend processing units, Multifunctional Phased Array Radar (MPAR) is more feasible by programmable RF and processing parallelization. This improvement makes possible to combine multiple types of radar in one unit, which is also a way to enhance the efficiency of spectrum utilization. For example, current U.S. government operates several unique types of radars that provide weather, air traffic control, and homeland defense missions. It is possible to reduce the total number of radars and spectrum footprints with a single network of MPAR, which could potentially save billions of dollars [2]. Moreover, the electronically scanned antennas can reduce the maintenance cost over mechanically steered antennas by the absence of moving parts, and the radar system would be still functional even if 20% of the TR modules fail [3]. With the fast development of commercial wireless industry, various companies and agencies made their RF equipment and required them to work on a stand-alone spectrum to avoid the interference. Therefore the spectrum becomes crowded and makes the spectrum a highly-priced product in the market. For example, a 65 MHz of spectrum in L-band are sold by \$45 billion in 2015 [4]. Although the defense or national weather radars have the privilege of using some specific spectrum, if government choose to move the working spectrum out of a crowded area, they can use the selling money to update their system without raising fund from other places. Thus, the MPAR would be a feasible, reliable and cost-effectiveness system.

Many types of research have begun in academia, industry, and government to identify technical challenges and risks, and demonstrate their technologies for needs from both weather and the airport surveillance. MIT Lincoln laboratory had a concept study for the requirement of the aircraft surveillance and weather observation [5], in which it purposed a planar PAR with four antenna faces. Each face contains roughly 20,000 elements with 10 Watts peak power. In 2015, MIT Lincoln lab had built a 10-panel prototype array with the dual-polarization capability to refine system requirements and to quantify performance for weather observations. This prototype has 640 elements with 3.5 kilo-Watts peak power at antennas, working at S-band [6]. As mentioned before, the problem of using planar array in the dual polarization application is  $E_{\nu}$  and  $E_h$  are skewed when beam is not perpendicular to the array face. At the meantime, the Cylindrical Polarimetric Phased Array (CPPAR) has recently been introduced for MPAR. In the University of Oklahoma, a demonstrator of the CPPAR is designed by Advanced Radar

Research Center (ARRC) to prove the concept of polarimetric measurements of actual weather and demonstrating a multi-functional PAR. CPPAR has 1824 elements separated into 96 columns. Each column has 80 Watts peak power, working at 2900 MHz. Figure 1.2 shows the picture of CPPAR currently operated by ARRC.

Figure 1.2: CPPAR demonstrator operated by OU-ARRC

#### 1.2. Challenge and Requirements of Multi-functional PAR Backend

The concept of MPAR is associated with many technical challenges which remain to be solved. This work mainly focuses on the backend aspect. A canonical PAR processing platform contains a front-end component that performs basic array signal processing, which requires relative easy but a significant amount computing throughput. A more advanced backend performs knowledge-based processing requires complex operations but the relatively small amount of computing throughput. For example, [5] proposed a 400-channel PAR with 1 ms pulse repetition interval (PRI); assuming 8,192 range gates, each range sample uses 8 bytes length in memory. For each PRI, the throughput in the front-end can reach up to 5.24 GB/s. As the requirements for such data throughput are extraordinarily demanding, at present, such computing performance requires digital I/Q filtering to be mapped to a fixed set of gates, look-up tables, and Boolean operations on the field-programmable gate array (FPGA) or very-large-scale integration (VLSI) with the full-custom design [7]. After front-end processing, data are sent to the backend system, in which more computationally intensive functions are performed. Compared with FPGA or full-custom VLSI chips, programmable processing devices such as digital signal processors (DSPs) offer a high degree of flexibility, which allows designers to implement algorithms in a general-purpose language (e.g., C) in backend systems. For application in aerospace surveillance, target detection and tracking are thus performed in the backend. Target tracking algorithms, including the Kalman filter and its variants, predict future target speeds and positions by using Bayesian estimation [8], whose computational requirements vary according to the format and content of input data. Accordingly, detection and tracking functions require processors to be more capable of logic and data manipulation, as well as complex program flow control. Such features are different from those of baseline radar signal processors, in which the size of data involved dominates the throughput of processing [9]. As such, for tracking algorithms, a general purpose processor or Graphics Processor Unit (GPU)-based platform is more suitable than FPGA or DSP. In summary, in radar backend processing, hybrid solutions need to be developed that exploit the advantages of each type of processor units.

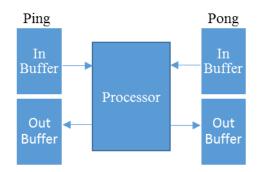

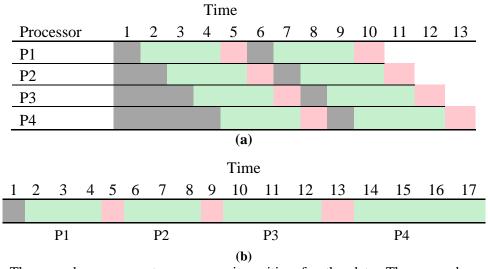

Normally, the hybrid backend system is based on a modular design concept, in which one or more processors are placed in one extension card. The modular architecture is scalable, which allows the sub-system to be upgraded with minimal impact on the overall system. However, the drawback of modular architecture is the communication requirement among the extension cards and the complexity of software design when the granularity of processing becomes small. The granularity of processing is defined according to the size of a processing assignment that forms a part of the entire task. Although finer granularity allows designers to attune the processing assignment, it also poses the disadvantage of increased communication overhead within each unit [10]. To balance computation load and real-time communication in one extension card, the ratio of the number of computation operations to communication bandwidth needs to be checked carefully. For example, in a 6678 Evaluation Module (Texas Instruments), which has eight C66xx DSP cores, contains 24 DSP cores and four ARM cores in a single board. Texas Instruments claims that each C66xx core has 16 Giga floating point operation per second (GFLOPS) at 1 GHz [11]. On this board, it has four-lane SRIO (Gen 2) link, which has a theoretical link speed up to 1,600 MB/s in NWrite mode; since the single-precision floating point format (IEEE 754) [12] occupies 4 bytes in memory, the SRIO link convoys 400 million floating point data per second. The ratio of computation to bandwidth is 40 [8], meaning that the core can perform up to 40 floating point operations for each piece of data that flows into the system without halting the core-to-core communication link. As such, when the ratio reaches 40, the processor achieves an optimal balance between real-time computing and communication. To achieve this optimization and efficiency,

technologies needed are optimized algorithms, computing resources optimization, and ensuring that I/O capacity reaches its peak level.

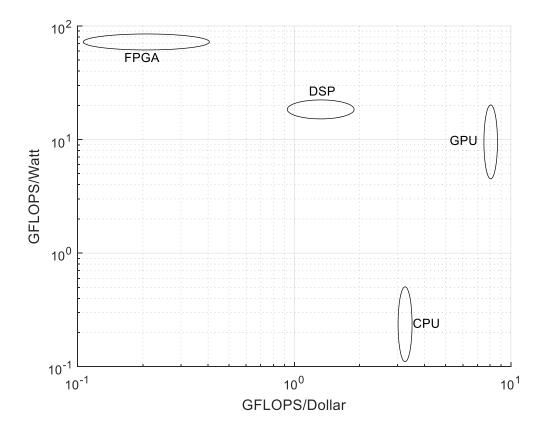

The key design tradeoffs depend on the constraints imposed by the radar system. In some applications, such as airborne radar, the size, weight, and power consumption (SWaP) is a constraint and requires the designer to address the SWaP challenges by balancing the performance and form factors. In contrast, the SWaP requirements are likely to be relaxed for ground-based applications, but the cost of the platform may need to be limited. As one of the tradeoffs, Figure 1.3 shows the comparison among different type of processor selections in terms of power consumption, cost, and computing power. Based on such comparisons, a designer may choose the proper type of processor to fulfill the processing task according to the requirement. For example, FPGA is more appropriate

Figure 1.3: Cost-effectiveness and power efficiency comparison

for applications those require highest computation throughput at the lowest unit SWaP. On the other hand, CPU is suitable for the cost-sensitive scenarios. DSP or GPU can be a better choice when a balance between cost and performance is needed. Even though FPGA and ASIC are relatively difficult to be programmed than DSP and the cost is higher. However, when a large volume of devices are in demand and high computing intensity is required, FPGA and ASIC will be used in the most demanding portion of the system to keep the power consumption and form factor under control. For example, [5] mentions that each MPAR contains 1,200 channel and more than 200 MPAR are needed in the future. Based on this volume, the cost of using FPGA and ASIC would be dropped. So, in the final phase of the product, FPGA or ASIC would be a better choice.

Besides the high data throughput requirements for the backend of a PAR system, in the front-end, there are also issues related to antenna calibration, RF distortion, and multi-channel synchronization. Compared with PAR, reflector dish radars have mechanically steered the antenna to point the radar beam in a specific direction, so the characteristics of the beam are the same during scanning. However, the beam characteristics of a PAR change with the pointing directions as well as the performance of its transmit and receive elements. For dual-polarized PAR, antenna beams at each pointing direction need to be calibrated and monitored. Moreover, distributed array architecture, such as the distributed local oscillator (LO) in digital arrays, leads to small variations in signal response among different channels. Although various antenna calibration methods, such as peripheral fixed probes and near-field measurement, can help channel equalization, those procedures are all complex and need a clutter-free environment. Once a PAR is deployed, re-calibration may be difficult, which brings the challenge of achieving stable system performance.

In practice, due to the nonlinear behaviors of RF hardware, the relative phase, and amplitude values deviate considerably during the time and among different channels. This distortion reduces the dynamic-range and downgrades the data quality, so the predicting, assessing and quantifying these effects would be necessary for calibrations. Several linearization techniques have been developed to inversely models the behavioral models of system's gain and phase characteristics, such as feedforward linearization [13], RF predistortion [14], Cartesian feedback [15], and digital predistortion. These methods require extra predistortion circuits and feedback from the output of RF system, which increase the complexity of RF front-end design and cost.

The transmitters, receivers, and other sequential circuits in PAR channels are synchronized by a Local Oscillator clock (LO). In other to synchronize LOs in different channels, a global clock signal is distributed so that the data acquired from multiple channels are correlated in time. A reliable clock network is required to deliver the clock signal to all the channel circuit components. In a multiple chassis PAR (especially for DAR) application, the interconnection clock distribution network is complex and the control of arrival times of the global clock at different LOs becomes difficult. If not properly controlled and monitored constantly, the clock skew can adversely affect the performance or even cause erratic operations of the systems.

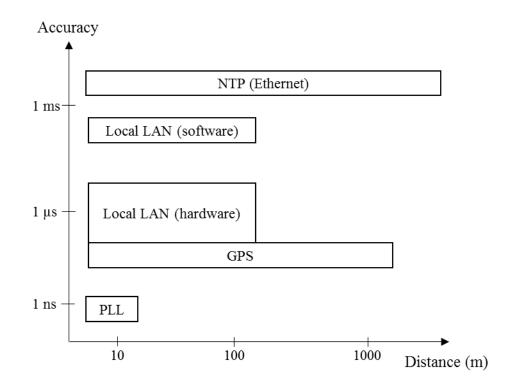

The design of clock distribution network poses a formidable challenge of considering the variations in interconnect parameters. For example, the length of between the source of global clock to each LO may be varied, and the power supply noise on each

LO affects the clock jitter, which, in turn, affects the arrival time of the global clock. Those instabilities would make the overall system unreliable, which is one of the lessons learned from OU's first version CPPAR development. The most common synchronization solution is using Network Time Protocol, which synchronizes each client by using the UDP packets over Ethernet. The drawback of this solution is the low accuracy, ranging from 5 to 100 ms [12]. Another more accurate method is using the IEEE 1588 Precision Time Protocol (PTP) standard [13], which can achieve submicrosecond synchronization [14]. However, to implement PTP, an extra dedicated hardware and software are needed, which would increase the complexity and cost of front-end system.

#### 1.3. Emerging Technologies for Digital Backend System

The digitization of transmitting and receiving signals at the element level opens the door to new processing technologies for the phased array system. In the RF front end, the stateof-art Gallium nitride technology outperforms traditional CMOS power amplifiers in terms of high power density and smaller die areas [16]. With the fast development of integrated chip industry, the cost and size of chips are reduced, which makes the radar system smaller, more powerful, and affordable for the customers from the consumer electronics market. For example, in the automotive industry, the frequency modulation continuous wave radar has been widely utilized in the forward collision avoidance system and active cruise control system. Those mass productions would further bring down the cost of the radar and make the radar product more affordable.

In the backend processing platforms, a high-performance embedded computing (HPEC) platform contains microprocessors, network interconnection technologies such

as those of the Advanced Telecommunications Computing Architecture (ATCA) and Micro Telecom Computing Architecture (MTCA), and management software that allows more computing power to be packed into a system with smaller SWaP. Such designs achieve compatibility with industrial standards and reduce both the cost and duration of development. MTCA and ATCA contain groups of specifications that aim to provide an open, multi-vendor architecture that seeks to fulfill the requirements of a high throughput interconnection network, increase the feasibility of system upgrading and upscaling, and improve system reliability. In particular, MTCA specifies the standard use of an Advanced Mezzanine Card (AMC) to provide processing and input-output (I/O) functions on a high-performance switch fabric with a small form factor.

Within the backend system, the processing chipsets have also evolved rapidly. Not only the data throughput of widely-used FPGA and DSP are increased dramatically, but also a new type of processor has emerged as a new tool to accelerate radar signal processing tasks. Traditionally, GPU has been used as a special-purpose device whose function is to accelerate the graphics pipeline for the video games in the PC environment. With the fast development of GPU and its standardized application programming interfaces (API), such as OpenGL, DirectX, and CUDA, GPUs have moved beyond graphics applications to become powerful floating point processing units [17]. As GPU is a native hardware for floating point operations, many areas of study related to a significant computing throughput requirement, such as machine learning, computational biology [18], and computer vision, has begun to adopt newer signal processing algorithms to GPU. Moreover, GPUs offer good backward compatibility than DSP and FPGA.

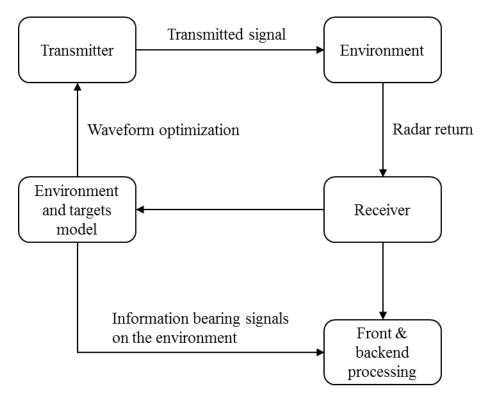

Applying machine learning algorithms in radar signal processing, especially in the target recognition area, has become a new trend [19]. For example, cognitive radar [20] is designed to intelligently perceive, track, and classify the targets from the past experiments, which is realized by the Bayesian approach. The cognitive aspect is manifested in the form of the cognitive signal processing cycle, in which an adapt waveforms are generated to illuminate the non-stationary environment. Within this cycle, active target classifications are optimized based on prioritized system objectives, understanding of the observation environment, and other forms of prior knowledge. With each illumination, the system improves the understanding of surrounding area in response to collected data and other information [21]. The cognitive radar uses the scene analysis to develop an appropriate statistical model to describe the information content of received signal on clutter, targets, or other false alarms. For example, when there is a target moving on an ocean surface, the Doppler spectrum of clutter would be relatively smooth across a wide range of the spectrum, whereas the spectral of the target would be appeared as a line component [22]. Moreover, when the power level reflected from the target is small compared with clutter, the cognitive radar needs an enhancement to extract the target information from the clutter. Thus, three statistic models are developed to classify the different conditions: clutter-statistics described by the F-distribution  $F_{2,2k}(z)$ , where z is the power of spectrum and, k is the number of neighboring Doppler bins [23], targetpulse-clutter statistics described by scaled F-distribution  $\frac{1}{\gamma}F_{2,2k}\left(\frac{z}{\gamma}\right)$ , where  $\gamma$  is the power ratio of target to clutter, and target motion described by the Gaussian distribution .

#### **1.4.** Comparison of DSP, FPGA, and GPGPU

The signal processing tasks in the DAR can be implemented with different types of processors; each has its own benefits and limitations. FPGA has the advantage of low non-recurring expenses and reconfigurability with high throughput. Different from other types of general purpose processors, FPGA is programmable device based on user applications. In the FPGA, multiple logic blocks are connected with programmable interconnect point, in which the designer can implement algorithms by configuring logic blocks and routing the data traffic through interconnect points [24]. Since a designer can control the hardware structure implemented in FPGAs, the computation load and communication throughput may be balanced better than other General-Purpose Processors (GPPs). For example, the bus width and the processing speed is fixed in the GPP, so the performance of the processors may be compromised when the communication requirement is more stringent than computing requirements,

Before the proliferation of FPGA applications, DSP has been the primary choice for signal processors. Within DSP, multiple numbers of Multiply Accumulate Engines (MAC) are used for parallel processing. For example, a TI C66x core [11] contains one MAC, which can perform four single precision floating point multiplications and two single precision floating point additions in one clock cycle. Since a DSP operates on *instructions*, the programming mechanism can be a high-level language for fast deployment or assembly language for higher performance requirements. Those two choices provide the flexibility for the designers compared by using only one mechanism--HDL on FPGA. However, with hundreds of MACs, FPGA can be built into a more powerful parallel computing platform than DSP. Incorporating so much computing power in one chip makes the power consumption in FPGA much higher than DSP. Moreover, FPGAs are usually more expensive than DSP in terms of GFLOPS per dollar. Thus, DSP would be a better choice for applications which are cost sensitive and have strict power budget.

As a GPP, a CPU is designed to follow general purpose instructions among different types of tasks and thus allow the advantage of programming flexibility and efficiency in flow control. However, since CPUs do not accommodate for a range of scientific calculations, GPUs can be used to support heavy processing loads. The combination of a CPU and GPU offers competitive levels of flow control and mathematical processing, which enable the radar backend system to perform sophisticated algorithms in real-time. With the increasingly friendly programming environment and standardized API, CPU-GPU becomes easy to be programmed and maintained, compared with FPGA and DSP. Moreover, CPU-GPU has a better performance than FPGA and DSP in term of GFLOPS per dollar. The drawback of the combination, however, is its limited bandwidth for handling data flow in and out of the system. CPUs and GPUs are designed for a server environment, in which Peripheral Component Interconnect Express (PCIe) can efficiently perform point-to-point for onboard communication. However, PCIe is not suitable for high throughput data communication among a large number of boards. If the throughput of the processing is dominated by the size of data involved, then the communication bottleneck downgrades the computing performance for a CPU–GPU combination.

Therefore, when signal processing algorithms have demanding communication bandwidth requirements, DSP and FPGA are better options, since both can provide

14

significant bandwidth for in-chassis communication by using SRIO while at once achieving high computing performance. FPGA is more capable than DSP of providing high throughput in real-time for a given device size and power. When the DSP cluster cannot achieve performance requirements, the FPGA cluster can be employed for criticalstage, real-time radar signal processing. However, such improved performance comes at the expense of limited flexibility in implementing complex algorithms [7]. If FPGA and DSP both meet application requirements, then DSP can be a more preferred option given its reduced cost and less complicated programmability. The CPU-GPU combination can be used in the applications, in which there is a significant computing load requirement but with a more flexible timeline and power consumption requirements.

#### **1.5. Outline of Dissertation**

This dissertation presents the method of realizing digital phased array radar functions in a scalable, compact, and power efficiency form factor by using commercial off-self products. The ways of implementing fundamental signal processing algorithms in realtime on DSP platforms are discussed. An HPEC platform for parallel backend processing is introduced as an example, and novel algorithms to self-calibrate the array system are investigated. Finally, an example of system implementation is elaborated to demonstrate the performance of our purposed HPEC solutions.

Chapter 2 presents the computational aspect of canonical radar signal processing algorithms and procedures, focusing on computational complexity, algorithm decomposition, and mapping of algorithms onto embedded hardware processors. A new self-calibration technique based on Expectation Maximization (EM) algorithm is studied. Typically, antenna calibration needs a controlled environment and additional hardware, which is difficult to be performed in the field. The proposed self-calibration method would use EM algorithm to build up a Bayesian model to find the ground truth value based on thousands of observation data from the antenna. Moreover, compressive sensing is introduced to improve the range resolution. In this chapter, some of the research results are based on the past publication [25, 26].

Chapter 3 presents an efficient and scalable backend system architecture design for a large-scale PAR, which achieves high throughput and computing performance. The basic signal processing chain, including beamforming, pulse compression, and Doppler filtering are mapped to processing units in parallel for the real-time processing. More advanced adaptive processing algorithms can also be implemented on this HPEC testbed. Other radar applications, such as Synthetic Aperture Radar (SAR) can benefit greatly from this design as well. Our approach integrates multiple DSPs by using SRIO links as part of commercial-off-the-shelf (COTS) MTCA chassis. In a digital array radar (DAR) containing hundreds of channels, a highly accurate synchronization technique is critical to the system stability and performance since if transmitters or receivers are out of phase, a focused beam cannot be reliably formed and the SNR would be reduced. We developed a synchronization procedure with nano-seconds level accuracy to ensure the backend system is synchronized. Compared with other synchronization techniques, such as Network Time Protocol (NTP) and Precision Time Protocol (PTP), our method is more reliable, convenient, and accurate. In this chapter, some of the research results are based on the past publication [27].

Chapter 4 presents key benchmark results for radar processing algorithms to investigate the performance of the backend processing platform design, and proves that

the design can meet the real timeline requirements for a large-scale PAR containing 768 digital channels with 4,096 range gates. The system architecture allows adjusted processing power, which requires each processing board on the platform operates independently and be "hot swappable." Moreover, the architecture needs to provide enough bandwidth for the large data communication among different computing units. Based on those considerations, we use a product from various vendors and integrate them with hybrid backplanes, which proves to enhance the computing performance through benchmark results. Lastly, benchmark performance results of using "bare-bone" parallelism method and standard libraries (such as OpenCL) are compared.

In the end, Chapter 5 would summarize the architecture design consideration for the multi-functional PAR, in which the designer must diligently research the solution and ensure a predictable degree of operational continuity during production hours. Without a good underlying infrastructure and with poor planning, a single hardware failure in the computing environment could affect the system ability to continue the service. Although there are many considerations to a PAR system, the following are some of the most important aspects:

- System Fault-tolerance: A fault-tolerant system has redundant hardware components inside to withstand hardware failure. When the system encounters a hardware failure, the application should remain operational or may be degraded, while the system is repaired.

- Scalability: A scalable system is one whose performance can be increased, or decreased, after adding or removing proportional hardware without changing the framework of the infrastructure components.

17

• Cost-effective: Using less money to make more outcomes is the goal that every system designer wants to achieve. By doing so, the designer should compare different types of technologies and chose the one that can benefit the system most.

### 2. Signal Processing Algorithms and Processing Chain

#### **2.1. Introduction**

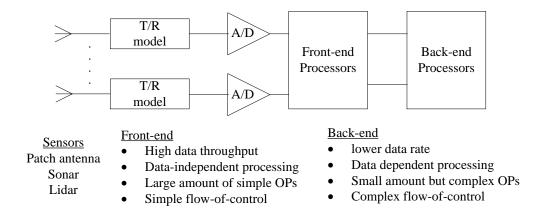

With the development of the higher level of functionality and complexity in signal and image processing applications, the computing throughput in HPEC becomes more demanding with hard-real-time deadlines and stringent form factors. Figure 2.1 shows a top-level structure for a typical HPEC application. The HPEC can be divided into three parts: sensors, a front-end signal processing and a backend data processing. For the PAR application, the sensor could be patch antenna or reflect array [28, 29]. The front-end is to transmit or receive the signal to/from the outside by using the appropriate sensors, remove noise and interference from the signal, and extract the useful information from a large amount of received data. The purpose of the backend is to further refine and classify the information into different categories, convert the numerical information into readable, user-friendly data, and estimate the status of the future targets based on the current result.

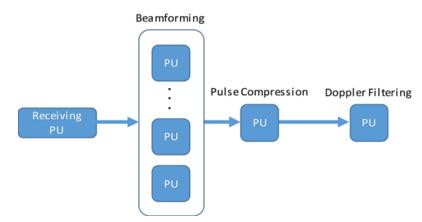

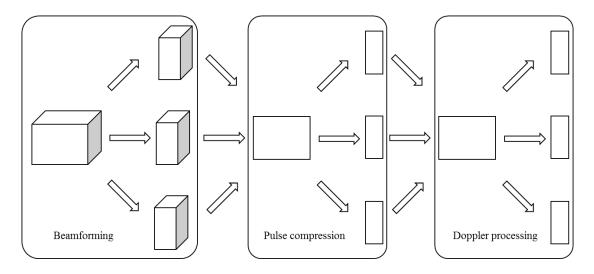

Figure 2.1: Canonical front-end and back-end architecture of an HPEC application

In the PAR application, multiple pulses are transmitted within one Coherent Pulse Interval (CPI). The pulses in the same CPI are phase-coherent, in which each pulse starts with the same phase and reflects back from targets with the relatively small differences in phase. The time interval between transmitted pulse is Pulse Repetition Interval (PRI), which determines the maximum unambiguous range. After the radar antenna receives the reflected signal, the signal would proceed through receivers that perform downconversion and band-pass filtering, and input to the front-end and back-end processing platform, in which more complex signal processing tasks are performed and output the detection result to the users. In the front-end, three fundamental or general-purpose processing tasks would be conducted— beamforming, pulse compression, and Doppler filtering, and then the result would be feed to the backend platform, in which the types of processing tasks are based on the requirements of different applications. For example, in the weather radar processing, it focuses on the information related to volume targets and analysis the spectrum of the target velocities. In contrast, the aircraft surveillance is committed to giving a good estimation of the position and velocity of the aircraft targets.

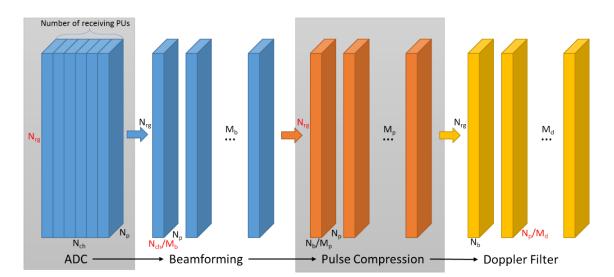

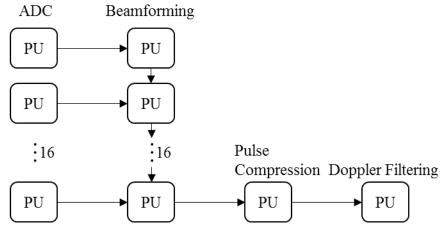

Figure 2.2: Overview of data cube processing chain in a general PAR

Figure 2.2 shows the data cube processing chain in the PAR front-end. The received data from the array manifold and front-end electronics are organized into threedimensional data cubes, and  $N_{rg}$ ,  $N_{ch}$ ,  $N_p$ , and  $N_b$  represent the total number of range gates, channels, pulses, and beams, respectively. When any of those four numbers are red, the data are aligned in their corresponding dimensions. After the data cube is digitized by ADCs, the data is aligned in the dimension of range gate. Before doing further processing, the large data cube would be decomposed to several small portions for the purpose of parallel computing and re-align the data in the channel domain to facilitate the following beamforming processing. The beamforming stage transform spatial domain signal into beam-space domain, creating a set of focused beams. Another data corner-turn is applied at the output of beamforming to align the data in the range gate dimension. The pulse compression stage concentrates the signal energy spread over the entire transmitted waveform into a short pulse response to increase the SNR and sensitivity. A third data corner turn is performed to transform the data from channel to pulse dimension. The Doppler filter stage determine the radial velocity of targets relative to the radar array by applying FFT across the pulses within one CPI. At the output of the Doppler filter, the data cube has dimensions of number of range gates  $\times$  the number of beams  $\times$  the number of Doppler bins. After the Doppler processing, the data cube is converted into a data set containing the information about the position and velocity of the targets, from which the processing tasks in the backend can further extract information based on the requirements of applications by using more complex signal processing algorithms.

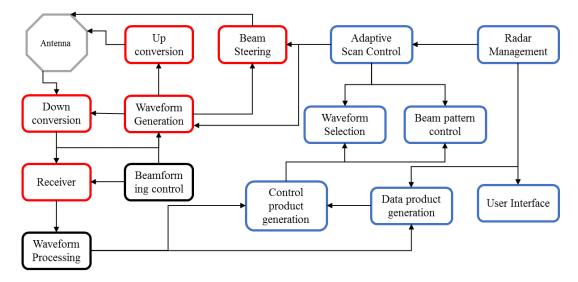

Figure 2.3 : Illustration of large-scale PAR overall software system diagram

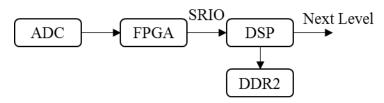

Figure 2.3 shows the large-scale PAR overall software diagram, in which the red, black, and blue boxes represent the corresponding tasks performed by the FPGA, DSP, and GPGPU platforms respectively. The selection of different types of the processor is based on the requirements of processing tasks mentioned in Section 1.4. The data cube is formed in the FPGA platform, red boxes, and processed on the DSP platform, black boxes. This dissertation focuses on performing waveform processing and beamforming control task on DSP. The following sections in this chapter would be organized as: Section 2.2-2.4 introduce the canonical radar algorithm in the processing chain and study the computing complexities of these algorithms. After the signal processing chain, the data processing tasks including weather data product generation and target tracking are discussed in Section 2.5. In Section 2.6, several advanced algorithms are introduced, aiming to improve the performance of overall processing chain.

Before calculating the computing complexity of each algorithm in the following sections, it is necessary to list the computational complexity expressions for several fundamental *signal processing* kernels for both real and complex values in advance. The

discussion of the complexity of each processing kernel is beyond the scope of this dissertation; a comprehensive discussion can be found in [30]. The following sections would use the computational complexity listed in Table 2.1 as a reference. Moreover, we use Giga Floating-point Operations (GFLOPS) [31] as a metric to measure the benchmarks of digital PAR backend system performance.

| Signal Processing Kernel                                 | Computational Complexity |                                     |

|----------------------------------------------------------|--------------------------|-------------------------------------|

|                                                          | Real value               | Complex value                       |

| Matrix Multiplication                                    | 2mnp                     | 2mnp                                |

| Fast Fourier Transform                                   | $\frac{5}{2}nlog_2n$     | $5nlog_2n$                          |

| Forward or back substitution                             | n <sup>2</sup>           | 4 <i>n</i> <sup>2</sup>             |

| Eigen-decomposition                                      | 9 <i>n</i> <sup>3</sup>  | 23 <i>n</i> <sup>3</sup>            |

| For the matrix multiplication, the matric                | es are of dimensions     | $m \times n$ and $n \times p$ . For |

| the FFT, the vector size is $\boldsymbol{n}$ . The lower | triangular matrix used   | d in forward or back                |

| substitution is $n \times n$ .                           |                          |                                     |

Table 2.1: Computational Complexity for Signal Processing Kernels

#### 2.2. Digital Beamforming

The procedure of beamforming is to convert the data from channel data (range gate) to beamspace, steer the radiating direction, suppress sidelobes and interferences by applying the beamformer weight,  $W_i$ , to received signal,  $Y_i$ , indicating in Equation (2.1), in which  $\Theta$  is the beam pointing angle indicator and  $\Omega$  is the total number of channels. The computation complexity of Equation (2.1) can be determined as follows: first, each complex multiplication requires four floating point multiplications and two floating point additions, for a total of 4 + 2 = 6 real flops. There are two complex additions for summing of each channel. Hence, for a complex beamforming, the complexity formula arrived at is  $(6 + 2) \times \Omega \times N_{rg} = 8N_cN_{rg}$ , where  $N_{rg}$  is the number of range gates. The above calculating complexity evaluates the throughput of beamforming at the time interval, *T*, as  $(8N_cN_{rg})/T$  FLOPS.

$$Beam^{\theta} = \sum_{i=1}^{\Omega} W_i^{\theta} Y_i$$

(2.1)

In a large-scale PAR, there will be thousands of range gates and channels, which bring huge computing burden for a front-end computing platform. For example, in [5], each face of the array contains 20,000 channels, and suppose the number of range gates is 1,000 and pulse time interval is *one ms*. If all the elements are digitalized, the throughput of the beamforming would be 160 GFLOPS for a single beam forming. It is impossible for a single processor to handle such computation. So parallel computing is needed and it requires to separate the entire computing load to various computing nodes. Equation (2.2) and (2.3) shows an example of "systolic beamforming", by dividing the beamforming process into *M* parts. The entire data is divided equally and a portion assigned to each sub-beamformers, (i.e., computing node), in which the term  $\sum_{i=1}^{C} (W_{jC+i}^{b} Y_{jC+i})$  is calculated independently and *C* is the number of channel of each computing node can get.

$$Beam^{\Theta} = \left[\sum_{i=1}^{C} W_i^{\Theta} Y_i\right] + \left[\sum_{i=1}^{C} W_{C+i}^{\Theta} Y_{C+i}\right] + \left[\sum_{i=1}^{C} W_{2C+i}^{\Theta} Y_{2C+i}\right] + \cdots + \left[\sum_{i=1}^{C} W_{(M-1)C+i}^{\Theta} Y_{(M-1)C+i}\right]$$

$$(2.2)$$

$$Beam^{\Theta} = \sum_{j=0}^{M-1} \left[ \sum_{i=1}^{C} W_{jC+i}^{\Theta} Y_{jC+i} \right]$$

(2.3)

A PAR system may operate in an environment which is not stable and contain unwanted interference, so an adaptive beamforming weight is used to generate high gain in the beam steering direction and reject or minimize energy from other directions by adaptively adjusting the steering vector according to the interference environment. There are numerous methods for calculating the beamformer weights adaptively. The most standard solution is Wiener filter [32, 33], showing in Equation (2.4), in which W is a beamforming weight matrix; V is a matrix of column steering vectors; R is the covariance matrix of the received signal A. To achieve good performance, [34] suggests that the number of samples needs to be 2 to 5 times of channel number,  $N_{ch}$ . For example, if the system has  $N_{ch}$  number of channels, then a sample matrix, A has dimension of  $N_{ch} \times 5N_{ch}$ . Moreover, to desensitize the adaptive weight computation to perturbations [35], covariance matrix R needs to be appended by an extra loading matrix, Q. Though many studies suggest that the loading matrix takes the form of the covariance matrix of steering vector due to of the simplicity and effectiveness [36], the most widely-used method is *diagonal loading matrix*. Equation (2.5) shows a method for appending the diagonal loading matrix to covariance matrix with a constant *Loading Level*,  $\sigma$ . The diagonal loading matrix can be accommodated into Equation (2.4) by augmenting the sample matrix with an identity matrix with square root of desired loading level, as showing in Equation (2.6), in which B is the sample matrix appended with the loading matrix. To efficiently solve the weight vector W, [9] suggests using the Winer filter to avoid the calculating of the covariance matrix in Equation (2.6) by decomposing matrix

*B* into a lower triangular matrix *L* and an orthogonal matrix *Q*. The Equation (2.7) shows the simplified version of Equation (2.6) after applying LQ decomposition to matrix *B*.

$$W = R^{-1}V, in which R = AA^{H}$$

(2.4)

$$\bar{R} = R + Q = AA^H + \sigma I \tag{2.5}$$

$$W_{1} = \bar{R}^{-1}V = (AA^{H} + \sigma I)^{-1}V = \left(\left[A|\sqrt{\delta}I\right]\left[A|\sqrt{\delta}I\right]^{H}\right)^{-1}V = (BB^{H})^{-1}V$$

(2.6)

$$W_1 = (L^H)^{-1}(L^{-1}V)$$

(2.7)

The Wiener filter method of calculating adaptive beamforming weight contains three parts: LQ decomposition and two matrices backsolve. Suppose in Equation (2.6), *B* and *V* are the matrices of dimensions  $m \times n$  and  $m \times 1$ . The complexity expressions for the LQ decomposition of matrix *B* is  $8mn^2 - 8n^3/3$ . As the dimension of *L* is the same as *B*, so two backsolves cost  $4n^2$  and  $4m^2$  flops, respectively. Thus, in total, the complexity of weight calculation is

$$8mn^2 - 8n^3/3 + 4n^2 + 4m^2 \tag{2.8}$$

$$W_{2} = (BB^{H})^{-1}V = \left( \left( A + \sqrt{\delta}I \right) \left( A + \sqrt{\delta}I \right)^{H} \right)^{-1} V$$

$$= \left( AA^{H} + \sigma I + \sqrt{\delta}\hat{A}^{H} + \sqrt{\delta}\hat{A} \right)^{-1}V$$

(2.9)

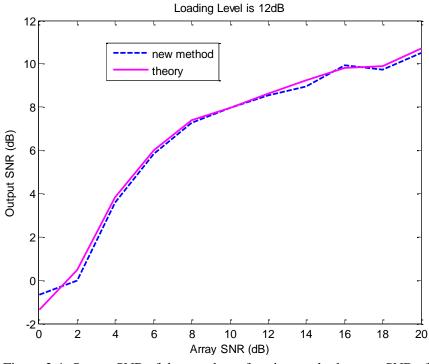

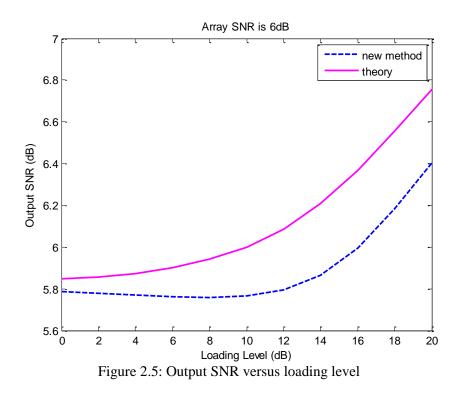

As mentioned above, the sample matrix *A* has the dimension of  $N_{ch} \times 5N_{ch}$ . In Equation (2.6), the symbol "|" represents that the matrix on the right side of the bar is appended to the end of the matrix on the left side. After diagonal loading matrix *Q* inserted into matrix *A*, the matrix *B* has the dimension of  $N_{ch} \times 6N_{ch}$ , which increases the complexity of computing the autocovariance matrix *A*. To reduce this additional computation load after diagonal loading, a new method is introduced here, named *direct appending loading level method*, by augmenting the loading matrix directly to the sample matrix *A*, as showing in Equation (2.9).  $\hat{A}$  is square matrix of the product from  $A \times I$ . By using this new method, the dimension of *B* is  $N_{ch} \times 5N_{ch}$ , maintaining the original size of sample matrix *A*. However, when we perform the direct appending method, two noise matrices  $\sqrt{\delta}\hat{A}^{H}$  and  $\sqrt{\delta}\hat{A}$  are brought into the covariance result, which may degrade the performance of beamforming. So, to investigate how much those two noise matrices may affect the performance of beamforming, we compared the SNR between original weight calculating method and our new method, as shown in Figure 2.4 and Figure 2.5, respectively. The signal power  $P_s$ , and the interference pulse plus noise power  $P_{i+n}$ , are given by

$$P_s = W^H R_s W \tag{2.10}$$

$$P_{i+n} = W^H R_{i+n} W \tag{2.11}$$

So, the SNR is equal to

$$\frac{P_s}{P_{i+n}} = \frac{W^H R_s W}{W^H R_{i+n} W}$$

(2.12)

Figure 2.4: Output SNR of the new beamforming method versus SNR of traditional beamforming method

In the first simulation, we compared the performance of adaptive beamforming versus the array SNR. The loading level, *LL* is defined as  $10 \log(LL/\delta^2)$ , in which  $\delta$  is the standard deviation of zero mean white noise. From Figure 2.4, we observe that the performance of new method is closed to the theory one, which means the new method bring little impact to the SNR. Next, the influence of the loading level is shown in Figure 2.5. The maximum difference between two methods is 0.4 dB, which also indicates that the new method has similar performance as the theory's. Thus, the direct appending loading level method can be a good way to reduce the computing resource. Note that to implement the weight vector calculating for the adaptive beamforming, an extra processing node are required to receive the all the channel data, and then the weight can be distributed to each processing node.

### **2.3.** Pulse Compression

After beamforming, pulse compression is for improving the signal-to-noise ratio and the range resolution. Pulse compression can be implemented by performing correlation of the return signal, s[n], and a replica of the transmitted waveform, x[n], which is equivalent to *matched filter* operation. By filtering the return signal, the energy of returned waveform would be aggregated into range gates and concentrates on the target ranges. Matched filter implementation converts the signal to the frequency domain, performs point-wise multiplies with transmitted waveform, and converts the result back to time domain [9], as shown in Equations (2.13)-(2.16). The length of FFT is chosen to be the first power of 2 greater than N + L - 1. For example, if N = 2250 and L = 22, which makes N + L - 1 = 2271, so the length of FFT should be 4098. In this situation, it requires to zero-pad x[k] and s[k] to the length of 4098, before converting into frequency

domain. Zero-padding increases computing complexity of the FFT in Equation (2.13) and (2.14), and makes Equation (2.15) to consume more computing resources. Values of N and L need to be selected to avoid unnecessary computation.

$$S[k] \xleftarrow{FFT} s[n] \ 0 \le n \le N$$

(2.13)

$$X[k] \stackrel{\text{FFT}}{\leftarrow} x[n] \quad 0 \le n \le L \tag{2.14}$$

$$Y(k) = S[k]X[k] \ 0 \le k \le (N + L - 1)$$

(2.15)

$$y[n] \stackrel{\text{IFFT}}{\longleftarrow} Y[k] \quad 0 \le n \le (N+L-1)$$

(2.16)

From the above equations, the overall computing complexity of pulse compression depends on FFT, IFFT and point-wise vector multiplication. For radix-2 FFT, there are  $log_2(N)$  butterfly computation stages. Each stage consists of N/2 butterflies, and each butterfly operation requires one complex multiplication, one complex addition, and one complex subtraction. Hence, the complexity of computing radix-2 FFT is:

$$C_{FFT} = (6+2+2) \times \frac{N}{2} \times \log_2 N = 5N \log_2 N flops.$$

As the IFFT has the same complexity of FFT, the throughput of the whole pulse compression in frequency domain is

$$\frac{2 \times C_{FFT} + NC_{mult}}{T} = \frac{10N \log_2 N + 6N}{T} FLOPS,$$

where *N* is the number of range gates after zero-padding, and  $C_{mult}$  is the complexity of point-wise complex multiply.

## 2.4. Doppler Processing and Data Corner Turn

The first objective of the Doppler processing is to mitigate the impacts of stationary or slow-moving clutter. The second objective is to measure the radial velocity of the targets by calculating the Doppler shift [37], from the Flourier transformation of data cube along the CPI dimension for each range bin. The throughput of an FFT-based basic Doppler filter is  $C_{FFT}/T = 5N_p \log_2 N_p/T$  FLOPS, where  $N_p$  is the number of pulses in one CPI. The Doppler filtering performance is shown in Table 2.2.

| <b>Range Gates</b> | Pulses |        |        |        |        |  |  |

|--------------------|--------|--------|--------|--------|--------|--|--|

|                    | 8      | 16     | 32     | 64     | 128    |  |  |

| 1024               | 0.7293 | 1.6036 | 2.6852 | 3.8543 | 4.2866 |  |  |

| 2048               | 0.7294 | 1.6000 | 2.6841 | 3.8543 | 4.2867 |  |  |

| 4096               | 0.7294 | 1.5999 | 2.6842 | 3.8544 | 4.2867 |  |  |

| 8192               | 0.7295 | 1.6000 | 2.6842 | 3.8544 | 4.2732 |  |  |

Table 2.2: Doppler filtering performance measured in GFLOPS per core

Compared with previous beamforming and pulse compression processing, Doppler processing requires less computing power. However, additional data transmission time is required before Doppler processing. As the output of the pulse compression is arranged along the range gate dimension, the output needs to undergo a corner turn before being handled by the Doppler filtering processors [38]. This twodimensional corner turn operation is equivalent to a matrix transpose in the memory space. Using EDMA3 [39] on TI generic C66xx DSP, the data can be reorganized into the desired format without interfering the real-time computations in DSP core. So, the performance of Doppler processing can be performed without interference from data corner turn. The use of EDMA3 would be further discussed in further.

#### **2.5. Weather and Air-surveillance Data Products**

Section 2.2, 2.3, and 2.4 have illustrated the basic PAR signal processing algorithms, which are the building blocks of radar signal processing chain and foundations of other advanced signal processing algorithms. For example, in weather radar application, the mean Doppler velocity and spectrum width estimation takes outputs from beamforming and pulse compression. In the air-surveillance application, target detection and tracking processing also depend on the results of beamforming, pulse compression, and Doppler filtering. This section will illustrate the high-level, or *backend*, PAR data processing algorithms and discuss their complexities.

### 2.5.1. Mean Velocity Estimation

Mean Doppler velocity is the averaged velocity of the radar resolution volume. There are two methods to calculate the Doppler frequency shift: spectral processing and Pulse Pair Processor (PPP) [40]. In the spectral processing method, the first step is to calculate the periodogram [41] of signal along the CPI domain by using FFT as

$$S = \frac{|Z(f)|^2 T}{M}, in which Z(f) \stackrel{fft}{\leftarrow} s(n)$$

(2.17)

where *M* is the number of pulses, *T* is the Pulse Repetition Time (PRT), s(n) is the samples along the CPI domain. Then the mean velocity is calculated by using Equation (2.18) [42], in which  $\lambda$  is the wavelength of transmitting wave, *P* is the total power in the periodogram,  $k_m$  is the index of the strongest Fourier coefficient, and *i* is the index of pulse. Most of computation load in mean velocity estimation is from Equation (2.17) and the summation part in Equation (2.18). As the Z(f) is the result from Doppler filtering mentioned in Section 2.4, those results can be utilized twice in the mean velocity

estimation to save the computing resources. Therefore, the complexity of Equations (2.17) and (2.18) are 12M + 7M = 19M in combination.

$$v = \frac{\lambda}{2M} \left\{ \frac{k_m}{T} + \frac{1}{PT} \sum_{k_m - M/2}^{k_m + M/2} (i - k_m) S[mod_M(k_m)] \right\}$$

(2.18)

PPP is another method to estimate the mean Doppler velocity by comparing the phase differences among various samples. A general method to calculate the phase difference is using the covariance approach [40]. The first step is to estimate the autocorrelation of the signal along the CPI domain with one sample lag, n = 1, as

$$R_n = \frac{1}{M} \sum_{i=0}^{M-1} s_i^* s_{i+n}$$

(2.19)

So, the mean velocity can be estimated as

$$v = \frac{\lambda}{4\pi T} \arg(R_1) \tag{2.20}$$

where the argument of *R* calculates the phase of *R* in radians. Based on Equation (2.19) and (2.20), we can calculate the complexity of PPP is 6M + 2M = 8M. Compared with the spectral processing, PPP method has the advantages of requiring less computing resources and having smaller velocity variance when there is no unique solution for SNR and spectrum widths [43].

## 2.5.2. Spectrum Width Estimation

The mean velocity estimation mentioned in the previous section represents the average speed of hydrometeors in one range gate. When there are turbulence or chaotic flow, hydrometeors within one resolution volume have vastly different radial velocities [44]. In this case, the mean velocity cannot represent the entire range of velocities within one range gate and may overlook the fast-changing weather phenomenon. The spectrum

width can depict the standard deviation of the velocity and represent random particle movements. Methods used to extract the spectrum width are usually based on autocovariance processing and spectral estimation.

The autocovariance processing method utilizes the autocorrelation of the signal at different lags to estimate the spectrum width. If the weather signal spectra closely follow a Gaussian shape, the estimated spectrum width,  $\sigma_v^2$ , is

$$\sigma_v^2 = \frac{\lambda^2}{24(\pi T)^2} \ln \left| \frac{R_1}{R_2} \right|$$

(2.21)

where  $R_1$  and  $R_2$  are the autocorrelation based on Equation (2.19) [45]. The computing load of Equation (2.19) mainly comes from autocorrelation, so the complexity can be approximated as  $6N_p + 6N_p = 12N_p$ .

Corresponding to the autocovariance method, spectrum width estimation by using spectral processing is given by

$$\sigma_{\nu}^{2} = \frac{\lambda^{2}}{4PT^{2}} \sum_{k_{m}-M/2}^{k_{m}+M/2} \left(\frac{i}{M} + \frac{2\nu T}{\lambda}\right)^{2} S[mod_{M}(k_{m})]$$

(2.22)

The complexity of Equation (2.22) is the same as Equation (2.18), which is  $19N_p$ . Thus, the spectral processing requires more computing resources than autocorrelation method. Moreover, Equation (2.22) is a biased estimation due to the window effect in the FFT. In general, this bias is difficult to compute [43], thus in general, autocovariance method is superior than the spectral processing.

# 2.5.3. Target Tracking

For MPAR, target tracking (such as air-traffic tracking) is a crucial function. Once a radar receiver detects the presence of the targets and converts the detections into validated

measurements, the radar tracker initiates and estimates the target's future state, while integrating the new measurements into an existing track. Bayesian tracking or Bayesian recursively tracking is a method to treat the tracking problem from the perspective of Bayesian inference. It assumes that a likelihood function links the events observed in the current state to the future unknown. As such, if we specify a prior distribution of some targets, we can calculate the posterior distributions or future states with the help of likelihood function [23]. For example, if a surveillance radar records the previous speeds and locations of an air-vehicle, based on the currently measured speed and location, a likelihood function can be established, which is then used to predict the vehicle's future positions and velocities through different models.

The goal of multiple target tracking (MTT) is to estimate the states of multiple targets simultaneously [46]. Compared with single target tracking, MTT needs to determine which target generates each sensor response or whether the response is a false alarm. For most cases, we may not know the exact number of the objectives, which makes the MTT further complicated. Situations that the tracks of multiple targets are overlapped or intersected can lead to ambiguity of the data association process. Also, as the kinematic model of each target can vary, the transition functions that we used in a Kalman filter may not be suitable for all the scenarios.

For multiple target tracking, joint probabilistic data association (JPDA) and multiple hypothesis tracking (MHT) are the two classical Bayesian tracking methods. In all cases, both algorithms (JPDA and MHT) can provide reliable target tracking performance [46, 47]. MHT forms data association hypotheses by assigning probability 1 or 0 to a target, which is a *hard* association. JPDA relaxes this assumption by allowing

for the partial association. In the low SNR environments, JPDA and MHT are both capable of handling a high volume of clutter. However, MHT has a major disadvantage of requiring high computational complexity because the number of hypotheses grows exponentially over tracking time [48]. Although various methods have been developed to control the growth of hypotheses tree [49], JPDA is still more efficient and easier to be implemented. Also, when the detection probability is reduced for the weak target scenarios, MHT is more vulnerable than JPDA [50], since MHT is a single-scan algorithm compared to JPDA and depends heavily on the past scans. Hence, JPDA would be a better choice if there are no other specific requirements and use JPDA as an example to illustrate the computing complexity of tracking algorithm.

To track the targets, at first, we may build a model to represent the tracking system. Let S be the state space of a target dynamics, in which it contains various target information that can be utilized to locate and track the targets, such as the position, velocity, and acceleration of the targets. Thus, the targets in the space S can be represented as a vector containing kinematic parameters [8]. For a typical parametric approach, the classic Bayesian approach uses the dynamical motion and measurement equations shown in Equation (2.23) and (2.24) for the target tracking models:

$$y_k = A_{k-1} x_{k-1} + Q_{k-1} \tag{2.23}$$

$$y_k = H_k x_k + r_k \tag{2.24}$$

where  $x_k$  is the state vector for the target on the time step k,  $A_{k-1}$  defines the transition matrix of the dynamic model,  $y_k$  is the measurement vector on the time step k,  $Q_{k-1}$  is the process Gaussian random noise covariance matrix for the time step k - 1, denoted as  $Q_{k-1} \sim N(0, R_{k-1})$ .  $H_k$  is the measurement matrix that converts the system state to the measurement, and  $r_k \sim N(0, R_k)$  is the sensor measurement noise vector [37]. Based on this model, we can represent the target moving in a two-dimensional space in Cartesian coordinate system as

$$\boldsymbol{x}_k = [\boldsymbol{x}_k \ \boldsymbol{y}_k \ \dot{\boldsymbol{x}}_k \ \dot{\boldsymbol{y}}_k]^T \tag{2.25}$$

in which  $\dot{x}_k$  and  $\dot{y}_k$  are the velocities of the target along the x and y coordinate observed by a Radar. By giving Equation (2.25), we can represent transition matrix  $A_{k-1}$  as Equation (2.26), in which  $\Delta t = t_k - t_{k-1}$ .

$$A_{k} = \begin{bmatrix} 1 & 0 & \Delta t & 0 \\ 0 & 1 & 0 & \Delta t \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix}$$

(2.26)

For the nearly constant velocity motion model, the process noise covariance matrix is given by

$$Q_{k} = \delta^{2} \begin{bmatrix} \Delta t^{3}/3 & \Delta t^{2}/2 & 0 & 0\\ \Delta t^{2}/2 & \Delta t & 0 & 0\\ 0 & 0 & \Delta t^{3}/3 & \Delta t^{2}/2\\ 0 & 0 & \Delta t^{2}/2 & \Delta t \end{bmatrix}$$

(2.27)

The  $\delta^2$  is the design parameter for the system model error. Typically, this parameter is set to be greater than one half of the maximum acceleration of the target and less than the maximum acceleration [51]. The measurement matrix  $H_k$  is used to calculate the position of the target given the system state. In this case, the measurement matrix can be expressed as Equation (2.28).

$$H = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \end{bmatrix}$$

(2.28)

The system defined in (2.23) and (2.24) satisfies the Markov property, which means that the future state of this system is based solely on its present state. We can express this property in general as:

$$p(x_k|x_{1:k-1}, y_{1:k-1}) = p(x_k|x_{k-1})$$

(2.29)

This also implies the fact that the past does not depend on the future state by given the present, which is the same concept as in Equation (2.29), in which  $x_{k:T}$  represents the system states from current time step k up to future time step T.

$$p(x_k|x_{k:T}, y_{k:T}) = p(x_{k-1}|x_k)$$

(2.30)

For the measurement, which is the same as system state, the current measurement  $y_k$  is independent from the past measurement and system state. This property can be expressed in Equation (2.31).

$$p(y_k|x_{1:k}, y_{1:k-1}) = p(y_k|x_k)$$

(2.31)

The JPDA is an extended version of *Probabilistic Data Association Filter (PDAF)*. PDAF is to set up a validation region at each sampling time. Among that possible validated measurement, the position of a target can be determined by calculating the data association function of each measurement [52]. Similar to Kalman filter, PDAF makes an estimation based on the past measurements and states. If the state and measurement equations are assumed to be linear, the update and predicting algorithm of PDAF can be based on Kalman filter. When the state or measurement equations are nonlinear, then PDAF can be based on Extended Kalman Filter (EKF) [50] or Particle Filters [8]. The algorithms of PDAF and JPDA discussed in this section are based on Kalman filter. To perform PDAF, a basic assumption that the posterior probability function for the system state is summarized approximately by a normally distributed Gaussian

$$p[x(k)|z^{k-1}] = N[x(k); \hat{x}(k|k-1), P(k|k-1)]$$

(2.32)

In contrast with previously discussed front-end processing algorithms, the throughput of the tracking algorithm occurs on a per-target or per-track basis. Since the number of targets, tracks, and false alarms in the detection area is unknown, the computation requirements are nondeterministic. Moreover, compared with front-end processing tasks, which are all streamlined mathematic calculations, the back-end tracking algorithm involves more logical operations--stored, accessed, and updated target position overtime periods. So, it is usually difficult to estimate the computing resources needed for tracking algorithm without prior knowledge of the operational environment. To give a basic idea of the computational complexity, we calculate the throughput of the JPDA based on the sample parameters listed in Table 2.3.

| Description                                                         |  |  |  |  |  |  |

|---------------------------------------------------------------------|--|--|--|--|--|--|

| Number of currently confirmed targets                               |  |  |  |  |  |  |

| Number of measurements including potential targets and false alarms |  |  |  |  |  |  |

| Number of potential tracks                                          |  |  |  |  |  |  |

|                                                                     |  |  |  |  |  |  |

| T 11 0 0         | - 1 ·    | • •    |        |            |

|------------------|----------|--------|--------|------------|

| Table 230        | Trooling | 011011 | lotion | noromotoro |

| $I a D \Box Z D$ |          | SILLIU |        | parameters |

|                  |          |        |        |            |

# Prediction

The first step of JPDA is to conduct the Kalman prediction from k - 1 step to k, which is the same procedure as the single target Kalman filter, namely

$$\hat{x}(k|k-1) = A(k-1)\hat{x}(k-1|k-1)$$

(2.33)

$$\hat{z}(k|k-1) = H(k)\hat{x}(k|k-1)$$

(2.34)

$$P(k|k-1) = A(k-1)P(k-1|k-1)A(k-1)' + Q(k-1)$$

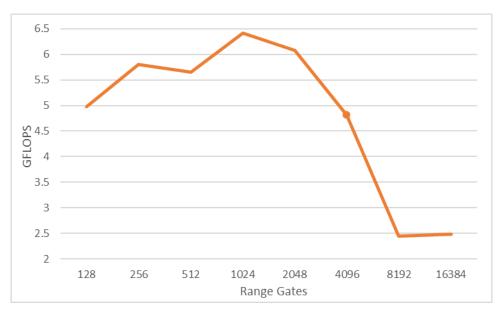

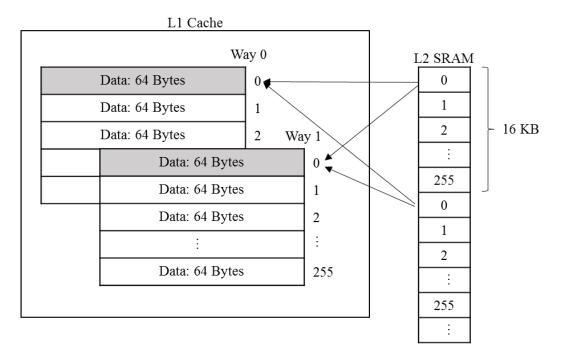

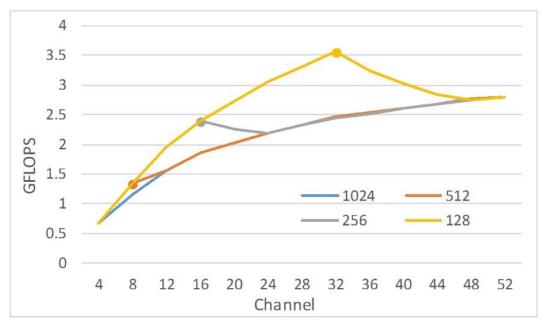

(2.35)