# AN IMPLEMENTATION OF A LOW POWER DELTA-SIGMA A/DC WITH A MULTI-BIT QUANTIZER ON SILICON-ON-SAPPHIRE

By

#### **CHIA-MING LIU**

Bachelor of Science Oklahoma State University Stillwater, Oklahoma 1994

Master of Science Oklahoma State University Stillwater, Oklahoma 1996

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of DOCTOR OF PHILOSOPHY August, 2002

# AN IMPLEMENTATION OF A LOW POWER DELTA-SIGMA A/DC WITH A MULTI-BIT QUANTIZER ON SILICON-ON-SAPPHIRE

Thesis Advisor Dean of the Graduate College

Thesis Approved:

ii

#### ACKNOWLEDGMENTS

The completion of this dissertation marks the end of my formal education. Throughout my life, there were numerous supports that are given to me unconditionally and lovingly. At this moment, I will take this opportunity to express my sincere gratitude to who have supported and loved me all along.

To begin, I thank my parents, grandparents, aunts and uncles for their unconditional love and support throughout my life. Their concern and caring always extends to the deepest of my heart. Ten years in the U.S., I would not able to achieve this milestone of my life without expressing my sincere gratitude to my aunt Kay and uncle Giin-Fa who have taken care of me for all these years, their love and care have helped me to accommodate my new life. Thanks to my cousins Bernard and Edwin who have also walked me through my loneliness from times to times.

Especially, I would like to express my deep appreciation to my wife, and my best friend, Rwei-Hsiang Kau who has accompanied and mentally stimulated me in many aspects of my life in these years. Her encouragement and support were the driving force for the write-up of this dissertation.

iii

Five and half years in Advanced Analog VLSI lab and many summer trips to San Diego; many of my partners came and graduated. I have not forgotten the friendship, encouragement, and technical assistance they all have given to me. To my friends Zheng, Wen, Jeff, Venu, Prasanna, Dave, Derek, Steve, Reghu, Zhu, Narendra, and Ira I appreciate and thank you.

I would also like to thank the faculty of the ECEN Department at OSU, especially Dr. Louis G. Johnson, Dr. Keith A. Teague, and Dr. Jack Cartinghour of Electrical Engineering Technology for being on my Graduate Committee. I am also indebted to Ms. Rea Maltsberger who has helped me throughout most of my years at OSU and her smile always inspires me. In addition, I am grateful to Space and Warfare (SPAWAR) Systems Center (formerly NRaD), San Diego, CA for its support of this project.

Last and foremost, I would like to thank my advisor, Dr. Chris Hutchens. I appreciate all of the opportunities and assistance he has provided me over the past five and half years. His numerous guidance and advice have deeply enhanced my chances for success at OSU and my subsequent career and life. Thank you!

iv

## TABLE OF CONTENTS

| Ch | Chapter Page                                                                                                                                                                                                                                                                                                                                                 |  |  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1. | INTRODUCTION 1                                                                                                                                                                                                                                                                                                                                               |  |  |

|    | 1.1 Objective.21.2 Organization.3                                                                                                                                                                                                                                                                                                                            |  |  |

| 2. | DELTA-SIGMA MODULATOR OVERVIEW                                                                                                                                                                                                                                                                                                                               |  |  |

|    | 2.1 Types of A/DCs.52.1.1 Nyquist A/DC.62.1.2 Oversampling A/DC.82.1.3 $\Delta$ - $\Sigma$ A/DCs.92.2 Architectures of $\Delta$ - $\Sigma$ A/DCs.112.2.1 Single loop modulator.122.2.2 MASH modulator.142.3 Power dissipation consideration.19                                                                                                               |  |  |

| 3. | MODULATER DESIGN AND IMPLEMENTATION                                                                                                                                                                                                                                                                                                                          |  |  |

|    | 3.1 Low power processes, Bulk or SOI?213.2 Architectural configuration and power estimation of a $\Delta$ - $\Sigma$ modulator.243.3 Modulator stability.333.4 Crucial building blocks of a $\Delta$ - $\Sigma$ modulator.433.4.1 Integrator and OTA.463.4.2 Dynamic common mode feedback.563.4.3 Quantizer.603.4.4 Serial D/AC.643.5 Device.693.6 Layout.74 |  |  |

| 4. | DECIMATION FILTER OVERVIEW                                                                                                                                                                                                                                                                                                                                   |  |  |

|    | 4.1 Moving average filter.804.2 Comb (Sinc) filter.814.3 Half-band filter.834.4 Two-path filter.86                                                                                                                                                                                                                                                           |  |  |

| Chapter |

|---------|

|---------|

# Page

| 5. | TWO-PATH FILTER DESGIN AND IMPLEMENTATION            | 89  |

|----|------------------------------------------------------|-----|

|    | 5.1 Filter in cascade                                | 91  |

|    | 5.2 Finite impulse response filter                   |     |

|    | 5.3 Decimation filter.                               |     |

|    | 5.3.1 Data multiplexer                               |     |

|    | 5.3.2 Two-path filter1                               |     |

|    | 5.4 Overall filter response                          | 10  |

| 6. | MEASUREMENT RESULTS1                                 | 18  |

|    | 6.1 Discrete Fourier Transform                       | .19 |

|    | 6.2 Modulator loop1                                  | .23 |

|    | 6.2.1 SNR and missing code1                          | .24 |

|    | 6.2.2 SFDR (Two-tone test)                           |     |

|    | 6.2.3 INL and DNL 1                                  |     |

|    | 6.3 Two-path decimation filter 1                     | 30  |

|    | 6.4 Power dissipation measurement1                   | 34  |

| 7. | CONCLUSIONS 1                                        | 37  |

|    | 7.1 Discussion                                       | 38  |

|    | 7.1.1 Leaky integrator                               |     |

|    | 7.1.2 Noisy transistors and current feedback sources |     |

|    | 7.1.3 Floating body of the transistors               |     |

|    | 7.1.3.1 Kink effect and pass-gate leakage1           |     |

|    | 7.1.3.2 History dependence                           |     |

|    | 7.2 Suggestion1                                      |     |

| RE | FERENCES 1                                           | 46  |

| ΛT | PENDIX ACHIP STATISTICS AND LAYOUT AND DIE           |     |

|    | OTOGRAPHS                                            | 52  |

|    |                                                      |     |

| VI | ТА1                                                  | 57  |

## LIST OF FIGURES

| Figure Page                                                                                   |

|-----------------------------------------------------------------------------------------------|

| 2.1 Block diagram of a general A/DC 6                                                         |

| 2.2 Noise spectrum comparison of A/DCs                                                        |

| 2.3 The 2 <sup>nd</sup> order single loop modulator12                                         |

| 2.4 Block diagram of VCO-DS-ADC14                                                             |

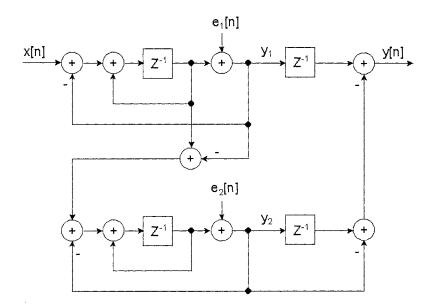

| 2.5 The 2 <sup>nd</sup> order MASH modulator16                                                |

| 2.6 The 2-1-1, 4-bit cascaded multi-bit delta-sigma modulator                                 |

| 3.1 Processes of Bulk and SOI. (Courtesy of IBM Corp)                                         |

| 3.1a Drain/source to substrate capacitance ( $C_{db}/C_{sb}$ ) of Bulk (left) and SOI (right) |

| (Courtesy of IBM Corp)22                                                                      |

| 3.2 Comparison of Bulk and SOI power dissipation. (Courtesy of IBM Corp)23                    |

| 3.3 A general form of a single loop $\Delta - \Sigma$ modulator                               |

| 3.4 A clock buffer driver for analog switches                                                 |

| 3.5 Oversampling ratio in various loop configurations                                         |

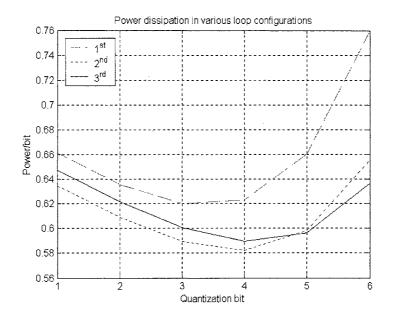

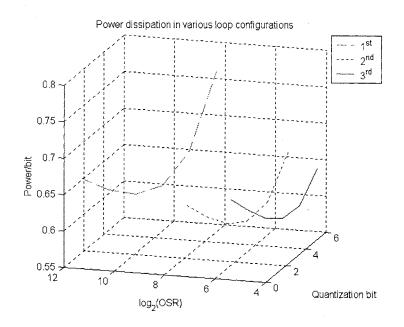

| 3.6 Power dissipation in various loop configurations                                          |

| 3.7 Combination plot of Figure 3.5 and 3.6                                                    |

| 3.8 Z-domain of the $2^{nd}$ order $\Delta - \Sigma$ modulator                                |

| 3.9 Block diagram of a $\Delta$ - $\Sigma$ loop                                               |

| 3.10 Root locus of the modulator NTF                                                          |

| 3.11 Root locus of the modulator NTF at various conditions                                    |

| 3.12 Frequency responses of the modulator STF and NTF                                       |

|---------------------------------------------------------------------------------------------|

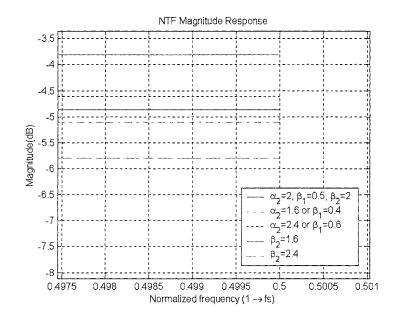

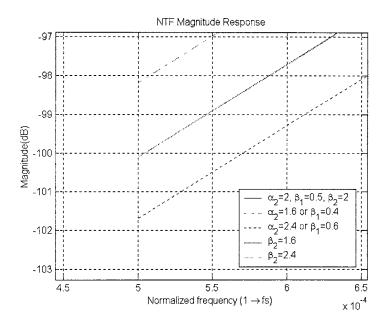

| 3.13 Frequency responses of the modulator NTF at various parameter variations40             |

| 3.13a A section zoom-in of the Figure 3.1340                                                |

| 3.13b A section zoom-in of the Figure 3.1341                                                |

| 3.14 Frequency responses of the modulator STF at multiple $\alpha$ parameter variations 41  |

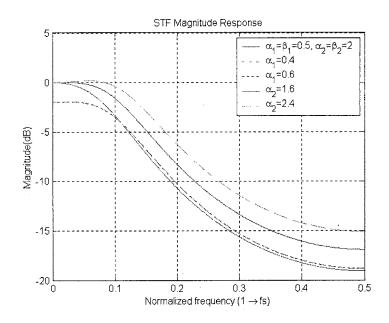

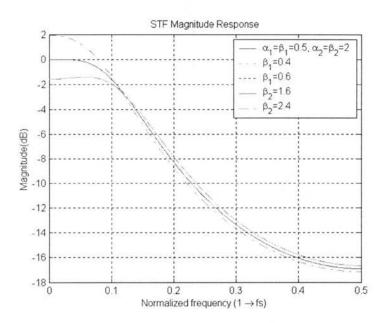

| 3.15 Frequency responses of the modulator STF at multiple $\beta$ parameter variations42    |

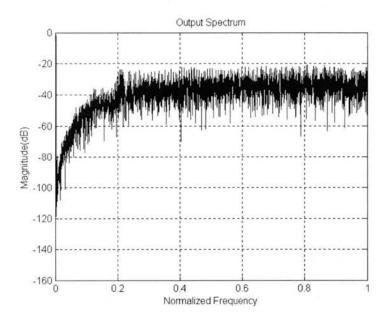

| 3.16 Output spectrum of the modulator                                                       |

| 3.16a A section zoom-in of the Figure 3.1643                                                |

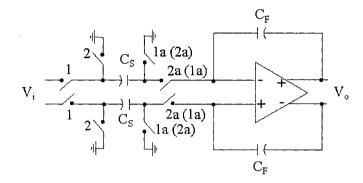

| 3.17 Switched-capacitor implementation of a $2^{nd}$ order $\Delta - \Sigma$ modulator      |

| 3.18 Forward and backward Euler and Trapezoid integrations                                  |

| 3.19 Switched-capacitor implementation of a fully differential integrator                   |

| 3.20 Switched-capacitor implementation of an integrator                                     |

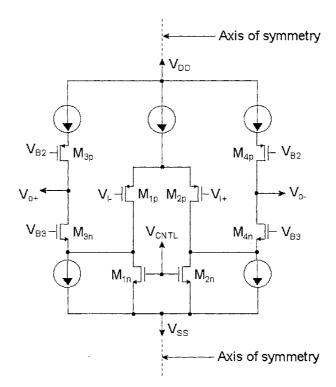

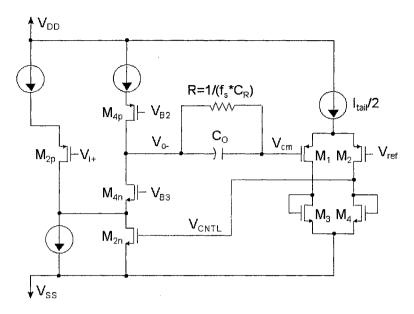

| 3.21 A fully differential folded cascode OTA without the CMFB circuit                       |

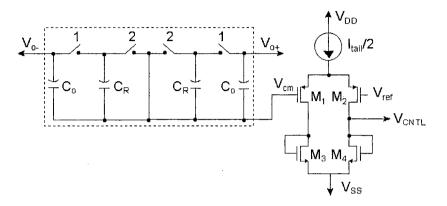

| 3.22 Architecture of the switched-capacitor CMFB circuit                                    |

| 3.23 Circuit diagram of the CMFB loop                                                       |

| 3.24 Equivalent circuit of the switched-capacitor section of the CMFB circuit               |

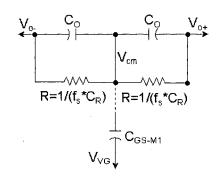

| 3.25 Circuit diagram of the low power regenerative quantizer60                              |

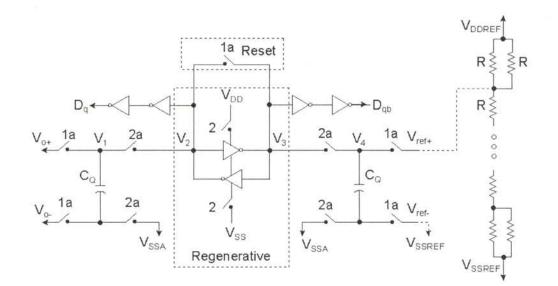

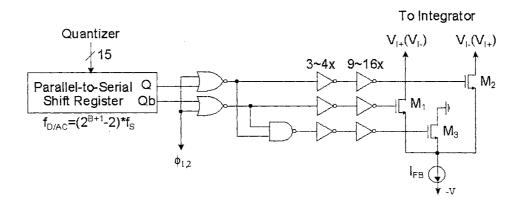

| 3.26 Circuit diagram of the parallel-to-serial current feedback D/AC64                      |

| 3.27 Circuit diagram of the parallel-to-serial shift register                               |

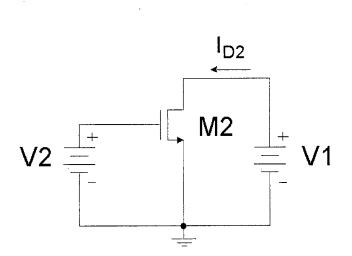

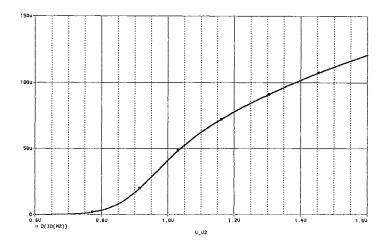

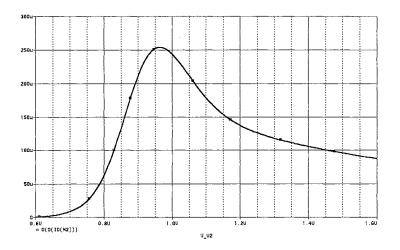

| 3.28 Circuit schematics of testing a single transistor72                                    |

| 3.29 The 1 <sup>st</sup> derivative of the simulated $I_D (g_m vs V_{ov})$                  |

| 3.30 The $2^{nd}$ derivative of the simulated I <sub>D</sub> ( $\beta$ vs V <sub>ov</sub> ) |

| Figure Pa                                                                       | ıge |

|---------------------------------------------------------------------------------|-----|

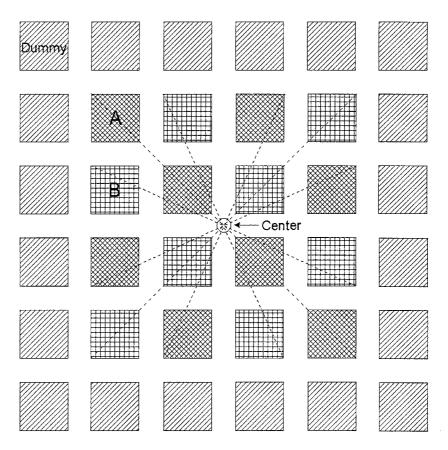

| 3.31 Layout pattern of a common-centroid                                        | 76  |

| 3.32 Layout pattern of an interdigitate                                         | 77  |

| 4.1 Block diagram of a gerneral $\Delta$ - $\Sigma$ A/DC                        | 78  |

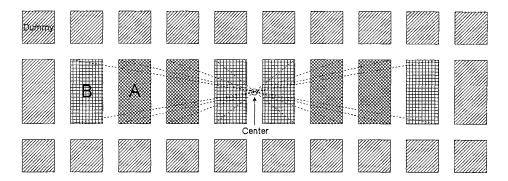

| 4.2 Frequency responses of an A/DC output and a decimation filter               | 79  |

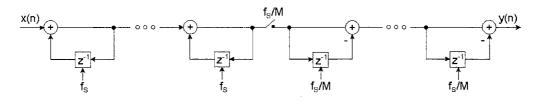

| 4.3 Block diagram of a general moving average filter                            | 80  |

| 4.4 Block diagram of a general Sinc filter                                      | 82  |

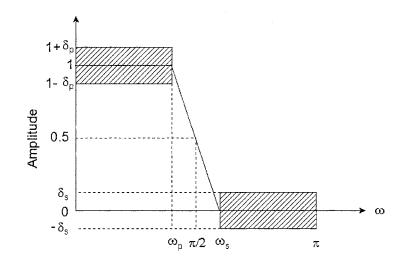

| 4.5 Design criteria of a half-band filter                                       | 84  |

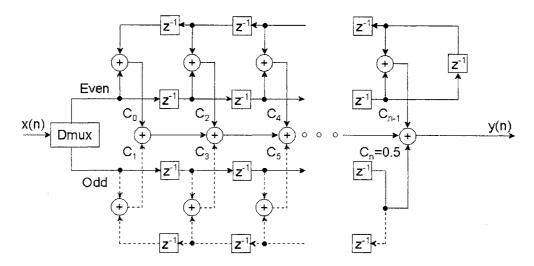

| 4.6 Poly-phase implementation of a half-band filter                             | 86  |

| 4.7 Block diagram of a general two-path filter                                  | 87  |

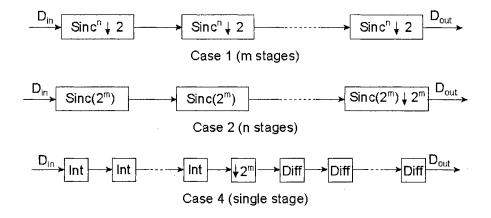

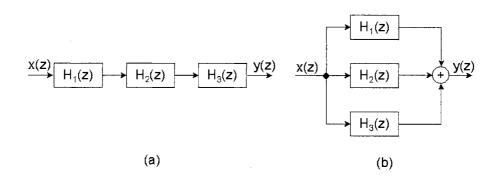

| 4.8 Block diagrams of various Sinc filters                                      | 87  |

| 4.9 Comparison of filter power dissipations                                     | 88  |

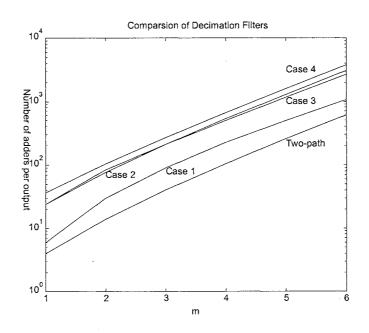

| 5.1 Block diagram of a filter in (a) cascade and (b) parallel                   | 90  |

| 5.2 Block diagram of a general decimation filter                                | 92  |

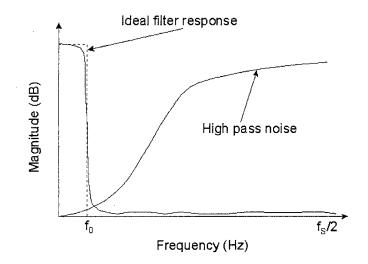

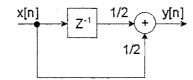

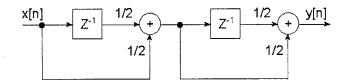

| 5.3 Circuit diagram of the 1 <sup>st</sup> order FIR                            | 93  |

| 5.4 Frequency response of the 1 <sup>st</sup> order FIR                         | 94  |

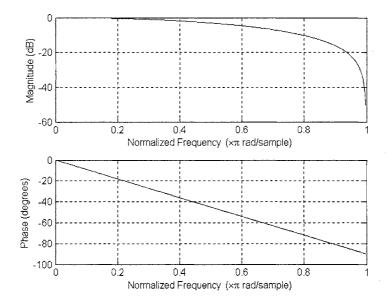

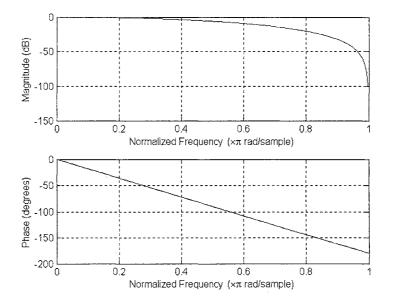

| 5.5 Architecture of the 2 <sup>nd</sup> order FIR                               | 95  |

| 5.6 A triangular window as the result of convolution of two rectangular windows | 96  |

| 5.7 Frequency response of the 2 <sup>nd</sup> order FIR                         | 96  |

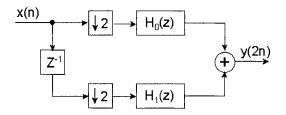

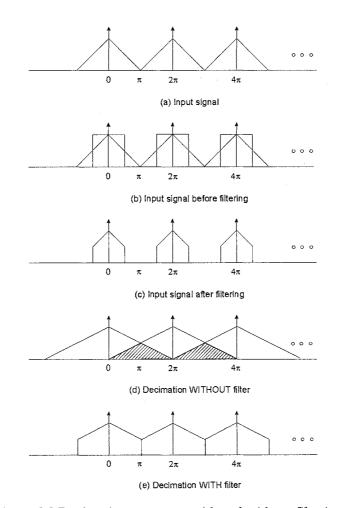

| 5.8 Decimation processes with and without filtering                             | 97  |

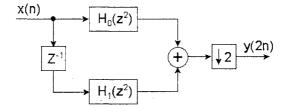

| 5.9 Single path filter approach (data filtered BEFORE frequency decimation)     | 99  |

| 5.9a Two-path filter approach (data filtered BEFORE frequency decimation)       | 99  |

| 5.9b Two-path filter approach (data filtered AFTER frequency decimation)        | 99  |

-

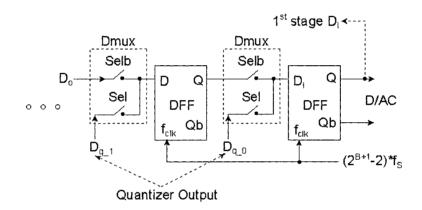

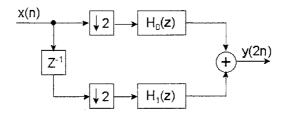

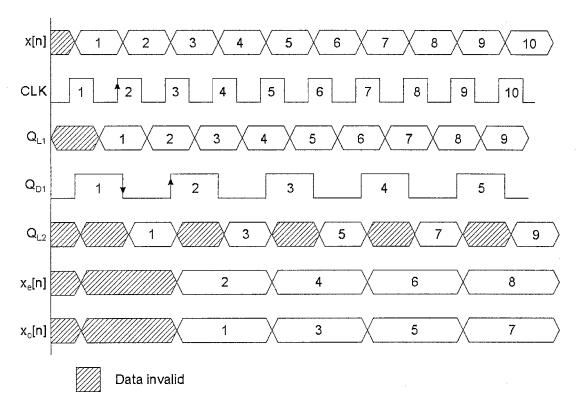

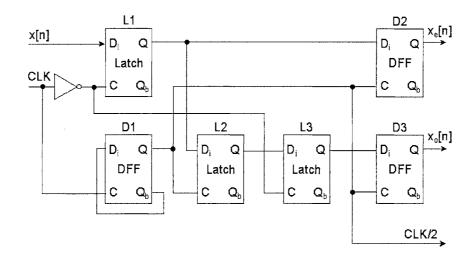

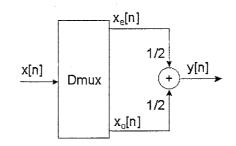

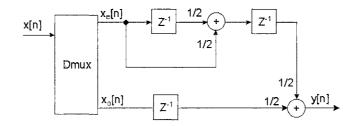

| 5.10 Circuit diagram of the data multiplexer (Dmux) 102                                  |

|------------------------------------------------------------------------------------------|

| 5.11 Timing diagram of the Dmux 103                                                      |

| 5.12 Circuit diagram of the improved data multiplexer104                                 |

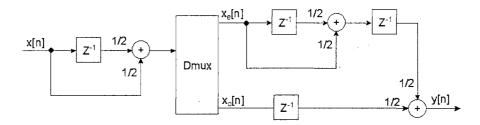

| 5.13 Block diagram of the 1 <sup>st</sup> order two-path filter 105                      |

| 5.14 Block diagram of the 2 <sup>nd</sup> order two-path filter106                       |

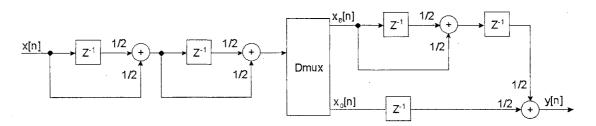

| 5.15 Block diagram of the 3 <sup>rd</sup> order two-path filter108                       |

| 5.16 Block diagram of the 4 <sup>th</sup> order two-path filter                          |

| 5.16a Low power version of the 4 <sup>th</sup> order two-path filter109                  |

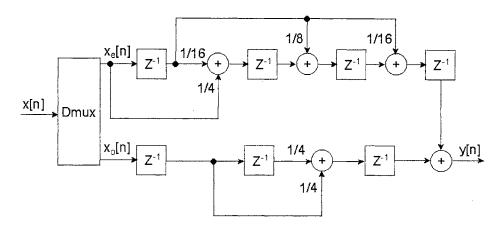

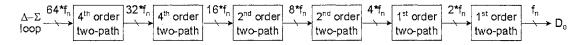

| 5.17 Architecture of the 64 times decimation filter                                      |

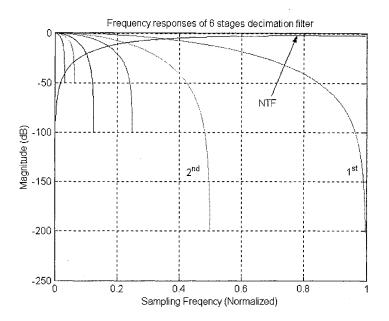

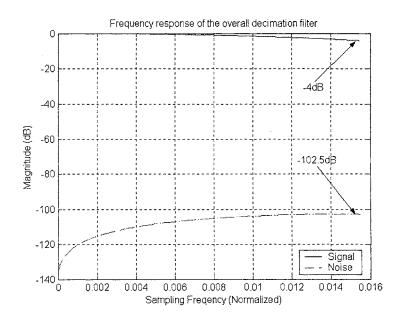

| 5.18 Frequency response of the filter and the NTF of the modulator                       |

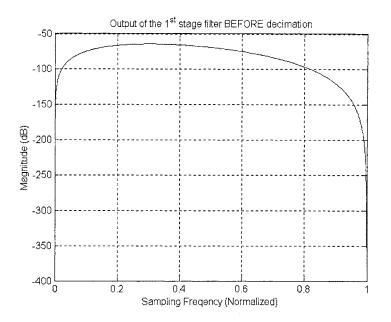

| 5.19 Frequency response of the 1 <sup>st</sup> stage filter output BEFORE decimation 112 |

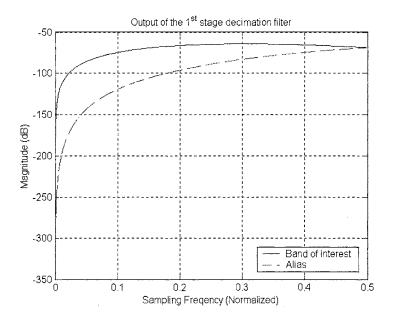

| 5.20 Frequency response of the 1 <sup>st</sup> stage filter output AFTER decimation112   |

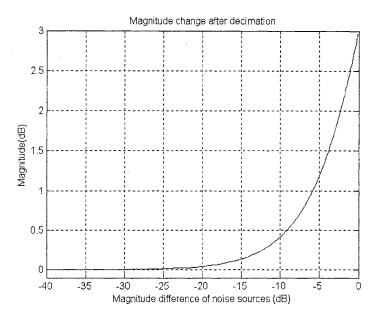

| 5.21 Aliasing effect to the noise floor                                                  |

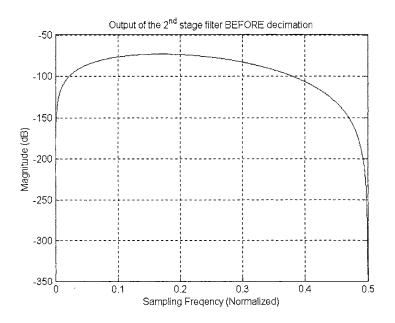

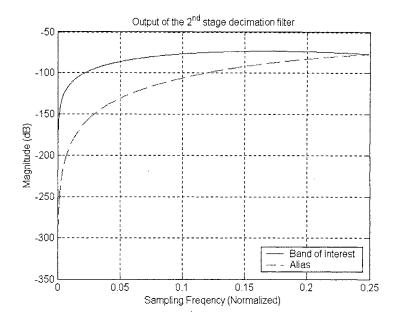

| 5.22 Frequency response of the 2 <sup>nd</sup> stage filter output BEFORE decimation     |

| 5.23 Frequency response of the 2 <sup>nd</sup> stage filter output115                    |

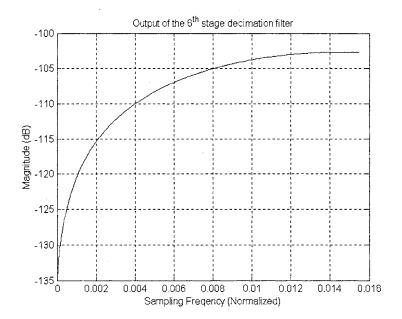

| 5.24 Frequency response of the last stage filter output115                               |

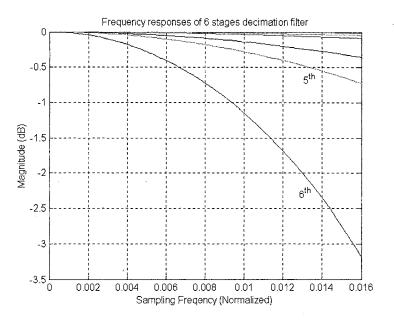

| 5.25 Frequency response of each stage at pass-band117                                    |

| 5.26 Frequency response of signal vs noise floor                                         |

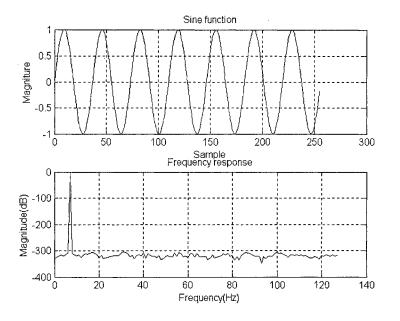

| 6.1 Signal is captured in a complete cycle                                               |

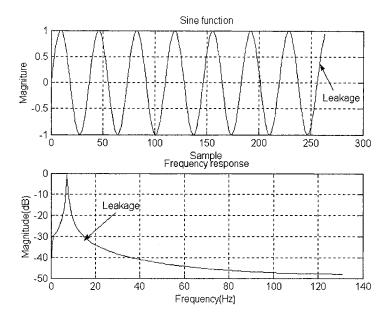

| 6.2 Signal is captured in incomplete cycle                                               |

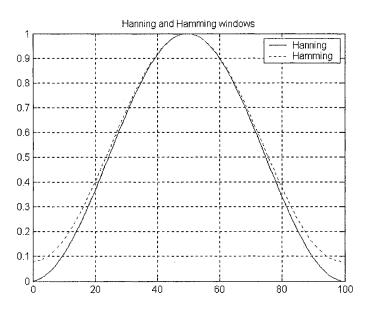

| 6.3 Comparison of window functions 121                                                   |

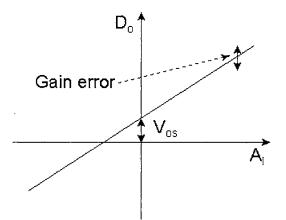

| 6.4 Gain and offset errors of an A/DC126                                                 |

| Figure                                                                        | Page   |

|-------------------------------------------------------------------------------|--------|

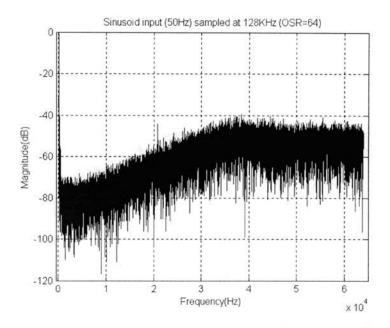

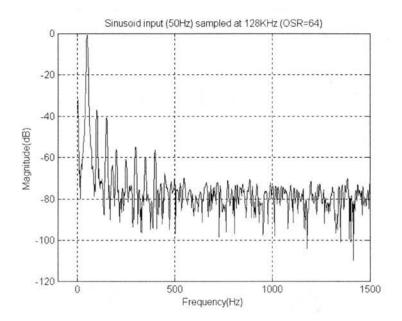

| 6.5 Frequency response of the AFE output                                      | 127    |

| 6.5a A section zoom-in of the Figure 6.5                                      | 127    |

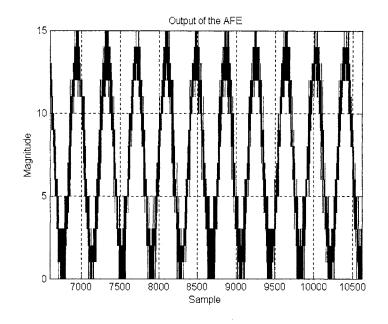

| 6.6 The AFE output in time domain                                             | 128    |

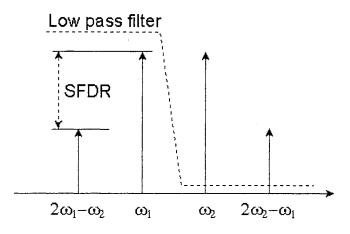

| 6.7 Intermodulation of two signals                                            | 129    |

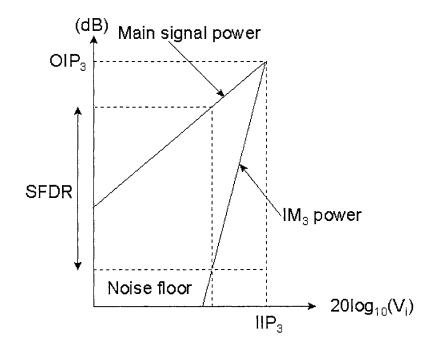

| 6.8 Graphical interpolation of SFDR                                           |        |

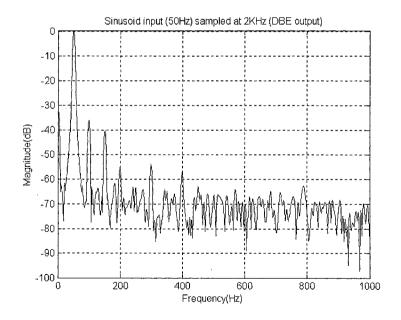

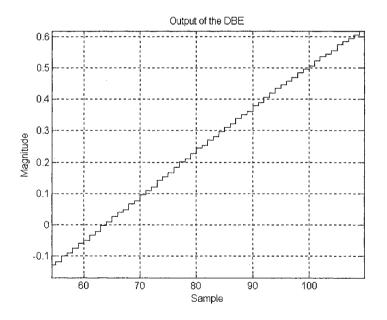

| 6.9 Frequency response of the DBE output                                      |        |

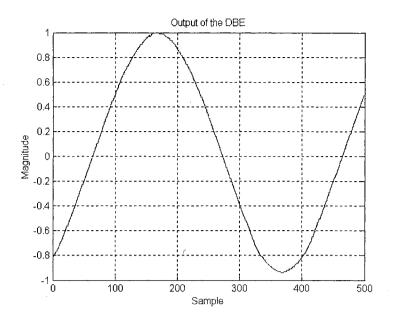

| 6.10 The DBE output in time domain                                            |        |

| 6.10a A section zoom-in of the Figure 6.10                                    |        |

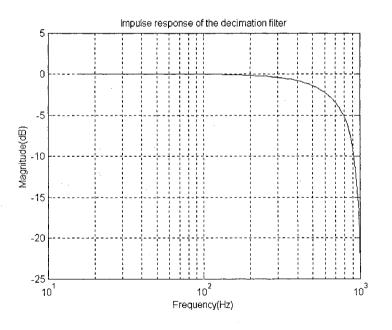

| 6.11 Impulse response of the DBE                                              |        |

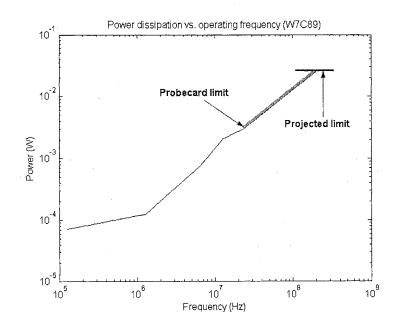

| 6.12 Re-plot the power dissipation per bit of the Figure 3.7 with $K_Q = 0$ . | 027134 |

| 6.13 Power dissipation and projection of the DBE                              | 135    |

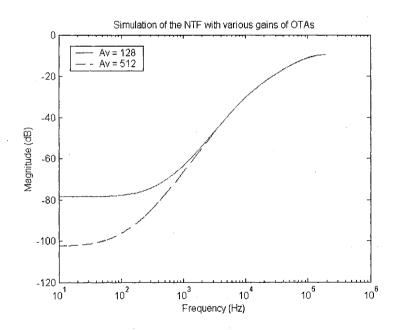

| 7.1 Simulation of the NTF with the gains of OTAs at 128 and 512               |        |

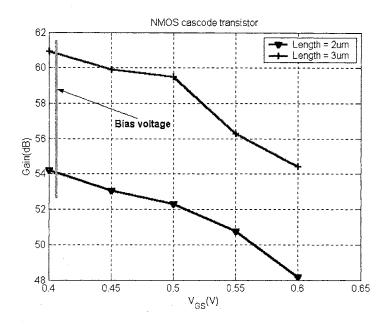

| 7.2 Projected gain of the OTA using the NMOS cascode measurement              |        |

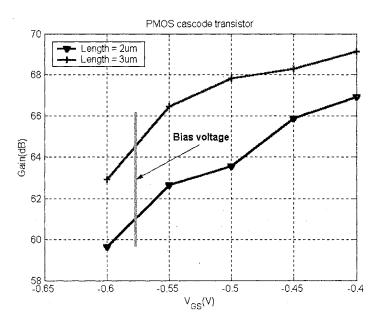

| 7.3 Projected gain of the OTA using the PMOS cascode measurement              | 140    |

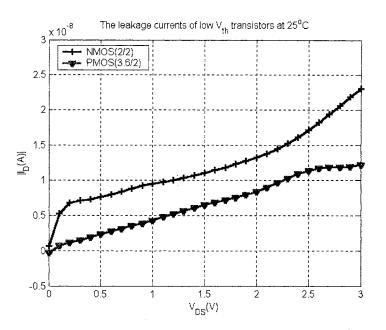

| 7.4 Measured leakage current of low V <sub>th</sub> transistors               |        |

| 7.5 Circuit elements determine body bias                                      | 144    |

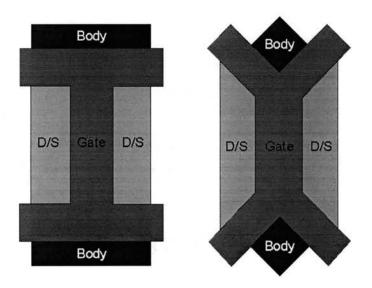

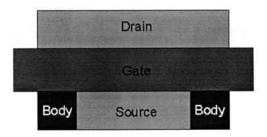

| 7.6 Two possible payouts of the H-gate                                        | 145    |

| 7.7 Layout of the BTS gate                                                    |        |

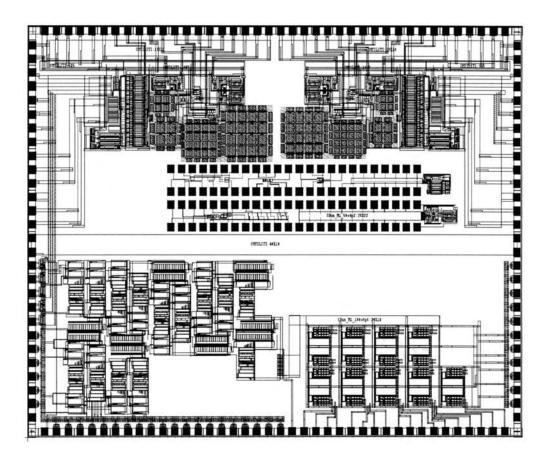

| A.1 Screen capture of the chip layout                                         |        |

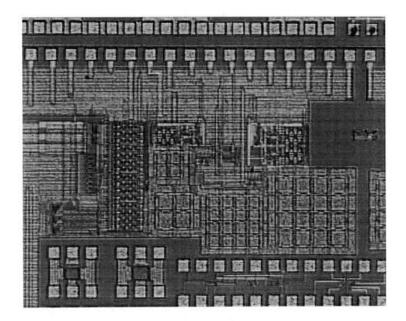

| A.2 Die photograph of the 18-bit modulator (upper left)                       | 155    |

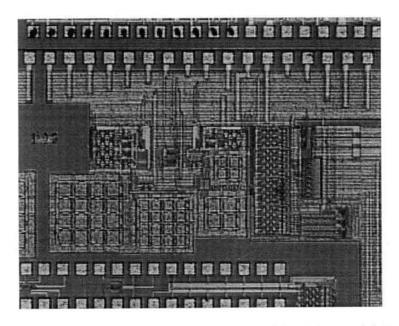

| A.3 Die photograph of the 16-bit modulator (upper right)                      |        |

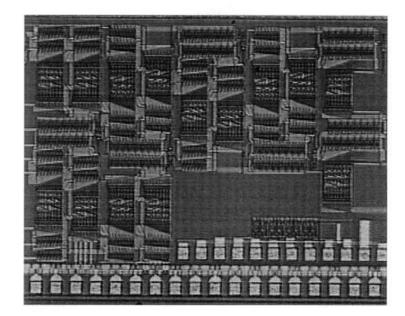

| A.4 Die photograph of the decimation filter (lower left)                      |        |

xi

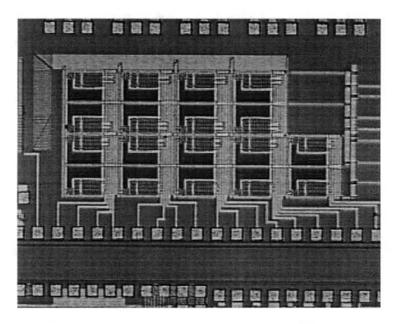

| A.5 Die photograph of the | pad driver (lower right) |  |

|---------------------------|--------------------------|--|

|---------------------------|--------------------------|--|

### LIST OF TABLES

| Table                                              | Page |

|----------------------------------------------------|------|

| 3.1 Power dissipation cost of improving resolution |      |

| 3.2 The effects of the loop coefficients           |      |

| 3.3 Clock phase assignment of the modulator        | 69   |

| 3.4 Design parameters vs. OTA parameters           | 72   |

| 5.1 Aliasing effect to the noise floor             |      |

| 6.1 Window functions and characteristics           | 122  |

| 6.2 General guideline to select applied windows    | 123  |

| 6.3 Power dissipation of the components in AFE     |      |

| A.1 Transistor count and sizes of the components   |      |

# NOMENCLATURE

| AAF             | Antialiasing filter              |

|-----------------|----------------------------------|

| A/DC            | Analog to digital converter      |

| AFE             | Analog front end                 |

| $A_0$           | Open loop DC gain                |

| В               | Quantizer number of bit          |

| BW              | Bandwidth                        |

| $C_F$           | Feedback/Integration capacitance |

| C <sub>gs</sub> | Gate to source capacitance       |

| $C_{db}$        | Drain to body capacitance        |

| $C_L$           | Load capacitance                 |

| CMFB            | Common mode feedback             |

| C <sub>OX</sub> | Gate oxide capacitance           |

| CPU             | Central processing unit          |

| Cs              | Sampling capacitance             |

| $C_{sb}$        | Source to body capacitance       |

| D/AC            | Digital to analog converter      |

| DBE             | Digital back end                 |

| Δ               | Quantization step size           |

| DFF             | D type flip-flop                 |

| DMUX            | Data multiplexer                 |

| DNL             | differential non-linearity       |

| DR              | Dynamic range                    |

| DSP             | Digital signal processor         |

| $\mathbf{f}_0$  | Base-band frequency              |

| $F_{\text{in}}$ | Input frequency                  |

xiv

| $\mathbf{f}_{c}$          | Corner frequency                                            |

|---------------------------|-------------------------------------------------------------|

| FIR                       | Finite impulse response                                     |

| FFT                       | Fast Fourier Transform                                      |

| $\mathbf{f}_{M}$          | Full power bandwidth                                        |

| $\mathbf{f}_{max}$        | Power gain frequency                                        |

| $\mathbf{f}_n$            | Nyquist frequency $(2*f_0)$                                 |

| $\mathbf{f}_{s}$          | Sampling frequency                                          |

| $\mathbf{f}_{\mathrm{T}}$ | Current gain frequency                                      |

| $\mathbf{f}_{TA}$         | Analog current gain frequency                               |

| $f_{TD}$                  | Digital current gain frequency                              |

| GBP                       | Gain bandwidth product                                      |

| g <sub>m</sub>            | Mutual transconductance                                     |

| g <sub>ds</sub>           | Drain to source conductance                                 |

| IIR                       | Infinite impulse response                                   |

| INL                       | Integral non-linearity                                      |

| $I_{\text{tail}}$         | Tail current                                                |

| k                         | Boltzmann's constant $(1.38 \times 10^{-23} J_{K^{\circ}})$ |

| Ksps                      | Kilo samples per second                                     |

| L                         | Channel length                                              |

| L <sub>eff</sub>          | Effective channel length                                    |

| LSB                       | Least significant bit                                       |

| М                         | Down sample rate                                            |

| m                         | Current source/sink number (Leg)                            |

| MSB                       | Most significant bit                                        |

| n                         | Number of bit in SNR                                        |

| MOSFET                    | Metal oxide semiconductor field effect transistor           |

| NTF                       | Noise transfer function                                     |

| 0                         | $\Delta$ - $\Sigma$ loop order                              |

| OSR                       | Oversampling ratio                                          |

| OTA                       | Operational transconductance amplifier                      |

| R <sub>in</sub>           | Input resistance                                            |

|                           |                                                             |

| R <sub>on</sub>        | Transistor on resistance                  |

|------------------------|-------------------------------------------|

| RMS                    | Root mean square                          |

| SC                     | Switched capacitor                        |

| SFDR                   | Spurious free dynamic range               |

| SNR                    | Signal to noise ratio                     |

| SOI                    | Silicon on insulator                      |

| SOS                    | Silicon on sapphire                       |

| SR                     | Slew Rate                                 |

| $\mathbf{P}_{analog}$  | Analog power dissipation                  |

| P <sub>avg</sub>       | Average noise power                       |

| $\mathbf{P}_{digital}$ | Digital power dissipation                 |

| PSRR                   | Power supply rejection ratio              |

| q                      | Electron charge $(1.6 \times 10^{-19} C)$ |

| q <sub>e</sub>         | Quantization error                        |

| τ                      | Settling time constant                    |

| t <sub>f</sub>         | Fall time                                 |

| t <sub>ox</sub>        | Oxide layer thickness                     |

| t <sub>r</sub>         | Rise time                                 |

| t <sub>s</sub>         | Sampling period                           |

| V <sub>BS</sub>        | Source to body voltage                    |

| V <sub>DS</sub>        | Drain to source voltage                   |

| V <sub>GS</sub>        | Gate to source voltage                    |

| $V_{FS}$               | Full scale voltage                        |

| $V_{G}$                | Gate voltage                              |

| V <sub>GS</sub>        | Gate to source voltage                    |

| V <sub>in</sub>        | Input voltage                             |

| V <sub>n</sub>         | Noise voltage                             |

| $V_{ref}$              | Accurate reference voltage                |

| V <sub>os</sub>        | Offset voltage                            |

| V <sub>out</sub>       | Output voltage                            |

| V <sub>OV</sub>        | Overdrive voltage ( $V_{GS}$ - $V_{th}$ ) |

|                        |                                           |

xvi

| $V_{T}$          | Thermal voltage         |

|------------------|-------------------------|

| $V_{\text{th}}$  | Threshold voltage       |

| $V_{VG}$         | Virtual ground voltage  |

| W                | Channel width           |

| W <sub>eff</sub> | Effective channel width |

#### CHAPTER 1

#### INTRODUCTION

The analog to digital converter (A/DC) and digital to analog converter (D/AC) are two essential components connecting the real world and the digital domains. Due to the high successful rate of digital circuit implementations and the fabrication process advancement of integrated circuit (IC) focusing only on digital circuits, many analog circuits (e.g. filters) are now replaced by their digital equivalents. As a result, the locations of the converters are shifted very close to the input/output of the systems, i.e. antennas, speakers and sensory devices. The concept of this approach is to 1) digitize the signal as early as possible; 2) retain the signal in digital domain as long as possible, due to the superiority of the noise immunity of the digital circuits. Potentially more significant is their superior availability to design automation.

Resolution and power dissipation are two important issues involved in A/DC designs. Due to the small and weak amplitude of the sensor output, the converters with high resolution are required to precisely interpret the information. However, poor component matching and reduced power supply levels of the advanced process technologies hinder many high precision A/DC implementations, and further reveal the design challenges. Although many error correction techniques have been developed to

implement precision Nyquist rate ADCs, it is still very difficult to achieve more than 12bit of accuracy. On the contrary, oversampled  $\Delta-\Sigma$  A/DCs are well suited for implementation in VLSI technology due to their efficient means of exchanging speed for resolution and their high tolerance to component mismatches and circuit non-idealities.

Power dissipation is the second issue of an A/DC design. As a result of low power CMOS many sensory or telecommunication devices are portable and battery powered. The improvement of the long-life battery is slow, and as a result converters with low power design are necessary to extend the life of the battery. Processes and system architectures are critical for power efficient product design. Today's advanced thin-film SOS/SOI CMOS VLSI processes with lower parasitic capacitance, smaller feature size, and insulated substrate have encouraged such converter designs and related circuits to be fabricated on one chip to lower power dissipation.

In today's standard digital CMOS process, low power and high resolution  $\Delta -\Sigma$ A/DCs have gained a unique role in cost effective mixed mode IC application. However, process power supply down scale and the high demand for lower power consumption still pose the great challenges regarding  $\Delta -\Sigma$  A/DCs research.

1.1 Objective

The objective of this project is to build high resolution and low power A/DCs. The selected delta-sigma architecture consists of the modulator or AFE and the decimation filter or DBE. The decimation filter does not improve the resolution but degrade it if not carefully designed. Therefore, the project requirements listed below are specified for the modulators addressed in this thesis.

- 18-bit 1Ksps @ 1mW

- 16-bit 2Ksps @ 0.5*mW* and 10Ksps @ 2*mW*

The decimation filter in this dissertation is designed for 64/32 times decimation, which is to accommodate the above modulators designed using the oversampling scheme and to interpolate the resolution of the coarse modulator output.

#### 1.2 Organization

Chapter 1 introduces the background and the purpose for this study.

Chapter 2 reviews the analog to digital conversion processes and available low power  $\Delta-\Sigma$  A/DC architectures.

Chapter 3 discusses the modulator in detail and its implementation. The low power design strategy, system stability, resolution improvement, and circuit consideration are included.

Chapter 4 reviews the decimation processes and available architectures of decimation filters. Two-path decimation filter is introduced.

Chapter 5 discusses the low power strategies of the decimation filter and the filter implementation. The constructions of the two-path filter and the data multiplexer are included.

Chapter 6 introduces basic A/DC characterization and sampling methods to improve the results of Fast Fourier Transform (FFT).

Chapter 7 summarizes the results of this study, conclusions, and proposes some improvements.

#### CHAPTER 2

#### DELTA-SIGMA MODULATOR OVERVIEW

Analog to digital conversion is the process by which analog values are mapped to their digital counterparts. From the viewpoint of digital algorithms, the number of bit of the processor limits the precision. From the viewpoint of the circuit implementation without CPU or DSP, the technology of the chip fabrication and circuit architecture are the limitations. The improvement of the fabrication process is beyond the scopes of circuit designers. However, understanding the technology is the key to the designer's ability to overcome the imperfection of the fabrication by creating better architectures and techniques. The oversampling technique, for example, is taking advantage of the process technology that advances (increasing  $f_T$ ) solely for the digital circuits.

#### 2.1 Types of A/DCs

Based on the sampling frequency, A/DCs can be categorized to two groups: Nyquist and oversampling. There is no specific guideline to use the certain type of A/DC, and it is the designer's advantage making the selection. In general, for applications with low resolution and wide input bandwidth, the Nyquist A/DC is a good candidate. For the

requirement of high resolution and low bandwidth, oversampled A/DCs have advantages. Both types of A/DCs have the same conversion errors (or noises) that designers strive to eliminate. In the following sections, three commonly used A/DCs (Nyquist, oversampling, and delta-sigma) will be introduced along with their techniques to improve the accuracy.

2.1.1 Nyquist A/DC

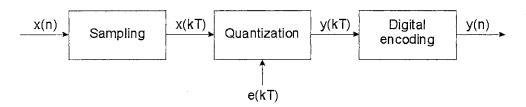

Figure 2.1 shows the general form of an A/DC. The sampled input value, x(kT), is rounded to the nearest level during the quantization. Since it is not the exact conversion, the quantized output can be described as

$$y(kT) = x(kT) + e(kT)$$

(2.1)

Figure 2.1 Block diagram of a general A/DC.

The quantization noise, e(kT), is dependent on the amplitude of x(kT) and is in the interval between  $-\Delta/2$  and  $-\Delta/2$ . Note that the quantization step size [1] is defined as

$$\Delta = \frac{V_{FS}}{2^B} \tag{2.2}$$

The noise power (variance) [1-2] can be found as

$$\sigma^{2} = E[e^{2}] = \frac{1}{\Delta} \int_{-\Delta/2}^{\Delta/2} e^{2} de = \frac{\Delta^{2}}{12}$$

(2.3)

where E denotes statistical expectation. Since the noise power spectrum is spread uniformly over the frequency range, the level of the noise power spectral density of a Nyquist A/DC can be expressed as

$$N_{Nyquist}(f) = \frac{\Delta^2}{12} \frac{1}{f_n}$$

(2.4)

Assuming that the input signal is a sinusoidal wave and its maximum peak value without clipping is  $|_{N_{n-\varepsilon}(f)}|_{=\left(2\sin\frac{\pi}{f_{n}}\right)^{\alpha}}$ , the signal power,  $P_{signal}$ , is equal to

$$P_{signal} = \left(\frac{\Delta 2^{B}}{2\sqrt{2}}\right)^{2} = \frac{\Delta^{2} 2^{2B}}{8}$$

(2.5)

The noise power of a Nyquist A/DC is

$$P_{noise} = \frac{\Delta^2}{12} \tag{2.6}$$

and the maximum *SNR* can be written as

$$SNR_{Nyquist} = 10\log\frac{P_{signal}}{P_{noise}} = 10\log\left(\frac{\Delta^2 2^{2B}/8}{\Delta^2/12}\right) = 10\log\left(\frac{3}{2}2^{2B}\right) = 6.02B + 1.76 \quad (2.7)$$

This states that the resolution of the Nyquist A/DC solely depends on the quantity of the quantizer. An additional bit of quantizer increases the resolution by 6*dB*.

The resolution of the Nyquist A/DC is directly proportional to the number of comparators in the quantizer, and matching between any of two is critical. Current technology of MOS comparators without auto-zeroing permits a minimum comparison of roughly 10mV due to the comparator's inherent offset voltage [2]. Thus, the implementation beyond 10- to 12-bit of resolution is quite difficult without using special calibration techniques, like laser trimming and auto calibration etc. Note that the purpose of presenting the Nyquist A/DC is to describe the quantization error and serve as reference for the ensuing discussions.

### 2.1.2 Oversampling A/DC

An increase in the sampling frequency can improve the resolution over the Nyquist A/DC. Equation 2.4 shows that the noise power spectral density is the function of the sampling frequency ( $f_s = OSR^*f_n$ ). Thus, the oversampled A/DC's noise power spectral density and noise power can be written as

$$N_{Oversampling}(f) = \frac{\Delta^2}{12} \frac{1}{f_n} \frac{1}{OSR}$$

(2.8)

$$P_{noise} = \frac{\Delta^2}{12} \left( \frac{1}{OSR} \right) \tag{2.9}$$

Assuming the same input as Equation 2.5, the *SNR* of the oversampling A/DC can be written as

$$SNR_{Oversampling} = 10\log\frac{P_{signal}}{P_{noise}} = 10\log\left(\frac{\Delta^2 2^{2B}/8}{\Delta^2/12 \cdot OSR}\right)$$

(2.10)

= 10log(OSR) + 6.02B + 1.76

Equation 2.10 states that resolution is a function of the sampling frequency and the doubling the OSR increases the SNR by 3dB or quadrupling the OSR provides an additional bit of resolution.

2.1.3 Δ-Σ A/DCs

The resolution of the oversampling A/DC can be improved significantly by applying the noise shaping techniques (delta-sigma). The principle of the technique is to delay (or low pass) the signal and high pass the noise. The noise power density and noise power [3-4] are expressed as

$$\left|N_{\Delta-\Sigma}(f)\right| = \left(2\sin\frac{\pi f_n}{f_s}\right)^0 \tag{2.11}$$

$$P_{noise} = \left(\frac{\Delta^2}{12}\right) \left(\frac{\pi^{2O}}{2O+1}\right) \left(\frac{1}{OSR}\right)^{2O+1}$$

(2.12)

and the SNR of the  $\Delta$ - $\Sigma$  A/DC is written as follows

$$SNR_{\Delta-\Sigma} = 10\log\left(\frac{3}{2}\frac{(2O+1)}{\pi^{2O}}OSR^{2O+1}2^{2B}\right)$$

$$= (20O+10)\log OSR + 10\log(2O+1) + 6.02B + 1.76 - 9.94O$$

(2.13)

The attraction of the  $\Delta$ - $\Sigma$  A/DC is that the modulator order has a dramatic effect in improving resolution. The resolution is increased approximately 1.5-bit/octave for the 1<sup>st</sup> order system, 2.5-bit/octave for the 2<sup>nd</sup> order, 3.5-bit/octave for the 3<sup>rd</sup> order, etc.

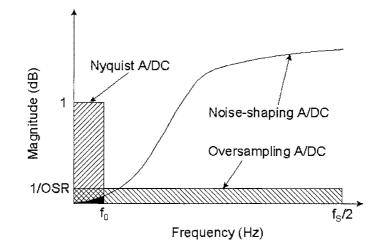

A qualitative view of three A/DC quantization noise powers is shown in Figure 2.2. The figure demonstrates that the in-band noise power of a noise shaping A/DC is much lower than the other techniques. For the out-of-band noise power, the attenuation is done by post digital decimation filter. Therefore,  $\Delta-\Sigma$  A/DCs are very suitable for applications that require high resolution.

Figure 2.2 Noise spectrum comparsion of A/DCs

#### 2.2 Architectures of $\Delta$ - $\Sigma$ A/DCs

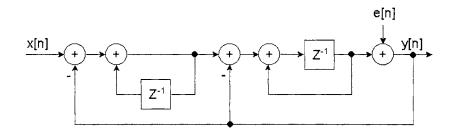

The  $\Delta$ - $\Sigma$  A/DC shows a decisive advantage in the improvement of the resolution. For the applications requiring high resolution, the  $\Delta$ - $\Sigma$  A/DC is the first selection. Over the years, the concept of delta-sigma has been developed and implemented in various forms in order to achieve higher resolution. Recently due to the great demands in the telecommunication area, mature  $\Delta$ - $\Sigma$  architectures are being modified to minimize power dissipation. The two types of architectures most frequently demonstrated in recent publications for low power and high resolution: single loop and multi-stage noise shaping (MASH). In the following sections, both architectures will be introduced and reviewed. Architectural considerations with regard to power dissipation will be discussed in the last section. This is the most basic architecture of the  $\Delta-\Sigma$  modulator. All other modulators are the derivatives with minor alterations. The advantage of this modulator is that it is always stable if the order is less than three [5]. Furthermore, the system is less sensitive to the component imperfection, such as mismatch of the capacitors of the integrators. Figure 2.3 shows the example of the 2<sup>nd</sup> order system.

Figure 2.3 The 2<sup>nd</sup> order single loop modulator.

The meaning of the delta-sigma is embedded inside the architecture; accumulate (sigma) the differences (delta) between input and output signals. Theoretically, the output is equal to the input in the long run. In reality, perfect conversion is still the goal of the ongoing research. The transfer function of the modulator is

$$Y(z) = X(z)z^{-1} + E(z)(1-z^{-1})^2$$

(2.14)

From the equation, the output of the modulator is the combination of the delay input signal and high passed quantization noise. An increase in the order of the modulator

affects the slope of the high pass filter. As the order increases, the slope steepens and the noise floor of the pass-band lowers for the system with optimal pole-zero placement.

Not just increasing the sampling frequency and modulator order, but increasing the number of bits of the quantizer can reduce the quantization step size resulting in SNR improvement. From Equation 2.13, the resolution improvement is directly proportional to the number of bits of the quantizer. However, the drawbacks of this approach are the requirement of the multi-bit D/AC that is non-linear by nature, and the limited number of quantization bits, which has the same limitation as the classical Nyquist A/DC.

The linearity of the modulator is dominated by the linearity of the D/AC, since the latter is in the feedback path. Non-linearity in the multi-bit D/AC will cause harmonic distortion and base-band noise increase due to intermodulation of high frequency noise [4]. Dynamic element matching (DEM) techniques can reduce the D/AC noise [6]. A DEM D/AC consists of an array of coarse D/ACs (D/AC cell) and the output is the sum of D/AC cells in random. This technique reduces the noise power of the D/AC by assuming that element matching error is a random, noise-like structure. By reducing the correlation among successive samples of D/AC noise, harmonic distortion is reduced. The implementation of an 8-bit D/AC with this technique has demonstrated the ability to achieve 90*dB* of SFDR or greater [6].

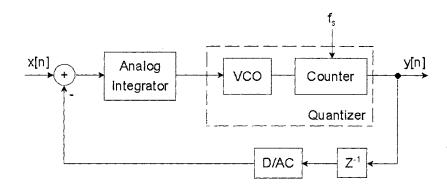

One paper (VCO-DS-ADC) [7] has developed the alternative approach of replacing the quantizer with the combination of a voltage control oscillator (VCO) and a counter, and a 1-bit feedback D/AC. Figure 2.4 redraws the diagram of the paper.

Figure 2.4 Block diagram of VCO-DS-ADC.

The VCO senses the voltage variation of the integrator output, converts to relative phase variation, and adjusts the frequency of the oscillator accordingly. With this approach, the number of the quantization bit is not limited by the component matching but the resolution and linearity of the VCO, which can be improved by better architecture and process advancement. Moreover, the 1-bit D/AC architecture ensures no D/AC non-linearity, and the details of this benefit will be discussed in Chapter 3.

Increasing the number of bits of the quantizer to reduce power dissipation is becoming a trend to lower the power dissipation. In the next section, the similar multi-bit quantizer approach to reduce the power dissipation will be demonstrated again in the example from references.

2.2.2 MASH modulator

The concept of this approach is to build a higher order modulator using the lower order  $\Delta$ - $\Sigma$  modulators as building blocks in cascade. Theoretically, the overall system is stable since the lower order modulators are stable [3]. Moreover, cascading more stages can improve the performance. However, at some point the improvement is limited by the uncanceled noise from the 1<sup>st</sup> stage. Beyond this point, no gain in performance will be realized by adding more stages.

An example of the  $2^{nd}$  order modulator obtained by cascading two first order modulators is shown in Figure 2.5. Note that the  $1^{st}$  stage quantization error  $e_1[n]$  is treated as the input signal of the second modulator. The final digital output y[n] is the difference of the first stage's delayed output  $y_1[n]$  and second stage's differentiated output  $y_2[n]$ . The output equation is written as

$$Y(z) = Y_1(z)z^{-1} - Y_2(z)(1 - z^{-1})$$

(2.15)

where

$$Y_1(z) = X(z)z^{-1} + E_1(z)(1 - z^{-1})$$

(2.15a)

$$Y_2(z) = E_1(z)z^{-1} + E_2(z)(1 - z^{-1})$$

(2.15b)

substituting (2.15a) and (2.15b) into (2.15) and rearranging the equation give

$$Y(z) = X(z)z^{-2} - E_2(z)(1 - z^{-1})^2$$

(2.16)

The quantization error is shaped by the  $2^{nd}$  order high pass filter and the signal is delayed, which has the same performance as the  $2^{nd}$  order single loop architecture except an additional delay (Equation 2.14).

Figure 2.5 The 2<sup>nd</sup> order MASH modulator.

The advantage of using the cascade architecture is shown in Reference [8-9]. For the modulator operated at a typical OSR, the quantization noise spectral density is a smooth continuous function of frequency and is independent of the input signal level. From Equation 2.16, increasing the order of each stage can further reduce the noise. However, in order to cancel the quantization noise of the first loop completely, the gain of the 2<sup>nd</sup> loop must be equal to the gain of the 1<sup>st</sup> loop. Due to the potential capacitor mismatch resulting in the gain error, the implementation of the stage with higher order is limited.

To illustrate the severity of the mismatch, the integrator gain of the 1<sup>st</sup> stage is assumed to be  $\delta$  and the integrator gain of the 2<sup>nd</sup> stage remains one. Equation 2.15a is rewritten as

$$Y_{1}(z) = X(z)\frac{\delta \cdot z^{-1}}{1 + (\delta - 1)z^{-1}} + E_{1}(z)\frac{(1 - z^{-1})}{1 + (\delta - 1)z^{-1}}$$

(2.17)

and the final output is

$$Y(z) = X(z) \frac{\delta \cdot z^{-2}}{1 + (\delta - 1)z^{-1}} - E_2(z) \frac{(1 - z^{-1}) + (\delta - 2)(1 - z^{-1})z^{-1}}{1 + (\delta - 1)z^{-1}} - [E_1(z) - E_2(z)] \frac{(\delta - 1)(1 - z^{-1})z^{-2}}{1 + (\delta - 1)z^{-1}}$$

(2.18)

The equation shows that gain mismatch results in not just the transfer function for signal and noise terms changed but also the additional noise term added.

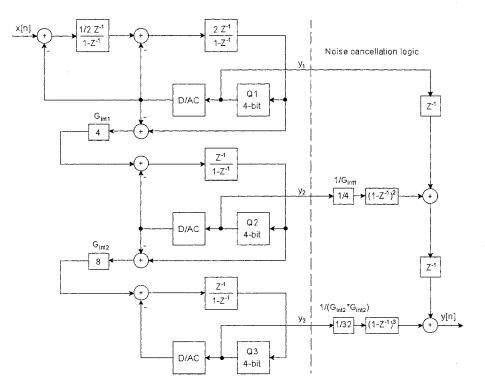

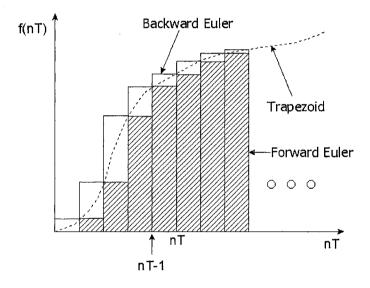

Reference [10] shows the improvement by placing interstage gains. Figure 2.6 is the duplicate from the paper. The 4-bit quantizers used at the 1<sup>st</sup> and 2<sup>nd</sup> stage do not directly reduce theoretical quantization noise (TQN) due to the noise cancellation [10].

However, the smaller quantization error extracted from the preceding stage allows insertion of an interstage gain to utilize the full dynamic range of the next stage. The quantization noise is reduced as

$$N_{TQN}(z) = E_3 (1 - z^{-1})^4 / (G_{int1} G_{int2})$$

(2.19)

Figure 2.6 The 2-1-1, 4-bit cascaded multi-bit delta-sigma modulator.

The reduction of quantization noise leakage (QNL) that results from the gain and pole errors of the integrators due to finite gains of the OTAs, is the other benefit to the use of 4-bit quantizers in the first two stages. In addition, optimizing the interstage gains and the use of high gain OTAs can reduce the QNL further and shown as;

$$N_{QNL}(z) \approx 6E_1(1-z^{-1}) / A_{OL} + (9+2G_{\text{int}\,1})E_1(1-z^{-1})^2 / A_{OL}$$

(2.20)

where  $A_{OL}$  is the open loop gain of the OTA. Equation 2.20 suggests that  $G_{int1}$  should be as small as possible while Equation 2.19 suggests that  $G_{int2}$  should be as large as possible without overloading the final stage.

The advantage of the MASH A/DCs is that no stability issues exist as a result of the higher order architecture as long as the stages in cascade are all stable. The drawback is the requirement of the precise matching in order to eliminate the QNL of the 1<sup>st</sup> stage, which is still the challenge in the fabrication process. As a result, the MASH architecture is still less attractive when compared to the single loop with potentially higher successful rate in fabrication, even though the stability issue exists in the high order (beyond 3<sup>rd</sup>) single loop architecture.

#### 2.3 Power dissipation consideration

The growing trend in reducing the power dissipation is to increase the number of quantization bits. Both examples of single loop and MASH architectures show the same approach. An increase in the number of quantization bits allows the modulator to reduce the oversampling rate or order. In addition, power dissipation is reduced since the comparators of the quantizer are essentially all digital circuits and offer less complexity, consuming less power relative to integrators.

In Chapter 3, the modulator order, the oversampling ratio, and the number of bits of the quantizer of the modulator will be explored to achieve improved resolution and power dissipation. The number of bits of the modulator will play an important role in the reduction of power dissipation.

## CHAPTER 3

### MODULATOR DESIGN AND IMPLEMENTATION

This chapter describes the design concepts and circuit implementations of low power  $\Delta - \Sigma$  Modulators. Since the design objective of this project is to minimize the power consumption, the design flow and strategies will focus on the four most significant aspects of a design: process, architectures, circuits, and devices. Their effects on the power dissipation are itemized as the order increases. In addition, reducing the power supply voltage decreases the power consumption but deteriorates the potential system's dynamic range. Various techniques will be deployed to maintain the SNR while minimizing power dissipation. Moreover, layout techniques are briefly described with regard to overcoming some process variations.

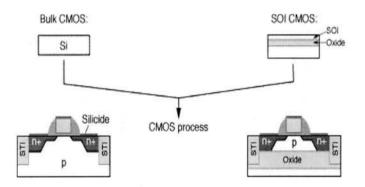

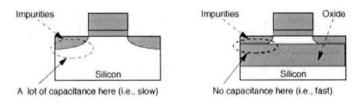

#### 3.1 Low power processes, Bulk or SOI?

The process selection is the first step toward the successful low power circuit designs. Large device leakage current and coupling capacitance, or costly process features, such as GaAs, are not suitable for this project. In this case, there are only two choices: Bulk or SOI.

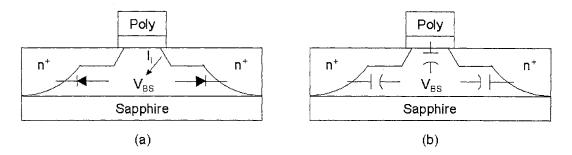

Both processes virtually share the same process procedures (Figure 3.1) except that an additional oxidation process, at beginning, to the wafer results in the formation of insulation layer in SOI processes. This exception is the major advantage and improvement of SOI over Bulk. Figure 3.1a shows no parasitic capacitances between drain/source and substrates. Since  $C_{db}$  is a major contribution of the transistor's output capacitance, its reduction will significantly reduce digital circuit power dissipation, based on the Equation 3.1. Lowering digital power provides more design freedom to the analog circuit designer under a power budget constraint. In addition, the reduction of  $C_{db}$  and  $C_{sb}$ reduces the transistor leakage.

Figure 3.1 Processes of Bulk and SOI. (Courtesy of IBM Corp.)

Figure 3.1a Drain/source to substrate capacitance (C<sub>db</sub>/C<sub>sb</sub>) of Bulk (left) and SOI (right).

(Courtesy of IBM Corp.)

$$P_{digital} = CV^2 f \tag{3.1}$$

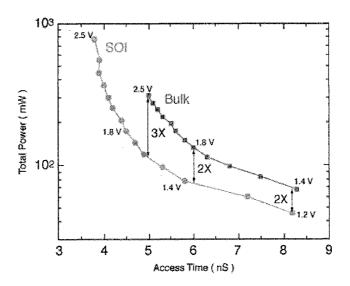

Figure 3.2 shows the comparison of digital power dissipation of Bulk and SOI. At the same operating frequencies, power consumption of SOI is 2~3 times lower than of Bulk.

Based on the information above, SOI technology is considered the best candidate for the low power digital circuit implementation. In this dissertation, the designed circuits are all fabricated on the Peregrine SOS process to minimize the power consumption. Note that the only significant difference between SOI and SOS is their substrates: SiO<sub>2</sub>/Silicon for SOI and Sapphire for SOS.

Figure 3.2 Comparison of Bulk and SOI power dissipation.

(Courtesy of IBM Corp.)

Analog power dissipation is governed by

$$P_{ana\log} = IV \tag{3.2}$$

The constant currents, which are used to bias the transistors in saturation (active) region, are the primary source of the power dissipation. A wide-band OTA, for example, requires large currents since its bandwidth is proportional to the bias current. High mobility and thick gate oxide processes can help to reduce the power. However, the trend of CMOS technology is to scale down the gate oxide along with other parameters, which makes the low power analog circuit design more challengeable than ever.

3.2 Architectural configuration and power estimation of a  $\Delta - \Sigma$  modulator

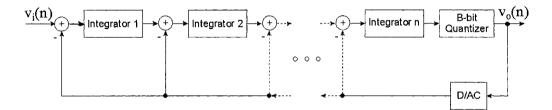

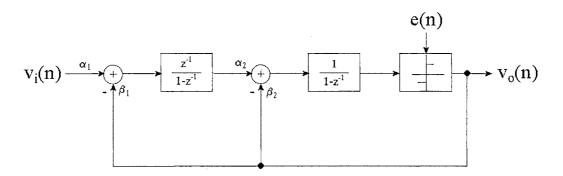

In Chapter 2, the single loop  $\Delta - \Sigma$  modulator has been demonstrated with its benefits and high successful rate in fabrication. In this section, a low power configuration of the modulator will be developed from the architecture shown in Figure 3.3.

Figure 3.3 A general form of a single loop  $\Delta$ - $\Sigma$  modulator.

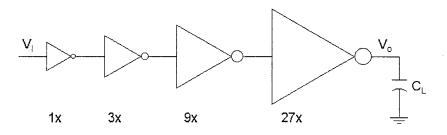

The modulator includes 4 major components: clock driver, integrator, quantizer, and D/AC. A clock driver as shown in Figure 3.4 is the cascade of the inverters. The purpose of this formation is to isolate the large load from the driving signal so the signal quality will not degrade as the load increase. The number of the stage depends on the ratio of the

load and input capacitance and the scaling factor. The factor,  $e \cong 2.7183$ , is an optimal number [11] but here it is rounded to 3 for simplicity.

Figure 3.4 A clock buffer driver for analog switches.

The power dissipation of the clock driver is considered as digital power and governed by Equation 3.1. It is small compared to the power of the integrator or quantizer. For example, both the clock driver and integrator are running at 100*KHz*. Note that the power supply is assumed unity to simplify the calculation. The power dissipation of the clock driver is

$$P_{digital} = CV^2 f \cong 100 \cdot 10^{-15} \cdot (1)^2 \cdot 10^5 \propto 10^{-8}$$

(3.3)

where  $100*10^{-15}$  is the total capacitance of the clock driver equivalent to the unit inverter which is in the range of *fF*. For the OTA, the supply current is approximately 10*uA* and 7 to 8 of such currents are required.

$$P_{analog} = IV \cong (7 \sim 8) \cdot 10^{-5} \cdot (1) \propto 10^{-4}$$

(3.4)

The ratio of analog to digital power is  $10^4$  and therefore, the power of the clock driver can be ignored.

A serial D/AC (details discussed later) is used in this project and consists of only three transistors. Compared to the rest of loop components, its power dissipation is so low as to be excluded in this discussion. Note that the power of the parallel-to-serial shift register used in conjunction with the serial D/AC, will be summed together with the quantizer's power.

After excluding the power of clock driver and D/AC, the total power dissipation of the modulator becomes only the summation of the integrator and quantizer. In the following discussion, the modulator order, OSR, and quantization bit will be explored based on the assumption above.

Oversampling is the first technique deployed to increase the SNR in the A/DC design. Without additional circuits, simply increase the sampling frequency boosts the resolution of the A/DC as shown the Equation 3.5

$$SNR_{oversampling} = 10\log(OSR) + 6.02B + 1.76$$

(3.5)

For a 1-bit quantizer system to increase 1-bit of resolution, the OSR must be quadrupled. As a result, the power dissipation increases 4 times as well (Equation 3.1). The SNR/bit in Equation 3.6 can be used as a rough gauge for the power dissipation (proportional). The more precise estimation will be developed later. Note that this practice is power inefficient if the target pass-band is wide. Moreover, no fabricated circuit operates beyond  $f_{max}$ , which is the upper limit of the process.

$$SNR_{oversampling} / bit = 10\log(OSR) / 6 \cong 1.6\log(OSR)$$

(3.6)

The second technique is noise shaping. Equation 3.7 shows the SNR of a modulator loop based on the OSR modulator order, and a B-bit quantizer.

$$SNR_{\Delta-\Sigma} = (200+10)\log OSR + 10\log(20+1) + 6.02B + 1.76 - 9.94O$$

(3.7)

For the modulator architecture with a 1-bit quantizer, the SNR increases 1.5-bit for every doubling the frequency; 2.5-bit for the  $2^{nd}$  order and 3.5-bit for the  $3^{rd}$  order etc. The *SNR/bit* of the modulator is

$$SNR_{\Delta-\Sigma} / bit \cong (3.3O + 1.6) \log OSR + 1.6 \log(2O + 1) - 1.6O$$

(3.8)

Note that as the order increases, not just the SNR and power dissipation increase but the degree of difficulty in maintaining loop stability [3].

Increasing the quantization bits is the most power efficient technique to boost the SNR since its power dissipation is governed by (3.1) and small. The capacitors used in the comparators are equivalent to 10 of unit inverter. As a result the power ratio of the

integrator to comparator is, therefore,  $\propto 10^3$ . For every quantization bit increase, the resolution increases one bit, and its SNR/bit is

$$SNR_{quantizer} / bit \cong 2^B - 1 \tag{3.9}$$

However, a multi-bit quantizer system requires a multi-bit D/AC to convert the digital output back to the analog signal to form the feedback loop. The drawback of multi-bit D/ACs is their inherent non-linearity. Additional techniques and circuits are required to linearize the conversion process [11]. More importantly, the noise (or error) generated from the D/A process reduces the SNR and as such, requires additional attention to the design.

The summarized proportional power dissipation using the three methods to increase the SNR is listed in Table 3.1.

|                        | SNR/bit                                           |

|------------------------|---------------------------------------------------|

| Oversampling frequency | 1.6log( <i>OSR</i> )                              |

| Loop order             | $(3.3O + 1.6) \log OSR + 1.6 \log(2O + 1) - 1.6O$ |

| Quantization bit       | $2^{B}-1$                                         |

Table 3.1 Power dissipation cost of improving resolution.

The most appealing technique to increase the SNR is to boost the order of the loop, but the power dissipation increase may be the largest. In the modulator design, the order is equal to the number of integrators and the core of an integrator is an OTA. The power consumption of an OTA is dictated by its gain and bandwidth requirement and can be written as

$$P_{ana\log} = mI_{BIAS} (V_{DD} - V_{SS}) \tag{3.10}$$

where  $m = 7 \sim 8$  for a fully differential OTA. Thus, operating the OTA at high frequency is not the best selection to boost the SNR if there are alternative digital circuits that can lower operating frequency of the analog circuits and achieve the same goal. The multi-bit quantizer and D/AC approach is such a circuit and its bottleneck (D/AC non-linearity) can be solved through the use of an innovated serial D/AC, which will be explained in detail in Section 3.3.4.

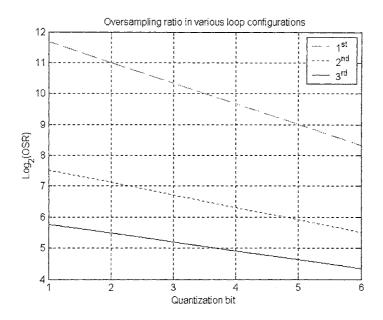

To further illustrate this low power design concept, the example of 18-bit resolution is set for various modulator approaches. Note that the modulators beyond 4<sup>th</sup> order are not included due to the circuit complexity and stability issues. Figure 3.5 shows that the 1<sup>st</sup> order system requires very high oversampling ratio; approximately 32 and 64 times higher than the 2<sup>nd</sup> and 3<sup>rd</sup> order systems, respectively. Since the power is proportional to the operating frequency, the 1<sup>st</sup> order system is not a good candidate for high resolution requirement design.

Figure 3.5 Oversampling ratio in various loop configurations.

An increasing the number of the quantization bits is more power efficient than an increasing the order. However, the number of required comparators for the quantizer grows exponentially, which means there is a minimum where the modulator order and the number of quantization bit are in balance. To a 1<sup>st</sup> order system, power dissipation is the summation of an integrator and quantizer powers. Note that the D/AC is a digital serial shift register dominated by digital power and as a result is insignificant. For better representation and understanding integrator power, Equation 3.2 is rewritten as

$$P_{\text{int egrator}} = IV = GBP \cdot C_L \frac{\Delta V}{2} V \tag{3.11}$$

where  $C_L$  is the effective load of the integrator and V is power supply voltage. Using integrator settling of 5 time constants (t<sub>s</sub>=5 $\tau$ ), Equation 3.11 is rearranged as follows

$$P_{\text{integrator}} = GBP \cdot C_L \frac{\Delta V}{2} V = 10\pi f_s C_L \Delta V V$$

(3.11a)

Including both digital power of the quantizer and analog power of the integrator, the total power of the modulator is

$$P_{\text{modulator}} \cong P_{\text{integrator}_{1}} + K_{\text{int}} \sum_{i=2}^{O} P_{\text{integrator}_{i}} + P_{quantizer}$$

$$= 10\pi f_{s} C_{L} \Delta VV + K_{\text{int}} \sum_{i=2}^{O} 10\pi f_{s} C_{L} \Delta VV + K C_{Q} V^{2} f 2^{B}$$

(3.12)

where  $K_{int}$  is the power weighting factor for the 2<sup>nd</sup> through n<sup>th</sup> integrators and K is a function of the flash comparator architecture. Normalizing the power of the 1<sup>st</sup> integrator to 1, rearranging the equation, and dividing by the number of bits of resolution give

$$P_{\text{modulator}} / bit \propto \left[ 1 + K_{\text{int}} (O-1) + K_{Q} K 2^{B} \right] / SNR \quad where \quad O = 2, 3, ..., n \quad (3.13)$$

where  $K_Q$  is the power weighting factor of comparators. The 1<sup>st</sup> integrator must be large enough to maintain the thermal noise floor. The 2<sup>nd</sup> and the subsequent integrators were selected at ½ of the power dissipation of the 1<sup>st</sup> integrator ( $K_{int} = 0.5$ ) since the 1<sup>st</sup> integrator dominates the noise floor and requires more power as a result of the capacitors requirement to suppress the thermal noise. As the SNR increases  $K_{int}$  can be reduced further.  $K_Q$  is defined as

$$K_{Q} = K \left( \frac{C_{Q}}{C_{L}} \right) \left( \frac{V}{10\pi\Delta V} \right) \approx 0.02$$

(3.14)

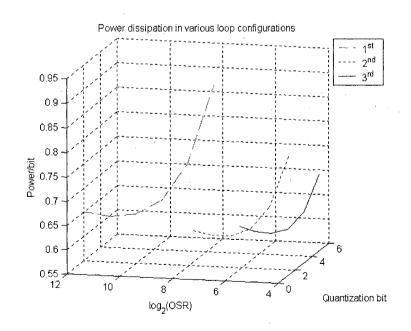

where  $C_Q$  is the value of quantizer capacitor that will be discussed later. Equation 3.13 is plotted in Figure 3.6 and 3.7 below demonstrates that an optimal power/bit architecture exists.

Figure 3.6 Power dissipation in various loop configurations.

Figure 3.7 Combination plot of Figure 3.5 and 3.6.

Assuming an 18-bit objective, Figure 3.7 reveals that  $2^{nd}$  order systems are the most power efficient until quantizer bit is increased beyond 4. At witch points, the  $3^{rd}$  order systems are a better candidate. In conclusion, the  $2^{nd}$  order  $\Delta - \Sigma$  modulator with a 4-bit quantizer, running at 64 times of OSR was chosen to achieve 18-bit of resolution (Equation 3.15).

$$SNR_{A-\Sigma} = (20O + 10) \log OSR + 10 \log (2O + 1) + 6.02B + 1.76 - 9.94O = 118.3dB$$

(3.15)

## 3.3 Modulator stability

As described in the previous section, the 2<sup>nd</sup> order system is a very stable modulator but not in all condition. The loop can be guaranteed stable if the loop

coefficients are chosen correctly. In addition, coefficient setups must compensate for disturbances generated from process variation. Analysis of the modulator loop is performed in the Z-domain using Figure 3.8. From the transfer function of the modulator, the loop coefficients can be determined.

Figure 3.8 Z-domain of the  $2^{nd}$  order  $\Delta - \Sigma$  modulator.

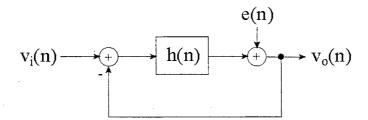

In the analysis, a stable modulator for the desired base-band SNR is the primary consideration used to set the coefficients for the overall system design. To understand the system behavior, a linear approximation model of the modulator is shown in Figure 3.9.

Figure 3.9 Block diagram of a  $\Delta$ - $\Sigma$  loop.

The output of the linear system,  $v_o(n)$ , can be described as a combined responses of both input  $v_i(n)$  and quantization noise e(n).

$$V_o(z) = \frac{H(z)}{1 + H(z)} V_i(z) + \frac{1}{1 + H(z)} E(z)$$

(3.16)

where the first term on the right side of the Equation 3.16 is the STF and the second term is the NTF. By solving the loop equations of Figure 3.8, simlar expression can be found with detail parameters (Equation 3.17).

$$V_{O}(z) = \frac{\alpha_{1}\alpha_{2}z}{(\beta_{2}+1)z^{2} + (\alpha_{2}\beta_{1} - \beta_{2} - 2)z + 1}V_{i}(z) + \frac{z^{2} - 2z + 1}{(\beta_{2}+1)z^{2} + (\alpha_{2}\beta_{1} - \beta_{2} - 2)z + 1}E(z)$$

(3.17)

$$H(z) = \frac{\beta_2 z^2 + (\alpha_2 \beta_1 - \beta_2) z}{z^2 - 2z + 1}$$

(3.18)

Equation 3.17 shows that the STF is simply a low pass function and NTF is a high pass function. Note that both transfer functions share the same poles (same denominator) and only one of them can dominate. Since the STF is simply a delay of signals, the design will focus on the NTF. The noise shaping of the modulator is determined by the NTF order, placement of the poles, and distributed zeros in the signal pass-band. With the correct approach, the quantization noise can be minimized dramatically.

For the NTF design, all zeros of the function are placed at Z = 1, (i.e. DC) so that the converter can be used for various OSR [4]. In other words, the final design will not be restricted to a particular sampling frequency. In order to simplify the design and increase the successful rate, a Butterworth high pass filter with maximum flatness of pass- and stop-band was chosen to place the system poles in achieving the A/DC specifications while maintaining the stability of the modulator loop. Moreover, the poles of the Butterworth filter are relatively low Q, and thus, the filter alignment tends to be less susceptible to oscillations caused by input signals that are at the same frequency as the poles [12].

There is an inverse relationship between the gain of the NTF and the loop stability; the higher the NTF gain, the more unstable the loop is. However, the gain of the NTF is proportional to the loop's SNR; the higher the gain, the better the loop's SNR. Reference [13] discusses these relationships in detail. For a 1-bit quantizer system, a peak frequency response gain of less than 2 for the NTF is necessary to ensure stability, (i.e.  $|NTF(e^{j\omega T})|_{max} < 2$ ). In practice,  $|NTF(e^{j\omega T})|_{max} \le 1.5$  is usually set to provide a reasonable input range (about 80% of the range of the quantizer). Simulation [13] shows that the NTF gain is proportional to the number of bits in the quantizer. For a system with a 4-bit quantizer,  $|NTF(e^{j\omega T})|_{max} \le 5$  can be set.

The technique used in [13] to increase the NTF gain and boost the SNR is to push the corner frequency away from the base-band,  $f_c >> f_0$ . The noise in the base-band falls well within 12*dB*/octave slope of a 2<sup>nd</sup> order filter transfer function. Taking into account both the increased gain and corner frequency of NTF implies that quantization noise in the base-band is suppressed by an additional 24*dB* for a converter with a 4-bit quantizer compared to a single bit quantizer. Therefore, the total reduction of the quantization noise in the base-band (from 1- to 4-bit) is approximately

36

$$(4-1)bit * 6dB / bit + 25dB = 43dB \tag{3.19}$$

After matching the NTF to the proper filter architecture and the numerical values of both NTF(z) and H(z) functions found, the coefficients can be solved. In practice, dynamic scaling of the coefficients dominates the techniques discussed previously. The scaling ensures that the power levels of all nodes are equal; no large noise gains from nodes with small signal levels results in unstable operation. Dynamic scaling is achieved by proportional scaling the loop coefficients (or gains of each integrator) to avoid signal clipping, as well as power optimization by simulating the system [4]. Coefficients are determined by simulation and through iterative runs for different coefficients. The final coefficients are selected as

$$\alpha_1 = \beta_1 = \frac{1}{2} \quad and \quad \alpha_2 = \beta_2 = 2$$

(3.20)

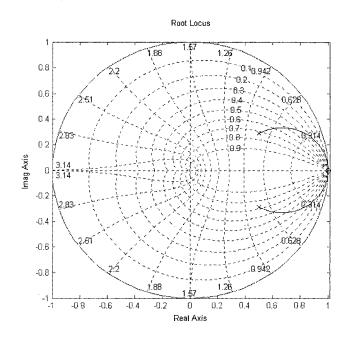

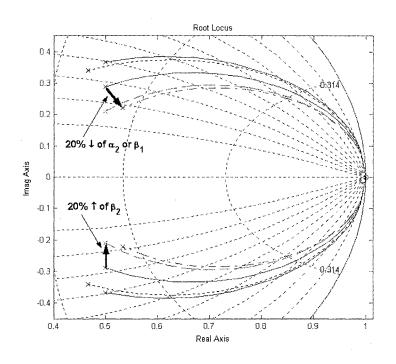

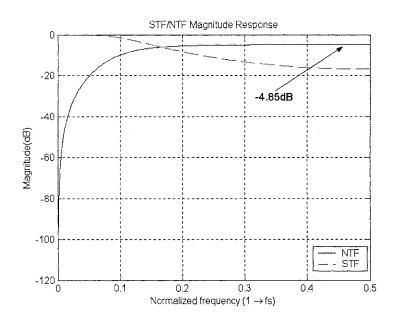

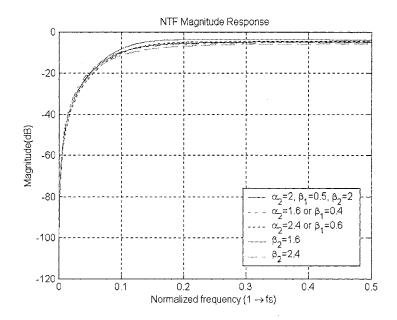

By using the MatLab<sup>®</sup> toolbox developed by Richard Schreier of Analog Device Inc. [14], the 2<sup>nd</sup> order  $\Delta - \Sigma$  modulator with a 4-bit quantizer is simulated at OSR = 64. Figure 3.10 shows both poles are inside the unit circle and proven stable. In Figure 3.11, coefficients are varied within 20% to prove the system's tolerance to the process variation. The NTF magnitude,  $|NTF(e^{j\omega T})|_{max} \leq 0.57$ , fortifies the loop stability (Figure 3.12). Figure 3.13a shows that the results show no sign of instability within the variation. However, the noise floor rises ( $\cong 2dB$ ) when  $\alpha_2$  or  $\beta_1$  is reduced by 20% (Figure 3.13b). On the STF side, Figure 3.14 shows that either  $\alpha_1$  increase or decrease will attenuate the signal about 2*dB*, and  $\alpha_2$  can be used to adjust the width of the base-band; BW increases as  $\alpha_2$  increase. For  $\beta$  variation (Figure 3.15), only  $\beta_1$  decrease will boost the signal about 2*dB*.  $\beta_1$  and  $\beta_2$  increase and  $\beta_2$  decrease will attenuate the signal by 1.8*dB*. The FFT output reconfirms the design through time domain simulation (Figure 3.16 and 3.16a).

Figure 3.10 Root locus of the modulator NTF.

Figure 3.11 Root locus of the modulator NTF at various conditions.

Figure 3.12 Frequency responses of the modulator STF and NTF.

Figure 3.13 Frequency responses of the modulator NTF at various parameter variations.

Figure 3.13a A section zoom-in of the Figure 3.13.

Figure 3.13b A section zoom-in of the Figure 3.13.

Figure 3.14 Frequency responses of the modulator STF at multiple  $\alpha$  parameter variations.

Figure 3.15 Frequency responses of the modulator STF at multiple  $\beta$  parameter variations.

Figure 3.16 Output spectrum of the modulator.

Figure 3.16a A section zoom-in of the Figure 3.16.

Table 3.2 shows the summary of the effects. Note that 'X' means unchanged.

|          |        | $\alpha_1$   | β1             | α2               | β2             |

|----------|--------|--------------|----------------|------------------|----------------|

| Increase | Signal | -2 <i>dB</i> | -1.8 <i>dB</i> | Base-band widen  | -1.8 <i>dB</i> |

|          | Noise  | Х            | -1.8 <i>dB</i> | -1.8 <i>dB</i>   | Х              |

| Decrease | Signal | -2 <i>dB</i> | 2dB            | Base-band shrink | -1.8 <i>dB</i> |

|          | Noise  | Х            | 2dB            | 2dB              | Х              |

Table 3.2 The effects of the loop coefficients.

# 3.4 Crucial building blocks of a $\Delta\text{-}\Sigma$ modulator

The integrator, quantizer, and D/AC are the three crucial building blocks of the modulator. The sophistication level of these block designs dominates the success of the modulator. As a result, all the design techniques and considerations of these circuits are

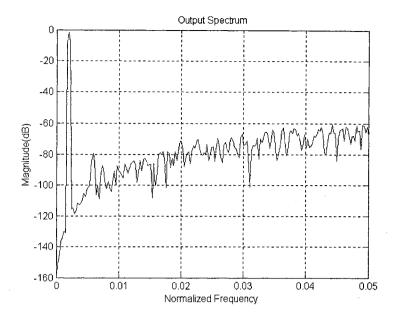

described in detail in this section. Figure 3.17 shows the switched-capacitor implementation of the  $2^{nd}$  order single loop  $\Delta - \Sigma$  modulator.

Figure 3.17 Switched-capacitor implementation of a  $2^{nd}$  order  $\Delta - \Sigma$  modulator.

This modulator feeds a 4-bit quantizer output back to the inputs of the two integrators through an innovated serial D/AC. The same OTA is used for both integrators except the first OTA's size is twice of the second one since the second stage does not have the same stringent requirement on noise, slew rate, and high gain requirement as the first stage.

The fully digital control, serial feedback D/AC is a novel addition to the  $\Delta$ - $\Sigma$  modulator. Moreover, the serial D/AC inherits no non-linearity issue since it is a 1-bit D/AC. The shift register output is converted to a serial word used as the control signal to steer the reference currents back to both integrators in order to achieve negative feedback. The benefit for this approach is that the OSR of the modulator can be reduced compared to that of a 1-bit quantizer approach with the same SNR. Therefore, the power dissipation is lower. In addition, this robust serial D/AC approach is taking the advantage of under

44

utilized digital BW, which exists between the integrator ( $f_{analog}$ ) and the digital circuit ( $f_{digital}$ ). A very important observation is that the  $f_s$  is limited by  $f_{analog}$  and the ratio of  $f_{digital}$  over  $f_{analog}$  is related by their overdrive voltages ( $V_{OV-D}/V_{OV-A}$ ) and the square of their channel lengths ( $L_A/L_D$ ). For example, if the channel length ratio of analog over digital is 4 to 6 [4] as in the Peregrine SOS process, the existence of at least 16X more digital BW than analog BW is guaranteed. It is this resource that is exploited to operate the serial D/AC running at  $2^{B*}f_s$ .

For better understanding of the concept, Equation 3.22 and 3.23 shows the approximation of analog and digital operating frequencies using overdrive voltage, channel length, and loading capacitance.

$$GBP = \frac{g_m}{C_L} = \frac{g_m}{nC_{GS}} \propto \left(\frac{V_{OV}}{L^2}\right)$$

(3.21)

$$f_{ana\log} = \frac{gm}{2\pi C_{LA}} \approx \frac{V_{OV-A}}{2\pi C_{LA}L_A^2}$$

(3.22)

$$f_{digital} = \frac{1}{2.2RC_{LD}} \approx \frac{V_{OV-D}}{2.2C_{LD}L_{D}^{2}}$$

(3.23)

$$\frac{f_{digital}}{f_{ana \log}} = \left(\frac{C_{LA}}{C_{LD}}\right) \left(\frac{L_A}{L_D}\right)^2 \left(\frac{2.2}{2\pi}\right) \left(\frac{V_{OV-D}}{V_{OV-A}}\right)$$

(3.24)

Equation 3.24 demonstrates that the ration of the operating frequencies is proportional to the overdrive voltage and inverse proportional to the square of channel length. Assuming the worst case loading of 5 for analog and 6 for digital,  $L_A = 2um$  and  $L_D = 0.5um$ , and  $V_{OV-A} = 0.3V$  and  $V_{OV-D} = 3.6V$ . The result of Equation 3.24a shows that digital circuits can operate 56 times faster than analog counterparts. The excessive BW allows the modulator designed with a quantizer less than 6-bit (Equation 3.25).

$$\frac{f_{\text{digital}}}{f_{\text{ana log}}} = \left(\frac{5}{6}\right) \left(\frac{2}{.5}\right)^2 \left(\frac{2.2}{2\pi}\right) \left(\frac{3.6}{.3}\right) \approx 56$$

(3.24a)

$$B = \log_2 \left(\frac{f_{digital}}{f_{ana\log}}\right) = 5.8 \approx 5$$

(3.25)

Since the power of this D/AC is digital in origin, the added power cost is minimal. By increasing the number of quantization bits, the modulator can be operated at a lower frequency. In another word, the number of quantization bits for a given process can be extended by exploiting this unused digital BW. Thus, implementing a serial D/AC to a multi-bit modulator is an excellent choice for improving the SNR of the A/DC with low power budget.

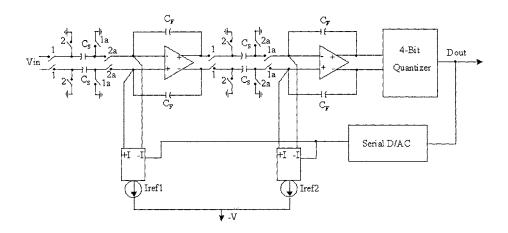

3.4.1 Integrator and OTA

Shown in Figure 3.18, the modulator is implemented by using two types of integrators: Forward and backward Euler. The first integrator  $(\frac{z^{-1}}{1-z^{-1}})$  is a backward Euler and it over estimates the function. The second integrator  $(\frac{1}{1-z^{-1}})$  is a forward Euler and it under estimates the function. By combining both integrations, the output of the second integrator should be virtually the same as the Trapezoid  $(\frac{1+z^{-1}}{1-z^{-1}})$  (area under the dash line in Figure 3.18).

Figure 3.18 Forward and backward Euler and Trapezoid integrations.

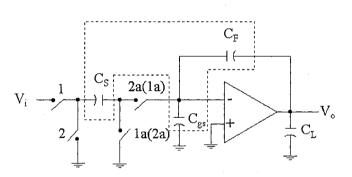

The core of the integrator is an OTA. Thus, both of them are discussed concurrently in this section. Figure 3.19 shows a generic fully differential switchedcapacitor integrator. The benefits of the circuit are high PSRR, reduced clock feedthrough and switch charge injection errors, improved linearity, and increased dynamic range [15]. Note that the clock signals outside the parentheses are for non-inverting integrators and inside are for inverting version (delay-free).

Figure 3.19 Switched-capacitor implementation of a fully differential integrator.

Non-fully differential version of integrator is shown in Figure 3.20. It is a half of the fully differential version and easier for circuit analysis.

Figure 3.20 Switched-capacitor implementation of an integrator.

The major functions of the integrator are to integrate (sum) charges and to maintain the noise level. The operation of the former is simple and described in Reference [3] and the latter requires special attention. In Figure 3.20, the dominant noise sources are the thermal noise generated from the MOS switching resistance. Capacitors do not generate any noise but accumulate noise generated by other noise sources [4]. Thus,  $C_S$  must be designed sufficiently large to set the noise 9*dB* lower than the modulator noise floor [15]. Equation 3.26 shows the integrator RMS noise voltage. Note that 8 switches (P and NMOS in parallel represent one switch in Figure 3.20) involve in the sample-and-hold processes and with the NMOS assumed to be the dominant noise sources. Finally, their resistor values can be ignored in the noise calculation [4]

$$V_{n(rms)-\text{integrator}} = \sqrt{\frac{4kT}{C}}$$

(3.26)

Since the oversampling technique is used in the modulator design, the sampling capacitor can be scaled down and Equation 3.27 is modified as follows

$$V_{n(rms)-\text{int egrator}} = \sqrt{\frac{4kT}{OSR \cdot C}}$$

(3.27)

The SNR of the integrator is

$$SNR_{NF} = 10\log\left(\frac{\left(V_{FS}/2\sqrt{2}\right)^{2}}{\left(V_{n(rms)-\text{integrator}}\right)^{2}}\right) = 10\log\left(\frac{V_{FS}^{2} \cdot OSR \cdot C}{32kT}\right) \le SNR_{\Delta-\Sigma} - 9dB \quad (3.28)$$

The first integrator dominates the overall system noise floor and any noise injected at the 1<sup>st</sup> integrator will be seen as signal for the following stages. In such a case, the first

sampling capacitor must be designed large enough to minimize the noise level (Equation 3.29).