# SUPERQUADRIC DESCRIPTION ON LARGE ARRAYS OF BIT-SERIAL PROCESSORS

# Ву

# RONALD ELLISON DANIEL JR.

Bachelor of Science in Electrical Engineering

Oklahoma State University

Stillwater, Oklahoma

1985

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of MASTER OF SCIENCE July, 1987

Thesis Approved:

Thesis Advisor

Crah and L. Cummins

C.M. Barn

Dean of the Graduate College

#### **PREFACE**

This study describes the parallel implementation of a new computer vision technique, superquadric description. The use of superquadric primitives to extend the power of Constructive Solid Geometry for Computer Aided Design purposes was first proposed in [BARR 84]. The application of this technique for machine vision purposes was first published by Alex Pentland in [PENTL 86b].

This study developed a parallel least-squares solution technique to solve a slightly modified form of the regression equations originally derived in [PENTL 86b]. This technique is intended for execution on large arrays of bit-serial processors. Several ways have been suggested to interconnect the processing elements in such arrays, therefore the performance of this technique was estimated for three interconnection networks.

An effort such as this study is not possible without help. I would like to thank Dr. Alex P. Pentland, Dr. Steven L. Tanimoto, Dr. Steven P. Levitan, and Dr. Charles C. Weems for their courteous responses to my requests for information. I would also like to thank Dr. Dave Ballew, of OSU and AT&T Technologies, and Dr. Ron Rhoten, of OSU, for their help with particular portions of this study.

The members of my advisory committee, Dr. Charles M. Bacon, Dr. Richard L. Cummins, and Dr. Keith A. Teague deserve special mention for their guidance, enthusiasm, and friendship during this project as well as during previous semesters. The School of Electrical and Computer Enginering also has my deep appreciation for the constant employment which made this study possible.

I would also like to thank my parents for their love and support through all of the trying times children inflicted upon them. Honorable mention in this area goes to my brother and sisters. Most especially, I want to thank my fiance Laura for her patience with me throughout this period of insanity.

# TABLE OF CONTENTS

| Chapter |                                                                                                                                                                                                                                                                                               | Page                                         |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| I.      | INTRODUCTION                                                                                                                                                                                                                                                                                  | 1                                            |

|         | Purpose and Motivation                                                                                                                                                                                                                                                                        | 1<br>4<br>6                                  |

| II.     | REVIEW OF LITERATURE                                                                                                                                                                                                                                                                          | 8                                            |

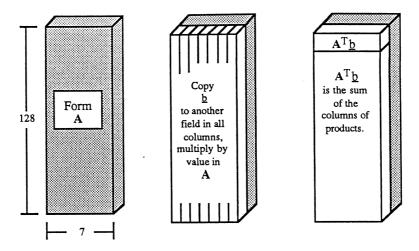

|         | Computer Vision Superquadrics Comments on the Estimation of Surface Normals Description of the Processing Element Parallel Image Processing Architectures Interconnection Networks Studied VLSI Fabrication Considerations                                                                    | 8<br>11<br>12<br>15<br>22<br>24<br>31        |

| III.    | PROCEDURE                                                                                                                                                                                                                                                                                     | 40                                           |

|         | Derivation of the Regression Equations Parallel Regression Algorithms  Main Procedure  Calculation of the Regression Coefficients.  Forming the A Matrix and b Vector  Calculating A <sup>T</sup> A and A <sup>T</sup> b  Inverting A <sup>T</sup> A  Calculating x  Distributing the Results | 40<br>46<br>47<br>52<br>53<br>62<br>63<br>64 |

| IV.     | RESULTS                                                                                                                                                                                                                                                                                       | 67                                           |

|         | Execution Timings                                                                                                                                                                                                                                                                             | 67<br>80                                     |

| V.      | CONCLUSIONS                                                                                                                                                                                                                                                                                   | 81                                           |

|         | Summary                                                                                                                                                                                                                                                                                       | 81<br>81<br>84                               |

| BIBLIO  | GRAPHY                                                                                                                                                                                                                                                                                        | 87                                           |

| APPENDIXES                                      | 9(  |

|-------------------------------------------------|-----|

| APPENDIX A - FUNDAMENTAL OPERATIONS             | 90  |

| APPENDIX B - SUPEROUADRIC ESTIMATION ALGORITHMS | 105 |

# LIST OF TABLES

| Table |                                                                                                                                         | Page  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------|-------|

| I.    | Accuracy of Lee's Estimator for Sphere                                                                                                  | . 14  |

| II.   | Accuracy of Lee's Estimator for Ellipsoid                                                                                               | . 14  |

| III.  | Non-Leaf Chip Parameters as a Function of the Number of Levels per Package                                                              | 36    |

| IV.   | Leaf Chip Parameters as a Function of the Number of Levels per Package and the Number of PEs on the Top Level                           | . 37  |

| V.    | System Level Comparison                                                                                                                 | . 39  |

| VI.   | Number of Data Transfers Needed to Distribute the Estimation Region Among the Sub-Submeshes on the Flat Machines                        | . 109 |

| VII.  | Number of Data Transfers Needed to Distribute the Estimation Region Among the Sub-Submeshes on the Pyramid Machine                      | . 109 |

| VIII. | Number of Data Transfers Needed to Reorganize the Parameters Prior to Their Being Moved To The Originating Estimation Region            | . 118 |

| IX.   | Number of Data Transfers Needed to Move the Reorganized Block of Parameters to the Originating Estimation Region on the Flat Machines   | . 120 |

| Χ.    | Number of Data Transfers Needed to Move the Reorganized Block of Parameters to the Originating Estimation Region on the Pyramid Machine | . 121 |

| XI.   | Number of Data Transfers Needed to Move the Parameters to All PEs in the Originating Estimation Region                                  | 123   |

# LIST OF FIGURES

| Figure |                                                                                   | Page |

|--------|-----------------------------------------------------------------------------------|------|

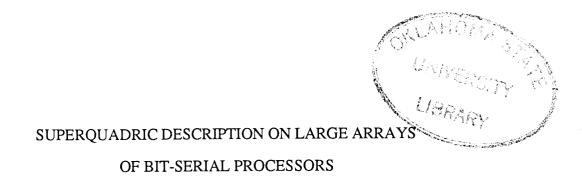

| 1.     | Unit and Deformed Superquadrics                                                   | 2    |

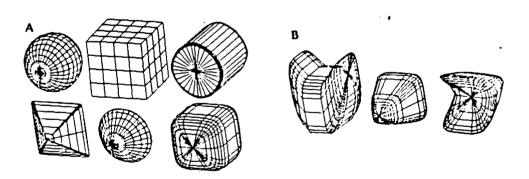

| 2.     | Projection of Normal Vector onto Image Coordinates                                | 13   |

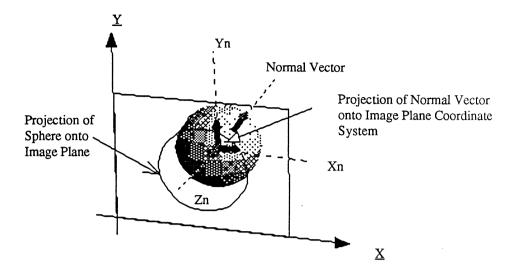

| 3.     | Functional Block Diagram of a Single PE                                           | 16   |

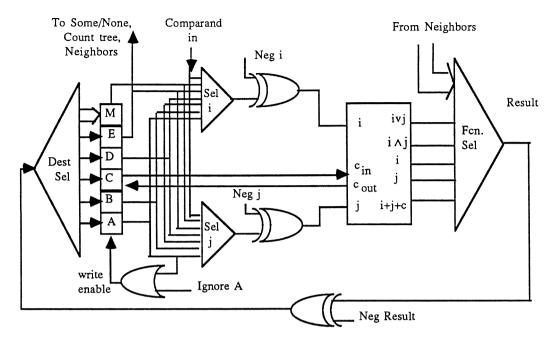

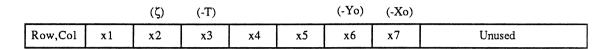

| 4.     | Microinstruction Format                                                           | 21   |

| 5.     | Four Nearest Neighbor Interconnection Network                                     | 25   |

| 6.     | Sample Edge Treatments                                                            | 25   |

| 7.     | Data Movements for Convolution                                                    | 27   |

| 8.     | Interconnection Network for One Chip of the CAAPP                                 | 28   |

| 9.     | The Pyramid Interconnection Network                                               | 30   |

| 10.    | Inter-Chip Communication for 8NN Meshes                                           | 35   |

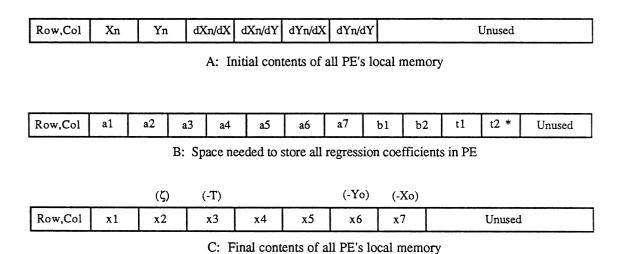

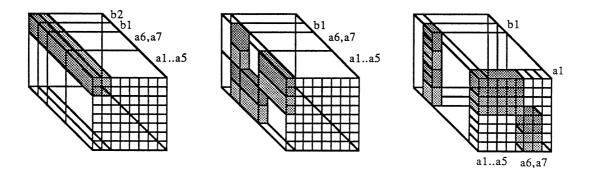

| 11.    | PE Memory Contents on the CAAPP and 4NN Machines                                  | 49   |

| 12.    | PE Memory Contents on the Pyramid Machine                                         | 53   |

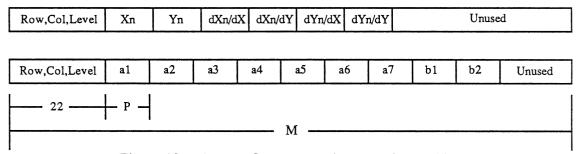

| 13.    | Form of the Sparse A and $\mathbf{A}^T\mathbf{A}$ Matrices                        | 56   |

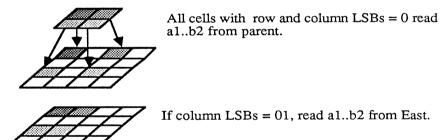

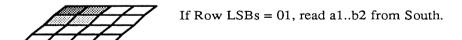

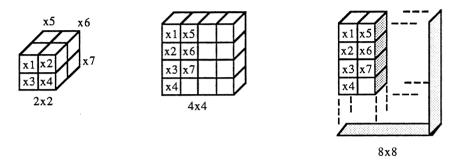

| 14.    | Submesh organization                                                              | 58   |

| 15.    | Partitioning the Estimation Region on the Flat Interconnection Networks           | 60   |

| 16.    | Partitioning the Estimation Region on the Pyramid Interconnection Network         | 60   |

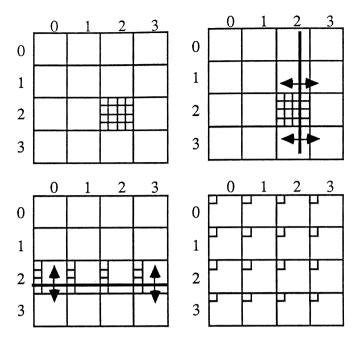

| 17.    | Filling the sub-submeshes                                                         | 61   |

| 18.    | Organization of Coefficents for Distribution to the Originating Estimation Region | 65   |

| 19.    | Final Contents of Local Memories                                                  | 66   |

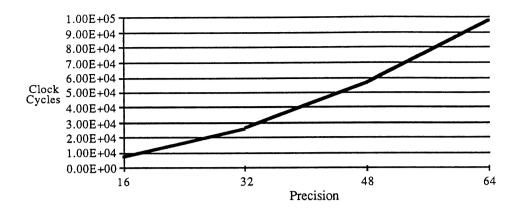

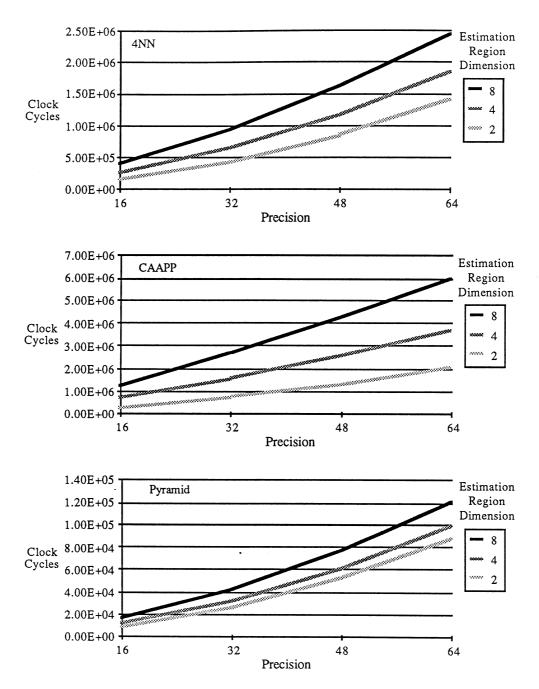

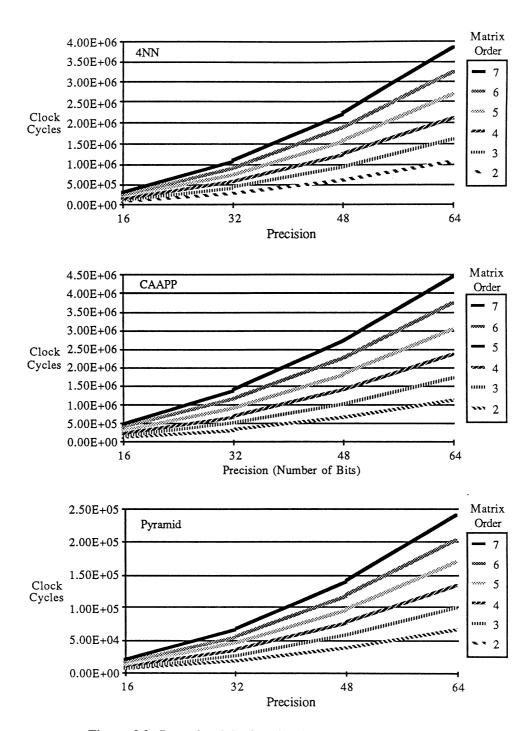

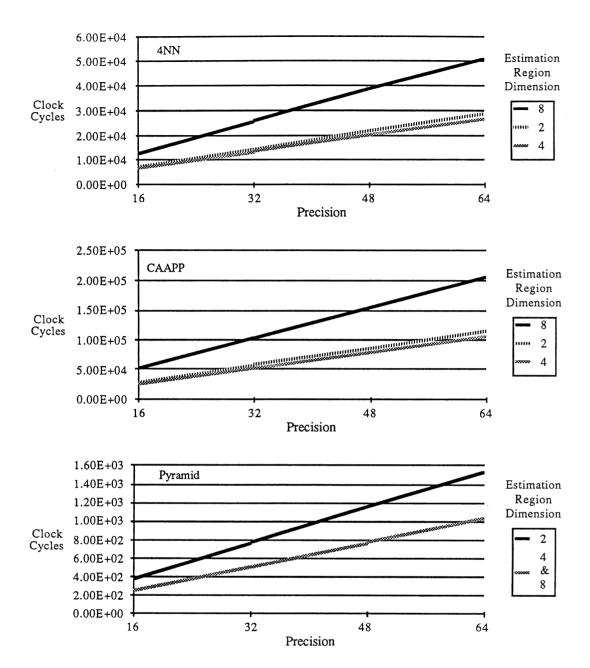

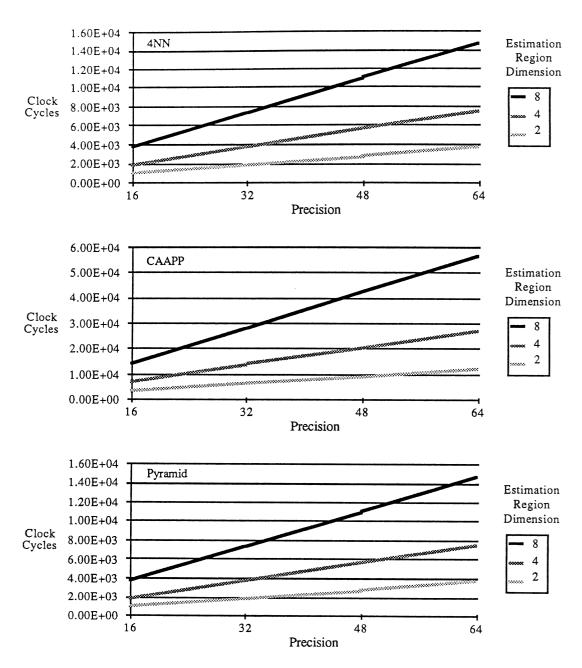

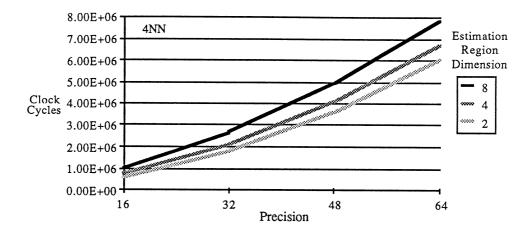

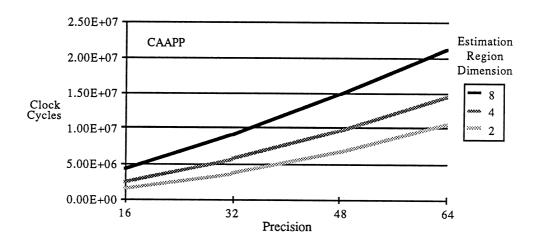

| 20. | Calculation of Regression Coefficients              |

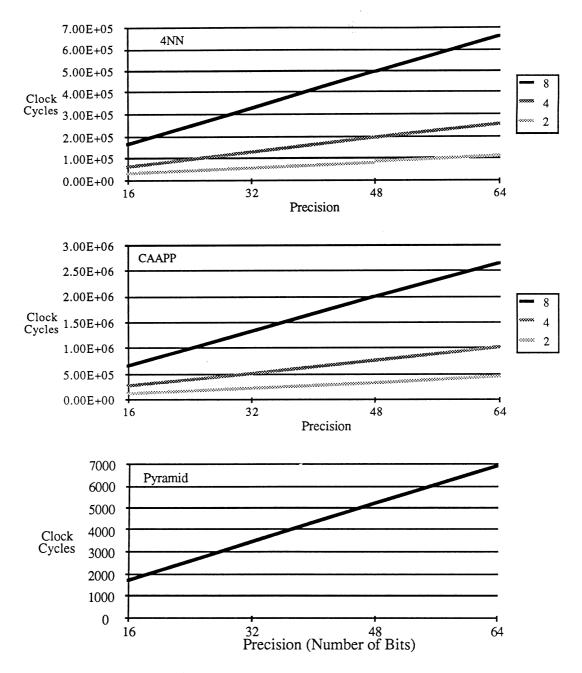

|-----|-----------------------------------------------------|

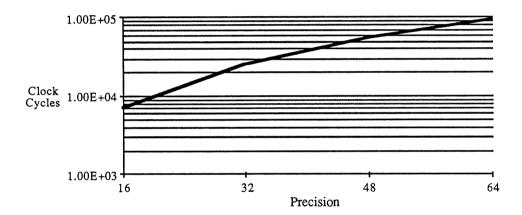

| 21. | Calculation of Regression Coefficients (Log Scale)  |

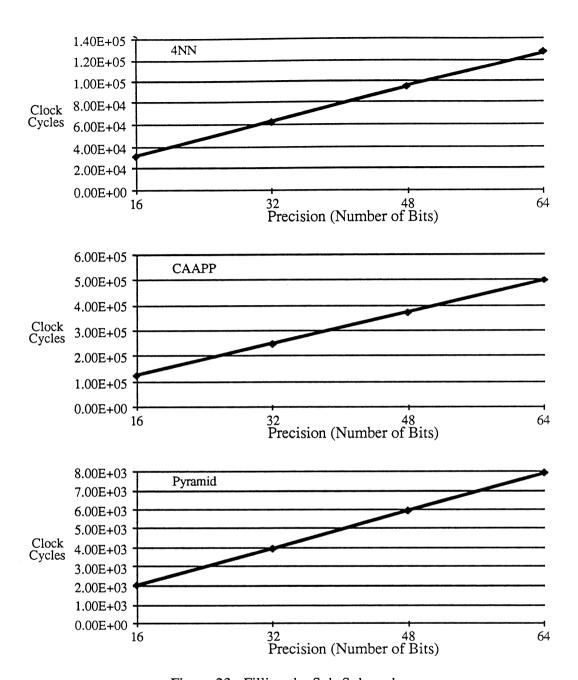

| 22. | Distribute Estimation Region among Sub-Submeshes 69 |

| 23. | Filling the Sub-Submeshes                           |

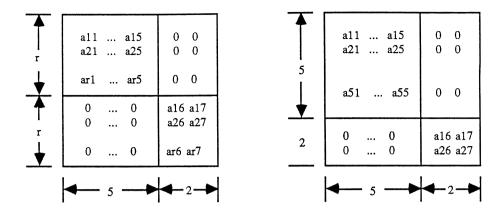

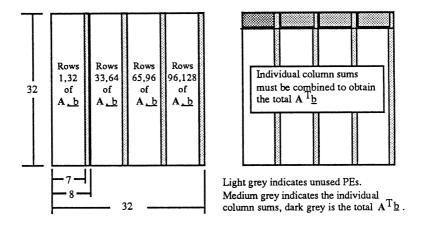

| 24. | Calculating $A^T\underline{b}$                      |

| 25. | Calculating $A^TA$                                  |

| 26. | Inverting Matrices by the Faddeeva Technique        |

| 27. | Calculating the Vector of Superquadric Parameters   |

| 28. | Reorganizing Parameters                             |

| 29. | Moving Parameters to Originating Estimation Region  |

| 30. | Filling Estimation Region with Parameters           |

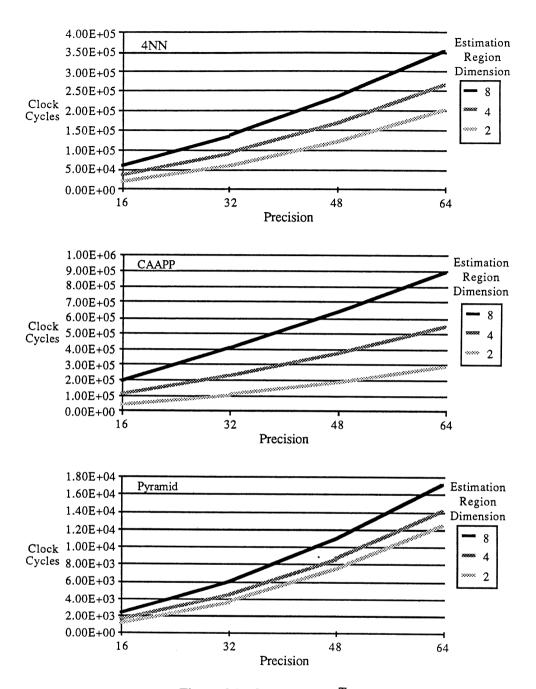

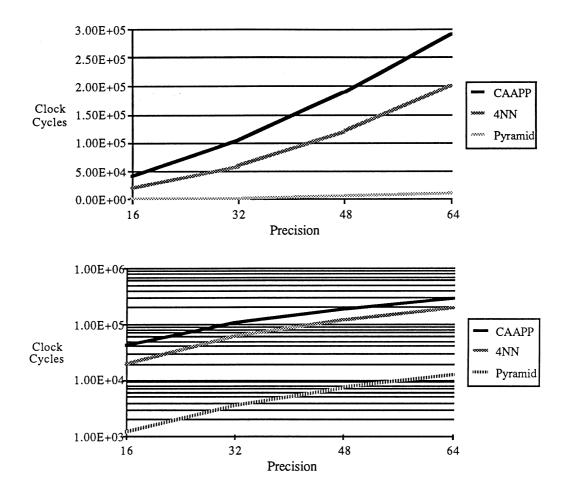

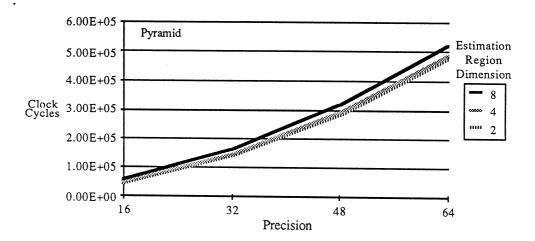

| 31. | Total Execution Time                                |

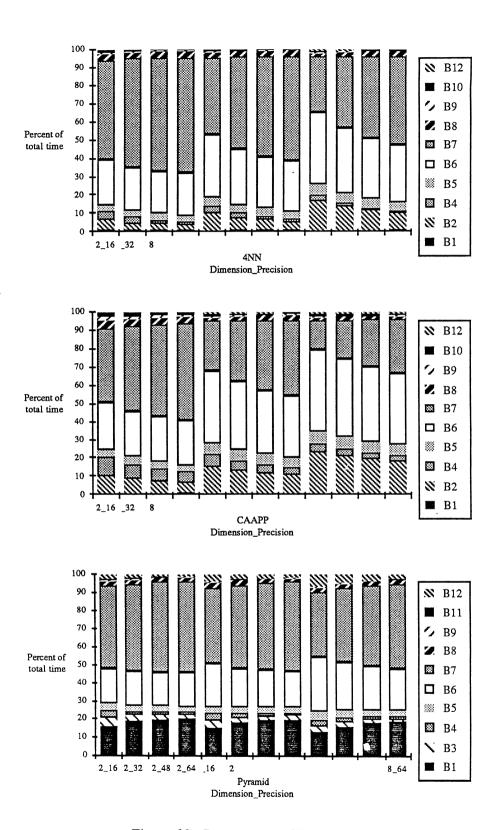

| 32. | Percentages of Total Time                           |

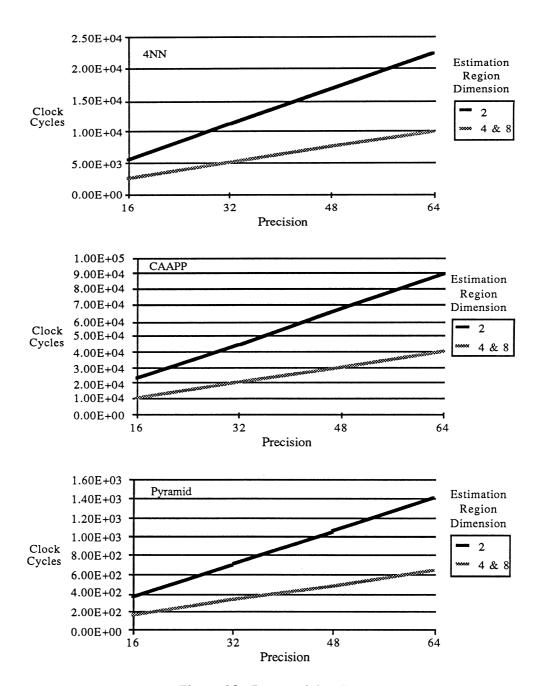

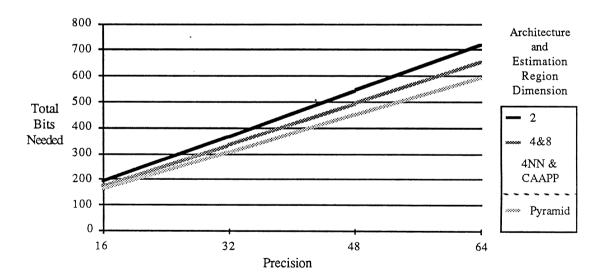

| 33. | Memory Requirements                                 |

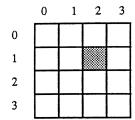

| 34. | Estimation Region Used for Average Performance      |

#### CHAPTER I

#### INTRODUCTION

#### Purpose and Motivation

This study has two purposes. The first is to investigate the parallel implementation of a new computer vision technique, superquadric description [PENTL 86b]. This technique is described more fully in Chapter Two, but the basic idea is to model imaged objects in terms of Boolean combinations of easily recognized solid primitives. This CSG (Constructive Solid Geometry) approach to object modeling is a standard CAD/CAM (Computer Aided Design / Computer Aided Manufacturing) technique. The use of CSG in machine vision was first investigated by Marr and Nishihara in [MARR 78]. Introductory information about this problem may be found in [BALLA 82]. Superquadrics are a recently suggested enhancement for CSG based systems. They provide a very general three dimensional modeling primitive which includes the sphere, cube, and cylinder as special cases. Figure 1, reproduced from [PENTL 86b], illustrates some of the possible superquadric forms. Almost any physical object can be represented as a CSG form, but the representation may become arbitrarily large. This problem can be reduced if we allow the superquadrics to be deformed as in Figure 1b [PENTL 86b, BARR 84].

Image processing is computationally intensive. Many specialized architectures have been suggested to handle this burden at higher speed than a serial processor is capable of. Since parallel implementations of a particular procedure will be highly dependent upon the architecture they are designed for, the second purpose of this study is to examine how the choice of architecture affects the execution speed of this task. Three specialized image

processing architectures are compared for speed of executing the superquadric recovery algorithm. Some aspects of their physical construction are also examined. Image processing architectures can be divided into several major classes. Some of the metrics used to divide the machines into classes are the granularity of the processing elements, the interconnection network used, and the type of parallelism, i.e. SIMD or MIMD (Single Instruction stream Multiple Data streams or Multiple Instruction streams Multiple Data streams). All of the architectures considered in this study are members of what I will call the highly parallel class. This term will be used to identify machines that have at least one bit-serial processing element (PE) for each pixel in the image. A standard image resolution is 512 pixels by 512 pixels. Machines for this size image would have more than a quarter of a million PEs! The massive parallelism of these designs allows very high performance on a broad range of image processing algorithms. These are very fine-grained SIMD machines. Three interconnection networks are studied.

Figure 1: Unit and Deformed Superquadrics

· This study is motivated by the limitations of current computer vision systems. A typical task for a current industrial vision system is to determine the exact location and orientation of parts whose location is limited to the width of a conveyor belt. Contrast this with the general purpose vision needed by a household robot! Bridging this huge gap is several years away. Both hardware and software are responsible for the limitations in current vision systems. Computer vision algorithms have not been developed that approach the generality of human vision. Even the limited routines that have been developed are computationally intensive, requiring many operations to be performed for each pixel in the image. The sheer amount of data compounds this problem. For example, a common resolution is an image of 512 x 512 pixels. The typical refresh rate is 30 frames per second. If we assume that the processing for each pixel will be the equivalent of 1000 floating point multiplies [REDDY 78], our machine must execute the equivalent of 7.8 billion multiplies per second! There is a great deal of continuity in visual input, the later stages of a vision system could take advantage of this continuity to reduce the workload. However, these later stages will be dependent upon a great deal of preprocessing of the image. This preprocessing stage cannot be skipped and will have the majority of the arithmetic operations.

Computers capable of one billion multiplies per second have only recently become available, at a cost of millions of dollars. In order for affordable hardware to complete a vision task in an acceptable time, the software to perform the task must be made very simple. Typically, the environment and/or the task are restricted in order to simplify the problem. The vision software is then optimized for these restrictions. Unfortunately, the very restrictions which make the problem solvable in an acceptable time make the solution technique inapplicable for tasks with slightly different requirements. The non-portability of vision software is considered a major problem [REDDY 78].

The ultimate in portable software would be a system with the capabilities of human vision. While this goal is still far in the future, progress is being made. As can be expected, the powerful systems being researched impose a tremendous computational burden. A great deal of work has gone into the development of architectures which are capable of shouldering this burden. A wide variety of architectures have been proposed, with different trade-offs between the factors of price, performance, and programming ease. Chapter Two provides a brief review of some of the major architectures proposed. This study compares three similar architectures, the main difference between them being their interconnection networks. In addition to estimating execution times, we will also examine some of the characteristics of their VLSI and system-level fabrication.

The next section of this chapter sketches the outline of the procedure used to accomplish these purposes, while the subsequent section notes the limitations of this study. Chapter Two reviews the literature, while details of the procedure are in Chapter Three. Results are given in Chapter Four, and conclusions are offered in Chapter Five. The algorithms used for the superquadric estimation are presented in Appendix B. These algorithms are composed of call to microcoded subroutines which perform arithmetic and data transfer operations. The algorithms for these fundamental operations are given in Appendix A, along with the format of the pseudocode used to specify all the algorithms.

#### Overview of Procedure

#### Selection of Architectures

As noted above, many parallel architectures have been suggested for use in image processing. Some of these architectures are surveyed in Chapter Two. For reasons described more fully there, three architectures were chosen for comparison. The first architecture is the Content Addressable Array Parallel Processor (CAAPP), designed at the

University of Massachusetts at Amherst [LEVIT 84, LAWTO 84, WEEMS 85]. This machine has recently undergone some major design changes [WEEMS 87]. We will examine the older version, circa 1984. The second is the pyramid machine [TANIM 84, DYER 81]. These two machines were chosen because of the differing approaches they take in trading off speed for VLSI area. The other architecture examined provides an intermediate position in terms of complexity and expected performance. This final machine is the simple Four Nearest Neighbor (4NN) mesh. All of these are massively parallel machines with at least one PE for each pixel. In order to keep the comparisons of the architectures fair, all machines are assumed to have equivalent PEs, the only difference being in the connections with neighboring PEs. The PE used is described in detail in the third section of Chapter Two. The interconnection networks are described in Chapter Two, Section 4, while their implementation is considered in Chapter Two, Section 5.

#### Design of the Superquadric Recovery Software

Once the architectures were selected, the system to recover the superquadric parameters was designed. Pentland, in [PENTL 86b], derives linear regressions to solve for estimates of the superquadric parameters given estimates of the surface normals of the imaged objects as well as their derivatives along the x and y image axes. This study presents a parallel least-squares solution technique, and estimates its execution time. Procedures to obtain the estimates of the surface normals have been described in the literature [LEE 85, PENTL 84, 86a]. A technique to calculate the derivatives without excessive noise amplification is described in [HARAL 81,82].

#### Performance Estimation

Execution speed was estimated by breaking the least-squares procedure into major stages, such as matrix inversions and multiplies. The major stages were then decomposed

into fundamental operations, such as data movements and arithmetic operations. Formulas for the execution time of the major stages of the least-squares procedure were then derived as functions of the execution time for the fundamental operations. The formulas for the execution time of the least-squares solution are given in Appendix B, along with the parallel algorithms. The times for the fundamental operations were also estimated. These formulas and algorithms are given in Appendix A.

#### Limitations

Superquadrics are not a cure-all for computer vision. They cannot explain many important perceptual phenomena, such as character recognition or the fractal branching structures of trees. However, they are a much more general modeling primitive than those currently used by CSG based vision systems. As will be seen in Chapter Two, they do appear to satisfy some of the needs of the higher levels of vision processing.

By allowing deformations such as shearing and twisting (Figure 1b), superquadrics become a much more powerful modeling primitive. The principal limitation of superquadric description is that currently, only undeformed superquadrics can be recovered. To my knowledge, the regression equations to recover deformed superquadrics have not been derived. Another problem is that obtaining a CSG representation of imaged objects using superquadric primitives has not been investigated. Previous work [MARR 78] has been done in obtaining CSG descriptions using cylindrical primitives. The use of superquadrics should be a straightforward extension.

A limitation of this study is that the algorithms were not implemented, so no characterization of the errors of the recovery procedure is available. Another limitation is that only one class of parallel architectures was examined. Within this class, the machines studied span a broad range of the speed vs. area trade-off space, but this work could be

extended to examine other types of parallel architectures. I hope to address all these limitations in future studies.

No claims are made for optimality of the least-squares algorithms used. They are simple, straightforward implementations. Some possible ways to improve the performance of the algorithms are suggested in Chapter Five. While not optimal, neither are these procedures grossly inefficient. The matrix operations are quite conservative in the number of multiply and divide instructions issued. A special version of the least-squares algorithm was used for the Pyramid machine, which resulted in a marked improvement in speed, at the cost of a loss in the resolution of the solution. If the loss of resolution is unacceptable, the Pyramid can implement the same algorithms as the other two machines, with comparable performance.

#### CHAPTER II

#### REVIEW OF LITERATURE

The application of superquadrics to machine vision is quite new, very little has been published at this time. Much more has been published on specialized architectures for image processing. The purpose of this study is not to survey the literature in either area, however, some background material is appropriate in order to gain perspective on the role of superquadrics in machine vision. This chapter is quite brief, hitting only the major highlights. The interested reader is referred to the references for more complete information. The first section of this chapter provides a brief overview of computer vision. This is followed by sections on superquadrics and surface normals estimation. Subsequent sections deal with the hardware side of the study. The PE used by all the machines is described in section three. Section four discusses the interconnection networks examined in this study, while section five deals with some of the considerations of the actual physical implementation of these networks.

#### Computer Vision

Computer vision is a fast growing area of research and development. The end goal of this research is to create a machine vision system embodying the power and generality of human vision. Since much of the power of human vision is intimately tied to our learning, planning, and reasoning abilities, computer vision is considered to be a subset of Artificial Intelligence (AI). The high level reasoning capabilities provided by AI routines must have an input, they do not pull solutions from thin air! What is the form of this input, and how is it obtained from an array of intensity values? This is the fundamental question of

computer vision. The first part of the question is easy to answer in general terms; the input to high level cognitive processes should be a concise description of the scene in a form suited to the cognition mechanism(s). The second part of the question, obtaining the description, is much more difficult to answer. One thing is certain, the recovery of the description is a computationally intensive task. In Chapter One we estimated the processing power needed for real-time computer vision to be on the order of 10 Gigaflops. Given this estimate, the need for a highly specialized machine is clear.

This processing burden is typically described as having three levels: characterized as low, intermediate, and high level. High level vision refers to the AI capabilities mentioned above. It is concerned with the manipulation of abstract units such as 'tree' or 'cloud'. Low level vision is also known as image processing. This stage of vision computation operates on the image, and on image-like data structures. The intermediate level of vision is concerned with providing the interface between the two other stages. Superquadric description is on the border between the low and intermediate levels. The estimation of the parameters is low level, obtaining the CSG grouping is intermediate.

#### High Level Vision

The purpose of this study is not to compare the merits of various AI techniques for high level vision processing. However, before we can draw any conclusions about the suitability of superquadrics for a task we must know what the task is. Our task is to derive a description of the imaged scene in a format convenient for a high level reasoning mechanism. This format will be constrained by the needs of the high level mechanisms. The next few paragraphs attempt to show some of these needs. The format will also be constrained by what is possible to compute from the image. The characteristics of low level image processing algorithms will be examined in a subsequent sub-section.

The first restriction on the format is that it be amenable to processing by a variety of cognitive mechanisms. Learning, planning, belief maintenance, as well as formal and common sense reasoning will all be needed in a sophisticated vision application. Many of the mechanisms that have been developed so far are based on a linguistic analogy [SOWA 84]. The goal is to obtain and manipulate the semantic content of syntactic structures. For the case of vision, the imaged objects and their visual attributes can be viewed as forming the nouns and adjectives of a visual language. The role of verbs and adverbs is filled by relations, both spatial and temporal, between the objects. The structure of the grammar is imposed by the laws of physics. Seen in this light, the desired 'chunks' input to the cognition mechanisms would need to be at the complexity of words and phrases, or simple parsed structures.

While the main idea of this visual language would seem very attractive, we must be careful about carrying this analogy too far. Most linguistic structures cannot compactly describe natural objects, their attributes, and their physical relations. An additional problem with most linguistic structures is that they are not isomorphic to the physical world, that is, they do not unambiguously describe real scenes. It has been shown that many of the reasoning capabilities of humans cannot be explained unless we use an isomorphic representation [FISCH 78]. CAD/CAM data structures are an example of an isomorphic representation. They unambiguously describe a physical object.

Once we have the input data, how do we process it in order to extract it's meaning? The reasoning mechanisms would certainly find it much easier to work with more abstract entities, such as 'human' or 'tree', rather than a raw description of the parts in an image and their spatio-temporal relations. This leads us to the requirement that the format of the description be easy to match with known objects. This is where the need for a concise description comes into play. It would also be nice if the format of the raw description matched the format of the more abstract description. Having the representation be able to

span a range of abstractions would allow the high level mechanisms to operate directly on the unmatched description if it became desirable to do so.

Conceptual structures [SOWA 84], also known as relational structures or semantic nets, are one representation that has been suggested for the high levels of vision processing [BALLA 82, CHARN 86]. This representation offers many advantages for AI and vision. Reasoning can be done at varying levels of abstraction, matching is relatively easy, the structures map easily into linguistic forms, and they offer powerful abilities to model physical objects. CSG data structures are a natural extension of relational structures, so we can have an isomorphic representation. Therefore they meet the requirements set forth by the previous paragraphs. An introduction to the use of relational structures for vision is given in [BALLA 82] and [CHARN 86], where additional references may be found.

We will assume that the inputs to the high level section of the vision system should be at least a partial CSG description of the objects in the scene. The primitive solids used in this CSG model must now be selected. The basic requirement for these solids is that they be computable from the outputs of the image processing stage. An additional constraint is that the number of different primitives used be small and that their expression be compact.

#### Superquadrics

Superquadrics [BARR 81, PENTL 86b] appear to meet both these requirements. Unit superquadrics are a two parameter family of solids which include spheres, cylinders, and cubes as special cases (Figure 1a). The surface position vector  $\underline{X}$  and surface normal vector  $\underline{N}$ , as functions of latitude  $\eta$  and longitude  $\omega$  are given by

$$\underline{X}(\eta,\omega) = \begin{pmatrix} a_1 & C_{\eta}^{e1} & C_{\omega}^{e2} \\ a_2 & C_{\eta}^{e1} & S_{\omega}^{e2} \\ a_3 & S_{\eta}^{e1} \end{pmatrix} \qquad \underline{N}(\eta,\omega) = \begin{pmatrix} 1/a_1 & C_{\eta}^{2-e1} & C_{\omega}^{2-e2} \\ 1/a_2 & C_{\eta}^{2-e1} & S_{\omega}^{2-e2} \\ 1/a_3 & S_{\eta}^{2-e1} \end{pmatrix}$$

(1,2)

where  $C_{\eta} = \cos{(\eta)}$ ,  $S_{\omega} = \sin{(\omega)}$ ;  $a_1$ ,  $a_2$ ,  $a_3$  are scaling factors for x,y, and z; and the exponents  $e_1$  and  $e_2$  control the roundness or squareness in the latitudinal and longitudinal directions. By allowing deformations such as scaling, shearing, tapering and twisting, a very large set of shapes can be obtained (Figure 1b). The constants  $a_1$ ,  $a_2$ , and  $a_3$  implement scaling, which is a simple example of a deformation. Even with the more complex deformations, only a few parameters are needed to describe any of the possible shapes [BARR 84, PENTL 86b], therefore the requirements of a small number of primitives which have a compact representation is easily met. The parameters controlling the superquadric shapes are computable from a map of the surface normals of the imaged objects. The techniques to do so are still quite new, and further work is needed. However, the technique appeared promising enough that an investigation of its parallel execution seemed in order.

#### Comments on the Estimation of Surface Normals

Before the superquadric parameters can be estimated, knowledge of the surface normals in the image, as well as their derivatives along the x and y axes, is required. Several techniques to recover this information have been proposed in the literature. The output of these procedures is an estimate of the x, y, and z components of the surface normal of an imaged object in the area covered by a pixel. These components are aligned with the x, y, and z axes of the image plane. This is illustrated below in Figure 2. Frequently these estimates are expressed as the tilt and the slant. The tilt is the image plane component of the normal vector. In other terms, it is the polar combination of the x and y components. The slant is the perpendicular, or z, component. Both tilt and slant are usually expressed as angles.

Figure 2: Projection of Normal Vector onto Image Coordinates

Early work in the area concentrated on obtaining shape information from a single type of information, such as shading [HORN 75] or texture [WITKI 81]. More recently, Pentland developed a method that uses both texture and shading information [PENTL 84, 86a]. Extending his technique to include motion was covered in [FERRI 85]. A more accurate estimator is described in [LEE 85]. This estimator uses a coordinate system that has the slant oriented with the direction of the main illuminant, rather than being perpendicular to the image plane.

All of these estimates are subject to error. Quantitative description of the error is difficult, but it can be qualitatively described as a bias which is a function of the actual values of the surface normals, with an additive noise component. The shape of the imaged object strongly influences the results. The error is quite small for a spherical object, but becomes greater as the object shape becomes more ellipsoidal. Tables I and II are reproduced from [LEE 85]. Table I gives the absolute value of the error in estimates of tilt and slant for Lee's estimator applied to an artificially generated sphere. Table II gives the

absolute value of the error of Lee's technique on an artificially generated ellipsoid with a 3:1 ratio of major axis length to minor axis length. The top row of each of the tables gives the eight tilts being tested. The first column gives the nine slants tested. Each element of the table has two entries, the first is the error in slant and the second is the error in tilt. As can be seen, the performance degrades as the assumption of equal curvatures is violated.

TABLE I ACCURACY OF LEE'S ESTIMATOR FOR SPHERE

|       |   |   |    |   |    |   |    | Til | :  |   |    |   |    |   |    |   |

|-------|---|---|----|---|----|---|----|-----|----|---|----|---|----|---|----|---|

| Slant | ( | ) | 22 | 2 | 44 | 4 | 66 |     | 88 | 3 | 11 | 0 | 13 | 2 | 15 | 4 |

| 0     | 6 | 0 | 6  | * | 6  | * | 6  | *   | 6  | * | 6  | * | 6  | * | 6  | * |

| 11    | 1 | 0 | 3  | 0 | 3  | 0 | 3  | 0   | 1  | 0 | 3  | 1 | 3  | 1 | 3  | 1 |

| 22    | 2 | 0 | 2  | 1 | 2  | 0 | 2  | 1   | 2  | 0 | 2  | 2 | 2  | 1 | 2  | 0 |

| 33    | 1 | 0 | 1  | 0 | 1  | 0 | 1  | 0   | 1  | 0 | 1  | 1 | 1  | 1 | 1  | 1 |

| 44    | 2 | 0 | 2  | 0 | 2  | 0 | 2  | 0   | 2  | 0 | 2  | 1 | 2  | 1 | 2  | 1 |

| 56    | 0 | 0 | 0  | 0 | 0  | 1 | 0  | 0   | 0  | 0 | 0  | 1 | 0  | 1 | 0  | 1 |

| 67    | 1 | 0 | 1  | 0 | 1  | 0 | 1  | 0   | 1  | 0 | 1  | 1 | 1  | 1 | 1  | 1 |

| 78    | 0 | 0 | 0  | 0 | 0  | 1 | 0  | 0   | 0  | 0 | 0  | 1 | 0  | 1 | 0  | 1 |

| 89    | 7 | 0 | 7  | 0 | 7  | 0 | 7  | 0   | 7  | 0 | 7  | 1 | 7  | 1 | 7  | 1 |

TABLE II

ACCURACY OF LEE'S ESTIMATOR FOR ELLIPSOID

|       |    |   |    |    |    |    |    | Ti | lt |   |    |   |    |    |     |    |

|-------|----|---|----|----|----|----|----|----|----|---|----|---|----|----|-----|----|

| Slant | (  | ) | 2  | 2  | 4  | 4  | 6  | 6  | 88 | 8 | 11 | 0 | 13 | 32 | 1.5 | 54 |

| 0     | 0  | * | 0  | *  | 0  | *  | 0  | *  | 0  | * | 0  | * | 0  | *  | 0   | *  |

| 11    | 11 | 0 | 11 | 16 | 11 | 18 | 11 | 10 | 11 | 0 | 11 | 9 | 11 | 16 | 11  | 15 |

| 22    | 22 | 0 | 22 | 16 | 22 | 17 | 22 | 11 | 22 | 0 | 22 | 9 | 22 | 16 | 22  | 15 |

| 33    | 1  | 0 | 3  | 16 | 11 | 18 | 19 | 10 | 25 | 0 | 19 | 9 | 11 | 16 | 3   | 15 |

| 44    | 8  | 0 | 6  | 16 | 2  | 18 | 10 | 10 | 14 | 0 | 10 | 9 | 2  | 16 | 6   | 15 |

| 56    | 16 | 0 | 12 | 16 | 2  | 18 | 8  | 10 | 11 | 0 | 8  | 9 | 2  | 16 | 12  | 15 |

| 67    | 15 | 0 | 15 | 16 | 5  | 17 | 5  | 10 | 9  | 0 | 5  | 9 | 5  | 16 | 15  | 15 |

| 78    | 4  | 0 | 4  | 15 | 4  | 17 | 4  | 10 | 8  | 0 | 4  | 9 | 4  | 16 | 4   | 15 |

| 89    | 7  | 0 | 7  | 15 | 7  | 17 | 7  | 10 | 7  | 0 | 7  | 9 | 7  | 16 | 7   | 14 |

In addition to the normals information, we must know the derivatives of the normals along the x and y axes. Since the normals information is subject to noise, the calculation of the derivatives must be done with care. The facet model, [HARAL 81,82] seems to offer an approach that will allow the derivatives to be calculated without excessive problems due to the noise in the normals data. This technique assumes that in each K by K neighborhood of the image, the pixel values can be expressed as a polynomial function f of the row and column coordinates. The coefficients of the polynomial are obtained from linear combinations of the values in the KxK neighborhood. Knowing the coefficients of this polynomial, we can easily calculate the derivatives of interest. The convolution masks used to estimate the polynomial coefficients and the derivatives will depend on the size of the neighborhood, the order of the fit, and the basis functions of the polynomial. For the normals information the calculation would be performed three times, once for each of the components of the normal. Convolution on the architectures considered is quite fast, the execution time being proportional to the area of the mask rather than the image size. The convolution procedure is described later in this chapter.

#### Description of the Processing Element

The PE used in this study is essentially the one proposed for use in the CAAPP [LEVIT 84, LAWTO 85, WEEMS 85], circa 1984, with the number of inter-PE communication links being modified for whichever interconnection network is being studied. The memory was also extended from the original 128 to reflect the advances in fabrication technology. The PE is equipped with five register bits, 512 bits of local memory, a simple bit-serial ALU, and communication links with its neighboring PEs. A content addressable broadcast and response mechanism is also provided. These components of the PE, as well as the array controller and microcode format, are described below. Figure 3 gives the functional layout of a PE.

Figure 3: Functional Block Diagram of a Single PE

## Registers and Memory

Each PE has five one-bit registers, denoted A through E. Registers A, C, and E have special purposes, while registers B and D are general purpose. Register A is also known as the activity bit. When this register is cleared, no results can be stored in registers or memory of the PE, effectively disabling the PE. The activity bit can be overridden by setting the Ignore Activity (IA) bit in a micro-instruction. The C register is used as the carry register in the addition instruction. The PE can perform a one-bit add with carry in one clock cycle. The E register is the response register of the content addressable mechanism. The use of these three registers is dealt with below in greater detail.

Each PE has 512 bits of local memory, denoted by the block labeled M in figure 3. Content Addressable Memory (CAM) cells are usually used in a machine which has a

content addressable broadcast and response mechanism. For static memory, such cells involve three extra gates per bit of memory [WESTE 85]. However, the bit serial nature of the content addressable search mechanism for this PE, which performs the comparisons in the ALU instead of memory, allows us to use standard RAM cells instead of the larger CAM cells. Additional VLSI area could be saved by the use of dynamic memory cells, but the refresh cycle would hurt the speed of operation due to the width of the local memories. The timing estimates presented in the results section do not include the time needed for DRAM refresh.

#### **ALU Operations and Control**

The control inputs to the ALU select two sources, a function, and a destination. Sources may be registers, memory, or a value broadcast from the controller. The two sources are denoted as SRC i and SRC j. Destinations are either the registers or memory of the PE. Instructions that access memory can specify only one memory address per instruction. The functions that can be selected are listed in figure 4. They include logical operations, communication with neighboring PEs, and one bit addition with carry. The addition operation automatically uses and updates the carry bit, register C. All functions are computed in parallel and their results sent to the function select multiplexer. The function select field of the micro-instruction determines which of the results is placed on the result line for storage. Control lines are provided to allow the negation of any combination of the source and result bits.

Communication with neighboring PEs is accomplished with the E register and the function select block. Each PE continuously broadcasts the value in its E register to all PEs it can communicate with. When communication with neighboring PEs is desired, the function select lines of the destination PE choose which of the broadcast values will be placed on the result line. This value is then routed to its destination within the PE, either

register or memory. The slow-down of the communication operations due to the high fanout of the E register is ignored in this study, under the assumption that it will not be a critical limitation on the clock frequency. The number of control lines needed for the function select multiplexer will depend on which interconnection network is being used. The pincounts for the various architectures are given in the last section of this chapter.

## Content Addressable Broadcast and Response Mechanism

A notable feature of the PE is the content addressable broadcast and response mechanism. This mechanism allows the host or the controller to interrogate the PE array about characteristics of the image, avoiding the need for the image data to be dumped to the host for sequential evaluation. The controller broadcasts a one bit value to each PE on the Broadcast Comparand (BC) line. The source selected by the SELECT i multiplexer is compared with this broadcast value. If they are the same, a one is placed on the result line. This value will usually be stored in either the PE's response bit, register E, or the activity bit, register A. The response bits of all the cells are OR'ed together and made available to the controller as the SOME/NONE flag. At any time, the number of responding cells can be obtained by use of the COUNT RESPONDERS function. An adder tree is used to obtain the count. A description and timing analysis of the adder tree is given in [LEVIT 84]. The time to obtain the response count for a  $512 \times 512$  image is 2.5 microseconds. Due to the organization of the adder tree, response count requests can be issued every 1.6 microseconds [LEVIT 84]. The algorithms developed in this study do not make use of either the SOME/NONE or COUNT RESPONDERS functions, therefore we will not consider them further.

It will frequently be useful to restrict processing to only those PEs with a particular bit pattern in some field of memory. The activity bit, register A, allows subsets of the PEs to be disabled. By storing the result of a comparison in the activity bit, all PEs that failed

the comparison can be disabled. The simple algorithm below will leave enabled all cells that exactly meet some search criterion, leaving all others disabled.

#### **ALGORITHM 1: SELECTIVE PROCESSING**

SELECT all cells

for each bit in the pattern

BROADCAST bit value.

IF ACTIVE, COMPARE with memory location, store result in activity bit

next bit and memory location

Note that this algorithm's execution time is proportional to the length of the pattern, not to the size of the image. This is a frequent occurrence in these architectures. If an exact match is not desired, Foster [FOSTE 76] gives algorithms for several other matching criteria such as minimum, maximum, greater than, less than, closest to, etc. The algorithms developed in this study frequently select PEs based on their position in the array. These comparisons require that the coordinates of the PE be stored in its local memory.

#### Microcoded Array Controller

The array controller is a microcoded sequencer which receives assembly language level instructions from the host and interprets them as a call to a microcode subroutine that the PEs can execute. The same micro-instruction is broadcast to all PEs at the same time, thus the architectures are of the Single Instruction stream / Multiple Data stream (SIMD) variety. As mentioned earlier, the PE will execute the instruction only if its activity bit is set, or if the micro-instruction's IA, Ignore Activity, bit is set.

The format for the portion of a micro-instruction broadcast to the PEs is given in Figure 4, along with the basic micro-operations that can be performed by the PE. Micro-instructions are of the form: select two sources, perform some operation on them, then store the result in some destination. The local memory is fast enough that a read-modify-

write takes a single clock cycle. Instructions which access the local memory must use the same address for all memory operands. In other words, local memory to memory transfers take two instruction cycles per bit and must proceed through an intervening register. Transferring a data value in the memory of one PE to the memory of another PE also takes two instructions, since the data must be moved from the memory of the first PE to its E register. This takes one instruction cycle. During the second instruction cycle the value of the E register is automatically broadcast to all neighboring PEs. The function select of the destination PE puts this value onto its result line and enables writing to the memory location whose address is specified in the second micro-instruction.

The microword will also have additional fields for use within the array controller to support looping, microcode subroutines, etc. The form of these additional fields will depend on the design of the array controller and will not be considered in this study.

| IA SRCj SRCi F                                      | i j r                                                                    | Address                                                                                                                                                             |

|-----------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IA                                                  | Neg i,j,r                                                                | Function                                                                                                                                                            |

| 0 Use Activity Bit<br>1 Ignore Activity Bit         | 0 True<br>1 Complement                                                   | 0 i<br>1 j<br>- 2 CMP i,j (XNOR<br>3 ADD i,j,C<br>4 NAND i,j                                                                                                        |

| SRC i,j  0 None 1 M 2 A 3 B 4 C 5 D 6 E 7 Comparand | Dest  0 None 1 A,C (ADD,SUB) 2 A 3 B 4 C 5 D 6 E 7 M  * Only for Pyramid | 5 NOR i,j 6 Read N 7 Read S 8 Read E 9 Read W 10 Read NE* 11 Read NW* 12 Read SE* 13 Read SW* 14 Read Parent* 15 Read NE Child* 16 Read SE Child* 17 Read NW Child* |

Figure 4: Microinstruction Format

#### Parallel Image Processing Architectures

As noted above, many parallel architectures have been suggested for use in image processing. The majority of image processing algorithms apply the same operations to all pixels in an image, or a subset of the image. This makes them suitable for implementation on Single Instruction stream, Multiple Data stream (SIMD) machines. This is the simplest type of multiprocessor, where all PEs execute the same instruction at the same time. This greatly simplifies the programming task, especially for system software. Another important characteristic of image processing algorithms is that most calculations depend upon the values of a few neighboring pixels. This has important implications for the network interconnecting the processing elements.

Too many architectures have been suggested to give a complete survey here.

However, the architectures proposed can be divided into several classes. SIMD vs. MIMD is a major distinction, as is the granularity of the processing ensemble. The interconnection network used to connect the PEs is important. Also important is the communication between the host and the parallel architecture. The majority of specialized image processing architectures that have been proposed are coarse-grained SIMD machines. A linear or mesh interconnection is frequently used, although hypercube and tree topologies are also used on occasion. Few have used content-addressable memory, due to its high cost compared to standard DRAM. The coarse grained approach is used to take advantage of the widely available microprocessors and specialized DSP chips. Many fine-grained architectures have been proposed on paper but few have been fabricated.

Of all the SIMD architectures which have been suggested for image processing, the class of highly parallel architectures offers perhaps the greatest potential for performance. These architectures have at least one PE for each pixel in the image. These PEs are usually bit serial ALUs with a small amount of local memory, typically less than 1024 bits, and connections to a small number of neighboring PEs. The massive parallelism of these fine-

grained designs more than compensates for the slow speed of bit serial operation. By having one PE for each pixel in the image, the dependance on the size of the image in many image processing algorithms is removed. As an illustration, consider the problem of adding a constant to every pixel in an image. On a standard serial machine, ignoring the overhead of instruction fetches, the time to perform this function can be calculated from

$$N(t_{read} + t_{add} + t_{store}),$$

where N is the number of pixels in the image. For a large array of bit-serial processors the time can be calculated from

$$B(t_{read} + t_{add} + t_{store}),$$

where B is the number of bits to be added in each PE. If we assume that the standard processor can read a word, add the constant, and store the resulting word in the same time that the bit-serial processor can perform the same operations on a bit, then the array will work faster anytime there are more pixels in the image than bits in a word. If we use 16-bit words and the image size is 512 x 512, the array will be 16,384 times faster.

To provide another illustration of these machines, let us compute an approximate figure for floating point arithmetic speed. Assume that a 32-bit floating point multiply takes 2000 clock cycles. If the clock frequency is 10 MHz., each PE has a speed of 5 KFlops. This is quite slow compared to the performance of dedicated arithmetic coprocessors such as the Intel 80387, which can perform approximately 300 KFlops. However, the 5 KFlop figure was for one PE. There are 64 PEs on a chip, giving 320 KFlops per chip. For a 512x512 image, there are more than a quater million PEs. The floating point performance for the entire array is 1.25 GFlops!

Several factors go into determining the speed with which a parallel processor can execute a particular algorithm. Obviously, the speed of the PE is an important factor.

However, the fit between the interconnection network and the communication needs of the task to be performed is at least equally important. This latter factor is what we will be comparing in this study. In order to keep the speed and area comparisons of the interconnection networks meaningful, the three machines are considered to have equivalent PEs. The difference between the architectures in this study is the type of interconnection network used to communicate with neighboring PEs. The interconnection networks studied are described in the next section.

The interaction between the host and the processing array is handled by the array controller. The content addressable mechanism described earlier provides a powerful way to control the operations of the array, as well as obtain results without dumping the entire image for slow sequential evaluation by the host.

# Interconnection Networks Studied

Three interconnection networks were chosen for comparison in this study. All use essentially the same processing element, the only differences being in the number of communication lines and their corresponding control lines. Each of these interconnection networks will be described below. In addition to the interconnections between the PEs, each interconnection network has communication links with the array controller. As mentioned earlier, each of these architectures is of the SIMD type. All the instructions are broadcast from a microcoded central controller. The central controller can also broadcast data to all the PEs. This data broadcast is done bit-serially. As well as being able to send data to the array of PEs, the controller can receive data from the array by means of a content addressable response mechanism. The content addressable mechanism was discussed in a previous section.

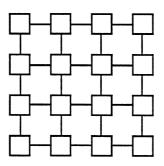

## Four Nearest-Neighbor Mesh

The first interconnection network is the standard four nearest neighbor (4NN) mesh. In this interconnection network the PEs are arranged in a two dimensional mesh, one PE for each pixel in the image. Each PE that is not on an edge of the mesh has communication links with its four nearest neighboring PEs, as illustrated below in Figure 5. Communication for those PEs that are on the edge of the mesh can be handled in several fashions, as shown in Figure 6.

Figure 5: Four Nearest Neighbor Interconnection Network

Figure 6: Sample Edge Treatments

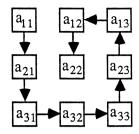

This interconnection network has recieved a great deal of attention for image processing purposes, due to direct mapping of pixels onto PEs. The 4NN mesh can execute many of the algorithms used in the lower levels of vision. As an illustration, consider the task of convolving the image with a three by three mask. We will denote the coefficients of this mask as a<sub>11</sub>, a<sub>12</sub>, ..., a<sub>33</sub>, and will ignore edge effects. The first step is to broadcast  $a_{11}$  to all the PEs. They will multiply  $a_{11}$  by the image value they contain, then move the product to their southern neighbor. The value of  $a_{21}$  will then be broadcast and multiplied by the image value, then added to the product from the previous step. We will continue the broadcast and accumulate process in a spiral fashion. At the last step, the value of a<sub>22</sub> is broadcast, multiplied by the image value, then added to the accumulated value read from the PE's northern neighbor. The data movements of this algorithm are shown in Figure 7. The important thing to note about this algorithm is that the execution time will be proportional to the area of the mask and the numeric precision of the operands, not the area of the image. [LEVIT 84] gives sample times for convolution with varying size masks. Assuming 8-bit pixels, the time for the 3x3 mask was 0.7 msec., the time for the 7x7 mask was 4.0 msec. These times are independent of the size of the image. Multiplies are quite slow on this machine, since their execution time is proportional to the square of the number of bits multiplied. If the convolution mask is symmetric, the time for the convolution can be reduced. Keep in mind that these times are for the CAAPP. As will be seen in the next section, the CAAPP is not as fast as the 4NN. The times for the 4NN would be roughly half those for the CAAPP.

Figure 7: Data Movements for Convolution

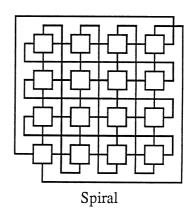

### Content Addressable Array Parallel Processor

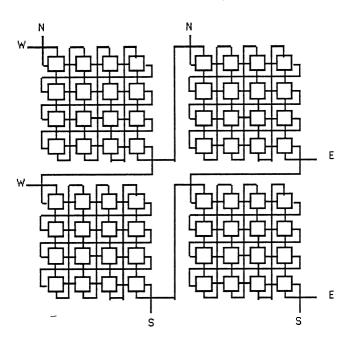

The second interconnection network is the one proposed for use in the Content Addressable Array Parallel Processor (CAAPP), circa 1984. This architecture has recently undergone major design changes, one of which was to use a full 4NN mesh. The original version uses an interconnection network which is organized as a mesh of submeshes. Referring to Figure 8, we see that each four by four submesh has the standard mesh connection, with the edges being treated as a double spiral. However, communication between the submeshes is restricted to one bidirectional link between neighboring submeshes. When data must cross a submesh boundary this will increase communication time by a factor of four, plus overhead, compared to the 4NN mesh. The advantage of this submesh organization is that the pincount of the VLSI devices is reduced considerably. For example, assume each package has 64 PEs organized as an eight by eight portion of the array, only needing communication links to neighboring packages. For the case of the 4NN mesh, each PE on the perimeter needs a communication link off-chip, and the corner PEs need two. This gives a count of 32 pins needed simply for inter-chip communication. For the CAAPP, this is reduced to eight. The savings in pin count is very important when the board level pin count is calculated. Assuming each board has 64 chips arranged in an eight by eight array, the number of pins needed to communicate with other boards in the

system is reduced from 256 to 64. Since connections are a major reliability problem, this savings is quite important.

Figure 8: Interconnection Network for One Chip of the CAAPP

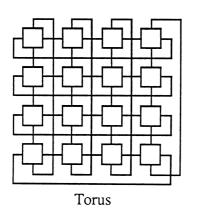

## The Pyramid

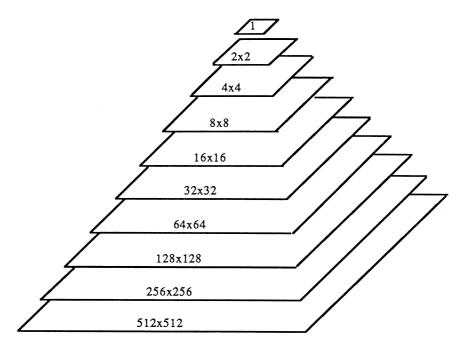

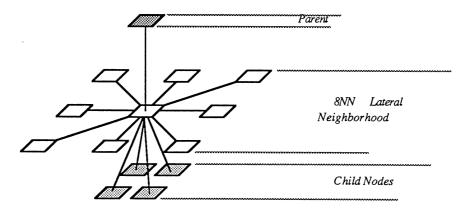

The final architecture studied is the pyramid [TANIM 84, DYER 81]. This architecture uses more PEs than the others, as well as a more complex interconnection network. The interconnection network used is illustrated below in Figures 9a and 9b. In this scheme, the processing array is organized into L layers of 8NN meshes. Each mesh has four times as many PEs as the mesh above it. The top layer has a single PE, while the bottom layer has as one PE for each pixel in the image. The number of layers, L, can be

found from the relation L = log<sub>2</sub>(r)+1, where r is the number of pixels per row or column in the base layer. Each PE not on the edge of a layer or in the top or bottom layers communicates with 13 neighboring PEs, one on the layer above, four on the layer below, and eight on the same layer. These 13 PEs are referred to as the pyramidal neighborhood. The pyramidal neighborhood is shown in Figure 9b. The eight nearest neighbors on the same layer are referred to as the lateral neighborhood. The connections at the root, base, and edge cells can be handled in fashions similar to those for the 4NN. Additionally, a border register is provided for high speed I/O between the array and either the image digitizer, image display unit, or mass storage. The border register has 2<sup>L-1</sup> one-bit registers which connect to the PEs on one edge of the base level of the pyramid. The overall organization of the pyramid machine is shown in Figure 9a.

This organization is an implementation of the resolution pyramid data structure, which has been shown to have several advantages for vision processing [BALLA 82, HANSO 78]. For serial machines, the upper levels of the Pyramid can be processed, and the results of that processing used to guide the processing of the lower levels. This has the advantage of reducing the computations expended on the lower layers, as well as providing some measure of noise immunity. Region growing algorithms based on a split and merge technique also use the Pyramid data structure for efficiency gains. More information on the use of pyramids can be found in [TANIM 80].

Figure 9a: The Pyramid Interconnection Network

Figure 9b: The Pyramidal Neighborhood

#### Edge Treatments

The subsection on the 4NN briefly discussed possible methods of handling communication for those PEs on the edges of the processing arrays. These edge treatments are also applicable to the CAAPP and Pyramid machines. Various algorithms make up the image processing stage of computer vision, not all of which will necessarily use the same edge treatment. Edge treatments can be handled by the use of programmable switches. The communication lines at the edge of the processing array would be routed to these switches, which could then provide spiral, torus, wired-1, or wired-0 connection schemes. These switches might be located on the controller board, or on a seperate board.

Another common factor in all the interconnection networks is the need for I/O with the image acquisition, image display, and mass storage hardware. All the interconnection networks will be augmented with a border register to provide this functionality. The border register was briefly described in the Pyramid subsection.

#### VLSI Fabrication Considerations

At this point, it seems appropriate to consider some of the details of the VLSI implementation of the interconnection networks studied. The following sub-sections discuss the package and board level implementation of these networks for a 512 x 512 image. Several simplifying assumptions were used. The first was that the area required for the memory and ALU of the PEs would dominate the size of the die, therefore no comparisons of the differences in area of the interconnection networks were made. No gate counts were computed, however, current limits on gate count suggest that there be no more than 64 PEs, each with approximately 512 bits of memory, integrated into one package.

Despite the ever-increasing numbers of devices that can be fabricated onto a chip, pin counts are expected to remain limited to around one or two hundred pins per package until the advent of wafer-scale integration. Therefore, the number of PEs that can be

fabricated onto a chip will be limited by practical pin count as well as by the total gate count. The CAAPP is the only interconnection network that directly addresses this limitation. However, by arranging the 64 PEs on each chip into an eight by eight array, the number of communication lines needed for each chip is not a major problem. The 4NN would require 32 pins for communication, the CAAPP would need eight. Even with the additional pins for instructions, power, ground, and clock, the pincounts are within current limits.

While the 4NN and CAAPP are within the capabilities of current fabrication technology, the limits on pin and gate count make the implementation of the pyramid impractical today. Therefore, the limits on the number of PEs were relaxed somewhat for the pyramid. Device sizes should soon be at a level that will allow more gates per device, without much help in the way of pincount limits. Pin counts do become restrictive for the Pyramid, as will be discussed later. By allowing 85 PEs per die, a practical configuration for the Pyramid was achieved which met the limits on pincount.

#### 4NN and CAAPP Pincounts

The 4NN and CAAPP, using 64 PEs per package, will require a total of 4096 packages for a 512x512 image. If 64 packages are mounted on each printed circuit board, 64 such boards would be needed. Obviously, such a system would be expensive to construct. The submesh organization of the CAAPP would make it a cheaper and more reliable system. This is due to the reduced number of pins needed on the packages and boards. For the 4NN, each PE on the perimeter of the package will need a communication pin, corner PEs will need two. This gives a total of 32 communication pins for each package. For the CAAPP, only eight communication lines will be needed per package. An additional 25 pins will be needed for instructions, two for power and ground, one for the

clock, and four for the content addressable broadcast and response mechanism. Thus, the number of pins for each package is 40 for the CAAPP and 64 for the 4NN.

Additional pins might be used for chip or quadrant enables. This would speed selections based on row-column coordinates by having all but a few of the least significant bits handled by chip and board enables instead of the ALU of the PEs. However, the benefit of the enable pins is unclear. For a 512x512 image there are only 18 bits in the row-column address. While such selection is a frequently used operation, its execution time by either method is quite small compared to a multiply or divide. For this study, the algorithms for superquadric estimation all execute on small portions of the array, allowing many estimations to be accomplished in parallel. Selections in these algorithms only depend on a few of the least significant bits in the row-column address, therefore the enable pins would not appreciably impact their execution. For this reason, no enable pins will be considered, and all row-column selections will be accomplished by a bit-serial associative search into memory.

Pincount savings at the package level will be especially important when the pincount of the printed circuit boards is considered. Assuming 64 packages per board, arranged in an eight by eight mesh, each board of the 4NN will require 256 connections to the backplane for communication lines while the CAAPP boards will only require 64. We again will need 32 additional lines for instructions, power, etc. Board level response counts must be provided, at the expense of an additional 17 lines. The total board level pincount is thus 113 for the CAAPP and 305 for the 4NN. The package and board level counts for the 4NN and CAAPP are presented with those for the Pyramid in Table V at the end of this section.

## **Pyramid Pincounts**

The twin limitations of gate and pin counts are especially acute for the Pyramid. Given that we cannot integrate the Pyramid into a single package, we must decide on an appropriate way to distribute the PEs. This will require that the machine be composed of two type of chips; those which contain leaf, or base, cells and those that do not [DYER 81]. The first type is called a leaf chip, the other is a non-leaf chip. Several levels of the machine would be provided in each type of chip.

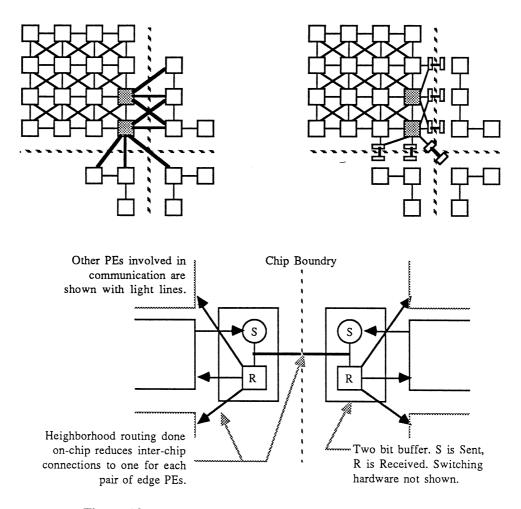

The number of levels that can be integrated onto a non-leaf chip will be limited by the pincount necessary for the lowest level of the non-leaf chip to communicate with its children. For example, consider the top of the pyramid. One line will be needed for communication above the root cell. If three levels of the pyramid are to be integrated into a single package, there will be 16 PEs on the bottom level. Each of these PEs must be provided with links to its four child nodes. This brings the pincount to 65 for communication with parent and children alone. To this must be added 33 more lines for instruction lines, power, ground, clock, and associative response. If we consider the chips which will make up the interior of the Pyramid, we see that we must also provide lines for communication within the lateral neighborhood. For the chips on the edges of the array, these lines will be wrapped around to the opposite side of the array to handle edge treatments as described earlier in this chapter. Since the lateral neighborhood is an 8NN mesh, the pincounts here will be greater than those for the 4NN or CAAPP. There are several ways to handle this 8NN connection, two are diagramed below in Figure 10. The first is the simple-minded solution. This requires three communication pins for each PE on the edge of a chip, while corner PEs require five pins. This is shown in the figure by highlighting a corner and edge PE, and showing their off-chip communication links with bold lines. The pincount can be reduced by adding two-bit buffers to each end of the

communication lines. One of the buffer bits would be dedicated to broadcasting the value from the E register of the closest PE on the same chip. This is denoted as the S, or Send, bit in Figure 10. The second bit would hold the E register value from the PE on the other chip. This value would then be routed to the necessary PEs on the first chip. This bit is denoted by R, or Receive, in the figure. Using this scheme, the pincount can be reduced to one pin for each edge PE, with corners needing three pins. This is a penalty of only four pins, one at each corner, compared to the 4NN and CAAPP interconnection networks.

Figure 10: Inter-Chip Communication for 8NN Meshes

For the three-level non-leaf package discussed above, this will add another 40 pins, bringing our total to 138. If only two levels of the pyramid are fabricated onto a non-leaf chip, the total pin count is reduced to 70. Four levels gets quite expensive with 365 pins per chip. The pin counts as a function of the number of levels per package are tabulated below in Table III. This table also gives information about how many chips and boards would be required for a complete 512 x 512 system. This will depend upon how many levels are integrated into the leaf chips. The numbers in Table III are based on the assumption of four levels in the leaf chips. They also assume a single PE at the top of each non-leaf chip.

TABLE III

NON-LEAF CHIP PARAMETERS AS A FUNCTION OF THE NUMBER OF LEVELS PER PACKAGE

| Number<br>of PEs | Comm. Pins<br>per chip | Total Pins<br>per chip       | Number of Chips<br>for 512x512 Image         |  |

|------------------|------------------------|------------------------------|----------------------------------------------|--|

| 5                | 37                     | 70                           | 273                                          |  |

| 21               | 105                    | 138                          | 65                                           |  |

| 85               | 332                    | 365                          | 17                                           |  |

|                  | of PEs  5 21           | of PEs per chip  5 37 21 105 | of PEs per chip per chip  5 37 70 21 105 138 |  |

The pin limit is not so severe for the leaf chips, since they do not need four lines for each terminal cell. Assuming a single PE at the top, a three-level leaf chip will have 21 PEs per package. Such a chip will implement an 4 x 4 section of the base level. There will be 40 lines for communication within the lateral neighborhoods, one for communicating with the parent PE, as well as 33 pins for instructions, etc. Such a device would have 71 pins.

There is no need for the top level of the leaf cell to have a single PE. If we do away with this restriction we can put more PEs on each leaf cell, reducing the number of packages needed. Table IV summarizes the pin, package and board counts versus the number of levels and the number of PEs that occupy the top level.

TABLE IV

LEAF CHIP PARAMETERS AS A FUNCTION OF THE NUMBER OF LEVELS

PER PACKAGE AND THE NUMBER OF PES ON THE TOP LEVEL

| Levels Number of PEs<br>per Chip on Top Level |    | Number of PEs per Chip | Communication<br>Pins per Chip | Total Pins<br>per Chip | Number of Chips<br>for 512x512 Image |  |

|-----------------------------------------------|----|------------------------|--------------------------------|------------------------|--------------------------------------|--|

| 2                                             | 1  | 5                      | 21                             | 54                     | 65,536                               |  |

| 2                                             | 4  | 20                     | 36                             | 69                     | 16,384                               |  |

| 2                                             | 16 | 80                     | 72                             | 105                    | 4,096                                |  |

| 3                                             | 1  | 21                     | 41                             | 74                     | 16,384                               |  |

| 3                                             | 4  | 84                     | 72                             | 105                    | 4,096                                |  |

| 4                                             | 1  | 85                     | 77                             | 110                    | 4,096                                |  |

| 5                                             | 1  | 341                    | 145                            | 178                    | 1,024                                |  |

## System Level Assembly

Assembling the 4NN and CAAPP into a system would be relatively straightforward. The designer of a Pyramid has several decisions to make which the other two machines do not present. The decision about how many levels per chip is one instance. In a similar fashion, we may wish to put both types of chip onto a single board to reduce pincount. Another minor problem to address concerns the root cell. The number of levels used for the leaf and non-leaf chips may not allow the root cell to appear at the top of the topmost package. In other words, the root PE will have parents! This is not as serious as it sounds, but a slight amount of special handling would be necessary when dealing with

the top of the pyramid. For Table V, the pyramid was assembled from 4 level leaf cells and three-level non-leaf cells. This gives a balanced pyramid, i.e., the root PE has no parents. The decision was also made to put 64 leaf chips and one non-leaf chip onto the low level boards. The single remaining non-leaf chip could then be easily placed on the controller board. This reduces the number of board-level connections, while also reducing the board count by one. The board eliminated would have held 64 non-leaf cells, each with 16 PEs on the bottom layer. Since each PE on the bottom layer of the non-leaf cell needs four communication lines to its children, eliminating this board reduces the complexity of the backplane considerably. The counts for such a system are presented below in Table V, along with those for the 4NN and CAAPP.

The final column gives an estimated MTBF (Mean Time Between Failures) for each machine. Typical failure times for backplane connections are on the order of 1E8 to 1E9 hours. For complex VLSI chips, the failure time is approximately 1E7 to 1E8 hours. The failure rates of validated printed circuit boards and solder joints are so low that they can be neglected 1. For the table below, the failure times were taken to be 5E8 hours for the connections and 5E7 hours for the chips. It should be noted that the failures may not be fatal, or even seriously degrade results. The massive parallelism of the interconnection networks considered provides a degree of fault-tolerance. Since most image processing algorithms are local, the effects of a hardware failure may remain confined to a small area of the image. Detecting such areas and deciding on an appropriate error-recovery technique is another question, and beyond the scope of this study.

<sup>1</sup> Reliability estimates courtesy Dr. Dave Ballew, AT&T Technologies

$\label{eq:table_v} \mbox{Table v}$   $\mbox{System Level comparison}$

| Network | PEs per<br>512 <sup>2</sup> image | Chips per image | Boards per<br>system | Backplane lines<br>per board | Backplane lines<br>per system | MTBF<br>(weeks) |

|---------|-----------------------------------|-----------------|----------------------|------------------------------|-------------------------------|-----------------|

| Pyramid | 349,525                           | 4,161           | 65                   | 570                          | 36,480                        | 38              |

| 4NN     | 262,144                           | 4,096           | 65                   | 286                          | 18,304                        | 50              |

| CAAPP   | 262,144                           | 4,096           | 65                   | 94                           | 6,016                         | 63              |

#### CHAPTER III

#### PROCEDURE