## UNIVERSITY OF OKLAHOMA GRADUATE COLLEGE

## EXPLOITING HETEROGENEOUS MULTICORE PROCESSORS THROUGH FINE-GRAINED SCHEDULING AND LOW-OVERHEAD THREAD MIGRATION

A DISSERTATION

#### SUBMITTED TO THE GRADUATE FACULTY

in partial fulfillment of the requirements for the

Degree of

#### DOCTOR OF PHILOSOPHY

By

LINA HAKAM SAWALHA Norman, Oklahoma 2012

#### EXPLOITING HETEROGENEOUS MULTICORE PROCESSORS THROUGH FINE-GRAINED SCHEDULING AND LOW-OVERHEAD THREAD MIGRATION

# A DISSERTATION APPROVED FOR THE SCHOOL OF ELECTRICAL AND COMPUTER ENGINEERING

BY

Dr. Ronald D. Barnes, Chair

Dr. Monte P. Tull, Co-Chair

Dr. Joseph P. Havlicek

Dr. James J. Sluss

Dr. Jon G. Bredeson

Dr. John K. Antonio

© Copyright by LINA HAKAM SAWALHA 2012 All Rights Reserved. To My Parents

For their support, care and love

### Acknowledgements

I wish to thank my advisor, Dr. Ronald D. Barnes, for his help, advice, encouragement and support he provided during my PhD studies. His insight and direction enabled me to produce quality research. I would also like to thank my co-advisor, Dr. Monte P. Tull, for his help, support, encouragement and valuable discussions. Moreover, I would like to thank my PhD committee members Dr. Joseph Havlicek, Dr. James Sluss, Dr. Jon Bredeson and Dr. John Antonio for their support and advice.

I would like to thank Xiaolei Yan and Dr. Amy McGovern for their work on the reinforcement-learning-based scheduler. I also wish to thank in particular the Soonergy Lab team, Sonya Wolff, Nick Freeman, Frederic Bard and Dustin Northup for their work on the Soonergy Framework used throughout this work.

I also would like to thank my parents for their ultimate support, endless love, valuable advice and encouragement. Without their support and encouragement I would not be able to finish my PhD studies. Furthermore, I thank my siblings, family and friends for being there for me and for their support not only for my graduate studies but in all other aspects of my life as well.

Finally, I would like to thank the school of electrical and computer engineering for the teaching assistantship and the support of the National Science Foundation (Grant No. 1018771).

## Table of Contents

| Acknowledgements i                                                                                                                                                                                                                                                                                                                                                                      | v                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| List of Tables vi                                                                                                                                                                                                                                                                                                                                                                       | ii                                          |

| List of Figures vi                                                                                                                                                                                                                                                                                                                                                                      | ii                                          |

| Abstract                                                                                                                                                                                                                                                                                                                                                                                | x                                           |

| Chapter 1. Introduction                                                                                                                                                                                                                                                                                                                                                                 | 1                                           |

| 1.1.1 Challenges of Designing Heterogeneous Multicore Processors .        2 Dissertation Motivation                                                                                                                                                                                                                                                                                     | 4<br>5<br>7<br>0                            |

| .4 Dissertation Organization                                                                                                                                                                                                                                                                                                                                                            | 1                                           |

| 2.1.1       Homogeneous Multicore Processors       1         2.1.2       Heterogeneous Multicore Processors       1         2.2       Scheduling Applications to Cores       2         2.2.1       Static (Off-line) Scheduling Techniques       2         2.2.2       Static/Dynamic Scheduling Techniques       2         2.2.3       Dynamic (On-line) Scheduling Techniques       2 | 3     4     8     0     1     2     4     9 |

| Chapter 3. Methodology 3                                                                                                                                                                                                                                                                                                                                                                | 4                                           |

| 3.1.1 Cycle-Accurate Simulation Framework                                                                                                                                                                                                                                                                                                                                               | 4<br>4<br>5                                 |

|                                                                                                                                                                                                                                                                                                                                                                                         | 6                                           |

| 3.1.4 Experimental Workload                                                                                                                                                                                                                                                                                                                                                             | 6                                           |

| 3.1.5 Evaluation Metrics $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 38  |

|--------------------------------------------------------------------------------------------------|-----|

| 3.1.6 Program Phase Detection Method                                                             | 40  |

| Chapter 4. Scheduling for Heterogeneous Multicore Processors                                     | 45  |

| 4.1 Phase-Based Scheduling                                                                       | 46  |

| 4.1.1 Scenario                                                                                   | 49  |

| 4.1.2 Phase_Sampling Approach                                                                    | 51  |

| 4.1.3 Phase_IPC Approach                                                                         | 53  |

| 4.1.4 Evaluation and Results                                                                     | 55  |

| 4.2 Energy-efficient Scheduling Algorithm                                                        | 67  |

| 4.2.1 Phase_EDP Scheduling Algorithm                                                             | 68  |

| Chapter 5. Hardware Support for Fast Context Switching                                           | 75  |

| 5.1 Methods to Support Frequent Thread Migrations                                                | 76  |

| 5.2 Measuring the Overhead of Context Switching                                                  | 77  |

| 5.3 Hardware Thread Migration and Context Switching                                              | 79  |

| 5.4 Evaluation                                                                                   | 89  |

| Chapter 6. Application Scheduling for Many-Core Processors                                       | 91  |

| 6.1 Scheduling for HMCPs using Machine Learning                                                  | 91  |

| 6.1.1 RL-Based Fine-Grained Scheduler                                                            | 92  |

| 6.2 Evaluation and Results                                                                       | 97  |

| 6.2.1 On-line Learning                                                                           | 98  |

| 6.2.2 Off-line learning                                                                          | 100 |

| Chapter 7. Conclusions and Future Work                                                           | 105 |

| 7.1 Summary                                                                                      | 105 |

| 7.2 Future Work                                                                                  | 108 |

| Bibliography                                                                                     | 111 |

## List of Tables

| 3.1 | Processor configurations                                                                                                                                                                                        | 36 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | SPEC2006 benchmarks simulated                                                                                                                                                                                   | 37 |

| 4.1 | IPC and number of instructions of each phase of threads A and B.                                                                                                                                                | 50 |

| 4.2 | Possible sets of phases, combining both threads A and B                                                                                                                                                         | 50 |

| 4.3 | Execution phases-identified when running threads for $10000 A$<br>and $B. \ldots \ldots$ | 51 |

| 4.4 | processor configurations                                                                                                                                                                                        | 55 |

| 7.1 | Comparison between the proposed scheduling algorithm and heuris-<br>tic sampling approach [42].                                                                                                                 |    |

## List of Figures

| 1.1  | IPC of an in-order core and an out-of-order core, for <i>bzip2</i> application                                                                          | 8  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | The ratio of IPC of an in-order core over an out-of-order core, for $bzip2$ application.                                                                | 9  |

| 1.3  | The performance of applications on a quad core processor using different scheduling granularity.                                                        | 9  |

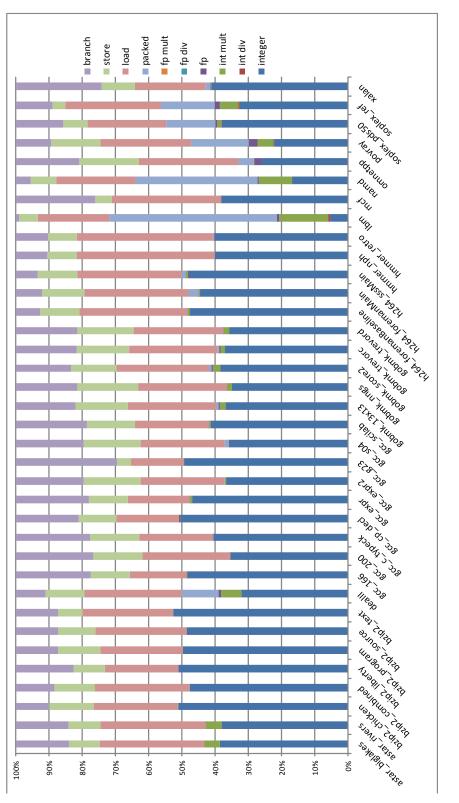

| 3.1  | Instruction Mix of SPECCPU2006.                                                                                                                         | 39 |

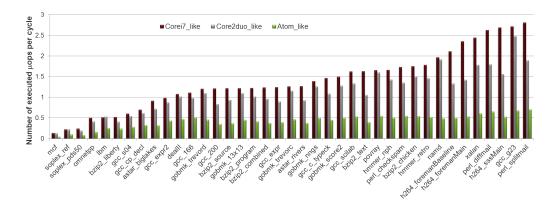

| 3.2  | A Comparison of the performance on three cores (Corei7_like,<br>Core2duo_like and Atom_like) described in Table 3.1 for SPEC-<br>CPU2006.               | 40 |

| 3.3  | Computation of current working set signature                                                                                                            | 42 |

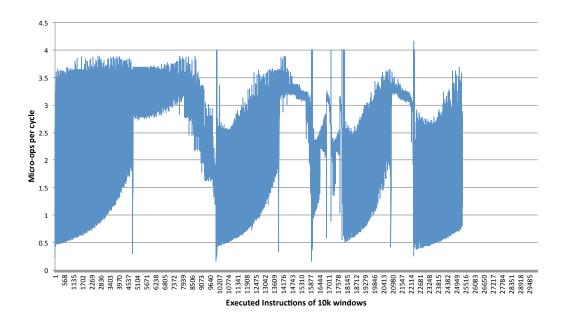

| 3.4  | Executed micro-operations per cycle over 10 000 instruction win-<br>dows for a CPU 2006 benchmark <i>xalan</i>                                          | 43 |

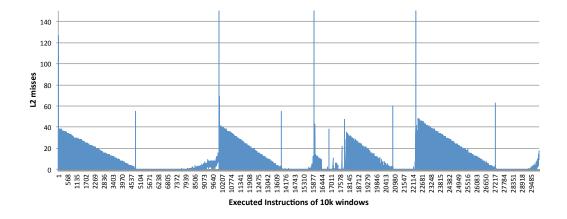

| 3.5  | The number of L2 cache misses for <i>xalan</i>                                                                                                          | 44 |

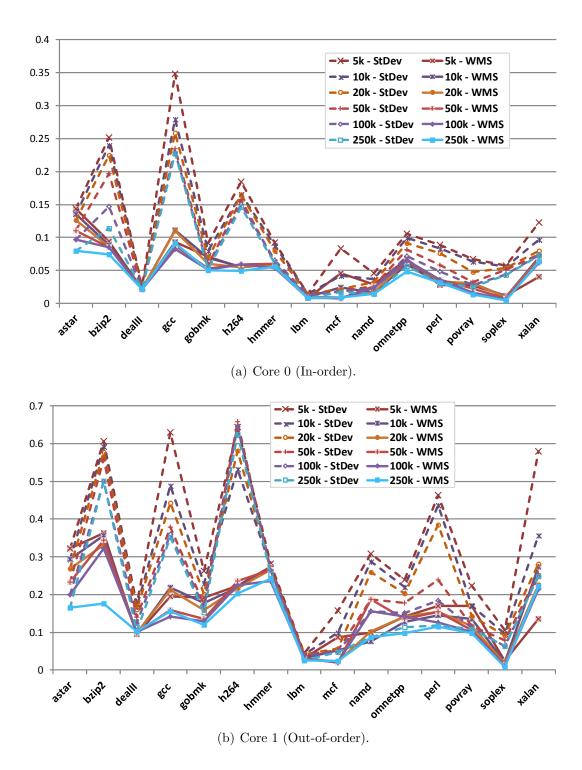

| 4.1  | Standard deviation of IPC over the entire application (StDev) and weighted mean standard deviation across windows of the same phase for each benchmark. | 48 |

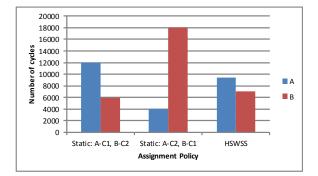

| 4.2  | Number of executed cycles for different assignment polices for<br>two threads running on a dual-core HMP                                                | 52 |

| 4.3  | Signature History Table for <i>Phase_Sampling</i> Approach                                                                                              | 53 |

| 4.4  | Signature History Table for <i>Phase_IPC</i> Approach                                                                                                   | 54 |

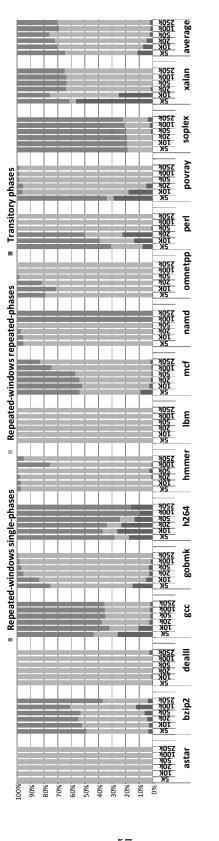

| 4.5  | Classification of windows in each application for varying window sizes.                                                                                 | 57 |

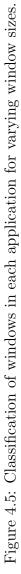

| 4.6  | Average number of phases and repeated phases detected using different signature sizes.                                                                  | 58 |

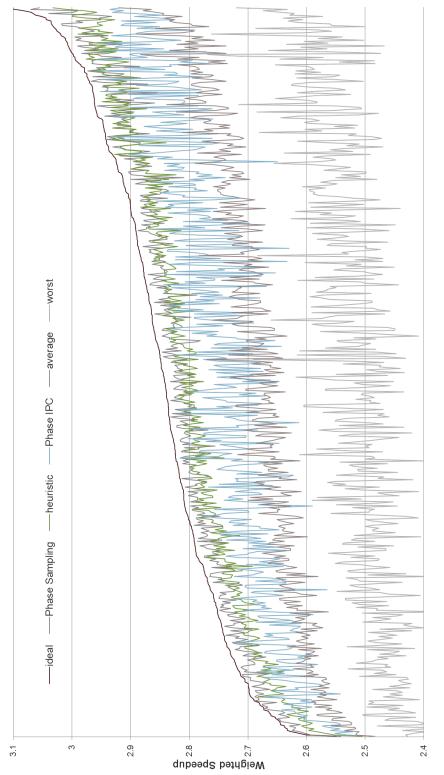

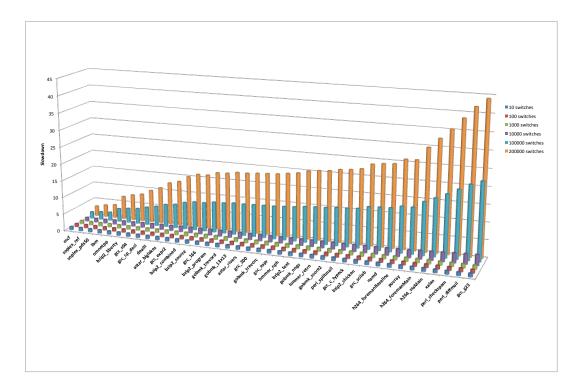

| 4.7  | Weighted speedup for different scheduling algorithms on 500 sets of 4-tuple benchmarks.                                                                 | 61 |

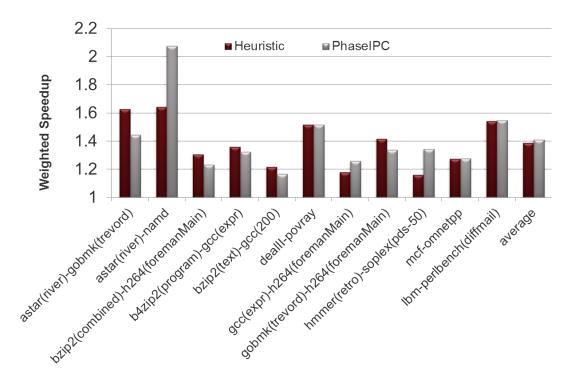

| 4.8  | Weighted speedup from <i>Phase_IPC</i> compared to Kumar's sampling method [42] on a dual-core system                                                   | 65 |

| 4.9  | Weighted speedup of Phase_IPC compared to heuristic method<br>on a dual-core system.                                                                    | 67 |

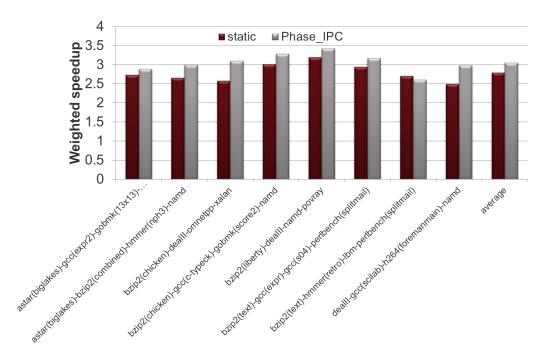

| 4.10 | Weighted speedup of Phase_IPC compared to random static as-<br>signment on a quad-core system                                                           | 68 |

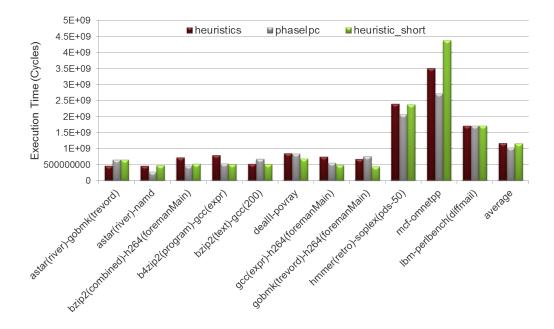

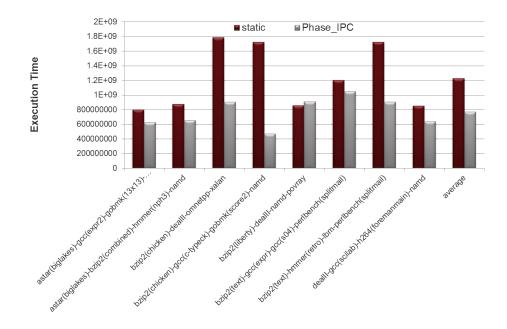

| 4.11 | Execution time of Phase_IPC compared to heuristic method on<br>a quad-core system                                                                             | 69  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.12 | Throughput of Phase_IPC compared to heuristic method on a quad-core system.                                                                                   | 69  |

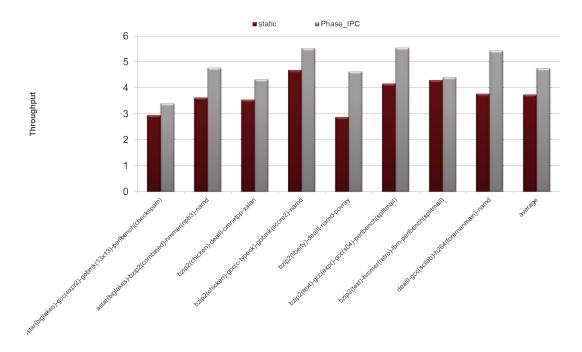

| 4.13 | Flow chart showing <i>Phase_EDP</i> scheduling technique                                                                                                      | 70  |

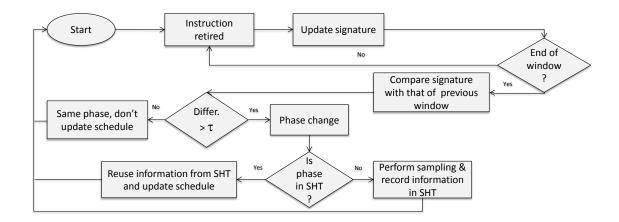

| 4.14 | Energy-delay product for <i>bzip</i> application on an energy efficient<br>in-order core and a less energy efficient, high-performance out-<br>of-order core. | 70  |

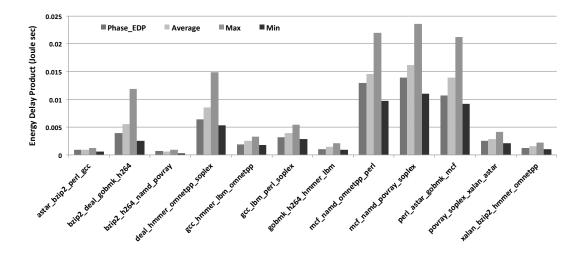

| 4.15 | Energy-delay product for four-tuple of programs (250 million instructions) using different scheduling methods                                                 | 72  |

| 4.16 | Percentage reduction in EDP from <i>Phase_EDP</i> over average of all static assignments.                                                                     | 73  |

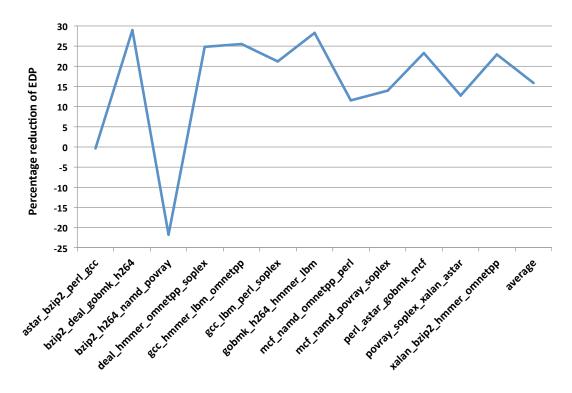

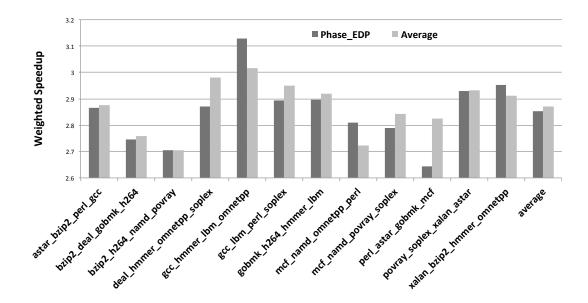

| 4.17 | Weighted speedup of <i>Phase_EDP</i> compared with the average of all static assignments.                                                                     | 74  |

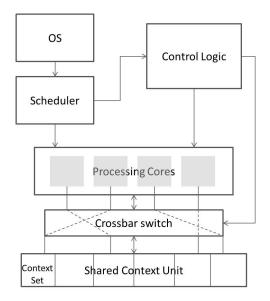

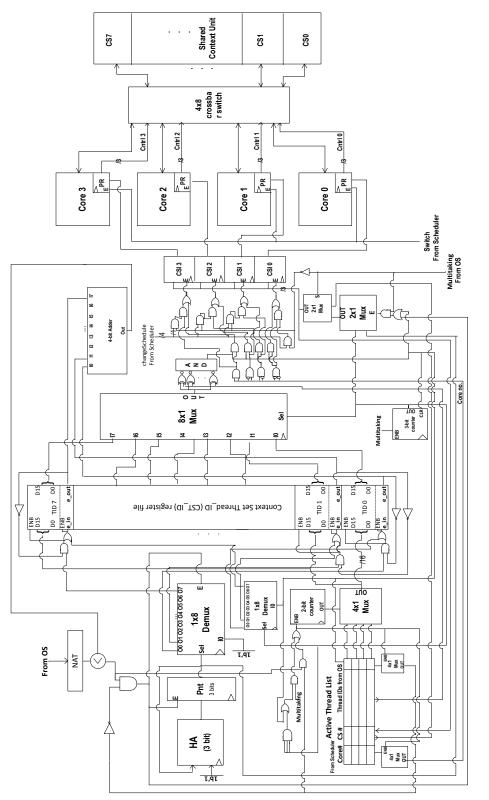

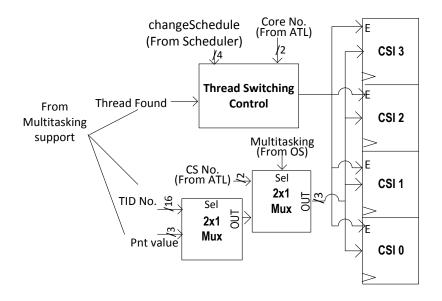

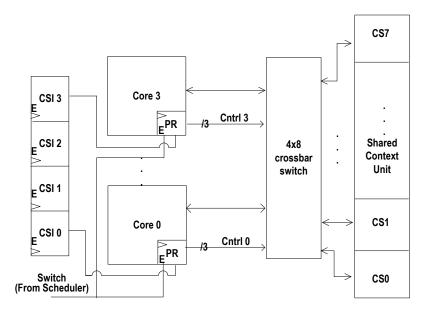

| 5.1  | Block diagram for the context switch circuit                                                                                                                  | 80  |

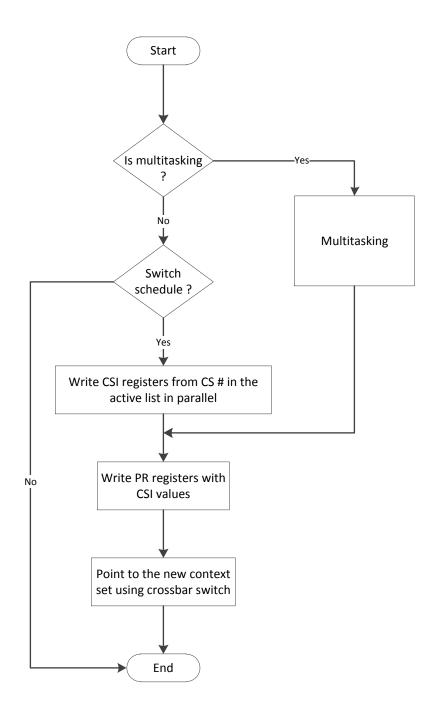

| 5.2  | Thread context switching circuit.                                                                                                                             | 82  |

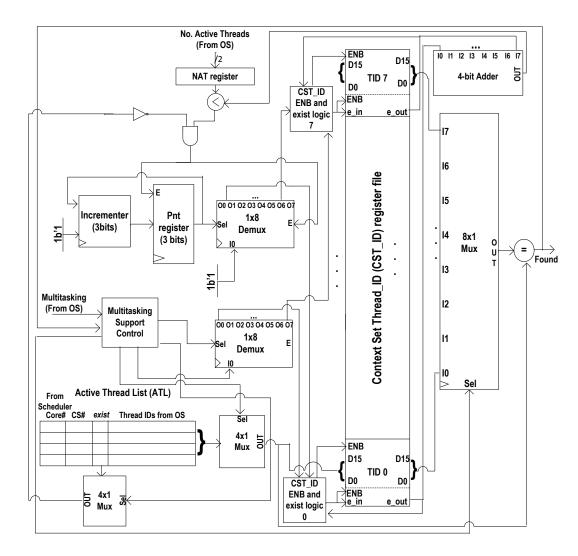

| 5.3  | Hardware context switching flow chart                                                                                                                         | 83  |

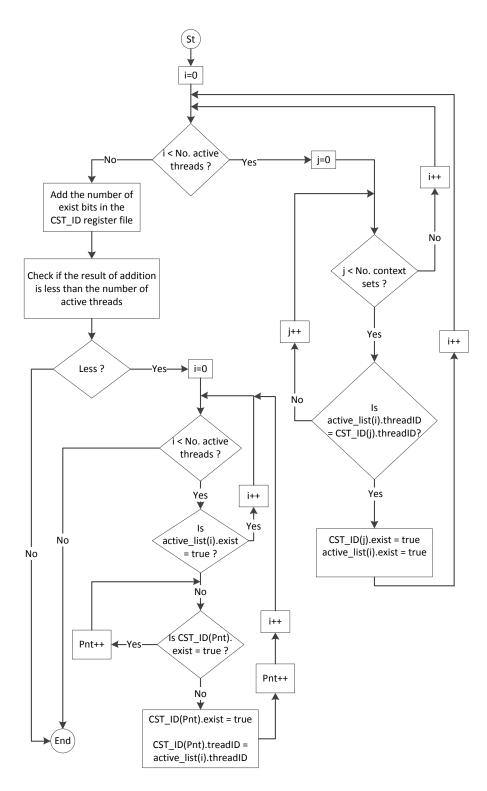

| 5.4  | Components for multitasking support $(n=4, m=8)$                                                                                                              | 86  |

| 5.5  | Hardware context switching Multitasking support step flow chart.                                                                                              | 87  |

| 5.6  | Components for thread switching $(n=4, m=8)$                                                                                                                  | 88  |

| 5.7  | Context set pointer switching components $(n=4, m=8)$                                                                                                         | 89  |

| 5.8  | Slowdown of executed applications due to the direct cost of switching only.                                                                                   | 90  |

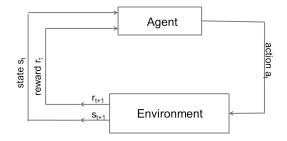

| 6.1  | Reinforcement learning.                                                                                                                                       | 94  |

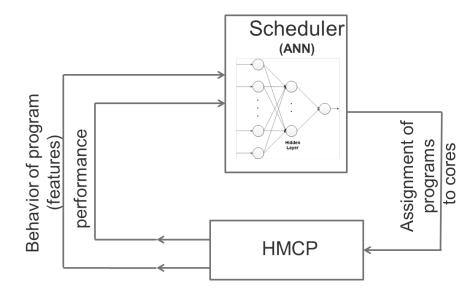

| 6.2  | RL-based HMCP scheduler.                                                                                                                                      | 95  |

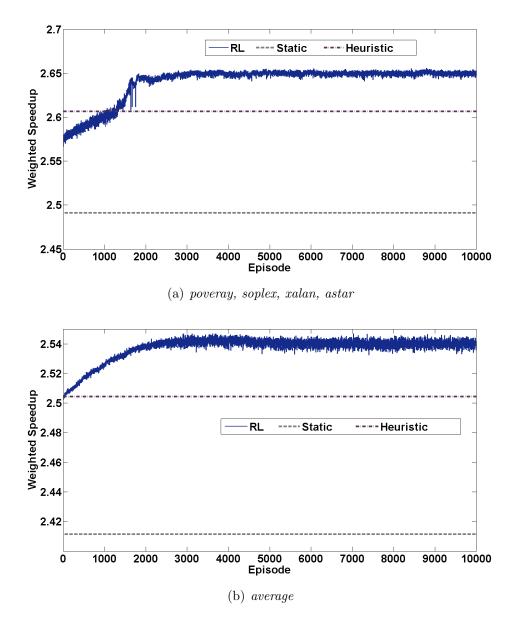

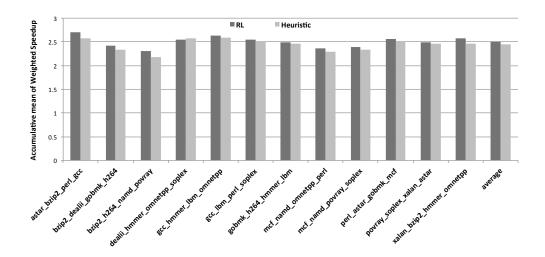

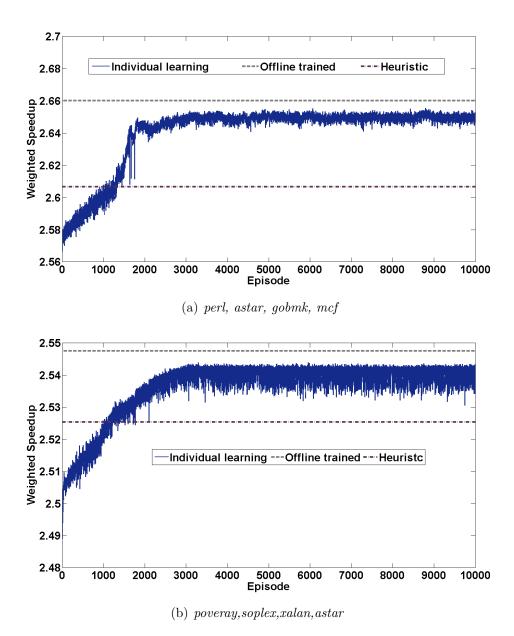

| 6.3  | Full learning curves from quad-core system compared with static and heuristic assignments.                                                                    | 99  |

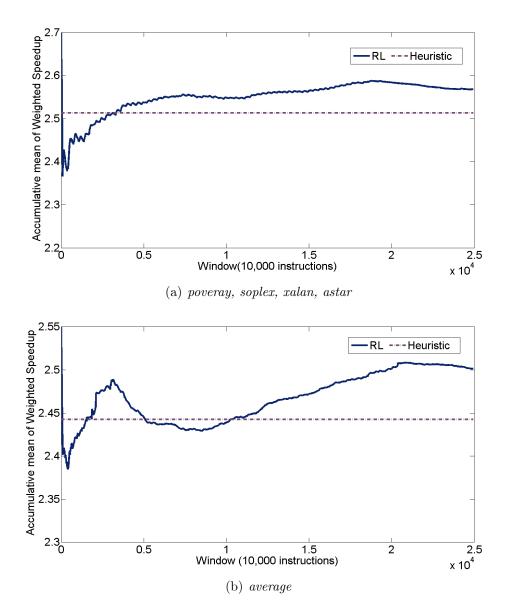

| 6.4  | on-line learning curve from quad-core system compared to heuris-<br>tic assignments.                                                                          | .01 |

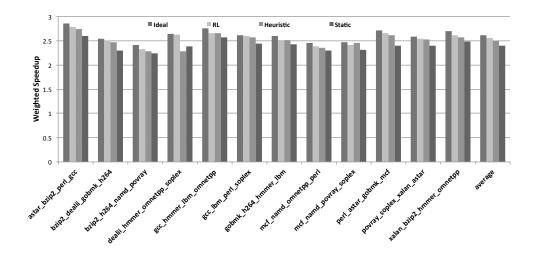

| 6.5  | Comparison between learning, static, and heuristic results in the quad-core system                                                                            | .02 |

| 6.6  | Comparison between on-line learning and heuristic results in the quad-core system                                                                             | .02 |

| 6.7  | Comparison between individual training, off-line trained, and sampling heuristic results in quad-core system                                                  | .04 |

### Abstract

## EXPLOITING HETEROGENEOUS MULTICORE PROCESSORS THROUGH FINE-GRAINED SCHEDULING AND LOW-OVERHEAD THREAD MIGRATION

Lina Hakam Sawalha, PhD The University of Oklahoma, 2012

Supervisors: Ronald D. Barnes Monte P. Tull

Heterogeneous (also known as asymmetric) multicore processors (HMPs) offer significant advantages over homogeneous multicores in terms of both power and performance. Power-efficient cores can be paired with higher-performance cores to achieve advantageous power/performance tradeoffs. Particular cores could also be tailored to efficiently meet the demands of particular application domains. Unfortunately, HMPs also create unique challenges in effective mapping of running processes to cores. The greater the diversity of cores, the more complex this problem becomes. Existing dynamic scheduling approaches for HMPs fall into two categories: sampling and prediction. Sampling approaches permute running applications to across core types to find the best-performing assignment. This sampling step hurts performance and power due to time spent migrating threads through non-optimal assignments. Alternatively, prediction-based approaches estimate the performance for each application on different types of cores and choose the schedule with the best estimated performance. Prediction eliminates the cost of sampling but may result in sub-optimal scheduling decisions. This dissertation introduces new and novel phase-identification-based online schedulers for HMPs that combine aspects of both sampling and prediction approaches by *identifying* phases of execution (instruction sequences with similar behavior), sampling new phases, *recognizing* repeating phases and *reusing* recorded phase information to *predict* the best performing schedule and optimize the schedule for either performance or power consumption. While previous approaches utilized only phase-change *detection* to begin evaluating new schedules, the proposed approaches recognize the current phase of each executing thread and reuse phase information recorded in a Signature History Table when the same or similar behavior of programs reoccurs. This dissertation further proposes machine-learning based schedulers that learns effective scheduling policies using the same characteristics of these program phases.

Exploiting differences between relatively short duration phases using the presented scheduling techniques results in frequent thread migrations that can harm performance. Operating system (OS) context switching can be time consuming. To reduce this context switching overhead, a context switching circuit that both accelerates thread switches among cores in HMPs and reduces switching cost within each core (multitasking) is further introduced in this work. This novel context switch circuit enables low-overhead hardware-level thread migration between cores on a chip and results in up to1380X speedup as compared to an OS context switch. Together with the presented scheduling approaches, this mechanism enables efficient and fine-grained scheduling for HMPs.

## Chapter 1

## Introduction

As microelectronic technology has advanced, transistor sizes have become smaller, and the number of transistors on a chip have increased. This allows computer architects to place more hardware logic on the same chip area. Architects improved processor performance by building deeper pipelines to increase processor frequency, building larger components such as caches and branch predictors to increase the number of instructions per cycle, and exploiting instruction level parallelism (ILP) to increase the number of executed instructions per cycle. Recently, power constraints have limited these increases in frequency to improve performance. Increasing performance by only increasing frequency is infeasible due to the amount of power consumed, heat generated and cooling required to prevent the processor from damage. Achieving higher performance through exploiting ILP almost reached the limit because it depends on the number of independent instructions that can execute simultaneously for each thread or application. With the contemporary limits on higher frequency processors and the small room for improvement that can be achieved by exploiting ILP, computer architects have moved to implementing increasing numbers of processing cores on the same chip to achieve improved system performance. A multicore processor implemented on a single silicon die is also known as chip multiprocessor (CMP). CMPs allow users to run multiple applications in parallel. They also allow multithreaded applications, however, they do nothing to accelerate

the sequential programs or sequential regions of programs.

Most of the currently available CMPs are homogeneous; each processor core is identical to other cores on a chip. Homogeneous multicore processors can be targeted for either single-thread efficiency, or thread-level parallelism (TLP), or specific domain applications. However, future high-performance processors are expected to be heterogeneous with larger number of cores than those currently available [25]. Heterogeneous multicore processors (HMPs) are CMPs that combine different types of processing cores on the same die area. While homogeneous CMPs are easier to design and verify, heterogeneous architectures can be exploited for power efficiency and targeted for performance or domain specific applications. However, HMPs create new challenges for designers and/or programmers in mapping applications to the different types of cores. Because user applications are heterogeneous in natures, they differ in the amount of resources they require, power they consume and performance they result in, heterogeneous multicore processor serves those applications' needs more efficient than homogeneous processors. Moreover, those applications may change their behavior over time. A static assignment that maps applications to core before hand does not adapt to the dynamic workload changes and can result in a decreased performance and increased power consumption. Thus, a dynamic scheduling mechanism is required to adapt to the dynamically changing workloads, and improve system performance and/or reduce power consumption.

This dissertation demonstrates that fine-grained online scheduling techniques with fast thread migration mechanisms can maximize performance and minimize energy consumption for HMPs. The proposed scheduling techniques identify changes in applications behavior to re-evaluate the current schedule. The techniques combine both sampling and prediction approaches to adapt to dynamic changes in workload behaviors and find the best map of threads to the dissimilar cores in HMPs. While frequent sampling (permuting applications on the different types of cores to find the best thread-to-core map) hurts performance, prediction (anticipating the performance for different thread-to-core assignments) may not produce accurate results and may hurt performance. Combining both sampling and prediction approaches can result in better throughput through performance sampling when a new behavior of a thread is encountered and predicting system's throughput of different possible assignments for new and repeating phases. However, fine-granularity scheduling results in frequent thread migrations, which causes performance degradation when performed in software. This dissertation further proposes hardware/software cooperative techniques that reduces the cost of thread migrations.

Processing cores in an HMP contain a mix of two or more general purpose processors, special purpose processors, accelerators and/or programmable logic such as field programmable gate arrays (FPGAs). All cores can either share the same instruction set architecture (ISA), execute subsets of an ISA, or each core (or a set of cores) can execute a different ISA. This work utilizes single-ISA HMPs where all cores execute the same ISA, but can be applied for other types of HMPs as well. Single-ISA heterogeneous systems lack the specialization of the instruction set that could be found in a general heterogeneous system, but maximize the flexibility in scheduling or mapping computation to processors. In such systems, any processing core may run any application thread. However, not all cores provide equal levels of performance or efficiency.

### 1.1 Motivation and Challenges for Heterogeneous Multicore Processors

According to Moore's Law [51, 68], the number of transistors on an integrated circuit doubles every two years as the size of transistors becomes smaller. Exploiting this, computer architects make use of the extra transistors on a chip to improve systems' throughput by: increasing the frequency( by exploiting deeper pipelines), improving the number of instructions executed per cycle (through enhanced branch predictors, caches, instruction dispatch and the number of execution units) and building more processing cores on a chip. With multiple cores, users can run more applications or threads in parallel, which leads to an increased system's performance. HMPs can further increase the performance of a system by serving a wider range of applications more efficiently than homogeneous CMPs. Heterogeneous multicore processors can efficiently execute both single-threaded applications and parallel (TLP) applications. HMPs can HMP can be built to target some domain specific applications.

The number of applications that support multiple threads is increasing. Thus, the ability to handle multiple parallel threads is crucial for high performance processors. Designers aim for a large number of cores to support the execution of a large number of parallel threads. Numerous simple, powerefficient cores are more desirable than a few high performance cores in this case. While executing multiple parallel threads is crucial for parallelizable program pieces, handling the serial part of program is vital for the overall system performance [32]. Amdal's Law [3,32] states that the speedup of a program using multiple processors in parallel is limited by the time needed for the execution of sequential fractions of the program. Hence, a high-performance core is desired for the serial part of a program. For these reasons, a heterogeneous mix of cores are being considered.

With heterogeneous cores, a processor can have more processing cores compared to a homogeneous processor, which contains high single-thread performance cores, occupying the same area [42]. For instance, a small in-order core occupies less area than a big powerful superscalar out-of-order core. Having more processing cores allow the system to execute more threads in parallel and service interrupts simultaneously. In HMPs, dissimilar types of cores result in different performance for any given application. In addition, a typical application's behavior changes over time, thus transitioning through distinct program phases [44]. Each phase of execution has different characteristics that may lead to a different behavior of the application or thread. These characteristics include the type and number of executed instructions, the degree of instruction-level parallelism and the utilization of available resources. Thus, each phase of a thread may result in different throughput. For example, a program phase that contains many memory accesses with last-level-cache misses may perform much better running on an out-of-order processor core than on an in-order core, due to the out-of-order core's ability to better tolerate long, variable latencies.

#### 1.1.1 Challenges of Designing Heterogeneous Multicore Processors

In addition to the increased core design and verification complexity, there are several challenges in designing HMPs–based system. Some of the challenges include: efficiently scheduling threads to the different processing cores, switching threads among cores, memory design and managing core interconnection overheads.

#### Scheduling Tasks on Heterogeneous Multicore Processors

Effective scheduling of threads on HMPs can be a more difficult problem than scheduling for homogeneous multicores, because of the difference between the processing cores. These differences can include the microarchitecture, numbers and types of execution units, sizes of execution units, sizes of local caches, types and sizes of branch predictors, ISA, etc. An efficient scheduling algorithm maps threads to cores by taking into consideration the characteristics, behavior and relative performance of applications while executing on cores of the various types, and matching them to the relevant characteristics of the cores.

Moreover, applications change their behavior over time, such that some execution phases may have different behavior characteristics and performs better on a different core type. A thread might achieve the best performance when running on one core for some phases, and running on another core for some other phases. While static scheduling approaches (offline thread-to-core assignments) provide a fixed assignment of applications to cores before execution and avoid thread migrations, dynamic schedulers are capable of reassigning threads online to adapt to the dynamic changes in workload behavior. A dynamic scheduler can benefit from the heterogeneity in the system to increase applications performance and/or reduce their energy consumption.

#### Thread Migration

The operating system (OS) typically is responsible for switching the contexts of running threads. With time-multiplexing between threads, the CPU saves the context of the old thread and launches another thread. Similarly, when a thread requests an IO (e.g. data from disk), the CPU does not wait for the request to be served (reading to finish). Instead, it switches to another thread, and when the first thread finishes reading, the CPU is interrupted with the result of the read. In HMPs, the same need for operating system context switches obviously exists. However unless a single, fixed core assignment is used, the CPU needs to be able to switch a thread among its cores depending on the thread's relative characteristics and behavior in the current phase of execution. The overhead and extensive computations associated with context switching in software limits the number of switches per second for a CPU. Thus, enabling more frequent or fine-grained thread reassignments in HMPs requires a faster thread migration mechanism among cores.

#### **1.2** Dissertation Motivation

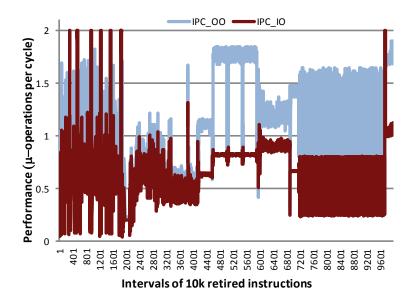

As an example of the varying behavior of a program, figure 1.1 shows the number of executed instructions per cycle (IPC) over a short interval of 10,000 instructions of an application, bzip2, run on both in-order and out-of-order cores. Figure 1.1 demonstrates that the behavior of bzip2 varies over relatively short intervals of execution. For most intervals, the performance of the application running on the out-of-order core is better than the performance of the same instruction interval running on the in-order core. This is not surprising as the out-of-order processor is able to dynamically exploit available instruction-level and memory-level parallelism by selecting instruction execution in an order other than program order. However, the opposite is true for other intervals. As can be more clearly seen in Figure 1.2, the in-order core actually outperforms the out-of-order core for some intervals, due to its shorter pipeline, larger cache and increased instruction issue width.

Figure 1.1: IPC of an in-order core and an out-of-order core, for *bzip2* application.

In general, to maximize throughput by benefiting from the heterogeneity in a system, an effective on-line scheduling technique that reassigns threadsto-cores dynamically is required to adapt to the dynamic changes in workload behavior [66, 67]. The dynamic scheduler is responsible for evaluating threadto-core assignments over time and changing the schedule to improve performance and/or reduce energy consumption. One way to adapt to the dynamic changes in workload is to detect relatively short changes in program behavior and re-assign jobs to cores on the fly. This work represents an adaptive online scheduler for HMPs, which detects fine-grained changes in programs' behavior

Figure 1.2: The ratio of IPC of an in-order core over an out-of-order core, for bzip2 application.

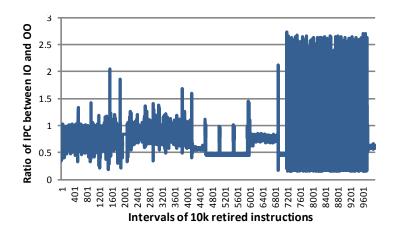

Figure 1.3: The performance of applications on a quad core processor using different scheduling granularity.

and efficiently reassigns threads to the different cores on a chip whenever a change in a program's behavior or a new phase of execution is detected. The scheduler keeps track of active threads behavior (or phases of execution) and their performance or best assignment, recognizes recurring phases and reuses the recorded information to predict the best map of threads to the cores.

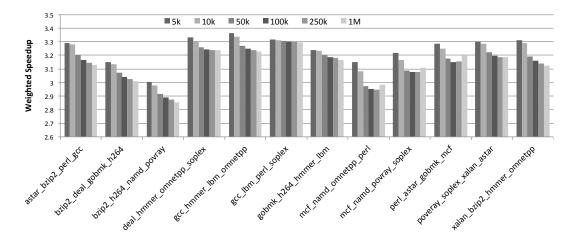

Figure 1.3 shows the results of executing four-tuple applications on a

quad-core processor with different sizes for windows of executed instructions, over which execution phases are detected. The figure demonstrates that, with ignoring context switching overhead, exploiting shorter changes in program behavior can result in an improved performance. However, fine-grained scheduling yields a large number of thread switches among the heterogeneous cores. Frequent thread migrations hurt performance. Thus, to support fine-grained scheduling and to overcome the overhead of thread migration, a faster context switching is required.

#### **1.3** Dissertation Contributions

This dissertation makes the following contributions:

- It analyzes the different design options of HMPs as well as industry trends for building HMPs, and it proposes different designs for single-ISA HMPs.

- It proposes online scheduling algorithms that adapt to fine-grained changes in programs' behavior to benefit from the asymmetry in the design to maximize performance and minimize energy consumption. The scheduling algorithms combine both sampling and prediction approaches to produce more accurate decisions for both performance and energy consumption.

- It introduces a machine learning technique to make the schedule intelligently learn when to switch to a different assignment to maximize performance.

- It demonstrates that the finer the granularity of scheduling, the higher the performance of HMPs can be–ignoring the cost of context switching.

It also analyzes both the direct cost and indirect cost of thread migrations between the cores on a chip.

• It proposes a hardware switching circuit that drastically reduces the direct cost of context switching, the cost of copying the processor state.

#### **1.4** Dissertation Organization

This dissertation is organized as follows: Chapter 2 provides background information and related work. Chapter 3 shows the design, simulation and evaluation parameters used through all the dissertation. Chapter 4 introduces different scheduling approaches for HMPs. Those approaches are applied to scheduling for both performance and energy consumption. The chapter also provides comparisons between my scheduling approaches and other methods. Chapter 5 analyzes the overhead of context switching and provides solutions for the direct cost of thread migration. Chapter 6 proposes a reinforcement learning-based scheduling for many-core processors. Finally, Chapter 7 concludes the dissertation and provides future work.

## Chapter 2

### Background

In the history of computing, there has been three main computing domains: high-performance computing domain, personal computing domain and embedded computing domain. The high performance computing domain concerns with multi-threaded and multiprogram applications throughput. It serve multiprogram and multithreaded applications through server systems. The personal computing domain concerns with single-application performance. The demand of personal applications performance was at the beginning through personal desktop computers. The embedded computing domain concerns mainly with power-consumption and serving real-time applications. There are several embedded systems that serve the demand of reduced power consumption, such as cell-phones, tablets, aircraft controllers, etc.

Furthermore, there has been many applications and devices that lie in the intersection of some of these domains such as personal laptops. When laptops first came to the market, they were designed to serve both demands of single-application performance and low-power consumption. Recently, there is a convergence in computer architecture such that many applications and devices requires a sufficient service level for the three demands. For example, most of the mobile devices today such as laptops, tablets, notebooks and cell phones contain multi-core processors to serve more than one application and at the same time single-application performance is important. In addition, battery life in mobile devices is a vital issue, thus these processors are designed to consume less power than processor designed for other applications.

#### 2.1 Multicore Processors

The first microprocessor, Intel 4004 [2], was introduced in 1971. It consisted of only 2300 transistors and operated at 784KHz. Since then, the number of transistors that microprocessors' manufacturers are capable of fabricating on a chip has doubled roughly every 18 months, closely following Gordor Moore's famous observation [51]. Computer architects has used the increased number of transistors to improve performance by increasing parallelism through additional components on chip and increasing frequency through ever-deeper pipelines. The frequency of current processors has reached the GHz scale. However, significantly improving the performance of monolithic processors by increasing frequency is no longer an option for a cost-effective design because of power and thermal limitations. The dynamic increasing the frequency of a processor increases the dynamic power dissipation linearly as shown from Equation 2.1 below:

$$P = ACV^2F \tag{2.1}$$

where P is the dynamic dissipated power, V is the voltage, F is the operating frequency and A is the activity factor. However, frequency is also closely related to operating voltage making the relationship super linear. More dissipated power yields more generated heat; this often means that more expensive heat dissipation methods are required. Moreover, improving performance through extracting instruction-level parallelism (ILP) has reached diminishing returns. Dynamically finding this parallelism requires power-hungry support and requires larger numbers of independent instructions that are often not available in typical programs. In addition, exploiting increased ILP increases the verification complexity and cost. For all these reasons, designers have moved to more power-aware and complexity-aware approaches to computing.

To benefit from the increased number of transistors on a chip to improve performance, architects have added more cores on a chip, which is known as chip multiprocessors (CMPs). CMPs improve the system performance by allowing multiple applications or threads to run on parallel. Instead of looking for concurrency at the instruction-level, multicore processors looks for concurrency at a coarser granularity-thread-level parallelism (TLP). Multi-threaded applications execute threads on different cores and communicate with each other through message passing or shared memory. In addition, parallelizing applications is often a complicated work for some programmers. In a more straightforward fashion, multicore processors can exploit a coarser granularity than TLP at the application level parallelism. Multicore processors can execute more than one application simultaneously, known as multi-programmed workload. Multicore processors can be either homogeneous processors where all cores on a chip are the same, or heterogeneous where some cores on a chip are designed differently than others. Most of the available multicore processors are homogeneous containing multiple symmetric processing cores.

#### 2.1.1 Homogeneous Multicore Processors

Multicore processors can be classified depending on their applications domain, power/performance, memory model and architecture design [10]. With contemporary power limitations, power/performance tradeoffs are becoming the main processor design concern. Although there has been convergence in computer architecture, most multicore processors lie on two points in the power/performance range: energy-efficient processors and high-performance processors.

#### Energy-Efficient Homogeneous Processors

Typical power-efficient processors are composed of small identical cores, usually with in-order execution model, or small, power-efficient out-of-order execution model. In in-order processors, the pipeline executes instructions in program order. Out-of-order execution model reorder instructions and execute them out of their program order to increase the number of instructions executed per cycle, while preserving the dependency order or between instructions. Powerefficient homogeneous processors can be further classified to either low-latency or high-throughput processors.

For applications where processor's power-consumption is very important such as mobile devices, few power-efficient low latency cores are used. However, in mobile devices, along with power consumption, applications performance is also important. Combining both demands, power-efficient with relatively low-latency processors are desired for real-time and mobile applications. For instance, ARM's cortex A9 MPCore processor can contain up to four symmetric cores on a chip. Each processing core contains an out-of-order eight-stage pipeline [4]. Cortex A9 provides relatively low-latency (or hight-performance) in low-power constraint devices such as smart phones, digital TVs, etc.

The second type of power-efficient homogeneous processors is the highthroughput processors where the system throughput is the main concern. In parallel computing, many processing cores are desired for multithreaded applications to execute many threads simultaneously. Small, power-efficient processing cores occupy less area than larger aggressive cores, hence more cores can be fabricated on a single chip than larger cores. In addition, small power efficient cores consume less power and require less sophisticated cooling than larger aggressive cores. Because of their small area and reduced energy consumption, those power-efficient cores are desired for parallel applications where single-thread throughput is not as important as the whole system throughput. In this case, more executing threads results in an increased throughput even if the single-thread performance is lower than that of a higher performance processor. This type of processor usually contain several small in-order cores to support a large number of threads with low power consumption.

An example of the high-throughput power-efficient processors is Intel's single-chip cloud computer (SCC) [1]. The SCC is a research chip that Intel built to study many-core CPUs. The SCC consists of 48 cores, where each couple of cores form a tile. Each core is based on a simple, in-order processor. The SCC tiles are connected using a 6x4 synchronous mesh fabric [33]. The chip has multiple voltage and frequency domains and can be dynamically targeted for fine-grain power and performance management.

A group of researchers in MIT developed the Raw processor [83]. It is made up of a set of programmable tiles that are connected through a tightly integrated programmable interconnects. Each tile contains an in-order pipeline, and private data and instruction memories. The Raw processor is mainly targeted for parallel and multimedia applications, and it allows for custom operations. This domain-specific application processor supports several multimedia applications or threads at the simultaneously while the over-all system throughput is the main concern.

One of Sun's multicore processors is the UltraSPARC T-1 [39]. This processor consists of eight simple in-order four-way simultaneous multithreaded cores. The T-1 is targeted at multithreaded applications. Thus, up to 32 threads can execute simultaneously on the processor. UltraSPARC T-1 may result in a lower single-thread performance than high-performance processors, but it increases system throughput by supporting the execution of many threads simultaneously. This processor is suitable for servers that does not require huge amount of computations such as web servers.

#### High-Performance Homogeneous Processors

Unlike the power-efficient processors described above, high-performance multicore processors are typically composed of a few larger aggressive superscaler cores with out-of-order execution model than the power-efficient cores. This type of processors aim for the highest performance of single-thread applications. This type of processor can be targeted for a very high-performance applications.

Intel has recently produced the latest in a series of multicore processors. Core i7 is an Intel's quad core processor with hyper threading (HT) technology, Intel's version of simultaneous multithreading. With HT, two threads can execute simultaneously on each core. The highest end version of the i7 has six cores and is capable of handling 12 threads simultaneously. Because Core i7 is designed for servers and desktops, it results in high performance for individual threads. However, it contains fewer cores and less multithreading support, and is much less power efficient than small power-efficient cores such as the UltraSpace T-1 and T-2.

#### 2.1.2 Heterogeneous Multicore Processors

A heterogeneous multicore architecture is one system design approach to meeting user's expectations of increased software capabilities and performance even in the presence of tight power constraints. By balancing specialization, singlethread performance and efficient parallel multiprocessing, such systems have the potential to outperform homogeneous architectures while at the same time providing a more power-efficient solution.

When designing a heterogeneous multiprocessor system, the choice of the different sets of processor cores is crucial for power, performance and programmability. Some processor cores may produce higher single-thread performance but require significantly more power or greater chip area. Cores may have different number of execution units, support varying degrees of out-oforder execution, have a different type/size of branch predictors, and feature a different size of private caches. The power consumption and die area requirements of each core play important roles in choosing the cores in a heterogeneous multicore processor.

Heterogeneous multicore systems can either be composed of processing cores that execute specialized instruction sets for a particular domain, or they can execute the same instruction set but feature heterogeneity in the types of characteristics mentioned above. Today, most heterogeneous systems follow the former approach. For example, IBM's Cell Broadband Engine [31] is a heterogeneous multicore processor targeted for specific applications related to streaming media and similar scientific applications. The Cell processor is composed of one Power Processing Element (PPE), and eight Synergetic Processing Elements (SPEs). The PPE is a two-way multithreaded general purpose core, which handles most of the control and coordination and acts as the controller for the eight SPEs. The PPE is similar to a 64-bit PowerPC (PPC) RISC processor. The SPEs are single-instruction multiple-data (SIMD) vector processors with instruction sets focused on SIMD vector instructions, similar to the SIMD vector instructions on the PowerPC. By combining one general purpose core with 8 small but computationally powerful cores, the Cell is an efficient and high performance processor for the multimedia application domain. Similarly, multicore architectures [13] that combine general purpose processing units with specialized graphics processing units (GPUs) offer the exciting promise of exploiting GPU SIMD hardware for accelerating computation.

However, partitioning computation between disparate cores with different ISAs is a challenging task, and one that must be done at software development level. Performing this partitioning automatically can be extremely difficult. In one approach to partitioning Cell applications, Blagojevic et al. [9] introduced a model of multigrain parallelism (MMGD) for parallelizing tasks on heterogeneous parallel architectures. They utilized a phased hierarchical task graph (HTG) to partition applications into multiple phases of execution and split these phases into nested sub-phases and evaluated their technique on a Cell Broadband Engine consisting of two PPEs (host processor unit) and 16 SPEs (accelerator processor unit). While approaches like this one for mapping application code to heterogeneous architectures are promising, multi-ISA heterogeneous architectures make it difficult, if not impossible, to dynamically partition application threads using run-time information.

Recently, ARM introduced a heterogeneous multicore processor named big.LITTLE [30]. This processor combines both a large superscalar processor (ARM Cortex-A15) for high performance, and a small in-order processor (Cortex-A7) for energy efficiency that both execute the same instruction set architecture. Two different implementations for this big.LITTLE processor exists. In one implementation, only one core is powered on at a time and the other is turned off. For this implementation, applications switch transparently between the two cores; they switch to Coretex-A7 to reduce power consumption, or to Cortex-A15 for increased performance. In the second implementation, both cores are switched on if there are more than one application running. Applications are statically mapped to their best fit core beforehand. While static mapping can prevent thread switching between the two cores, my dynamic scheduling techniques with the low-switching overhead described in this dissertation would work efficiently for this big.LITTLE processor and adapt to the dynamic changes of applications' behaviors.

Pericas et al. [57] proposed a flexible heterogeneous multicore processor (FMC). The FMC allows changing instruction window size at runtime based on an execution locality concept. Rather than allocating a single core for each thread, FMC allows threads to use as many resources as they need from a pool of available cores.

#### 2.2 Scheduling Applications to Cores

Heterogeneity significantly increases the complexity of scheduling the different types of applications on the dissimilar cores. Additionally, applications changes their behavior over time and adapting to these dynamic changes in applications' behaviors makes scheduling even more complicated. There has been several work on scheduling for heterogeneous systems, such as heterogeneous multiprocessor systems [29,55] and distributed systems [5,6]. However, scheduling for a single-chip heterogeneous multicore processor is different than these larger systems because multiprocessors and distributed systems consist of physically separated node locations. The time that is taken to migrate a task from one processor node to another differs widely depending on the distance between the two nodes. Distributed scheduling algorithms need also to account for recovery from node failures and relocation.

To adapt to the dynamic workload and the different execution phases of applications within a heterogeneous multicore processor requires dynamic reassignment of threads or applications to cores. There are many previous works that present scheduling algorithms for heterogeneous multicore processors. Each of these scheduling techniques can be classified as: static (off-line) scheduling, static/dynamic scheduling and dynamic (on-line) scheduling techniques.

#### 2.2.1 Static (Off-line) Scheduling Techniques

In static scheduling approaches the processing core to which each application will be mapped is decided prior to execution based on certain characteristics of applications. Most HMP off-line schedulers rely on previous analysis of benchmarks characteristics. In one such approach, after off-line profiling of microarchitectural independent characteristics, a signature is composed for each application representing the resources required by that application [69]. These architectural signatures are inserted into the executable binaries of applications' headers. The heterogeneity-aware signature-supported (HASS) scheduler uses those signatures to estimate the performance of entire applications on the different core types within an HMP, and maps applications to their highestperforming core. This approach was evaluated on symmetric cores operating under different frequencies using dynamic voltage frequency scaling (DVFS), and did not consider different types of architectures.

Chen and John [16] proposed another static scheduling algorithm that matches cores to programs. Similar to HASS, the scheduling software analyzes program characteristics and the hardware configurations of each core. The scheduler then matches runtime programs to cores depending on the characteristics of the program, resource demands, and the physical characteristics of cores. This algorithm looks at the inter-program diversity and does not adapt to dynamic changes in workloads.

#### 2.2.2 Static/Dynamic Scheduling Techniques

Static/dynamic schedulers combine both off-line analysis of applications and on-line rescheduling of jobs to the processing cores. In one static/dynamic approach, an offline program phase detection and marking were employed in HMP scheduling [74]. Phase marker code fragments were instrumented at statically detected phase transition points in application executable binaries. These markers perform dynamic performance analysis of these phases and handle threads' reassignment. Similarly, Cong and Yuan [20] uses static analysis to determine loops and function boundaries to determine program phases, and optimizes the scheduler assignments for reduced energy-delay product (EDP). Instrumentation functions are inserted in the executable binaries of programs at the boundaries of loops and functions. The instrumentation functions are responsible for measuring the call time and number of instructions for each loop and function call. A call graph is constructed from the detected loops and functions, and then major program phases are identified. To overcome the loss of performance due to thread migrations from one core to another, thresholds are used for the number of instructions and invocations. At runtime, when an instrumented code is reached, the EDP is predicted on both core types using regression model, and the scheduler predicts the lowest EDP schedule.

The aforementioned approaches require offline analysis of program behavior. While the scheduling approaches presented in this dissertation exploit the phase behavior of programs, they utilize a dynamic detection and identification of program phases that does not require special modification of code to be executed. Rather than relying on application code to make scheduling decisions as in [74], these techniques perform scheduling on a system-wide basis in a way that is transparent to the running applications.

Chen and John [15] proposed an energy-efficient scheduling mechanism for heterogeneous multicore processors. Instruction-level parallelism, branchtransition rate and data dependency distance characteristics are chosen to measure the suitability of cores issue width, branch predictor size and L1 cache size respectively. Programs are analyzed off-line for these three characteristic. Fuzzy logic was used to combine the individual suitabilities, determine an overall suitability that indicates a degree to find the best program-to-core map. This approach requires previous analysis of programs and is not adaptable to new applications.

#### 2.2.3 Dynamic (On-line) Scheduling Techniques

Dynamic schedulers are capable of changing job-to-core assignments on the fly without the need for off-line analysis or profiling. In this way, they can adapt to dynamic changes in program behaviors without prior profiling or analysis of applications. In a heterogeneous multicore processors, dynamic schedulers have increased potential to improve the system throughput through on-line rescheduling by adapting to both changes in programs behavior and need of resources. Dynamic scheduling techniques can be classified as: sampling, prediction and sampling/prediction techniques.

#### Sampling-Based Scheduling Techniques

Kumar et al. [42] designed a sampling-based heuristic scheduling approach for assigning jobs to cores dynamically. Like this work, they focused on single-ISA heterogeneous multicore architectures in which cores can vary in performance and power consumption but not in ISA. Their scheduling algorithm is divided into two different phases, a sampling step and a steady step. In the sampling step, all of the possible assignments of jobs to cores are examined and a weighted speedup is recorded for each assignment. In their evaluation, each assignment is run for two million cycles. Then the assignment with the best weighted speedup was chosen as the schedule for the steady step. Calculating the weighted speedup for this method requires before-hand knowledge of the performance of each application executed along on the system. Becchi and Crowley [7] proposed a similar approach called IPC-driven, in which an IPC ratio between a fast core and a slow core is presented as a more practical evaluation criteria. In either approach, whenever an execution phase change is detected or a certain number of cycles elapsed, the dynamic scheduler begins a new sampling phase. Note, that while both studies utilize a simple mechanism to detect when a phase change occurs, they do not seek to identify the particular phases. This distinction with the study in this dissertation is further clarified in Chapter 4.

A limitation of Kumar's scheduling algorithm [42] is its inefficiency in estimating the performance of particular mappings. The scheduler must examine all the possible assignments before it chooses the best assignment and enters the steady step. For a small number of cores and core types, this may be feasible but the number of possible mappings grows factorially with the number of unique core types. It also grows linearly with the number of total cores for fixed number of asymmetric core types. Thus, with a larger number of permutations only some of the possible assignments can be attempted. Furthermore, a significant amount of time is spent in the sampling phase, most of which is spent with a sub-optimal thread-to-core assignment. This can significantly hurt performance. The sampling approaches use coarse grain changes in program behavior, however, performance sampling can happen during fine grain changes in program behavior or during different sampling intervals, thereby misleading the scheduler decision. For instance, if a thread transits through a short phase that contains several last-level cache misses during one sampling interval and then for the next sampling interval the application transits through a phase with high instruction-level parallelism (ILP) the performance is different for both phases even on the same core types. This may cause the scheduler to choose a suboptimal assignment.

A scheduling algorithm called hierarchical hungarian was proposed for

many-core HMPs is proposed [85]. The cores in a processor are divided into clusters and the hungarian algorithm is applied for each cluster. Sampling is used to get performance information of each application on the different core types.

#### Prediction-Based Scheduling Techniques

The prediction-based scheduling approach relies on predicting the performance of threads on different core types, and/or predicting the assignment of threads on the different core types. In a related approach, Jooya et al. [37] introduced the history-aware, resource dynamic (HARD) scheduler for heterogeneous chip multiprocessors. The HARD scheduler performs reassignment of jobs to cores when an application phase change occurs by "upgrading" or "downgrading" job assignment to a higher-performance or more power-efficient core, respectively. Like Kumar's technique, the HARD scheduling approach relies on a change in an application's performance (in this case throughput and core utilization) to detect a change in a program phase. While HARD avoids permuting applications amongst different types of cores, it relies upon a strict performance ordering for processor core types. This may not always be the case, as some cores may have better performance for certain application domains.

Other scheduling algorithms exploit off-chip performance, such as memory accesses, to detect changes in programs behaviors [40,60]. Such algorithms do not account for the differences in the architecture such as the execution units, pipeline, etc. [60]. In one approach, Koufaty et al. [40] correlates an application's behavior with internal (on-chip) and external (off-chip) stalls. They estimate a bias for each application using performance counters that keep track of the external stalls. The algorithm uses overlapping windows of instructions to calculate a running average of each of the metrics. The bias of an application changes if the amount of stalls goes over or below a certain threshold. This algorithm can be implemented with any type of operating system scheduler without changing the properties of the scheduler such as responsiveness and fairness. However, it periodically checks the load balance of the system and migrates the thread with the highest bias to a "big" core. Saez et al modified the HASS scheduler (discussed in Section 2.2.1) to dynamically assign threads to cores by detecting program phases [61]. Similarly, the last-level cache miss rate is used to estimate a speedup factor. Initially, the speedup factor is assigned to a default value and after that it is calculated using the profiled information of last-level cache misses. The scheduler detects coarse-grain program phases and updates the speedup factor before making a decision.

Some scheduling algorithms for HMPs are concerned with multithreaded applications performance [12, 43]. In the age-based scheduling technique [43], the length of threads are predicted, using history of previous instances of code for predicting the next barrier or end of thread. The threads with the longest estimated run time are scheduled to run on the fastest cores. This scheduling technique improves the throughput of parallel applications by overcoming the barrier bottleneck through accelerating the longest thread. However, for single-threaded applications workloads, this approach acts the same as static approaches. Instead of measuring thread length, Poovey et al [12] measured thread complexity through analyzing dependance chain. The scheduler evaluates the current assignment every 100 ms and resets the dependence chain.

A dynamic scheduling approach for assigning threads in an HMP that

includes a central processing units (CPUs) and a graphical processing unit (GPU) was performed [46]. In [46], a dynamic compilation of programs to native machine codes is performed at run time to adapt to changes in the environment. The scheduler, Qilin, uses an empirical method to map computations to cores. The first time a program runs on Qilin, it is considered a training run. The input of the program is divided in two parts: one part runs on the GPU and the other part run on the CPUs. The execution-time projections are kept in a database, such that when the same program run again with different input size, the execution-time projection stored in the database are used to determine the mapping of computations to the processing cores. The algorithm attempts to find the fraction of work to run on CPU to minimize execution time. This method focuses on multimedia and parallel applications and assumes that programs are repeated before their information are forced out of the database.

The above prediction-based scheduling techniques rely on performance estimation. Another way to predict threads-to-cores map is to learn over time the best assignment that results in the best throughput when encountering certain features of programs [26,87].

## Prediction/Sampling Based Scheduling Techniques

Prediction/sampling scheduling approach combines both prediction and sampling techniques to improve the performance of the system. While sampling alone hurts performance when performed frequently, prediction may result in sub-optimal assignments. Thus, combining both prediction and sampling improves system throughput, by sampling when new behaviors of programs are

detected and predicting when similar behavior are encountered again. This type of scheduling techniques is used in this dissertation for scheduling on heterogeneous multicore processors because of its accuracy and reduced sampling cost. Wu et al. [86] proposes a hardware/software co-designed heterogeneous multicore processor that contains narrow out-of-order (OoO) with x86 ISA and wide in-order (IO) very long instruction window (VLIW) virtual machine. The code is dynamically translated from x86 to the VLIW machine. When the code is running on OoO core, there is no need for dynamic translation and it executes native machine code. Dynamic profiling is performed, and when one or more hot spots are detected the code is dynamically translated and optimized for the IO core. Two predictors are used to predict continuing on the same core and to predict switching to the other core in case of sampling. The first predictor compares data collected on both core types to decide whether to stay on the same core or not. Continuation is allowed for only K continuous times and then sampling is forced. If the scheduler predicts not to continue on the same core, the other core is activated and sampling is performed for a short interval to collect information. Based on the collected information the scheduler decides whether to stay or switch again to the first core.

# 2.3 Context Switching

Scheduling jobs on heterogeneous multicore processors requires switching among the different cores on chip frequently to benefit from the heterogeneity. Context switching is the process of saving the central processing unit (CPU) state (context) and restoring it when switching to another process. The conventional mechanism for this migration is through software context switching. The context of a CPU consists of a process control block (PCB), which includes the state of the process, CPU registers and information about memory management. Context switching is time consuming and depends on the objects to be switched–register, thread or process switching. It also depends on the size of data to be copied, which in turn depends on the behavior of the running program.

The OS is typically responsible for switching tasks to allow several threads to share the CPU (time-multiplexing) and to be able to switch the CPU to another thread when there is an interrupt or the current thread requests to use an IO device. On the other hand, some processors (including modern Intel x86 processors) have hardware support for context switching, by saving the processor state in a system data structure called the task state segment (TSS). The TSS consists of two types of fields: dynamic fields and static fields. The dynamic fields include the general purpose registers and the segment selector, while the static fields contain local descriptor table (LDT), CR3 control register, stack pointers and I/O map address [35]. The TSS is intended to automate switching between programs. However, it restricts how OS programmers can configure context switching. Instead of taking advantage of the TSS, many x86 OSs use their own context switching mechanism. For instance, Linux does not use the TSS feature. Instead, it simply creates only one TSS for each processor and modifies it for each process. However, Linux does use the static fields of Intel's TSS such as the control register CR3 while switching tasks.

There are two types of context switching overhead: direct cost and indirect cost [45]. The direct cost includes the time copying the context of the

CPU, such as CPU registers and TLB, and flushing the processors pipeline in which the switched thread is running. The direct cost can be measured using Ousterhout's method by forking a child process and sending a message forth and back between the parent and the child processes, using two pipes, periodically [56]. McVoy and Staelin improved Ousterhout's technique by eliminating system call overhead ([22, 48]). The indirect cost comprises the performance degradation of such a system caused by resource sharing. For example, switching a thread between two cores might result in more L1 cache misses and branch miss prediction since the thread was using the previous core's resources, which in turn affects the performance of the system. The indirect cost of context switch resulting from cache performance loss, ranges between several microseconds to few thousands microseconds [45], [22]. Other researchers have also examined the indirect cost of context switching for caches [50, 75, 76], and the cost of context switching for branch predictors [18]. Some hardware efforts to speed up context switch for ARM architecture are: fast address space switching (FASS) [84], and fast context switch extension (FCSE) [14]. Cho et al. [17] proposed a protocol that is ensures a deadlock-free thread switches for finegrained migration architectures. Chapter 5 will discuss both types of switching overhead and possible solutions in more details.

## 2.4 **Program Phase Detection**

Many applications exhibit behavior in which program execution occurs in distinct phases, where each phase consists of a set of code blocks that are executed with a high degree of temporal locality. Many common types of programs exhibit this execution phase behavior [44]. There are several different mechanisms which have been proposed to detect application phase changes. Some of these techniques can be used to identify unique application phases.

In one of the single-ISA heterogeneous scheduling approaches described in Sectiion 2.2, Kumar used a simple mechanism to determine when an application's phase changes by monitoring the instructions executed per cycle (IPC) over some windows. When this value changes by more than 50% for one application or by a total of 100% changes for all applications [42], a phase change is said to have occurred. This approach makes no attempt to identify the individual phases, but instead only detect coarse changes in program behavior. It further lacks the ability to detect more subtle changes in application behavior because it relies on a significant change in the IPC.

More precise phase detection methods rely on statistical sampling of executing instructions. Such samples can be subsequently analyzed in software to determine phase composition. Hardware performance monitoring counters or the program counter can be sampled to gather low-overhead profiles, but such profiles do not support the differentiation of one phase from another. Basic block distribution analysis [70] combines intense, periodic sample-based profiling to determine the composition of repetitive phases.

Special purpose hardware can be used to reduce the overhead of accurate phase detection and identification. The hot spot detector [49] is a hardware mechanism for detecting and identifying program phases based on the address and taken/not-taken direction of retired branch instructions. Working set signatures [23] can be used to provide an efficient, compressed representation of an application's phases, which are composed of windows of retired instructions. Exploiting the correlation between a working set phase and program behavior, this approach was used to control reconfigurable hardware resources, and provides a relatively general mechanism for finding relatively short phases. Sherwood et al. [72] used a similar technique but weighted the profiled code by a phase's frequency of execution. Their architecture provides an accurate way of not only identifying program phases, but also predicting when a phase change will occur and which phase will execute next.

Many performance metrics correlate strongly to application phases, including cache behavior, branch predictor behavior, utilization of core resources and IPC [72]. Any of the mechanisms for identifying application phases could be used with our approach, but for the purposes of this work, I utilize the relatively straightforward working set signatures mechanism [23], which is described in more detail in Chapter 3. Only improved results from using more accurate phase identification techniques are expected.

# Chapter 3

# Methodology

This chapter describes the experimental setup and evaluation metrics used in this work. It also includes a description and initial evaluation of some parameters of the phase detection method used in this dissertation.

# 3.1 Simulation Environment

The simulation environment used to evaluate the proposed techniques includes both a cycle-accurate simulator and a simulation model described below.

## 3.1.1 Cycle-Accurate Simulation Framework

Detailed evaluations of the techniques proposed in this dissertation was performed using a cycle-accurate simulation framework, Soonergy, a microarchitectural simulator developed by the Soonergy Architecture Research Lab at the University of Oklahoma [27]. This simulator provides timing simulations comparable with a physical hardware design because it provides a cycle-bycycle timing and performance simulation. The simulator is based on the x86 instruction set architecture (ISA), and is developed to simulate different architectural designs (including multicore architectures) for performance and power. The simulator runs on Windows platform systems and allows users to simulate different processor configurations. Two types of experiments were performed using Soonergy: single-core simulations and multicore simulations. Single-core simulations are used to evaluate the different characteristics of the executed programs and as inputs for the performance estimation model model described in Section 3.1.2. Each singlecore/single-benchmark ran for 300 million instructions. The Soonergy simulator profiled performance and microarchitectural behavior. Multicore simulations include heterogeneous mixes of different x86 cores. Different types of cores are distinct in micro-architectural design including pipeline depth and architecture, number and sizes of execution units, different cache sizes, and branch predictors. Dual-core and quad-core simulations were performed. In the presented experiment, the simulator runs all benchmarks on the multicore system simultaneously until the slowest benchmark executes 300 million. Faster benchmarks execute more than 300 million by looping through benchmark's trace files.

#### 3.1.2 Performance Estimation Model