### SYNTHESIS OF OPTIMUM COMPLEX

#### FLUID LOGIC SEQUENTIAL

### CIRCUITS

By

# JACK HOWARD COLE

### Bachelor of Science Oklahoma State University Stillwater, Oklahoma 1958

Master of Science Oklahoma State University Stillwater, Oklahoma 1963

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of DOCTOR OF PHILOSOPHY May, 1968

OKLAHOMA STATE UN SITY LIBRONY

OCT 24 1968

1

SYNTHESIS OF OPTIMUM COMPLEX

FLUID LOGIC SEQUENTIAL

CIRCUITS

Thesis Approved:

Thesis Adviser an 10 ra

Graduate College Dean the of

### ACKNOWLEDGMENT

I offer my sincere thanks to those who have helped me in the completion of my doctoral program:

This thesis is largely the result of my association with Dr. Earnest C. Fitch, chairman of my graduate committee, whose enthusiasm for fluid logic became contagious. I shall always be grateful for his inspiration, sound advice, and repeated acts of friendship over the years.

The members of my graduate committee, professors Lee Harrisberger, Charles M. Bacon, and Karl N. Reid, for their genuine interest in me and in this study. Their suggestions and constructive criticism were very helpful.

The management of North American Aviation, Inc., for selecting me to receive their Science and Engineering Fellowship. I especially appreciate the friendship of Messrs. Frank Rizzardi and Wayne Cloud.

My good friend, Mr. Charles E. Lewis, for his willingness to discuss this study and for his penetrating questions which helped my thinking.

Miss Gail Mortimer and Mrs. Beth Carpenter for their valuable typing assistance.

Miss Velda Davis for her expert typing and editing of the final manuscript.

iii

My wife, Carol, and daughter, Suzanne, for their years of patience and cooperation, and for making everything I do worthwhile.

### TABLE OF CONTENTS

| Chapter | r                                         | Page                         |

|---------|-------------------------------------------|------------------------------|

| I.      | INTRODUCTION                              | 1                            |

|         | Intuitive Circuit Design                  | 34<br>56<br>8                |

| II.     | OBJECTIVE AND SCOPE OF STUDY              | 11                           |

| III.    | OPERATIONS TABLE SYNTHESIS APPROACH       | 17                           |

| IV.     | OPERATIONAL PATTERNS OF BASIC CIRCUITS    | 24                           |

| V.      | DEVELOPMENT OF SYNTHESIS PROCEDURE        | 54                           |

|         | Initial Development                       | 54<br>75<br>89<br>102<br>109 |

| VI.     | TREATMENT OF SPECIAL SITUATIONS           | 121                          |

|         | Hazards                                   | 121<br>124                   |

|         | Larger Sequence                           | 124<br>125                   |

| VII.    | SUMMARY, CONCLUSIONS, AND RECOMMENDATIONS | 126                          |

|         | Summary                                   | 126<br>127<br>131            |

| SELECTI | ED BIBLIOGRAPHY                           | 134                          |

| APPEND  | IX                                        | 137                          |

### LIST OF TABLES

| Table |                                                                                                                                                                         | Page |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| I.    | Operations Table for Automatic Circuit<br>A, $\underline{A}$ , B, $\underline{B}$ , C, $\underline{C}$                                                                  | . 40 |

| II.   | Tabular Display of Structure of Automatic<br>Circuit A, <u>A</u> , B, <u>B</u>                                                                                          | . 41 |

| III.  | Tabular Display of Structure of Automatic<br>Circuit A, <u>A</u> , B, <u>B</u> , C, <u>C</u>                                                                            | • 44 |

| IV.   | Operations Table for Intuitively Designed<br>Automatic Circuit A, B, <u>B</u> , <u>A</u> , B, A, <u>A</u> , <u>B</u>                                                    | • 47 |

| ν.    | Tabular Display of Partial Structure of<br>Intuitively Designed Sequential Circuit<br>A, B, $\underline{B}$ , $\underline{A}$ , B, A, $\underline{A}$ , $\underline{B}$ | • 52 |

| VI.   | Preliminary Synthesis Table for Automatic Circuit A, B, $\underline{B}$ , $\underline{A}$ , B, A, $\underline{A}$ , $\underline{B}$                                     | • 55 |

| VII.  | Preliminary Synthesis Table II for<br>Automatic Circuit A, B, <u>B</u> , <u>A</u> , B, A, <u>A</u> , <u>B</u>                                                           | • 58 |

| VIII. | Synthesis of Eight-Event Sequence                                                                                                                                       | • 59 |

| IX.   | Operations Table for Automatic Circuit<br>A, B, $\underline{B}$ , $\underline{A}$ , B, A, $\underline{A}$ , $\underline{B}$                                             | . 61 |

| Χ.    | Synthesis of Modified Sequence                                                                                                                                          | . 66 |

| XI.   | Operations Table for Automatic Circuit<br>A, B, $\underline{B}$ , $\underline{A}$ , A, B, $\underline{A}$ , $\underline{B}$                                             | . 68 |

| XII.  | Synthesis of Ten-Event Sequence                                                                                                                                         | 。 70 |

| XIII. | Operations Table for Automatic Circuit<br>A, B, $\underline{B}$ , $\underline{A}$ , B, A, $\underline{A}$ , $\underline{B}$ , A, A                                      | • 73 |

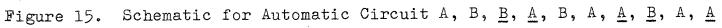

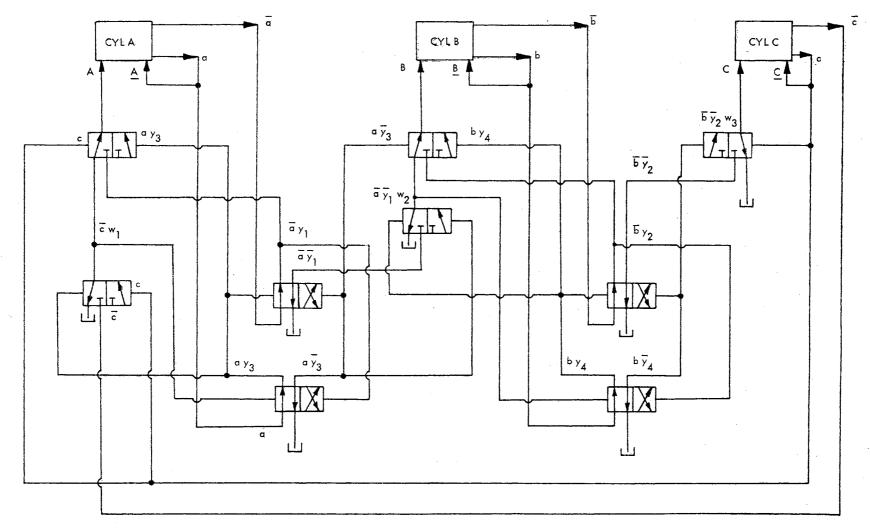

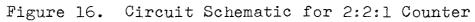

| XIV.  | Synthesis Table 2:2:1 Counter                                                                                                                                           | 。 76 |

| .VX   | Operations Table 2:2:1 Counter                                                                                                                                          | . 80 |

## Table

| XVI.    | Synthesis Table 2:2:1 Counter (Alternate)                                                             | 83  |

|---------|-------------------------------------------------------------------------------------------------------|-----|

| XVII.   | Operations Table 2:2:1 Counter (Alternate)                                                            | 85  |

| XVIII.  | Synthesis Table 3:2:1 Counter                                                                         | 87  |

| XIX.    | Operations Table 3:2:1 Counter                                                                        | 88  |

| XX.     | Synthesis Table 3:2:1 Counter (Alternate)                                                             | 90  |

| XXI.    | Operations Table 3:2:1 Counter (Alternate)                                                            | 91  |

| XXII.   | Synthesis Table for Fourteen-Event<br>Automatic Circuit                                               | 93  |

| XXIII.  | Modified Synthesis Table for Fourteen-<br>Event Automatic Circuit                                     | 94  |

| XXIV.   | Equations for Fourteen-Event Automatic<br>Circuit                                                     | 95  |

| .VXX    | Synthesis Table for Fourteen-Event<br>Sequence (Alternate)                                            | 96  |

| XXVI.   | Synthesis Table for Eighteen-Event<br>Automatic Sequence                                              | 99  |

| XXVII.  | Equations for Eighteen-Event Automatic<br>Sequence                                                    | 100 |

| XXVIII. | Synthesis Table and Circuit Equations for<br>Eighteen-Event Automatic Sequence<br>(Alternate Circuit) | 101 |

| XXIX.   | Synthesis Table for Twenty-Four-Event<br>Sequence Including 3:2:1 Counter                             | 104 |

| XXX.    | Circuit Equations for Twenty-Four-Event<br>Sequence                                                   | 106 |

| XXXI.   | Primitive Flow Table for Twenty-Four-<br>Event Sequence                                               | 107 |

| XXXII.  | Merged Flow Table for Twenty-Four-Event<br>Sequence                                                   | 108 |

| XXXIII. | Synthesis Table for Forty-Two-Event<br>Sequence                                                       | 110 |

| XXXIV.  | Circuit Equations for Forty-Two-Event<br>Sequence                                                     | 112 |

### LIST OF FIGURES

| Figu | re                                                                                                                                                                                                                                                             | Page |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| l.   | Sequential Control System Schematic                                                                                                                                                                                                                            | 13   |

| 2.   | Two Cylinder Schematic and Operations Table                                                                                                                                                                                                                    | 21   |

| 3.   | Schematic for Single Cylinder Which<br>Automatically Extends and Retracts                                                                                                                                                                                      | 25   |

| 4.   | Simplification of Power Circuit Schematic                                                                                                                                                                                                                      | 27   |

| 5.   | Interrupted Jet Position Sensing                                                                                                                                                                                                                               | 29   |

| 6.   | Memory Valve Combinations                                                                                                                                                                                                                                      | 31   |

| 7.   | Memory Valve Combination With Shut-Off<br>Provision                                                                                                                                                                                                            | 32   |

| 8.   | Pure Fluid Memory Circuit                                                                                                                                                                                                                                      | 34   |

| 9.   | Schematic for Automatic Circuit $A, \underline{A}, B, \underline{B} \dots \dots$                                                                         | 36   |

| 10.  | Schematic for Automatic Circuit A, $\underline{A}$ , $\underline{B}$ , $\underline{B}$ , C, C.                                                                                                                                                                 | 39   |

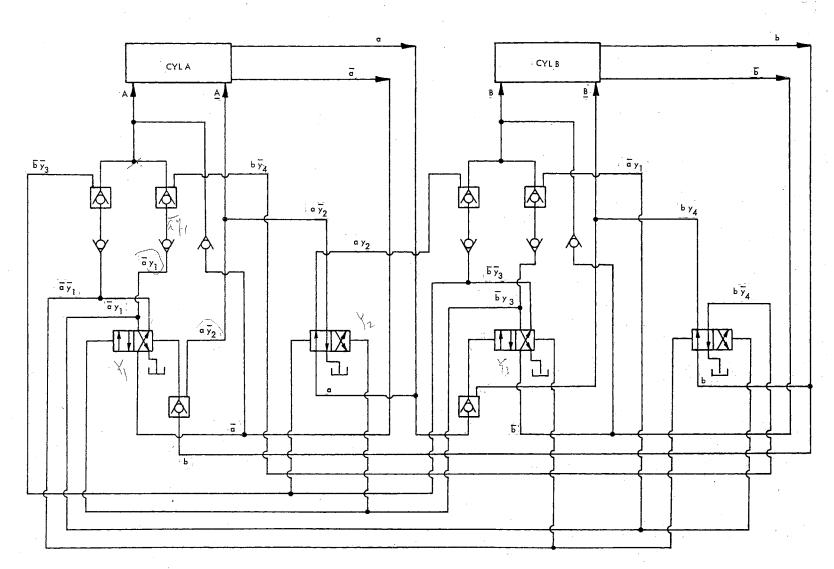

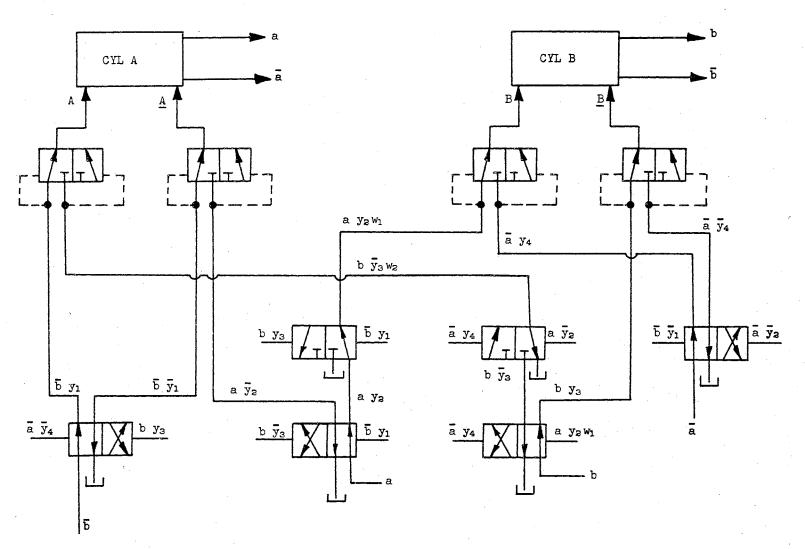

| 11.  | Intuitively Designed Automatic Circuit<br>A, B, <u>B</u> , <u>A</u> , B, A, <u>A</u> , <u>B</u>                                                                                                                                                                | 46   |

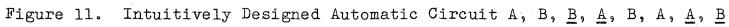

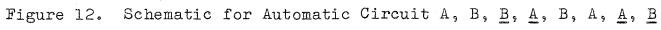

| 12.  | Schematic for Automatic Circuit A, B, $\underline{B}$ , $\underline{A}$ , B, $\underline{A}$ , $\underline{A}$ , $\underline{B}$                                                                                                                               | 62   |

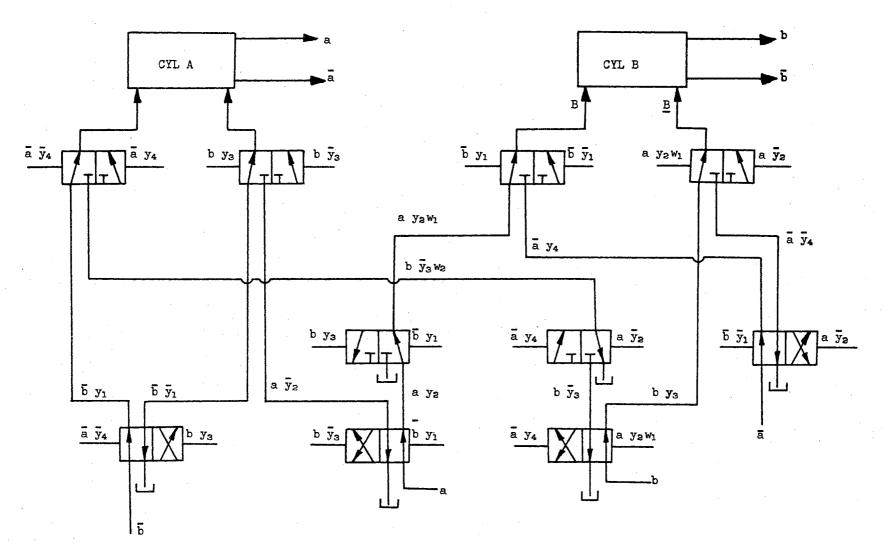

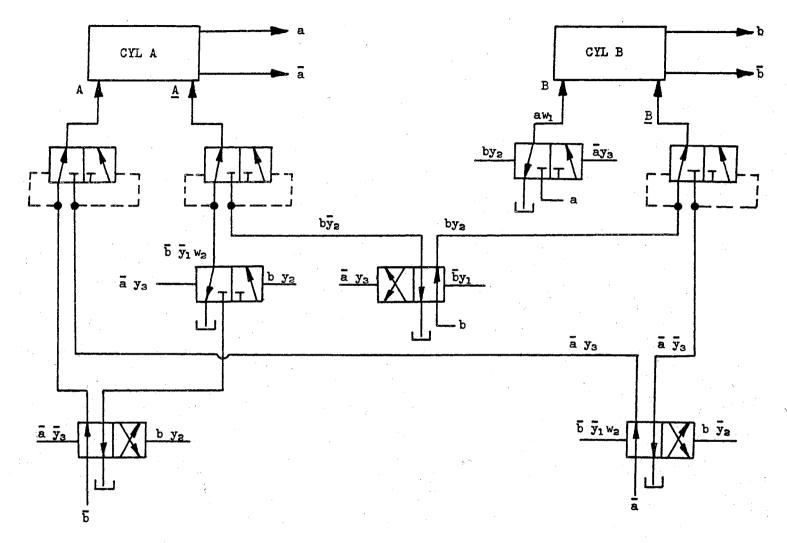

| 13.  | Schematic for Automatic Circuit<br>A, B, <u>B</u> , <u>A</u> , <u>B</u> , <u>A</u> , <u>A</u> , <u>B</u> (Modified)                                                                                                                                            | 64   |

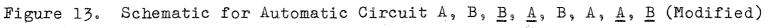

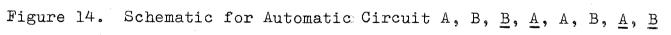

| 14.  | Schematic for Automatic Circuit<br>A, B, <u>B</u> , <u>A</u> , A, B, <u>A</u> , <u>B</u>                                                                                                                                                                       | 69   |

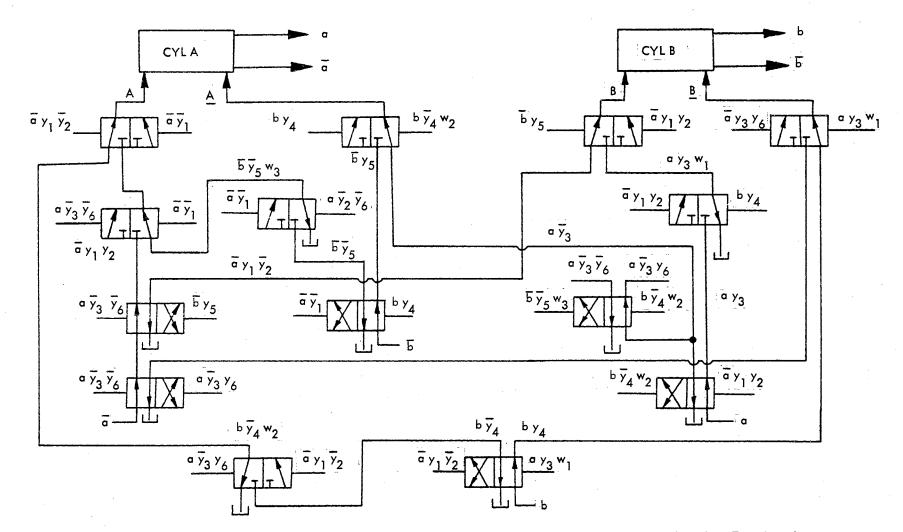

| 15.  | Schematic for Automatic Circuit A, B, $\underline{B}$ , $\underline{A}$ , B, $\underline{A}$ , $\underline{A}$ , $\underline{B}$ , $\underline{A}$ , $\underline{B}$ , $\underline{A}$ , $\underline{A}$ , $\underline{A}$ , $\underline{A}$ , $\underline{A}$ | 74   |

| 16.  | Circuit Schematic for 2:2:1 Counter                                                                                                                                                                                                                            | 81   |

# Figure

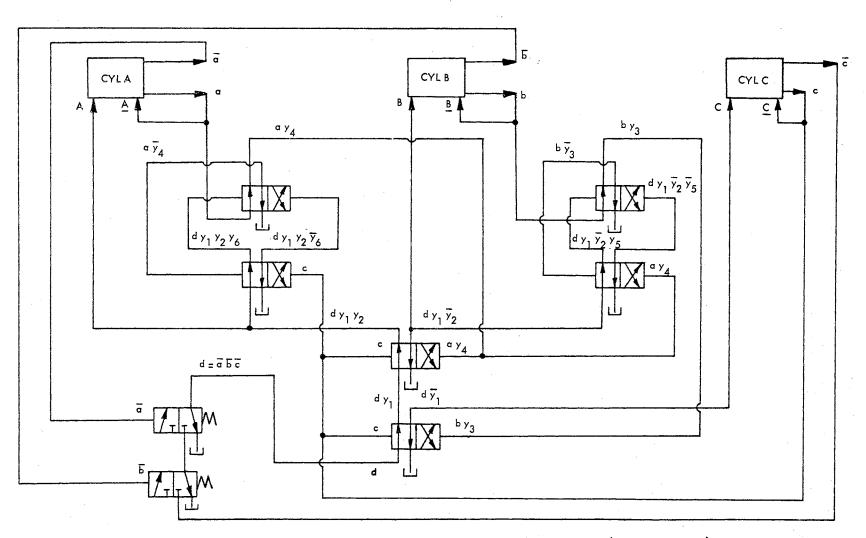

| 17. | Circuit Schematic for 2:2:1 Counter     |   |   |   |   | ~ ~  |

|-----|-----------------------------------------|---|---|---|---|------|

|     | (Alternate)                             | e | e | ٥ | ٥ | . 86 |

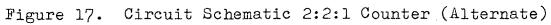

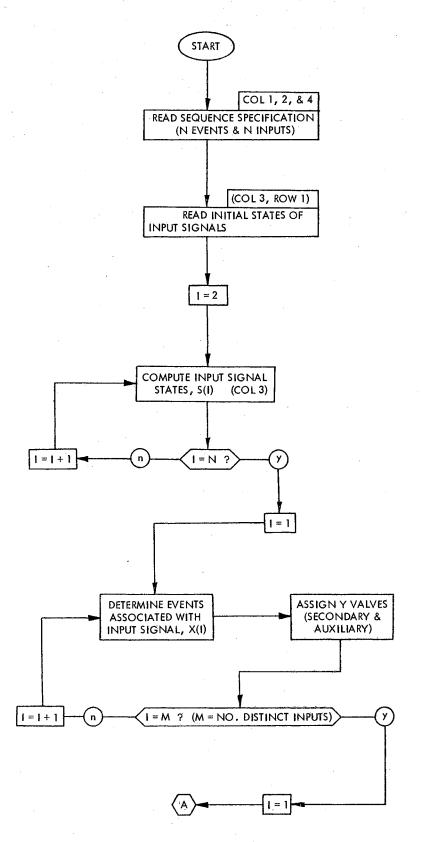

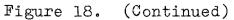

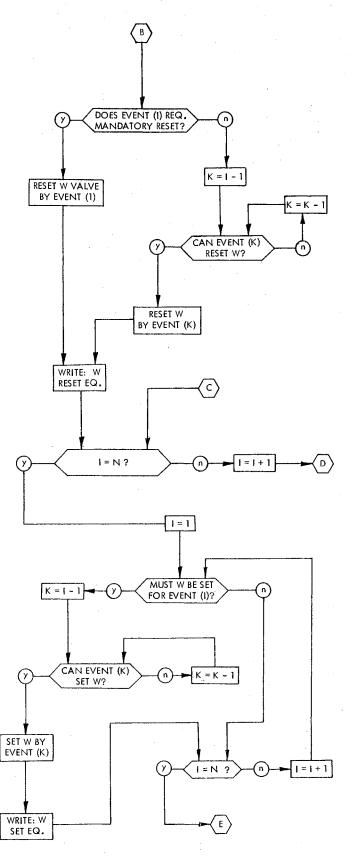

| 18. | Logic Flow Chart of Synthesis Procedure | ه | ٥ | ¢ | ٥ | 138  |

Page

### CHAPTER I

#### INTRODUCTION

Spurred on by the invention and development of fluidic devices, fluid logic is rapidly gaining acceptance and respect as a means of controlling automatic operations. References (1) through (6) report on a wide variety of applications.<sup>1</sup> Two major automotive companies are replacing electrical controls on assembly line machines with recently developed pneumatic systems. Other uses include scrap baling machines, numerous machine tools, high speed packaging machines, automatic assembly machines, material handling systems, process controls, jet engine control and missile guidance.

There is a growing realization that fluid systems are capable of performing all the logic functions that electrical systems can and often at less cost and with greater reliability. Other important advantages include freedom from fire and electrical shock hazards, immunity to nuclear radiation, resistance to vibration and ability to operate in high temperature environments (7).

<sup>&</sup>lt;sup>1</sup>Numbers in parentheses refer to references in the Selected Bibliography.

Although pure fluid amplifiers are most frequently mentioned in articles concerning fluid control, movingparts devices are also undergoing rapid development and are finding broad application in logic circuits. Some of the subminiature valve-type elements have such low-mass moving parts that their response times approach those of the pure fluid devices.

The terminology task group of the National Fluid Power Association committee working on standards have decided upon the term "fluidics" to include both the pure fluid and miniature conventional valves. The term is a contraction of the words "fluid" and "logic" and implies that the devices so classified are primarily logic control devices as opposed to the hardware in the "power" portion of a fluid system (8).

A large number of U.S. industries, as well as government agencies and several leading universities, are conducting research and development programs involving fluid control devices and applications. The result is that a broad selection of excellent hardware is available which can be used in the design of fluid logic systems.

In spite of the rapid evolution of logic devices, there has not been enough progress in the ability to systematically assemble the devices into efficient circuits. This lack of synthesis capability prevents the full exploitation of fluid logic in systems of large complexity.

A brief survey of the field of logic design is presented below.

### Intuitive Circuit Design

Most of the circuits in use today have been designed by cut and try methods wherein the designer sketches schematic diagrams of various configurations until he arrives at one that will work. Intuitive circuit synthesis is extremely time consuming, even for skillful and experienced designers. As the complexity of the required sequence increases, the possible number of circuit configurations that will "work" grows until it is highly improbable that any two designers would develop the same circuits or that either circuit would be near optimum. (Criteria for optimum circuits are described in the next chapter.) In efforts to add some semblance of orderliness to intuitive synthesis, some of the more experienced designers have developed several practical aids and procedures.

E. L. Holbrook (9, 10), who has been active in pneumatics since 1929, has written a series of articles describing a number of applications using pneumatic logic functions. He has also suggested ways to improve the schematic representation of circuits. His technique is to separate a logic control system into isolated functions, control them individually and then tie them together. He

has designed some fairly large systems using these methods.

Salek (11) recommends using a cascaded or stacked memory valve system wherein air pressure is "distributed" to limit valves which are activated at the ends of the piston rod travel. Morgan (12) also recommends this method because it helps reduce the number of logic valves in the control system. The approach starts to get into difficulty, however, when a signal from one of the limit valves is required to go to different places at different times during the cycle. There is also the problem of properly switching the memory valves in the distribution circuit.

Hall (13) points out the advantage of using the "ladder" diagram in designing logic circuits. This is a device borrowed from electrical circuit designers with abstract fluid logic symbols substituted for the analogous electrical symbols. The chief feature of the ladder diagram is that it enhances visualization of circuit operation. It has limited utility for synthesizing circuits.

### Application of Logic

One of the major steps toward development of nonintuitive circuit design procedures has been the application of Boolean algebra to describe the functions of fluid logic devices and combinations of these devices (14, 15). Once a circuit has been expressed as a function in this

mathematical system, a diagram of the circuit is not required in order to simplify the circuit. If a simpler circuit exists, it can be found by certain Boolean algebraic manipulations. Henke (16) and Ledgerwood (17) are strongly urging control circuit designers to learn the techniques of Boolean algebra and to depend less on the cut and try methods of the past.

#### The Timing Chart Method

The timing chart (also called sequence diagram or cycle chart) is a device widely employed in designing sequential circuits. Ronan (18) and Henke (19) recommend its use. The chart consists of vertical divisions with each division representing a certain time interval. The outputs and inputs are listed down the left-hand side of the chart. If a particular input or output is supposed to be "on" during a certain time interval, a solid bar is drawn horizontally through the interval. If the input or output is to be "off" in some interval, the space is left blank. Now, each interval is compared with the other intervals. Wherever the situation exists with different outputs occurring for the same combination of inputs, secondaries must be added. When the proper number of secondaries have been added and the intervals established during which each secondary must be "on" or "off", the chart is complete. A circuit is next designed which will satisfy the chart. Many variations will work and the

designer must be skillful in order to produce an optimum circuit.

Yuditskly (20) and Zenchenko (21) code each of the inputs with a weighted number and list this number beside the input at the left side of the chart. By going down each interval and summing weighted values where the bars cross the interval, a total for the column interval is reached. Secondaries are added when columns have the same total. Each secondary is also coded with a weighted value and where its bar crosses an interval, that value is added to the total. A unique situation exists when each column has a total of weighted values different from all the others. As before, a circuit is then assembled which will satisfy the chart.

The timing chart can be considered as one of the better aids in intuitive design. It displays the sequential specification in a graphical manner and provides for assigning secondaries or memory elements to cover appropriate intervals of the chart. The quality of the circuit resulting from the chart depends greatly on the skill of the designer. Ronan states that it is a good policy to investigate several arrangements so that a desirable circuit is not overlooked.

### Application of Switching Circuit Theory

Professor E. C. Fitch (22, 23, and 24), of Oklahoma State University, was one of the first to recognize the

limitations of intuitive circuit design and has been instrumental in introducing formal logic synthesis techniques. By successfully adapting the procedures developed for electrical switching circuits to the synthesis of fluid logic systems, he has contributed considerably to extending the complexity to which circuits can be systematically designed.

With this method, the sequence specification is carefully represented in the Huffman flow table model. The flow table is then reduced and merged to assure a minimum number of secondaries or memory valves. Next, the table is rearranged into a required order and becomes the operational flow table. Information is taken from the operational flow table and entered into Karnaugh maps from which equations for the output circuit and memory circuit are obtained. Circuit diagrams can be drawn by simply implementing the equations with fluid logic symbols representing physical hardware.

The procedure or method is non-intuitive and greatly reduces the time required to synthesize a sequential circuit. Its advantages are being recognized by industry and at least one large company uses the method in designing hydraulic logic circuits. They also conduct an in-plant course which is similar to Oklahoma State University's "Fluid Logic" course.

In spite of its significant contribution to the problem of fluid logic synthesis, the method becomes extremely

unwieldly as the number of variables increases. Each additional input or secondary doubles the size of the maps involved. Even large digital computers soon become incapable of handling the mushrooming problem.

### Synthesis Procedures Research

The development of digital computers and complex communications systems depends heavily on sequential synthesis procedures. Consequently, considerable effort is being made to improve existing methods and to develop new ones.

Marcus (25) shows how to use the Huffman flow table and Karnaugh maps to synthesize sequential circuits. His text is used for teaching a graduate course in switching circuits at Oklahoma State University and other universities.

Moore (26), one of the pioneers in developing sequential synthesis procedures, has published a collection of the more important papers on sequential machines and includes one by D. A. Huffman. An extensive bibliography of related work is included. This collection is primarily intended to supplement formal texts such as the one by Marcus.

Haring (27) outlines the recent work at M.I.T. which primarily involves investigating mathematical properties of sequential machines based on the Huffman model. As yet, no major progress has been made in developing improved synthesis procedures.

McKellar (28) has investigated what he terms as a practical synthesis procedure. His method involves artificially opening the feedback loops in a sequential machine. Each time a loop is "opened", a secondary is replaced by an input and an output. The rows of the flow table are, thus, reduced while the number of columns increases. After a sufficient number of interactions, the flow table is reduced to one row which can be expressed as combinational circuits. The chief claim for this method is that it is iterative and can be programmed for a computer. Its disadvantage is that there is no assurance of an optimum or near optimum resulting circuit because the result depends on the order in which the loops are opened.

Tripp (29) employs a matrix system of function representation. His method again becomes unwieldly as the complexity increases. Halsey (30) attempted to apply linear programming techniques to the state assignment problem but reported negative results.

In summary, although a considerable effort is being made to develop better synthesis procedures, the progress is slow. It should be noted that almost all of the approaches are fairly abstract and general in nature.

The models (such as the Huffman flow table) succeed in expressing the sequence specifications in a rigorous

non-ambiguous manner. However, a model of this type inherently contains all of the solutions which can satisfy the specification. The problem becomes one of arriving at the right solution from all the possibilities and it is impractical or even impossible to develop all of the solutions.

### CHAPTER II

### OBJECTIVE AND SCOPE OF STUDY

The objective of this study has been to investigate and develop a new procedure for the systematic synthesis of fluid logic sequential circuits. Although greatly simplified in comparison to present techniques, the procedure is rigorous and powerful, permitting the straightforward synthesis of problems which are too complex for ready solution by existing methods.

The circuits synthesized by the new procedure have a structure or form based on carefully designed ideal simple or basic circuits. These circuits are considered optimum based upon the following important criteria:

- 1. They have the fastest possible response. That is, the minimum time elapses between the completion of one event and the beginning of the next event in the sequence. (The time required for the event to occur is outside the control of the logic circuit.)

- 2. The circuits contain a minimum assortment of logic elements.

- 3. None of the distribution valves are

switched with fluid flowing through the valves. This has the advantages of using lower switching signals, providing faster switching response and allowing possible valve simplication.

4. A minimum or near minimum of total system hardware. This feature is important from the standpoints of economy, over-all size, and system reliability.

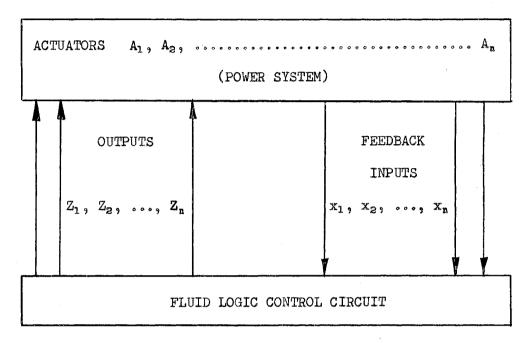

The scope of the study was limited to closed systems having only feedback inputs. However, this is an important class of fluid logic systems, representing a very broad application in industry. A schematic representation of this type of circuitry is shown in Figure 1. The power system is made up of actuators and their power control valves. The actuators may be linear or rotary devices. Each actuator is controlled by its respective output signal from the fluid logic control circuit. At the completion of an actuation (called an event) a signal is emitted from the power system and is fed into the control circuit where it is directed through the circuitry to initiate the next event. At the same time the signal modifies the control circuit, preparing it for the next input signal. This process is repeated until a specified sequence of events has been completed, at which time the power system shuts down or repeats the sequence as many times as desired.

Figure 1. Sequential Control System Schematic

Both input and output signals are of the level type. That is, a signal is either off (at vent or tank pressure) or on (maximum pressure). A signal changing from off to on is considered a step input, going from a steady state vent pressure to a steady state maximum pressure. The only time an input signal changes is when an event (in the case of a cylinder, a complete extension or retraction) is completed. Thus, the circuits are asynchronous as opposed to synchronous circuits where all of the changes occur at clocked intervals.

This study also assumes that an operational event of finite time follows each output from the fluid logic control circuit. The actuation of devices in the power circuit serve as effective delays, assuring that the control circuit modification has stabilized before the subsequent event completion signal is fed back into the control circuit. With this concept, the problem of timing does not have to be considered as it would in the case where the output is fed directly back into the control circuit without first causing some event to occur in the power circuit. Such a situation could occur in computational circuits which are not considered in this study.

Critical races are avoided by making the usual restriction that inputs change only one at a time. One exception to this restriction is permissible and will be discussed later.

Input changes result from position sensing which

takes place at the limits of the actuator travel. This precludes the system from getting out of sequence or confused as a result of false signals which could inadvertently occur in pressure sensing or preset program systems. The development of accurate and reliable position detection devices has made position sensing the dominant method of actuating input signals in the feedback type systems.

There are three main types of fluid logic circuits commonly encountered in the above classification. These different types will each be investigated so that a general procedure will result, capable of handling all three types. These three types are:

- 1. Ordinary sequential circuits. If there are two or more actuators in the power circuit, then if some actuator A, extends or retracts or cycles once, then some other actuator, say A, must extend or retract or cycle before actuator A, can act again.

- 2. <u>Counter circuits</u>. The first actuator in the power circuit will cycle some specified number of times, then the next actuator will cycle its specified number of times and so on until the sequence is complete and stops or starts over.

3. <u>Complex circuits</u>. This circuit results

from mixing a counter circuit into an ordinary circuit. As the name implies, this type of circuit is the most complicated and is the most difficult to handle.

### CHAPTER III

### OPERATIONS TABLE SYNTHESIS APPROACH

Assume for the moment that a circuit has been synthesized by any of the existing methods and it is desirable to check its operation. If the circuit is simple, one can go through a schematic diagram and carefully check for proper operation. This requires mentally keeping track of the positions of the different valves in the circuit at the various stages of the sequence. Alternatively, the circuit may be breadboarded and checked for operation using actual hardware. In either case, if the circuit is very complicated, correcting errors becomes a very tedious and time consuming task.

In order to enhance the verification of a circuit's proper performance, the operations table or composite chart has been recently developed (23). A fluid logic sequential circuit is digital with changes taking place at discrete intervals. The operations table depicts the complete status of the circuit at each of these intervals. Each row of the operations table represents a stabilized state of the input variables and the corresponding stable states of the affected output and secondary variables. In comparing two rows of the table, it is apparent which

variables were in transition during the change of circuit state. The completed table includes the entire spectrum of the various circuit states or conditions during one cycle of the sequence. Checking the rows one at a time is somewhat analogous to examining a film strip frame-byframe. If an error is contained in the circuit as synthesized, it will show up as a contradiction in the logic portrayed in the rows of the operations table. Not only does the contradiction appear, but the variables involved are directly identified.

Regardless of the procedure used to develop the sequential circuit, its operational logic structure can be fully displayed in the operations table. It was in checking out and examining the logic structure of various synthesized circuits in the operations table that led the writer to conclude that such a table could possibly be used for synthesizing a sequential circuit directly. The table contains the concise operational specification of the circuit in addition to the logic structure of the complete circuit for all stages of the sequence.

At the start of a synthesis procedure, all that is known to the designer is the sequence of events that the system is required to perform and the input signals associated with these events. Normally, this specification is expressed in a primitive flow table and from there the involved procedure of developing a solution is carried out.

If the operations table is used for direct synthesis, the problem is to start with the bare specification in the table and then proceed to develop the logic structure that completes the table and defines the circuit. As previously mentioned, there are always several distinct circuits that can satisfy even a simple sequential system or machine. As the complexity increases, the number of possible solutions rapidly becomes very large. Each distinct circuit realization for some specified sequence will appear differently in the operations table. Thus, it is immediately obvious that there are as many ways to construct a table as there are possible circuit realizations. Yet, it is this very feature which makes the synthesis approach attractive. For if it is possible to construct the logic in the table and derive workable circuits, then it might also be possible to construct a circuit having some desired form, since the manner in which the table is built up is at the discretion of the designer.

This construction of sequential fluid logic circuits having certain characteristics or form is precisely the object of this study.

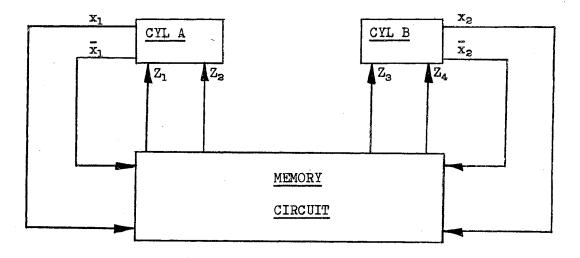

To illustrate the approach to be taken, the beginning of an operations table is shown in Figure 2. There are two cylinders, A and B. The sequence of operations to be performed is specified as follows:

| 1. | A | extends | Shorthand notatic |    |            |            | cio | l: |            |   |

|----|---|---------|-------------------|----|------------|------------|-----|----|------------|---|

| 2. | В | extends | A,                | в, | <u>B</u> , | <u>A</u> , | A,  | в, | <u>A</u> , | B |

- 3. B retracts

- 4. A retracts

- 5. A extends

- 6. B extends

- 7. A retracts

- 8. B retracts

- 9. Sequence repeats

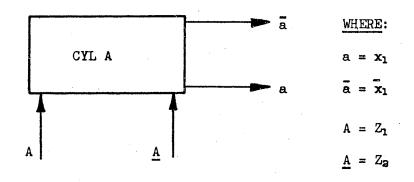

A basic schematic of the cylinder operation is also shown in Figure 2.

$Z_1$  and  $Z_2$  are the output signals which cause cylinder A to extend and retract, respectively, while  $Z_3$  and  $Z_4$  are the respective extend and retract signals for cylinder B. Input signal  $x_1$  denotes that cylinder A has extended, while signal  $\overline{x_1}$  indicates that A has retracted. The corresponding input signals for cylinder B are  $x_2$  and  $\overline{x_2}$ . The input signals affect the memory circuit so that the proper output signal occurs.

The preliminary operations table reveals that certain entries have been made. Starting at the left-hand side of the table, the event numbers are listed in the first column. The next column names the event that is associated with the number. The third column lists the stable condition of the inputs  $x_1$  and  $x_2$  just after completion of the previous event. For example, with the completion of event number 8, the final retraction of cylinder B in the sequence, the inputs  $x_1$  and  $x_2$  both stabilize at 0.

The next six columns are reserved for secondary

TWO CYLINDER SEQUENTIAL SCHEMATIC

|     |       |                               | Secondaries |                |                |    |                |                | Outputs        |                |            |                |

|-----|-------|-------------------------------|-------------|----------------|----------------|----|----------------|----------------|----------------|----------------|------------|----------------|

| No. | Event | x <sub>1</sub> x <sub>2</sub> | Yı          | Х <sup>5</sup> | Y <sub>3</sub> | ¥4 | Y <sub>5</sub> | Y <sub>6</sub> | Zı             | Z2             | Z3         | Z4             |

| 1   | A     | 00                            |             |                |                |    |                |                | x <sub>2</sub> | 0              | 0          | -              |

| 2   | В     | 10                            |             |                |                |    |                |                |                | 0              | <b>x</b> 1 | • 0            |

| 3   | B     | 11                            |             |                |                |    |                |                | <b>89</b> 51   | 0              | 0          | x <sup>s</sup> |

| - 4 | A     | 10                            |             |                |                |    |                |                | 0              | ž2             | 0          | _              |

| 5   | A     | 00                            |             |                |                |    |                |                | x <sub>1</sub> | 0              | 0          | -              |

| 6   | B     | 10                            |             |                |                |    |                | -              |                | 0              | x1         | 0              |

| 7   | A     | 11                            |             |                |                |    |                |                | 0              | x <sup>s</sup> | -          | 0              |

| 8   | B     | 01                            |             |                |                |    |                |                | 0              | 8              | 0          | x <sub>1</sub> |

### PRELIMINARY OPERATIONS TABLE

Figure 2. Two Cylinder Schematic and Operations Table

variables which make up the memory circuit. Although space has been provided for six, a lesser number may be needed. The last four columns are for the  $Z_1$ ,  $Z_2$ ,  $Z_3$ , and  $Z_4$  outputs. Zeros are entered where these signals must be off, as dictated by the sequential specifications. Dashes are entered where "don't care" conditions exist. This leaves blank spaces only for the conditions where the appropriate outputs must be on.

Now shifting back to the x1 x2 column, it is determined which variable changed as a result of the completion of the previous event. For example, upon completion of event number 8, x1 remained at 0 while x2 changed from one to zero. Thus,  $\overline{x_2}$  is entered into the  $Z_1$  output column in the first row. Subsequent variable changes are entered in the corresponding columns and rows. A systematic designation is, thus, derived for establishing the input that associates with the desired output. The task that remains is to assign secondaries appropriately so that they can be "anded" with the inputs in the Z columns. The proper secondary or combination of secondaries must be shifted to the appropriate memory positions prior to the time that the associated input signal appears. For example, when  $\overline{x_2}$  is turned on in the first event, it goes directly through the stable memory values to activate the  $Z_1$  output.

One of the fundamental differences in this approach as compared to existing methods is to work with the input signal (or signals) that changes at the completion of an

event rather than with the stabilized combination of input signals which exist at the completion of an event. The second aspect of the approach involves recognition of patterns in the operations tables for highly developed circuits. If these patterns can be identified and the basis for their occurrence established, the information can then be used to develop rules for the systematic assigning of secondaries. Circuits thus synthesized should be of the same basic type as the "ideal" circuits which were used to establish patterns in the operations table.

### CHAPTER IV

#### OPERATIONAL PATTERNS OF BASIC CIRCUITS

As previously stated, the objective of this study is to develop a synthesis procedure which will yield complex fluid logic circuits exhibiting the same type of structure as well developed simple or basic circuits. Some of these simple circuits will now be examined.

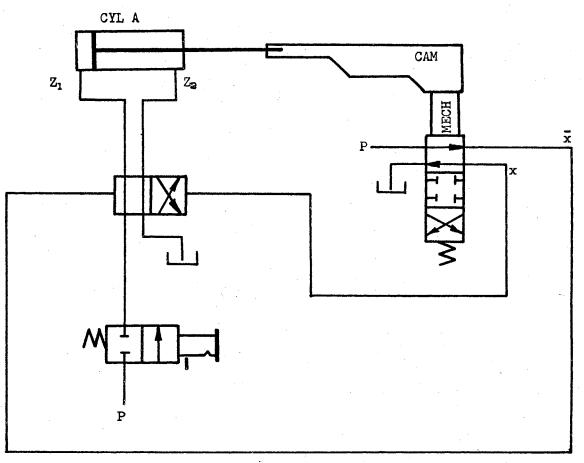

Figure 3 shows the simplest possible automatic fluid circuit using feedback inputs. Fluid power symbols are used to represent the valves in the circuit schematic. As in all the circuits which will be considered, position sensing is employed to turn the extend and retract signals off and on. In this case, a cam attached to the rod of cylinder A activates the input signal valve. With the cylinder retracted as shown, signal line  $\bar{x}$  is at maximum pressure while signal line x is vented to tank. During extension of the cylinder, the signal valve is in the center positions with lines x and  $\bar{x}$  both blocked. Thus, the  $\bar{\mathbf{x}}$  line remains pressurized until the cylinder reaches the end of its extension, at which time line x is pressurized and line  $\overline{\mathbf{x}}$  is vented to tank. During cylinder retraction, the signal valve is again in the center position, blocking off both ports so that pressure is

|   | Z2          | Zı          | x | EVENT | NO |

|---|-------------|-------------|---|-------|----|

|   | 0= <b>x</b> | x           | 0 | A     | 1  |

|   | x           | 0= <b>x</b> | 1 | A     | 2  |

| - |             |             |   |       |    |

OPERATIONS TABLE

Figure 3. Schematic for Single Cylinder Which Automatically Extends and Retracts maintained in line x until the end of the retraction stroke is reached. The input signals x and  $\bar{x}$  directly switch the cylinder control valve, commanding the cylinder to reverse operation at the ends of the strokes. The manually operated valve beneath the cylinder control valve is for starting and stopping the automatic operation.

The operations table is shown at the bottom of the figure. Note that the signal which comes on at the completion of an event (extension or retraction) goes directly to change the states of the output signals  $Z_1$  and  $Z_2$ .

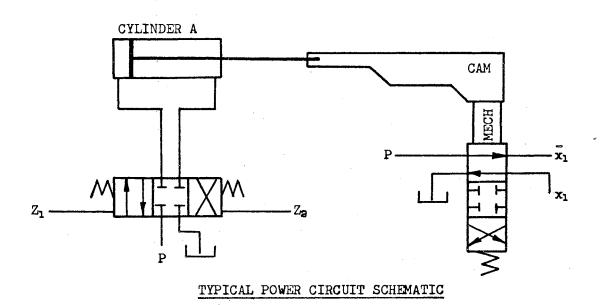

In this first example, the cylinder control value also acts as the logic value. However, in subsequent circuits, the power control value and the logic value delivering the output signals  $Z_1$  and  $Z_2$  will be separate elements. This will permit separation of the logic circuitry from the power system. Such an arrangement is shown at the top of Figure 4.

Here, the power valve has three positions and is spring centered. With both output signals  $Z_1$  and  $Z_2$  off, the valve will be centered, locking the cylinder in the position it had at the time the output signal went off. Thus, an optional feature is added to the system. For example, if cylinder A is fully extended and is to remain extended while some other event occurs, it is optional whether or not signal  $Z_1$  remains on during that time. Optional or "don't care" states of a system make a circuit

## SIMPLIFIED EQUIVALENT SCHEMATIC

Figure 4. Simplification of Power Circuit Schematic

easier to synthesize.

A simplified equivalent schematic of the power circuit is shown at the bottom of Figure 4. Although it is customary to use subscripted Z's to represent the output signals and subscripted x's to represent the input signals, a simpler and more meaningful notation is desirable for complex circuitry. Therefore, the output signal Z, commanding cylinder A to extend, becomes signal A, while <u>A</u> replaces the cylinder A retract signal  $Z_2$ . The input signals x, and  $\bar{x}$ , are replaced by a and  $\bar{a}$ , respectively. Thus, in a multicylinder circuit, it becomes easier to associate signals with cylinders.

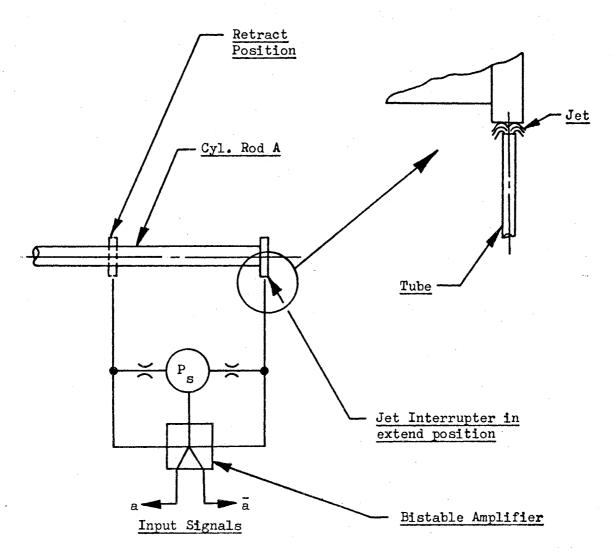

In the previous examples, position sensing has been shown by the action of a cam and valve combination. Α more recent and in some cases a more reliable and accurate method is to interrupt a jet of air. This sensing technique is especially useful when using fluidic devices without moving parts. A schematic representation of this type of sensing is shown in Figure 5. When the cylinder reaches the end of its travel, an interrupter attached to the cylinder rod or some part of the object being moved causes a back pressure to build up in the air tube. This back pressure switches a bistable amplifier causing a change in the output signals. Various other schemes of using the interrupted jet for position sensing are possible.

After the input signal is produced by the position

Figure 5. Interrupted Jet Position Sensing

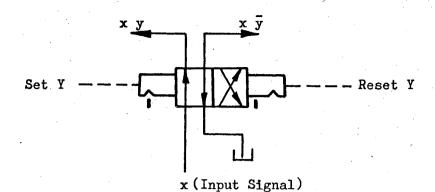

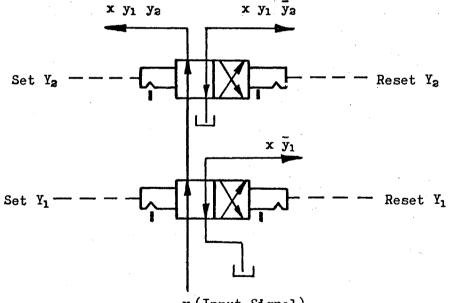

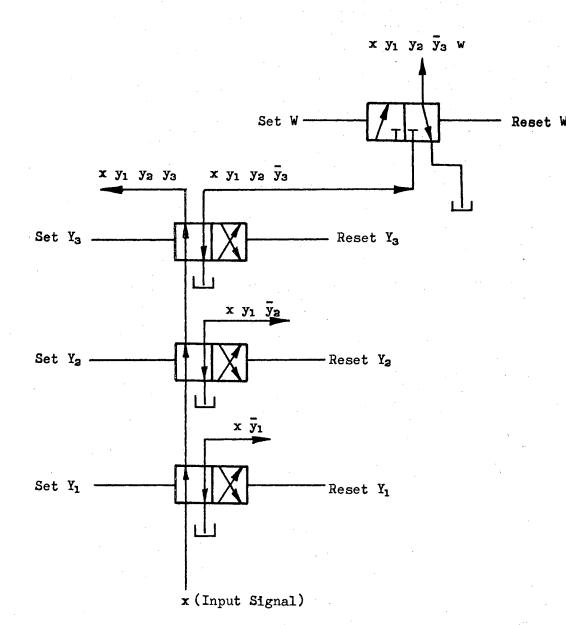

sensor, it is necessary to direct the signal to the desired part of the logic circuit. If the signal always goes to the same place, there is no problem. However, when a particular signal goes to different places at different intervals of the sequence, it is necessary to provide gating. The implementation of this gating using fluid power symbols is shown in Figure 6. Single gating for sending signal x to two different locations is shown at the top. The valve combination for sending signal x to three locations is shown at the bottom. The valves are detent held in their most recently activated position (set or reset) and will shift only when the opposite signal is applied. Both the set and reset signals will not be simultaneously applied. The notched portions on the sides of the symbols represent the detents. These will be eliminated on most of the subsequent symbols for simplicity. However, it is to be understood that whenever a pilotoperated logic valve is shown, it is a detent valve. The detent provides the "memory" function of the logic circuitry.

A memory value combination for sending an input signal to four different locations is shown in Figure 7. This is referred to as "third order" memory since three separate activating signals are required to gate the input signal. The two-value combination in Figure 6 represents second order memory and the one value, first order memory. In general, if an input signal goes to n different places,

Memory Valve for Sending Input Signal x to Two Different Locations.

Note: Capital Y refers to the memory valve. Lower case y refers to the state of the valve.

x (Input Signal)

Memory Valve Combination for Sending Input Signal x to Three Different Locations

Figure 6. Memory Valve Combinations

Memory Valve Combination for Sending Input Signal x to Four Different Locations With Shut Off Provision for Signal  $x y_1 y_2 y_3$

Figure 7. Memory Valve Combination With Shut Off Provision

n-l memory valves will be required to distribute the signal. The memory gating valves just discussed are referred to as "Y" valves. This nomenclature is appropriate because the valve does act as a "Y" or branch point in the logic circuit. Figure 7 also contains another type of memory or detent valve. This valve serves to shut off an input signal and vent the output port to tank when the valve is in the "reset" position shown. This valve will be referred to as a "shut-off" valve or a "W" valve. When the shut-off valve is in the "set" position, the input signal passes through. The purpose of the W valve is to prevent signals from opposing each other in the logic circuitry. The W valve function will be seen as more circuits are examined.

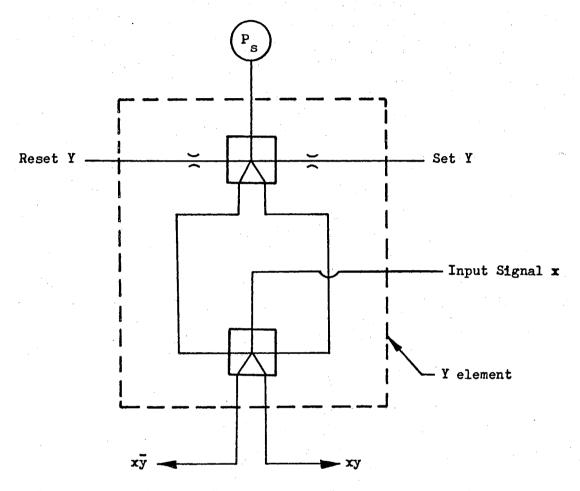

The gating functions just discussed can be implemented equally well with pure fluid components. A memory circuit for sending an input signal to two different locations is shown in Figure 8. The pair of bistable amplifiers enclosed by the dashed line is considered as a single element and can be made so physically. The reason for staging the amplifiers is to enable the element to remember its last setting even if the set or reset signal has been removed. The top amplifier is connected to supply pressure and is controlled by the set and reset signals. Once the amplifier is set or reset, it will remain in that state until the opposite signal comes on. Its output is a low level signal which biases the second amplifier. Thus,

Figure 8. Memory Circuit for Sending Input Signal x to Two Different Locations

when the input signal x appears at the bottom amplifier, it is steered by the bias signal that happens to be controlling.

When there is no input signal x, there is no output xy or  $x\overline{y}$  because the bias signal is strong enough to steer x through the second amplifier, but is not strong enough to cause an output without x. Wilson (31) has shown that a much weaker signal is needed at the control port to divert an incoming signal than is required to **switch** an established flow.

The shut-off function can be accomplished in an almost identical manner. In this case, however, one of the outputs is vented and the shut-off bias signal must be strong enough to switch an established flow.

The preceding discussion has shown that sensing and memory functions can be implemented with either pure-fluid or moving-parts fluidic elements. For the sake of brevity and consistency, only moving parts symbols will be used in the circuits involved in the remainder of this study. It is important to realize that the logic developed could also be implemented with pure fluid devices. The major purpose in discussing fluidic elements has been to provide an understanding of the key circuit functions involved in developing the synthesis procedure.

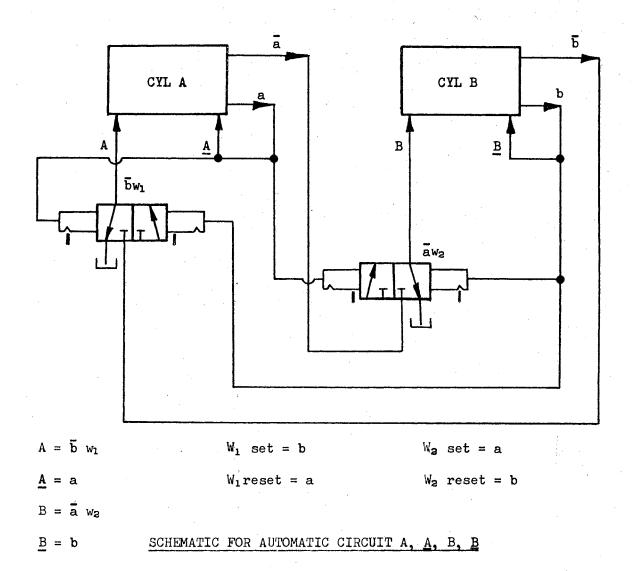

A very simple two-cylinder automatic circuit with feedback inputs is shown in Figure 9. Note that only shut-off valves are required in the control circuit. The

| NO | EVENT | ab | A                       | <u>A</u> | В                    | B                  | Wı      | Wg      |

|----|-------|----|-------------------------|----------|----------------------|--------------------|---------|---------|

| 1  | A     | 00 | ์<br>bิพ <sub>่</sub> า | 0 = ā    | $0 = \overline{w}_2$ | $0 = \overline{b}$ | DET     | O = DET |

| 2  | A     | 10 | $0 = \overline{w}_1$    | a        | 0 = a                | 0 = b              | 0 = a   | a       |

| 3  | В     | 00 | 0 = <b>w</b> 1          | 0'= ā    | āwa                  | 0 = b              | O = DET | DET     |

| 4  | B     | 01 | 0 <b>=</b> b            | 0 = ā    | 0 = W2               | b                  | b       | 0 = b   |

### OPERATIONS TABLE

Figure 9. Schematic for Automatic Circuit A, <u>A</u>, B, <u>B</u>

circuit equations are written immediately below the schematic. These equations are obtained directly from the schematic simply by labeling the lines and valves with logic notation and then determining the combinations that result in actuation signals. After the equations are obtained, the circuit operation can be verified by filling out the operations table as shown at the bottom of the figure.

A distinguishing feature of this circuit is that the signal which switches on at the completion of an event goes directly through a prepared path to activate the next event in the sequence. For example, at the completion of event number 2, the retraction of cylinder A, signal  $\bar{a}$  is turned on. Signal  $\bar{a}$  passes through the open valve  $W_2$  which was opened at the beginning of event number 2. Thus, the start of event number 3 is triggered in the minimum possible time. Had signal  $\bar{a}$  been required to combine with another signal, there would have been a delay while this combination took place. In addition to its fast action, this circuit contains only two control valves and is the simplest circuit that could be used to perform the control function.

One more interesting observation should be made about this circuit. The shut-off valve is not normally considered to be a logic element in that it does not perform in the classical sense. Circuits synthesized by the classical methods would not contain such an element. Yet it is

not possible to design a circuit with classical logic devices which is faster acting or has less values. The conclusion is that the memory shut-off function is a desirable feature, at least in the circuit just discussed, and could possibly be used effectively in more complicated circuits.

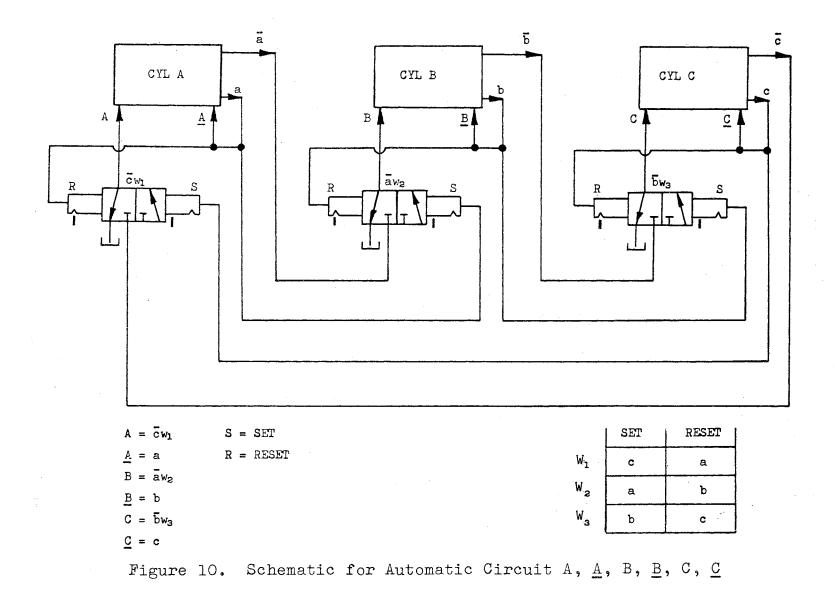

A slightly more complex automatic circuit is shown in Figure 10. Here, three cylinders are involved and an additional control valve is used. Again, the circuit equations are obtained and the operation verified in Table I. The comments made about Figure 9 also apply to this circuit.

Although the entire spectrum of circuit behavior is contained in the operations table, a clearer insight about what is taking place can be obtained by omitting some of the information and building up a table that is logically equivalent to the actual circuit diagram. Such a table for the circuit of Figure 9 is shown in Table II. The first three columns of this table are identical to those of the corresponding operations table. The fourth column labeled CS contains the signal which switches on at the completion of the previous event. For example, at the completion of event number 1, signal a appears and is entered in column 4 in row 2.

Now, in every case, the changed signal is the command signal for the event that is to occur. In the second row, signal a is commanding cylinder A to retract. However, as shown by the states in the input column, signal  $\overline{b}$  is

| TABLE | I |

|-------|---|

|-------|---|

OPERATIONS TABLE FOR AUTOMATIC CIRCUIT A, A, B, B, C, C

| No. | EVENT | abc | A                      | A     | B                    | B                      | С                    | <u>C</u>           | Wl      | Wg      | Wg      |

|-----|-------|-----|------------------------|-------|----------------------|------------------------|----------------------|--------------------|---------|---------|---------|

| 1   | A     | 000 | ēwı                    | 0 = ā | 0 = w <sub>2</sub>   | 0 = 5                  | 0 = w <sub>3</sub>   | $0 = \overline{c}$ | DET     | O = DET | O = DET |

| 2   | A     | 100 | $O = \overline{w}_{l}$ | а     | 0 = a                | 0 = <b>b</b>           | $0 = \overline{w}_3$ | 0 = <del>c</del>   | 0 = a   | a       | O = DET |

| 3.  | В     | 000 | $O = \overline{w}_1$   | 0 = ā | ā w <sub>2</sub>     | 0 = b                  | 0 = w <sub>3</sub>   | $0 = \overline{c}$ | O = DET | DET     | O = DET |

| 4   | B     | 010 | $O = \overline{w}_1$   | 0 = ā | $0 = \overline{w}_2$ | Ъ                      | 0 = b                | $0 = \overline{c}$ | O = DET | 0 = b   | b       |

| 5   | С     | 000 | $O = \overline{w}_1$   | 0 = ā | $0 = \overline{w}_2$ | $\vec{\mathbf{d}} = 0$ | δw <sub>3</sub>      | $0 = \overline{c}$ | O = DET | O = DET | DET     |

| 6   | C     | 001 | 0 = c                  | 0 = ā | $0 = \overline{W}_2$ | 0 = b                  | 0 = w <sub>3</sub>   | с                  | c       | O = DET | 0 = c   |

# TABLE II

# TABULAR DISPLAY OF STRUCTURE OF AUTOMATIC CIRCUIT A, <u>A</u>, <u>B</u>, <u>B</u>

| Event<br>No. | Event | Inputs<br>a b | cs | Shut<br>Off    | Shut Off<br>Set | Shut Off<br>Reset |

|--------------|-------|---------------|----|----------------|-----------------|-------------------|

| 1            | A     | 00            | ชื | ¥<br>W1        | b               | a                 |

| 2            | A     | 10            | a  | R<br>S         | 14              |                   |

| 3            | В     | 00            | â  | ₩ <sub>2</sub> | a               | đ                 |

| 4            | B     | 01            | b  | RS             |                 |                   |

simultaneously commanding cylinder A to continue to extend and, thus, a contradiction exists. To eliminate this undesirable situation, a shut-off valve,  $W_1$ , is placed in the  $\overline{b}$  signal line. Now signal a directs cylinder A to retract and at the same time cuts off the opposing signal  $\overline{b}$ , venting the A extend side of the power control valve to tank. When the next signal  $\overline{a}$  comes on, it will have to pass through valve  $W_2$  before it can reach the power control valve for cylinder B. Therefore, signal a sets or opens  $W_2$  at the same time it shuts off  $W_1$ . Likewise, signal b turns off or resets  $W_2$  while opening  $W_1$ . The arrows indicate the action on the W valves. An arrow pointing down sets the valve while an arrow pointing up indicates a reset command.

The last two columns are a tabular equivalency of the arrows. In row 1, b is entered in the sixth column to indicate that signal b opens value  $W_1$ , while in the last column and row 1, the lower case a indicates the shut-off or reset signal for  $W_1$ .

It must be noted that a delay in switching the power control valve can occur while the actuating signal cuts off the opposing signal. However, this delay is less than that which results from combining input signals. This is because the new actuating signal is already acting on the power control valve as it switches the shut-off valve. In the combined signal situation, the new signal must actuate a combination element before a resulting signal can act on

the power control valve.

Table III is a tabular display of the logic structure of the circuit of Figure 10. Again, this model clearly shows where the shut-off valves are needed to eliminate signal opposition and indicates the signals which are used to set and reset the shut-off valves.

The two tabular displays were constructed using information from existing automatic sequencing circuits and reveal in logic notation the circuit structure. However, the real significance is that these tables could have been used to synthesize the circuits if only the sequential specifications were known. For example, the first four columns can be completed with information implicitly contained in the specification. Now, assuming that the CS column signals are all that are required to activate events in the same rows, signal contradictions become When a contradiction occurs, a W valve is rerevealed. quired to shut off the opposing signal. After the number of W valves are established, the problem is to select signals which will appropriately set and reset these valves.

Thus, recognition of the role which shut-off valves play in an automatic fluid logic circuit and establishment of a criterion for systematically selecting these valves are considered important steps in the development of a synthesis procedure. Next, a more complicated sequential circuit will be investigated to establish further

# TABLE III

# TABULAR DISPLAY OF STRUCTURE OF AUTOMATIC CIRCUIT A, <u>A</u>, B, <u>B</u>, C, <u>C</u>

| Event<br>No. | Event | Inputs<br>abc | CS  | Shut<br>Off    | Shut Off<br>Set | Shut Off<br>Reset |

|--------------|-------|---------------|-----|----------------|-----------------|-------------------|

| 1            | A     | 000           | i c | ¥<br>₩ı        | C               | a                 |

| 2            | A     | 100           | a — | RS             |                 |                   |

| 3            | в     | 000           | a   | W2             | a               | Ъ                 |

| 4            | B     | 010           | b — | R<br>S         |                 |                   |

| 5            | C     | 000           | ้อิ | ₩ <sub>3</sub> | b               | с                 |

| 6            | Ē     | 001           | c   | RS             |                 |                   |

desirable features.

An intuitively designed automatic circuit with the sequence A, B,  $\underline{B}$ ,  $\underline{A}$ ,  $\underline{B}$ , A,  $\underline{A}$ ,  $\underline{B}$  is shown in Figure 11. The circuit is labeled so that the equations can be written in Boolean Algebra notation. The output equations are as follow:

$A = \overline{a}(\overline{by_4} \ \overline{ay_1} + \overline{b} \ \overline{y_3} \ \overline{a} \ \overline{y_1}) = \overline{aby_1} \ \overline{y_4} + \overline{a} \ \overline{b} \ \overline{y_1} \ \overline{y_3}$   $A = a \ \overline{y_2}$   $B = \overline{b}(\overline{a} \ y_1 \ \overline{b} \ y_3 + a \ y_2 \ \overline{b} \ \overline{y_3}) = \overline{a} \ \overline{b} \ y_1 \ y_3 + a \ \overline{b} \ y_2 \ \overline{y_3}$   $\underline{B} = b \ y_4$

The equations for memory valve operation are tabulated below:

| SECONDARY  | SET                | RESET                |

|------------|--------------------|----------------------|

| Yl         | b y3               | b a $\overline{y_2}$ |

| У <b>2</b> | b y3               | b y3                 |

| Y3         | a b y <sub>4</sub> | ā yı                 |

| Y <b>4</b> | ā y <sub>1</sub>   | a yı                 |

An operations table can now be prepared to verify the proper sequential operation of the circuit. This table is shown in Table IV. The table is started by listing the number and associated event in the first two columns. The states of the inputs are listed in the third column. The state of the input in each row represents the stabilized condition of the inputs at the completion of the previous

# TABLE IV

| OPERATIONS | TABLE | FOR  | INTU          | ITI | VELY | DE | SIC | INED | AUTOMATIC | CIRCUIT |  |

|------------|-------|------|---------------|-----|------|----|-----|------|-----------|---------|--|

|            |       | A, 1 | З, <u>В</u> , | A,  | В, . | A, | Α,  | В    |           |         |  |

| No . | EVENT | ab | A                               | A                  | В                               | B                    | Yı                       | Yz                    | Υ <sub>3</sub>                   | Y <sub>4</sub>        |

|------|-------|----|---------------------------------|--------------------|---------------------------------|----------------------|--------------------------|-----------------------|----------------------------------|-----------------------|

| 1    | A     | 00 | aby <sub>1</sub> y3             | 0 = À <sup>s</sup> | $0 = \overline{ay_1}$           | d = 0                | O = DET                  | ັ້ນ yັ <sub>ື່ງ</sub> | $0 = \overline{a}\overline{y}_1$ | ā yī                  |

| 2    | В     | 10 | 0 = a                           | 0 = JS             | aby <sub>2</sub> y <sub>3</sub> | d = 0                | O = DET                  | ້b y <sub>ື</sub>     | O = DET                          | DET                   |

| 3    | B     | 11 | 0 = a                           | 0 = y2             | 0 = b                           | by4                  | O = DET                  | DET                   | aby <sub>4</sub>                 | DET                   |

| 4.   | A     | 10 | 0 = a                           | a y <sub>2</sub>   | 0 = ay <sub>3</sub>             | d ≈ 0                | b y <sub>3</sub>         | 0 = b y <sub>3</sub>  | DET                              | DET                   |

| 5    | В     | 00 | 0 = by <sub>3</sub>             | 0 = a              | aby <sub>1</sub> y <sub>3</sub> | $0 = \overline{y}_4$ | ົ້ວ y <sub>3</sub>       | 0 = by <sub>3</sub>   | DET                              | $0 = \overline{ay_1}$ |

| 6    | A     | Ol | aby <sub>1</sub> y <sub>4</sub> | 0 = a              | 0 = b                           | 0 = y <sub>4</sub>   | DET                      | O = DET               | DET                              | 0 = ā y <sub>1</sub>  |

| 7    | A     | 11 | 0 = a                           | a y <sub>e</sub>   | d = 0                           | $0 = \overline{y}_4$ | $0 = ab\overline{y}_{2}$ | 0 = DET               | DET                              | O = DET               |

| 8    | B     | 01 | $0 = by_4$                      | 0 = y2             | 0 = b                           | b y <sub>4</sub>     | O = DET                  | O = DET               | 0 = ā y <sub>1</sub>             | a y <sub>1</sub>      |

event. For example, in row 3, the desired event is for Cylinder B to retract. The input signals which are available to help accomplish the desired event are a = 1 and b = 1.

The next four columns of the table provide space for the equations which produce the desired outputs of the circuit. The last four columns are allocated to the equations associated with the secondaries or memory valves. Now, the table is ready to receive the circuit operation equations.

An explanation of how this table is filled out is in order since the circuit is considerably more complicated than the previously discussed circuits. In this case, it is necessary to work with the circuit schematic as well as with the algebraic equations, particularly in establishing which elements provide the tanking functions for the outputs which must be off.

Looking at row 1, it is apparent that the first desired event is for Cylinder A to extend. It is assumed at this point that a = 0 and b = 0 and that the memory valves are in their required positions. (These assumptions will be verified as the table is filled out, providing the circuit is actually designed to perform the desired sequence. Otherwise, the table will contain contradictions which show that the circuit will not work.) Now referring to the output equations, it is obvious that the only possible combination of signals and memory valve

positions which will permit Cylinder A to extend is  $\overline{a} \ \overline{b} \ \overline{y_1} \ \overline{y_3}$ . Therefore, this combination is entered in row 1 in the column A. Secondaries Y<sub>1</sub> and Y<sub>3</sub> must both be zero or in the "reset" position. From the tabulated memory valve operation equations, it can be seen that no set or reset signal is acting on Y<sub>1</sub>. Thus, the detent must be holding Y<sub>1</sub> in the reset position and "O = DET" is accordingly entered in row 1 and column Y<sub>1</sub>. Looking at Y<sub>3</sub> and the tabulated equations, one can see that the signal  $\overline{a} \ \overline{y_1}$ is acting to reset Y<sub>3</sub>. Accordingly O =  $\overline{a} \ \overline{y_1}$  is entered in row 1 and column Y<sub>3</sub>. Similarly, the combination  $\overline{b} \ \overline{y_3}$  indicates that memory valve Y<sub>2</sub> is in the "set" or "on" position and  $\overline{a} \ \overline{y_1}$  indicates that Y<sub>4</sub> is also set.

Since the desired output is A, the output <u>A</u> must be off and vented to tank. By looking at the equation  $\underline{A} = a \ \overline{y}_2$  and the circuit, it is seen that this condition is satisfied by  $\underline{Y}_2$  being in the set position. Thus,  $O = \underline{y}_2$  is entered in row 1 and column <u>A</u>. Output B must also be off because Cylinder B is to remain retracted until A has completely extended. Both parts of the right side of the equation  $B = \overline{a} \ \overline{b} \ y_1 y_3 + a \ \overline{b} \ y_2 \ \overline{y}_3$  must be zero to satisfy this condition. Since a = 0 and b = 0,  $y_1$  or  $y_3$  must be zero to make the first part zero. From row 1 of the table,  $y_1$  and  $y_3$  are both found to be zero, which takes care of the first part of the equation. The second part is also zero because a = 0. Therefore, the variables  $\overline{a}$  and  $\overline{y}_1$  are sufficient to prevent an output B. The

equation  $0 = \bar{a} \bar{y}_1$  is entered in the first row and column B. It does not matter whether the output signal <u>B</u> is on or not during the extension of cylinder A. However, <u>B</u> = 0 because b = 0 and "0 = 5" is entered under <u>B</u> in row 1.

The first row of the table is now complete. The next step is to establish the states of the memory values in the second row. First, it is established that  $Y_4$  could not have switched at the completion of the extension of Cylinder A and  $Y_4$  remains in the "set" position because of the detent. "DET" is entered under  $Y_4$  in row 2. This information is then used with the stabilized states of the inputs to show that  $Y_3$  is being held in the "reset" position by the detent. In turn, the conditions of  $Y_1$  and  $Y_2$ are likewise established and the entries are accordingly made in the table.

After the states of the secondaries are determined for row 2, the output conditions can be found, completing the second row of the table. The third and subsequent rows are filled out by a similar procedure until the table is complete. The last row is checked to verify that it is compatible with the first row where the assumptions were made concerning the initial states of the memory values.

As can be seen from Table IV, all of the output and memory valve operation conditions are satisfied. This confirms that the circuit will automatically operate in the specified sequential manner. It should be obvious from the preceding that the operations table is a very

powerful tool for analyzing and checking out an existing circuit. To have checked this circuit any other way would have been extremely difficult, especially if there had been something wrong with the circuit.

There are some interesting features of the circuit just analyzed which can best be shown in a tabular display similar to those made for the previous circuits. The first three columns of Table V are the same as the first three columns of the operations table (Table IV). The fourth column shows the signal which changed at the completion of the previous event. The last column contains the signal which was actually used to initiate the event in the same row.

In the first row, the new signal is  $\overline{b}$  and the signal used to command cylinder A to extend is  $\overline{a} \ \overline{y}_1 \cdot \overline{b} \ \overline{y}_3$ . From the operations table it is apparent that the  $\overline{a} \ \overline{y}_1$  signal is already on and the Y<sub>3</sub> value is in the reset position. The circuit diagram shows that when  $\overline{b}$  comes on, it is gated through Y<sub>3</sub> and opens a check value "and" gate to let the  $\overline{a} \ \overline{y}_1$  signal pass and act on the power control value. Note that there is a delay which occurs when the  $\overline{b} \ \overline{y}_3$ signal opens the "and" gate. Had the  $\overline{b} \ \overline{y}_3$  signal gone directly to act on the power control value, there would be no delay. A similar situation occurs in rows 2, 5, and 6.

In row 4, the new signal is  $\overline{b}$  while the output signal is a  $\overline{y}_2$ . The operations table shows that signal  $\overline{b}$  is gated through  $Y_3$  and resets  $Y_2$ . Again, a delay results

#### TABLE V

# TABULAR DISPLAY OF PARTIAL STRUCTURE OF INTUITIVELY DESIGNED SEQUENTIAL CIRCUIT A, B, B, A, B, A, A, B

| No . | Event | Inputs<br>a b | CS | Signal Used                       |

|------|-------|---------------|----|-----------------------------------|

| 1    | A     | 0 0           | ซี | ayı • by <sub>a</sub>             |

| 2    | В     | 10            | a  | ayə ° by <sub>3</sub>             |

| 3    | B     | 11            | ъ  | (by4)                             |

| 4    | A     | 10            | Б  | ayz                               |

| 5    | В     | 0 0           | ā  | ayı ° by <sub>a</sub>             |

| 6    | A     | 01            | b  | ay <sub>1</sub> • by <sub>4</sub> |

| 7    | A     | 11            | a  | aya                               |

| 8    | B     | 01            | a  | by <sub>4</sub>                   |

while value  $Y_2$  is reset. This condition is repeated in row 8.

In rows 3 and 7 the output signals are circled. Note that the changed signal b in row 3 is directly involved in generating the output signal. The operations table shows that valve  $Y_4$  was in the "set" state before b came on. Thus, signal b is gated through  $Y_4$  and goes immediately to shift the power control valve. Likewise, in row 7, signal a goes directly through a prepared path to act on the power valve.

Summarizing, there are six delays built into the logic circuit. These occur when one signal has to combine with another to produce an output. In two instances, (rows 4 and 8) the memory valves are shifted while the input ports are pressurized. The most desirable output signals are circled in rows 3 and 7. In each case here, there is no delay because the event completion signal is guided through a pre-set memory valve directly to activate the next event.

Two desirable features of well-designed circuits were brought out in this chapter. These are the use of the shut-off valves to eliminate signal oppositions and the presetting of Y valves to avoid signal transmission delays. The next chapter will show how these features can be incorporated into circuits during synthesis.

#### CHAPTER V

#### DEVELOPMENT OF SYNTHESIS PROCEDURE

#### Initial Development

The objective of the following synthesis efforts will be to force the circuits to contain the same desirable features as the example circuits of Chapter IV.

The last example will be used as a starting point. A preliminary synthesis table is shown in Table VI. The first four columns contain the same information as the tabular display in Table V. This time, however, an attempt will be made to always use the changed input signal to start the next event. Looking at the fourth column from the left, one can see that signal 5 associates with event A in row 1 and with  $\underline{A}$  in row 4. That is,  $\overline{b}$  is the signal which commands these events to occur. Therefore, in the next column (Associated Events) A, A is entered. An arrow is drawn from  $\overline{\mathtt{b}}$  to  $\mathtt{A}, \underline{\mathtt{A}}$  to show the relationship. Since signal b is asked to go to two different places at different intervals of the sequence, a memory gating valve is The last column contains the signal and memory needed. valve combination. In row 1, the combination is b y, , and in row 4 the combination becomes  $\overline{b}$   $\overline{y}_1$ . Between events 1

#### TABLE VI

## PRELIMINARY SYNTHESIS TABLE I FOR AUTOMATIC CIRCUIT A, B, <u>B</u>, <u>A</u>, B, A, <u>A</u>, <u>B</u>

| No . | Event | Inputs | I (Changed Input) | II (Assoc. Events) | *III             |

|------|-------|--------|-------------------|--------------------|------------------|

| l    | A     | āb     | ō                 | A, <u>A</u>        | Б у <sub>1</sub> |

| 2    | В     | a b    | a                 | ► B, <u>A</u>      | a y <sub>2</sub> |

| 3    | B     | ab     | b —               | — <u>—</u> B, A    | b y <sub>3</sub> |

| 4    | A     | аЪ     | ັ້ນ.              |                    | b yı             |

| 5    | В     | āb     | ā                 | → B, B             | āy4              |

| 6    | A     | ā b    | b                 |                    | b y <sub>3</sub> |

| 7    | A     | ab     | a                 |                    | a y <sub>2</sub> |

| 8    | B     | āb     | ä                 |                    | ā y4             |

\*III Changed input signal and memory valve combination.

and 4, the memory value  $Y_1$  will have to shift from "set" to "reset".

Similarly, events are associated with the remaining input signals and memory gating values assigned to properly distribute the signals. The last column shows that four memory values or Y values are required. Note that at least two events occur before a particular Y value changes from its previous state to a new state. For example, in row 3, Y<sub>3</sub> is in the set state and in row 6, Y<sub>3</sub> is required to be in the reset state. Thus, there are two opportunities to change the state of Y<sub>3</sub> between events 3 and 6. More will be said about this later.

It is now necessary to check the output signal combinations in the last column for contradictions. This is done by examining each event in the sequence and checking to see if an output signal which would cause the negation of the event is still on. This amounts to checking the output signal associated with the most recent negation of the event. For example, in row 1, the output combination is b y<sub>1</sub>, commanding event A to occur. The most recent negation was row 7 where the signal was a  $\overline{y}_2$ . It can be seen from the input combination in row 1, that signal a is off and signal a  $\overline{y}_2$  must consequently be off. Thus, there is no conflict. Likewise, row 2 shows no conflict with row 8. However, rows 2 and 3 are found to represent a contradiction, with signal a y2 still commanding cylinder B to extend while signal b y; orders cylinder B to retract.

Therefore, signal a  $y_2$  must be cut off before cylinder B can retract. Accordingly, a shut off value is added.