### UNIVERSITY OF OKLAHOMA GRADUATE COLLEGE

### SELF-PACKAGED AND LOW-LOSS SUSPENDED INTEGRATED STRIPLINE FILTERS FOR NEXT GENERATION SYSTEMS

A DISSERTATION

#### SUBMITTED TO THE GRADUATE FACULTY

in partial fulfillment of the requirements for the

Degree of

### DOCTOR OF PHILOSOPHY

By

JAY MCDANIEL Norman, Oklahoma 2018

### SELF-PACKAGED AND LOW-LOSS SUSPENDED INTEGRATED STRIPLINE FILTERS FOR NEXT GENERATION SYSTEMS

# A DISSERTATION APPROVED FOR THE SCHOOL OF ELECTRICAL AND COMPUTER ENGINEERING

BY

Dr. Hjalti H. Sigmarsson, Chair

Dr. Mark B. Yeary, Co-Chair

Dr. Nathan A. Goodman

Dr. Caleb J. Fulton

Dr. Jeffrey B. Basara

© Copyright by JAY MCDANIEL 2018 All Rights Reserved. This dissertation is dedicated to my dear wife. None of this would have been possible without her sacrifices, unconditional love, and support.

### Acknowledgments

I would like to thank my Ph.D. advisor and chair, Dr. Hjalti H. Sigmarsson, for his endless support and encouragement throughout my Ph.D. studies. Professor Sigmarsson has taught me the invaluable importance of attention to detail in all aspects of conducting research. I have had the opportunity to see his fiery passion for the academic field and commitment to excellence in both his teaching and research practices, which I hope to carry over into my academic career. I cannot thank him enough for continuously providing ample advice to grow myself as a professional and helping me ultimately achieve my goal of becoming an Assistant Professor. But above all else, the friendship between professor Sigmarrson and I is one of the greatest take-aways from this experience and hopefully just the beginning of many years of exciting collaborations.

My Ph.D. co-chair, Dr. Mark B. Yeary, also deserves my deepest gratitude. Professor Yeary has challenged me to go way beyond my technical comfort zone and broaden my understanding and appreciation for both the hardware and digital side of next generation systems. He has also continuously supported my desire to become an Assistant Professor and has put-forth a tremendous effort to get me prepared for a successful career.

I am forever grateful to the Department of Energy's Kansas City National Security Campus, operated by Honeywell Federal Manufacturing & Technologies and the Radar 2021 consortium PDRD, that supported my Ph.D. research. Furthermore, a special thanks to the executive director of the Advanced Radar Research Center (ARRC), Dr. Robert D. Palmer. I would also like to thank all of the staff members of ARRC as well as the School of Electrical and Computer Engineering at the University of Oklahoma.

I would like to extend my thanks to all of my colleagues at the ARRC and a special thanks to Dr. Shahrokh Saeedi, Christopher Walker, and Paul Boydstun who have helped me tremendously in fabrication and bringing my designs to reality. I wish them all the best of luck in their future careers and academic studies.

I also thank my father, Gary McDaniel, and grandmother, Marjorie Mc-Daniel, for their continued support throughout my many years of education. Their sacrifices and encouragement over the years to help me pursue my passion has been more than I could have ever asked for. I can not thank them enough. An extended thanks to my in-laws, Leonard and Susan Zalenski, for not only helping us put together a plan and executing it, but also helping my wife and I make the transition from Kansas to Oklahoma. They have continuously provided guidance and a helping hand when needed.

Last, I thank my wife, Kathryn, for her unfailing support and sacrifices over the last several years. Kathryn has not only provided me with an opportunity to pursue my passion, but has simultaneously excelled in her own career as a chemical engineer. She has constantly been there to offer words of encouragement when I was struggling with research and there to celebrate during times of success. My gratitude to her is more than can be expressed in words and I only hope that I can repay her for her support and sacrifices many times over.

### Table of Contents

| $\mathbf{A}$ | Acknowledgments |         | $\mathbf{iv}$                               |     |

|--------------|-----------------|---------|---------------------------------------------|-----|

| A            | Abstract        |         |                                             | xxi |

| 1            | Intr            | roducti | ion                                         | 1   |

|              | 1.1             | Motiva  | ation                                       | 1   |

|              | 1.2             | Filter  | Impact on Systems: SWaP vs. Sensitivity     | 3   |

|              | 1.3             | Histor  | y of Low Loss Filter Integration            | 11  |

|              | 1.4             | Resear  | rch Objective                               | 23  |

|              | 1.5             | Outlin  | ne of the Dissertation                      | 24  |

| <b>2</b>     | Full            | ly-Boa  | rd Embedded SISL Technology                 | 27  |

|              | 2.1             | SISL I  | Design and Implementation                   | 27  |

|              |                 | 2.1.1   | Material Stack-up                           | 34  |

|              |                 | 2.1.2   | CPWG Design                                 | 36  |

|              |                 | 2.1.3   | Stripline Design                            | 42  |

|              |                 | 2.1.4   | Vertical Via Transition Design              | 44  |

|              |                 | 2.1.5   | Effective Relative Permittivity & ADS Model | 52  |

|              |                 | 2.1.6   | DC-20 GHz SISL Thru-Line Design             | 58  |

|              |                 | 2.1.7   | SISL Air Cavity Tuning                      | 59  |

|              | 2.2             | DC-20   | ) GHz SISL Thru-line Simulations            | 62  |

|          | 2.3                                                       | Layou                                                                          | t File Generation                                                                                                                                                                                            | 63                                                                                                                 |

|----------|-----------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

|          | 2.4                                                       | Device                                                                         | e Fabrication Procedure                                                                                                                                                                                      | 64                                                                                                                 |

|          | 2.5                                                       | Measu                                                                          | ured Results                                                                                                                                                                                                 | 65                                                                                                                 |

| 3        | Sus                                                       | pendeo                                                                         | d Integrated Stripline Lowpass Filter                                                                                                                                                                        | 68                                                                                                                 |

|          | 3.1                                                       | SISL I                                                                         | LPF Design                                                                                                                                                                                                   | 68                                                                                                                 |

|          |                                                           | 3.1.1                                                                          | Filter Characteristics                                                                                                                                                                                       | 71                                                                                                                 |

|          |                                                           | 3.1.2                                                                          | Ideal LC Model                                                                                                                                                                                               | 74                                                                                                                 |

|          |                                                           | 3.1.3                                                                          | Distributed LPF Design Equations                                                                                                                                                                             | 76                                                                                                                 |

|          |                                                           | 3.1.4                                                                          | ADS and HFSS Simulations of the SISL LPF $\ . \ . \ .$ .                                                                                                                                                     | 84                                                                                                                 |

|          |                                                           | 3.1.5                                                                          | DC-18 GHz SISL LPF and Air Cavity Tuning                                                                                                                                                                     | 90                                                                                                                 |

|          | 3.2                                                       | DC-18                                                                          | GHz SISL LPF Simulations                                                                                                                                                                                     | 92                                                                                                                 |

|          | 3.3                                                       | Layou                                                                          | t File Generation and Device Fabrication                                                                                                                                                                     | 95                                                                                                                 |

|          | 3.4                                                       | Measu                                                                          | red Results                                                                                                                                                                                                  | 96                                                                                                                 |

|          |                                                           |                                                                                |                                                                                                                                                                                                              |                                                                                                                    |

| <b>4</b> | Sus                                                       | pendeo                                                                         | d Integrated Stripline Highpass Filter                                                                                                                                                                       | 100                                                                                                                |

| 4        | <b>Sus</b><br>4.1                                         | -                                                                              | d Integrated Stripline Highpass Filter                                                                                                                                                                       | <b>100</b><br>100                                                                                                  |

| 4        |                                                           | -                                                                              |                                                                                                                                                                                                              |                                                                                                                    |

| 4        |                                                           | SISL I                                                                         | HPF Design                                                                                                                                                                                                   | 100                                                                                                                |

| 4        |                                                           | SISL 1<br>4.1.1                                                                | HPF Design   Filter Characteristics                                                                                                                                                                          | 100<br>103                                                                                                         |

| 4        |                                                           | SISL 1<br>4.1.1<br>4.1.2                                                       | HPF Design       Filter Characteristics       Ideal LC Model                                                                                                                                                 | 100<br>103<br>106<br>108                                                                                           |

| 4        |                                                           | SISL 1<br>4.1.1<br>4.1.2<br>4.1.3                                              | HPF Design          Filter Characteristics          Ideal LC Model          Distributed HPF Design Equations                                                                                                 | 100<br>103<br>106<br>108                                                                                           |

| 4        |                                                           | SISL 1<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5                            | HPF Design          Filter Characteristics          Ideal LC Model          Distributed HPF Design Equations          ADS and HFSS Simulations of the SISL HPF                                               | 100<br>103<br>106<br>108<br>115                                                                                    |

| 4        | 4.1                                                       | SISL 1<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>2 GHz                   | HPF Design          Filter Characteristics          Ideal LC Model          Distributed HPF Design Equations          ADS and HFSS Simulations of the SISL HPF          2 GHz SISL HPF and Air Cavity Tuning | <ol> <li>100</li> <li>103</li> <li>106</li> <li>108</li> <li>115</li> <li>121</li> </ol>                           |

| 4        | 4.1                                                       | SISL 1<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>2 GHz<br>Layou          | HPF Design                                                                                                                                                                                                   | <ol> <li>100</li> <li>103</li> <li>106</li> <li>108</li> <li>115</li> <li>121</li> <li>126</li> </ol>              |

| 4        | <ul><li>4.1</li><li>4.2</li><li>4.3</li><li>4.4</li></ul> | SISL 1<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>2 GHz<br>Layou<br>Measu | HPF Design                                                                                                                                                                                                   | <ol> <li>100</li> <li>103</li> <li>106</li> <li>108</li> <li>115</li> <li>121</li> <li>126</li> <li>127</li> </ol> |

|              |       | 5.1.1  | Stripline Trace for Internal Cascade     | 132 |

|--------------|-------|--------|------------------------------------------|-----|

|              | 5.2   | 2-18 0 | GHz SISL BPF Simulations                 | 134 |

|              | 5.3   | Layou  | t File Generation and Device Fabrication | 136 |

|              | 5.4   | Measu  | red Results                              | 136 |

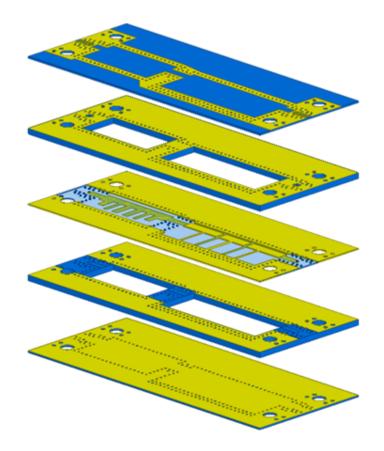

| 6            | Free  | quency | Scaling of SISL Design to Ka-band        | 138 |

|              | 6.1   | Ka-Ba  | and SISL Thru-line and Filter Design     | 138 |

|              |       | 6.1.1  | Ka-band Vertical Via Transition          | 141 |

|              |       | 6.1.2  | Ka-band SISL Thru-line Design            | 147 |

|              |       | 6.1.3  | Ka-band SISL Chebyshev LPF Design        | 148 |

|              |       | 6.1.4  | Ka-band SISL Chebyshev HPF Design        | 149 |

|              |       | 6.1.5  | Ka-band SISL Chebyshev BPF Design        | 151 |

|              | 6.2   | Simula | ated Results                             | 152 |

|              |       | 6.2.1  | Ka-band SISL Thru-line                   | 152 |

|              |       | 6.2.2  | Ka-band SISL Chebyshev LPF               | 153 |

|              |       | 6.2.3  | Ka-band SISL Chebyshev HPF               | 154 |

|              |       | 6.2.4  | Ka-band SISL Chebyshev BPF               | 155 |

| 7            | Sun   | nmary  | and Future Work                          | 157 |

|              | 7.1   | Summ   | ary                                      | 157 |

|              | 7.2   | Contri | ibutions                                 | 159 |

|              | 7.3   | Future | e Work                                   | 160 |

| $\mathbf{R}$ | efere | nces   |                                          | 164 |

| A            | ppen  | dix A  | Fabrication Process                      | 178 |

|              | A.1   | Detail | ed Fabrication Process                   | 179 |

|              |       | A.1.1  | Preparation                              | 180 |

| Appen | dix B       | List of Acronyms and Abbreviations | 189 |

|-------|-------------|------------------------------------|-----|

| A.2   | Fabric      | ation Procedure                    | 184 |

| 1.0   | <b>Б</b> Т. |                                    | 104 |

|       | A.1.7       | Individual Route                   | 183 |

|       | A.1.6       | Ground Vias                        | 183 |

|       | A.1.5       | Etch Copper Layer 1                | 183 |

|       | A.1.4       | Laminate Layers 1-5                | 182 |

|       | A.1.3       | Signal Via                         | 182 |

|       | A.1.2       | Laminate Layers 1-3                | 182 |

### List of Tables

| 1.1 | Comparison of filter technologies.                                                                         | 23  |

|-----|------------------------------------------------------------------------------------------------------------|-----|

| 2.1 | Calculated inductance and capacitance values for the vertical via transition equivalent LPF circuit model. | 48  |

| 3.1 | Calculated element values for an eleventh-order generalized Cheby                                          | _   |

|     | shev LPF prototype using an alternating-pole technique $\left[23\right]$ .                                 | 73  |

| 3.2 | Calculated normalized frequencies using an iterative Newton-                                               |     |

|     | Raphson technique [23].                                                                                    | 73  |

| 3.3 | Calculated inductance (nH) and capacitance (pF) values for the                                             |     |

|     | ideal LC circuit model                                                                                     | 74  |

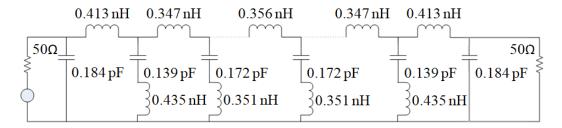

| 3.4 | LPF calculated distributed prototype parameters                                                            | 84  |

| 3.5 | Calculated edge effect lengths                                                                             | 87  |

| 3.6 | Final LPF distributed parameters                                                                           | 91  |

| 3.7 | Comparison of commercially available and academically researched                                           | ł   |

|     | LPFs to the proposed SISL LPF                                                                              | 98  |

| 4.1 | Calculated element values for an eleventh-order generalized Cheby                                          | -   |

|     | shev HPF prototype using an alternating-pole technique [23]                                                | 105 |

| 4.2 | Calculated normalized frequencies [23]                                                                     | 106 |

| 4.3 | Calculated inductance (nH) and capacitance (pF) values for the                                             |     |

|     | ideal LC circuit model                                                                                     | 107 |

|     |                                                                                                            |     |

| 4.4 | HPF calculated distributed prototype parameters | 114 |

|-----|-------------------------------------------------|-----|

| 4.5 | Final HPF distributed parameters                | 122 |

| 6.1 | Final LPF distributed parameters                | 149 |

| 6.2 | Final HPF distributed parameters.               | 150 |

## List of Figures

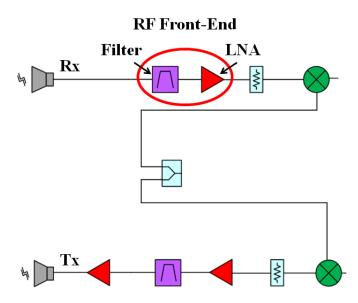

| 1.1  | Block diagram of a simple RF front-end                                              | 4  |

|------|-------------------------------------------------------------------------------------|----|

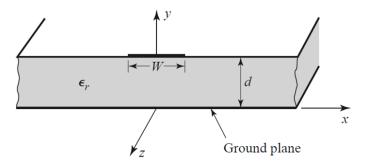

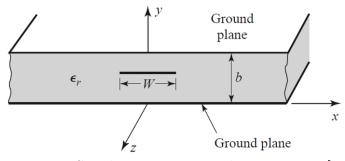

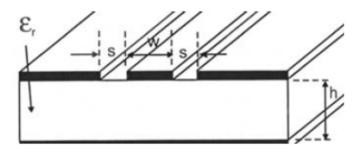

| 1.2  | Microstrip transmission line geometry [18]                                          | 6  |

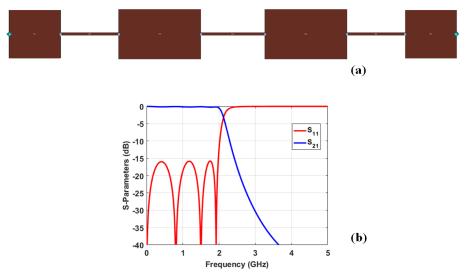

| 1.3  | Stepped impedance LPF (a) layout and (b) S-parameters                               | 6  |

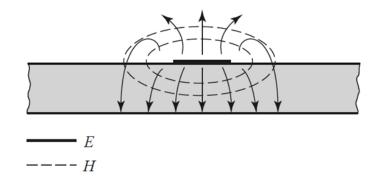

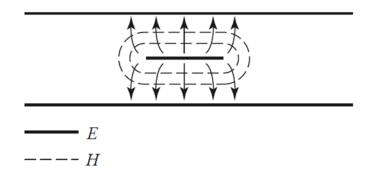

| 1.4  | Microstrip transmission line field distribution [18]                                | 7  |

| 1.5  | Stripline transmission line geometry [18]                                           | 7  |

| 1.6  | Stripline transmission line field distribution [18]                                 | 8  |

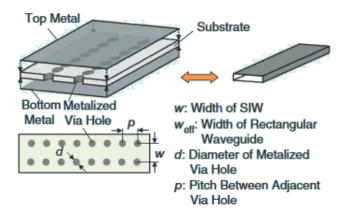

| 1.7  | SIW technology [22]. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 12 |

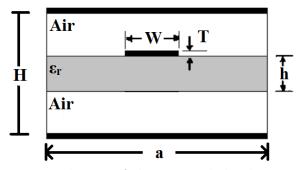

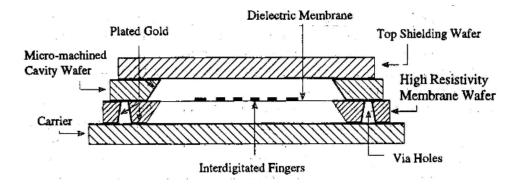

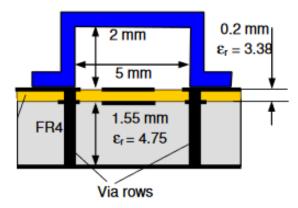

| 1.8  | Cross-sectional view of the suspended substrate stripline design.                   | 13 |

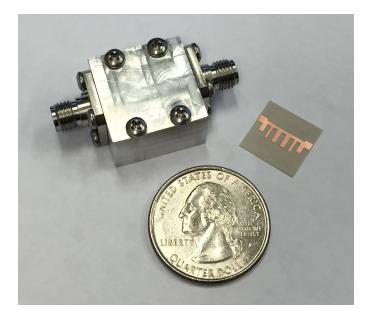

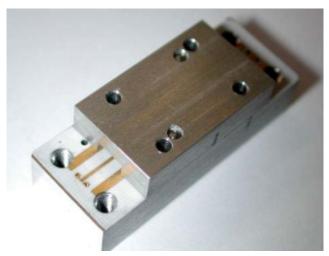

| 1.9  | Photograph of a suspended substrate stripline lowpass filter [46].                  | 15 |

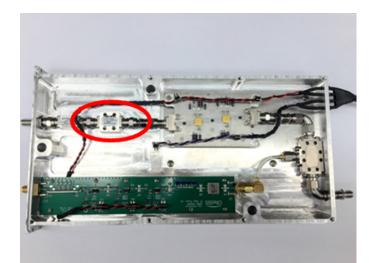

| 1.10 | Photograph of a connectorized radar receiver with SSS front-                        |    |

|      | end filter [49]                                                                     | 16 |

| 1.11 | Cross-sectional view of the microshield structure [51]                              | 17 |

| 1.12 | Cross-sectional view of the suspended stripline structure $[56].$ .                 | 18 |

| 1.13 | Cross-sectional view of the quasi-SSL structure [57]                                | 19 |

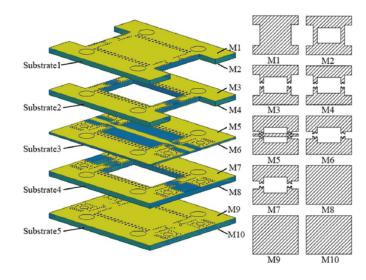

| 1.14 | 3-D view of the SISL stack-up [58]                                                  | 20 |

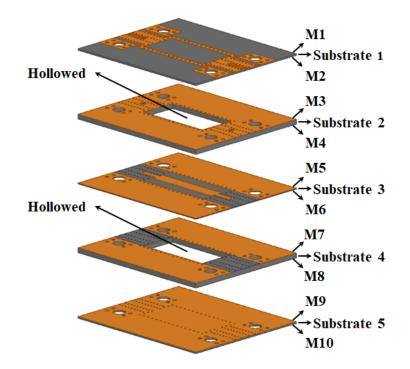

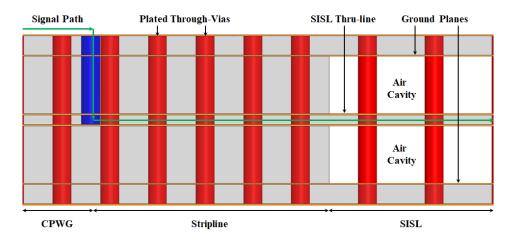

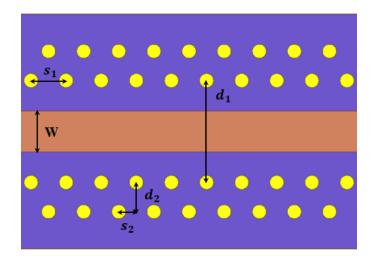

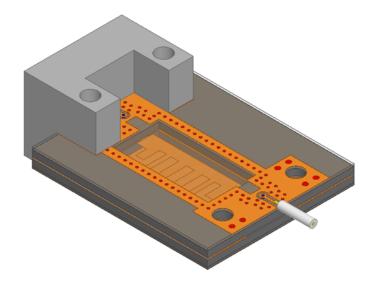

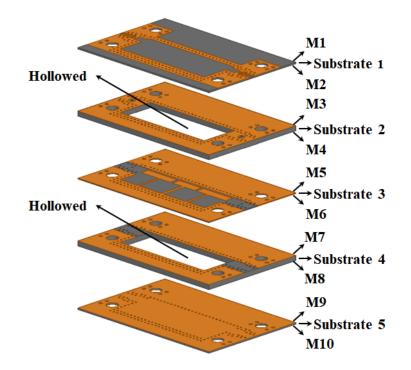

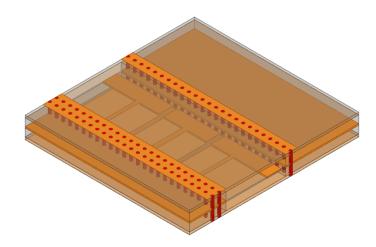

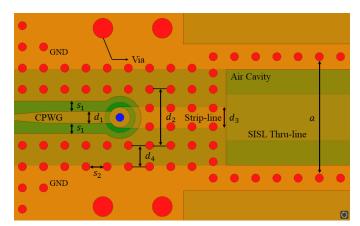

| 2.1  | 3-D exploded view of the proposed SISL technology                                   | 28 |

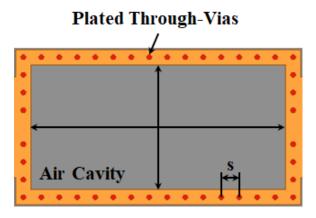

| 2.2  | Top-down view of the proposed SISL design to illustrate the                         |    |

|      | plated through-vias creating the metal side walls                                   | 29 |

| 2.3  | Side-view of the proposed SISL design to illustrate the CPWG-                       |    |

|      | to-stripline vertical via transition                                                | 29 |

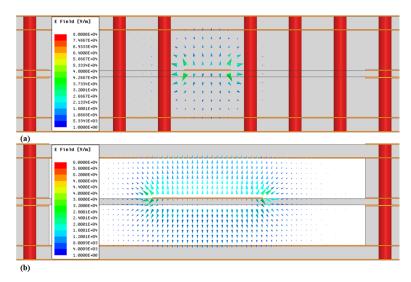

| 2.4  | Vector plot of the E-field in the (a) stripline and (b) suspended     |    |

|------|-----------------------------------------------------------------------|----|

|      | integrated stripline medium                                           | 30 |

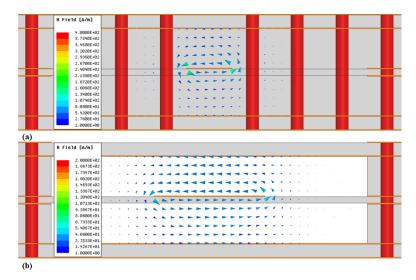

| 2.5  | Vector plot of the H-field in the (a) stripline and (b) suspended     |    |

|      | integrated stripline medium                                           | 30 |

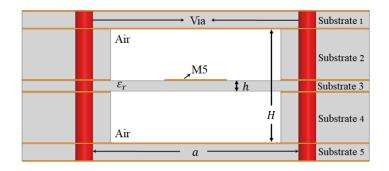

| 2.6  | Cross-sectional view of the proposed SISL design to further il-       |    |

|      | lustrate the waveguide-like structure                                 | 31 |

| 2.7  | Ground-Backed Coplanar Waveguide geometry [84]                        | 36 |

| 2.8  | Top-down view of the CPWG trace to illustrate design dimensions.      | 37 |

| 2.9  | HFSS model of the CPWG transmission line                              | 38 |

| 2.10 | Simulated S-parameters of the tuned CPWG transmission line.           | 38 |

| 2.11 | Zoom-in on the edge-launch connector transition                       | 39 |

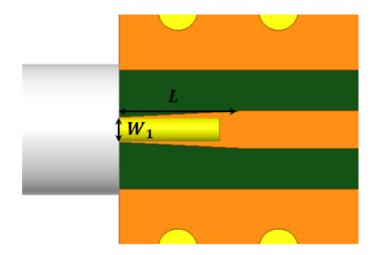

| 2.12 | Top-down view of the CPWG taper to illustrate taper dimensions.       | 40 |

| 2.13 | HFSS model of the CPWG transmission line with Southwest               |    |

|      | Microwave edge-launch connector                                       | 41 |

| 2.14 | Simulated S-parameters of the CPWG transmission line with             |    |

|      | edge-launch connector and taper compensation                          | 41 |

| 2.15 | Top-down view of the stripline trace to illustrate design dimen-      |    |

|      | sions                                                                 | 42 |

| 2.16 | HFSS model of the stripline transmission line                         | 43 |

| 2.17 | Simulated S-parameters of the stripline transmission line             | 44 |

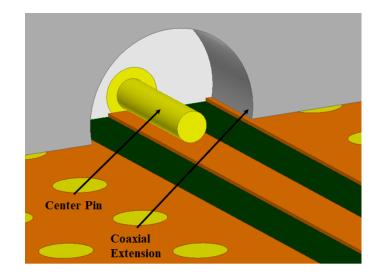

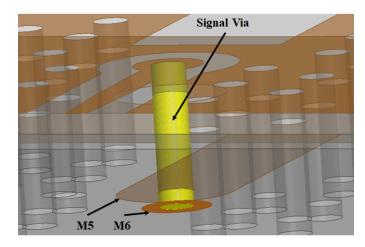

| 2.18 | 3-D view of the CPWG-to-stripline vertical via transition. $\ .$ .    | 44 |

| 2.19 | Bottom view of vertical via transition to illustrate stripline on     |    |

|      | M3 and via pad on M4                                                  | 45 |

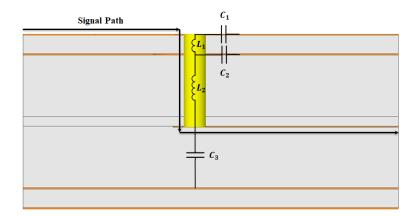

| 2.20 | Side-view of the CPWG-to-stripline vertical via transition to         |    |

|      | illustrate the associated inductances and capacitances. $\ . \ . \ .$ | 46 |

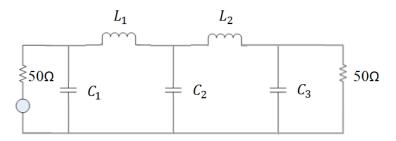

| 2.21 | Equivalent circuit model of the vertical via transition               | 47 |

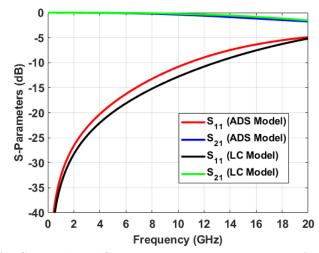

| 2.22 | ADS simulated S-parameters comparing the ADS multilayer            |    |

|------|--------------------------------------------------------------------|----|

|      | vertical via transition model and the LC equivalent circuit model. | 48 |

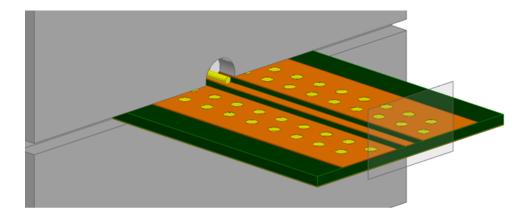

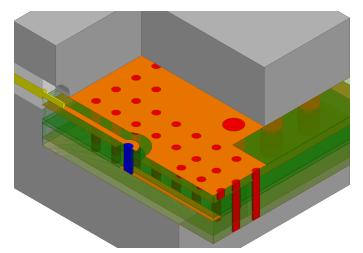

| 2.23 | 3-D view of a single CPWG-to-stripline vertical transition mod-    |    |

|      | eled in HFSS                                                       | 49 |

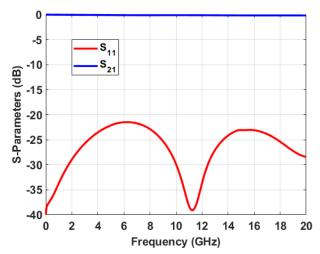

| 2.24 | Simulated S-parameters comparing the HFSS multilayer ver-          |    |

|      | tical via transition model and the ADS LC equivalent circuit       |    |

|      | model with CPWG and stripline traces                               | 50 |

| 2.25 | Simulated S-parameters comparing the tuned HFSS multilayer         |    |

|      | vertical via transition model and the tuned ADS LC equivalent      |    |

|      | circuit model                                                      | 51 |

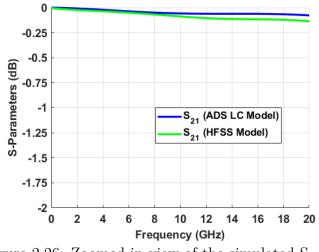

| 2.26 | Zoomed-in view of the simulated $S_{21}$ plots                     | 51 |

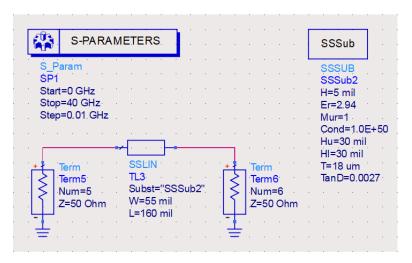

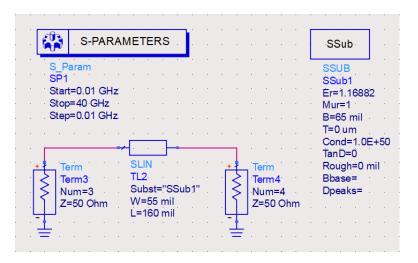

| 2.27 | Image of the ADS suspended stripline model.                        | 54 |

| 2.28 | ADS simulated S-parameters of the suspended thru-line              | 54 |

| 2.29 | Image of the HFSS suspended stripline model                        | 55 |

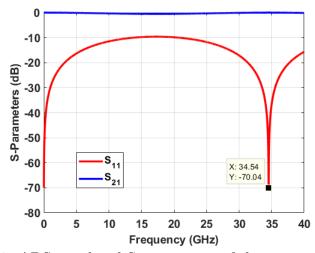

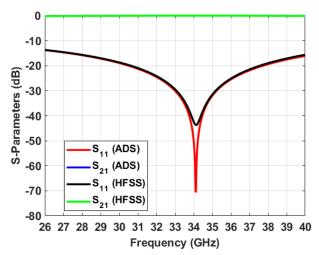

| 2.30 | ADS and HFSS simulated S-parameters of the suspended thru-         |    |

|      | line                                                               | 55 |

| 2.31 | Image of the ADS stripline model                                   | 56 |

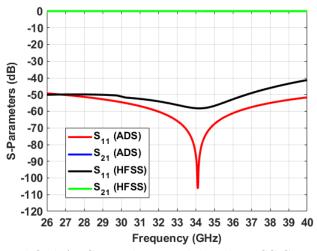

| 2.32 | Modified ADS stripline model and HFSS simulated S-parameters.      | 57 |

| 2.33 | Modified ADS stripline model and HFSS S-parameters (tuned).        | 57 |

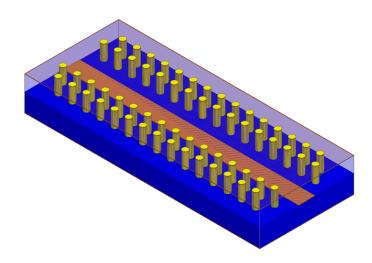

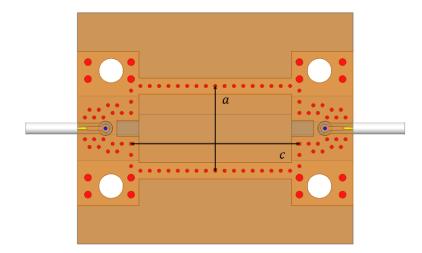

| 2.34 | 3-D view of the proposed DC-20 GHz SISL thru-line                  | 58 |

| 2.35 | Top-down view of the proposed SISL design showing the effec-       |    |

|      | tive rectangular waveguide structure                               | 59 |

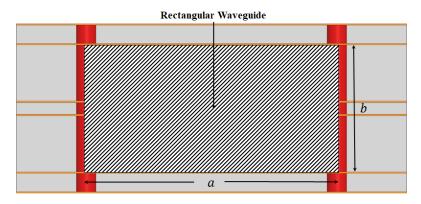

| 2.36 | Cross-sectional view of the proposed SISL design showing the       |    |

|      | effective rectangular waveguide structure                          | 60 |

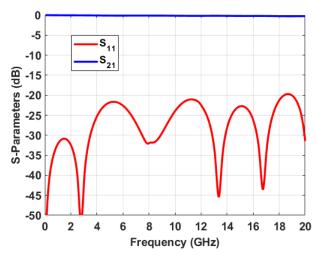

| 2.37 | $\rm HFSS$ simulated S-parameters of the proposed DC-20 GHz SISL   |    |

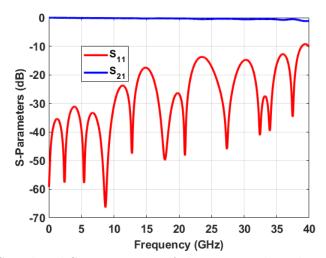

|      | thru-line                                                          | 62 |

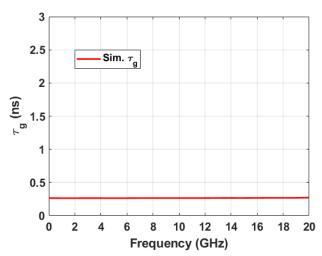

| 2.38 | HFSS simulated group delay of the proposed DC-20 GHz SISL $$         |    |

|------|----------------------------------------------------------------------|----|

|      | thru-line                                                            | 63 |

| 2.39 | Photograph of the fabricated DC-20 GHz SISL thru-line                | 65 |

| 2.40 | Simulated and measured S-parameters of the proposed SISL             |    |

|      | thru-line                                                            | 66 |

| 2.41 | Simulated and measured group delay of the proposed SISL thru-        |    |

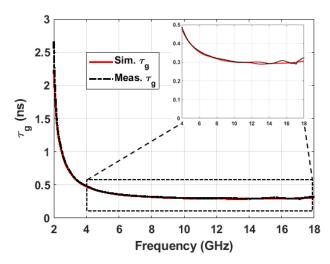

|      | line                                                                 | 67 |

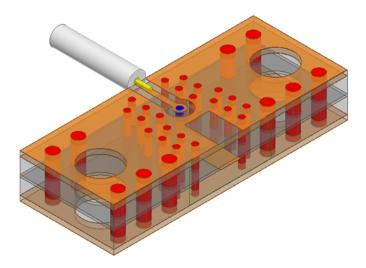

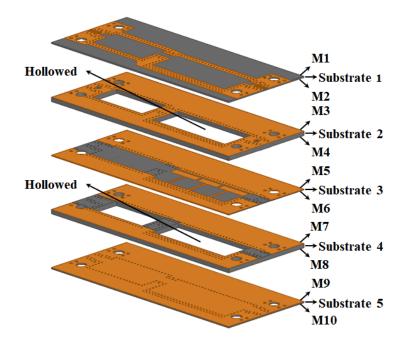

| 3.1  | 3-D exploded view of the proposed SISL generalized Chebyshev         |    |

|      | LPF                                                                  | 69 |

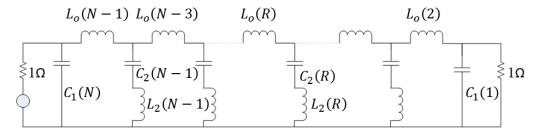

| 3.2  | Generalized Chebyshev LPF prototype filter having 3 transmis-        |    |

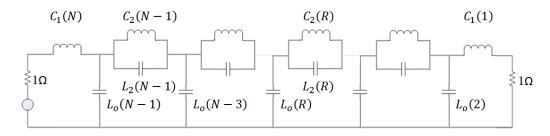

|      | sion zeros at infinity and (N-3) at a finite frequency               | 71 |

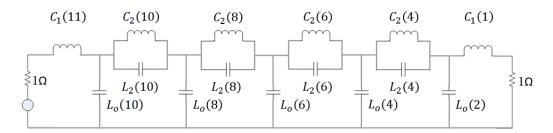

| 3.3  | Generalized Chebyshev LPF prototype for an eleventh-order filter.    | 72 |

| 3.4  | Generalized Chebyshev LPF prototype for an eleventh-order fil-       |    |

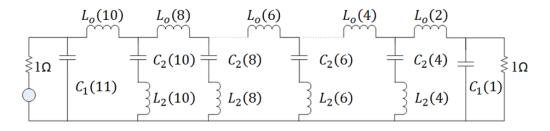

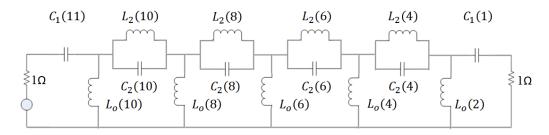

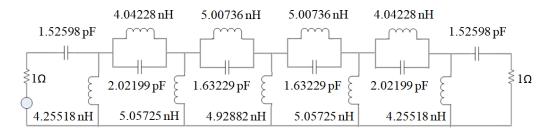

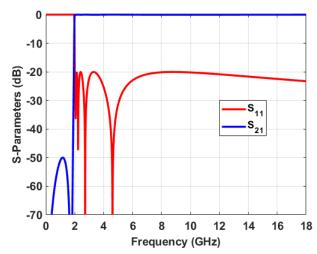

|      | ter with calculated inductance and capacitance values. $\ . \ . \ .$ | 75 |

| 3.5  | ADS simulated S-parameters of the eleventh-order Generalized         |    |

|      | Chebyshev ideal LC circuit model.                                    | 75 |

| 3.6  | Capacitance model for the proposed SISL transmission line [50].      | 79 |

| 3.7  | Layout representation of the distributed generalized Chebyshev       |    |

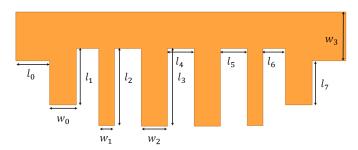

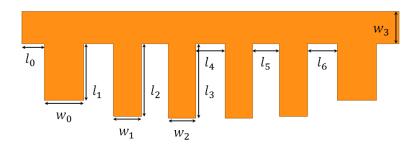

|      | LPF                                                                  | 84 |

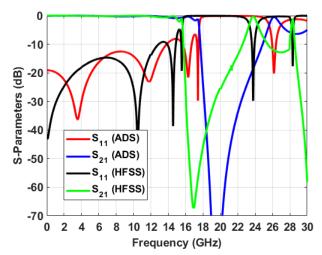

| 3.8  | ADS simulated S-parameters of the Chebyshev LPF ignoring             |    |

|      | open-circuit edge effects (calculated values).                       | 85 |

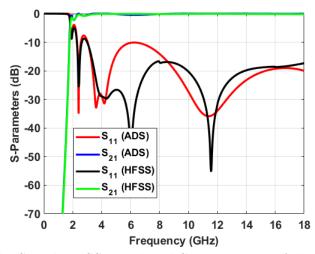

| 3.9  | 3-D view of the LPF HFSS model.                                      | 85 |

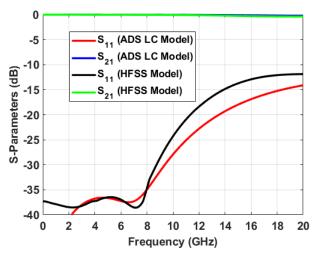

| 3.10 | ADS and HFSS simulated S-parameters of the Chebyshev LPF             |    |

|      | (calculated values)                                                  | 86 |

| 3.11 | ADS and HFSS simulated S-parameters of the Chebyshev LPF             |    |

|      | with additional edge effect length added to ADS LPF model            | 87 |

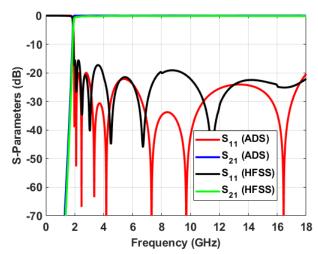

| 3.12       | ADS and HFSS simulated S-parameters of the Chebyshev LPF                                                                                           |      |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------|

|            | with edge effect compensation added to the HFSS model                                                                                              | 88   |

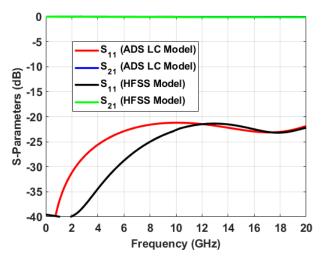

| 3.13       | ADS and HFSS simulated S-parameters of the Chebyshev LPF                                                                                           |      |

|            | (tuned values). $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                     | 89   |

| 3.14       | 3-D view of the proposed DC-18 GHz SISL LPF                                                                                                        | 90   |

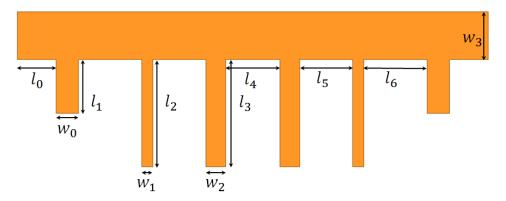

| 3.15       | Layout representation for the tuned SISL Chebyshev LPF. $\ .$ .                                                                                    | 91   |

| 3.16       | Top-down view of the proposed SISL LPF design showing the                                                                                          |      |

|            | effective rectangular waveguide structure dimensions                                                                                               | 92   |

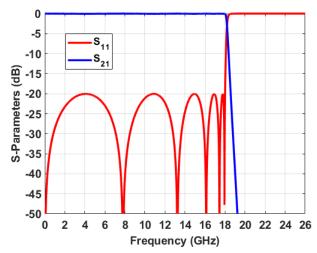

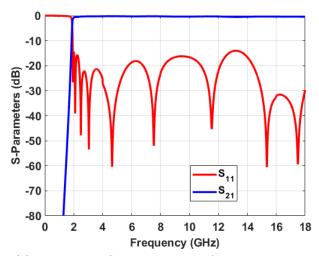

| 3.17       | $\rm HFSS$ simulated S-parameters of the proposed DC-18 GHz SISL                                                                                   |      |

|            | LPF                                                                                                                                                | 93   |

| 3.18       | HFSS simulated group delay of the proposed SISL LPF. $\ . \ .$ .                                                                                   | 94   |

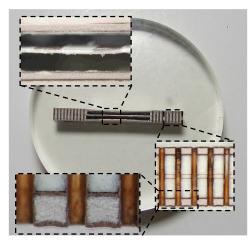

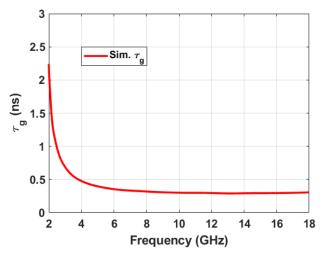

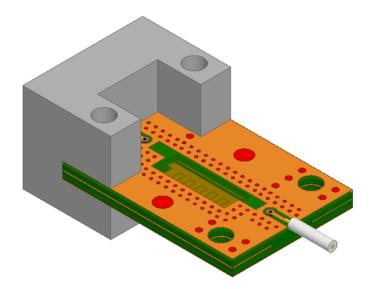

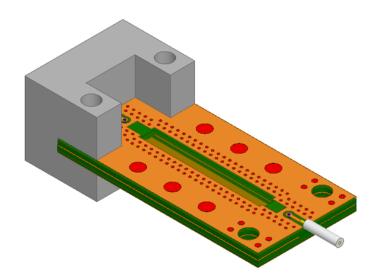

| 3.19       | Photograph of the fabricated DC-18 GHz SISL LPF. $\ . \ . \ .$                                                                                     | 95   |

| 3.20       | Cross-section of a fabricated SISL LPF with inset showing both                                                                                     |      |

|            | the air cavity and plated thru-hole vias (dark areas are due to                                                                                    |      |

|            | $oxidation). \ldots \ldots$ | 95   |

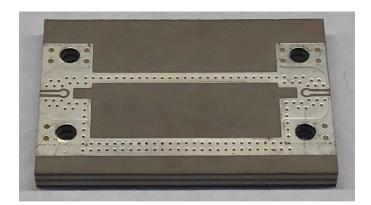

| 3.21       | Simulated and measured S-parameters of the proposed SISL LPF.                                                                                      | 96   |

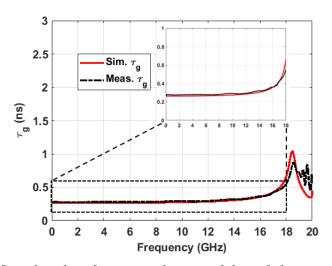

| 3.22       | Simulated and measured group delay of the proposed SISL LPF.                                                                                       | 97   |

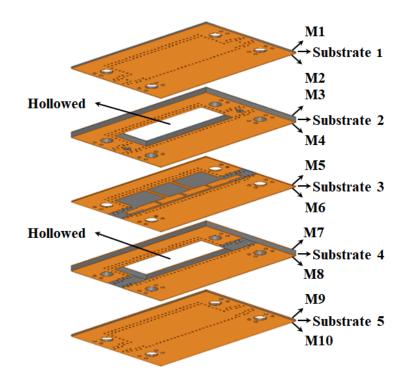

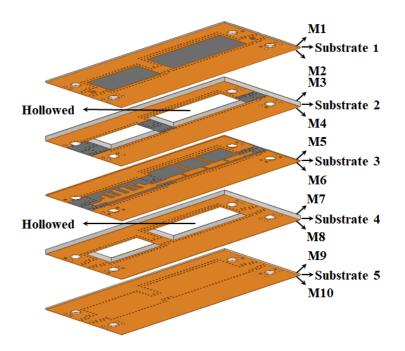

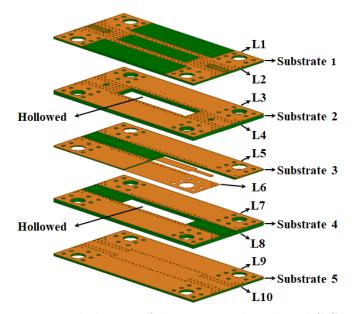

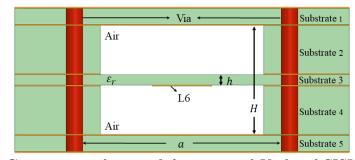

| 4.1        | 3-D exploded view of the proposed SISL generalized Chebyshev                                                                                       |      |

|            |                                                                                                                                                    | 101  |

| 4.2        | Bottom 3-D exploded view of the proposed SISL generalized                                                                                          |      |

| 1.2        |                                                                                                                                                    | 102  |

| 4.3        | Generalized Chebyshev LPF prototype (dual) having 3 trans-                                                                                         | 102  |

| 1.0        |                                                                                                                                                    | 104  |

| 4.4        | Generalized Chebyshev LPF prototype (dual) for an eleventh-                                                                                        | LU-I |

| <b>1.1</b> |                                                                                                                                                    | 104  |

|            | order filter                                                                                                                                       | 104  |

| 4.5  | Generalized Chebyshev HPF prototype for an eleventh-order                                    |     |

|------|----------------------------------------------------------------------------------------------|-----|

|      | filter                                                                                       | 105 |

| 4.6  | Generalized Chebyshev HPF prototype for an eleventh-order                                    |     |

|      | filter with calculated inductance and capacitance values. $\ . \ .$                          | 106 |

| 4.7  | Generalized Chebyshev HPF prototype for an eleventh-order                                    |     |

|      | filter with calculated inductance and capacitance values. $\ . \ .$                          | 107 |

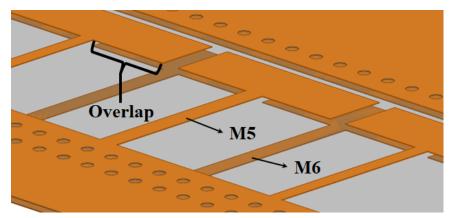

| 4.8  | 3-D view of the overlap section to further illustrate the broad-                             |     |

|      | side coupling structure                                                                      | 110 |

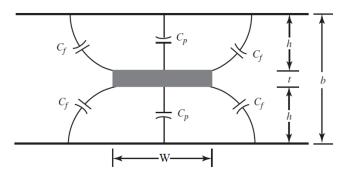

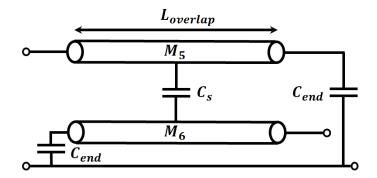

| 4.9  | Side view of the broadside coupled structures equivalent model.                              | 111 |

| 4.10 | Side view of the broadside coupled structures equivalent model.                              | 111 |

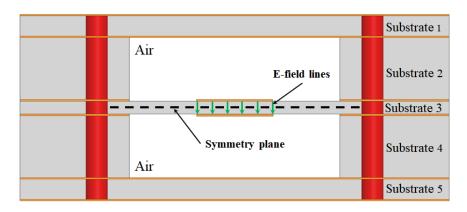

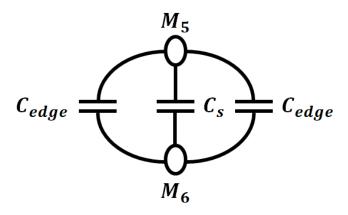

| 4.11 | End view of the broadside coupled structures equivalent model.                               | 113 |

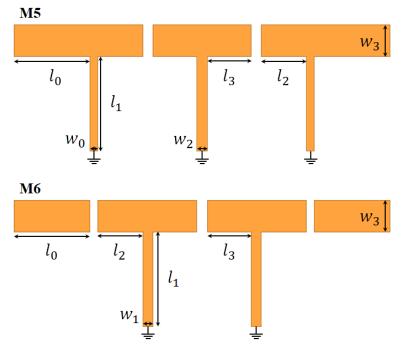

| 4.12 | Layout representation of the distributed generalized Chebyshev                               |     |

|      | HPF                                                                                          | 115 |

| 4.13 | ADS simulated S-parameters of the Chebyshev LC model HPF                                     |     |

|      | with distributed shunt short-circuit stubs                                                   | 116 |

| 4.14 | ADS simulated S-parameters of the Chebyshev LC model HPF                                     |     |

|      | with tuned shunt short-circuit stubs.                                                        | 117 |

| 4.15 | ADS simulated S-parameters of the distributed Chebyshev HPF.                                 | 117 |

| 4.16 | 3-D view of the HPF HFSS model                                                               | 118 |

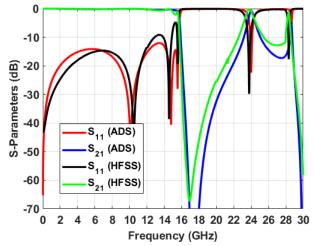

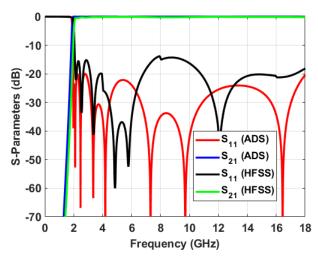

| 4.17 | ADS and HFSS simulated S-parameters of the Chebyshev HPF                                     |     |

|      | (calculated values). $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 118 |

| 4.18 | ADS and HFSS simulated S-parameters of the Chebyshev HPF                                     |     |

|      | (tuned values). $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$      | 119 |

| 4.19 | Top-down view of the HPF HFSS model                                                          | 120 |

| 4.20 | ADS and HFSS simulated S-parameters of the Chebyshev HPF.                                    | 121 |

| 4.21 | 3-D view of the proposed 2 GHz SISL HPF                                                      | 121 |

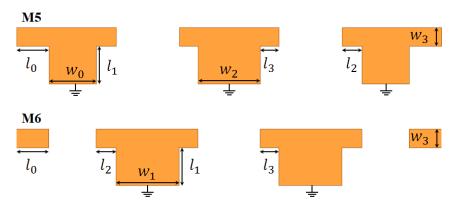

| 4.22 | Layout representation for the tuned SISL Chebyshev HPF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 122   |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 4.23 | Top-down view of the proposed SISL HPF design showing the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

|      | effective rectangular waveguide structure dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 123   |

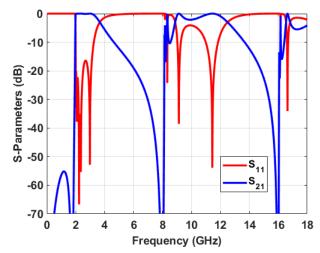

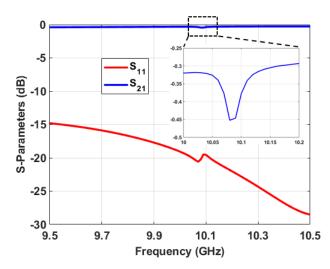

| 4.24 | Simulated S-parameters showing the resonance around 10 GHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 124   |

| 4.25 | Top-down view of the proposed SISL HPF design showing the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

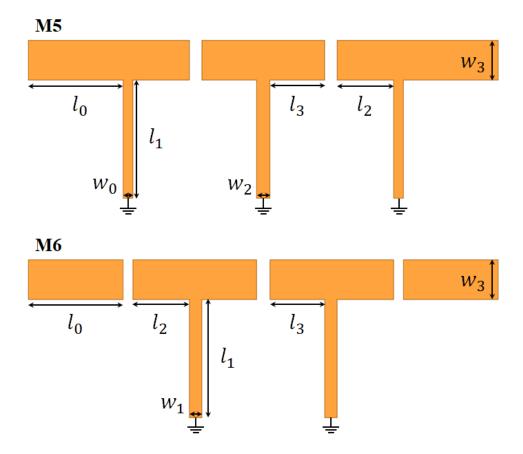

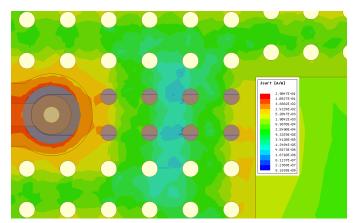

|      | internal resonance on (a) M5 and (b) M6. $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 124   |

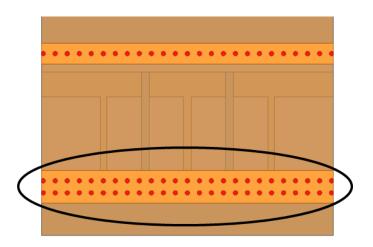

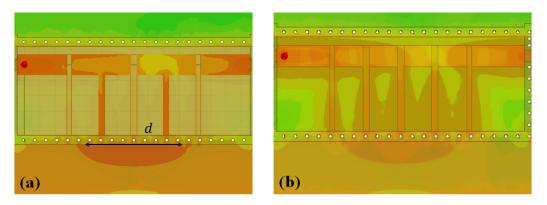

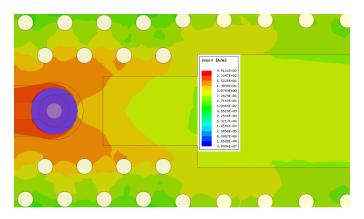

| 4.26 | Top-down view of the proposed SISL HPF design showing the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

|      | current density on M5 after adding the second row of grounding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

|      | vias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 125   |

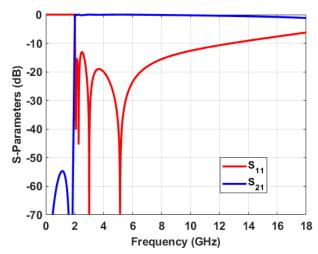

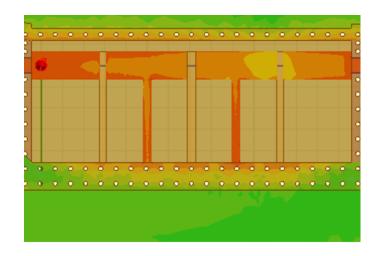

| 4.27 | Simulated S-parameters after adding the second row of stitching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

|      | vias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 125   |

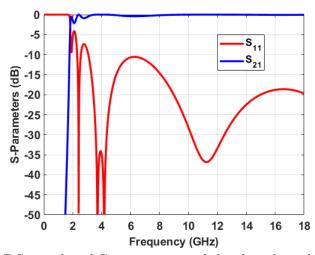

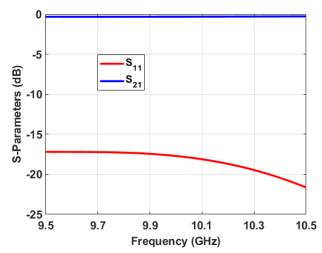

| 4.28 | HFSS simulated S-parameters of the proposed 2 GHz SISL HPF $$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | .126  |

| 4.29 | HFSS simulated group delay of the proposed SISL HPF. $\ . \ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 127   |

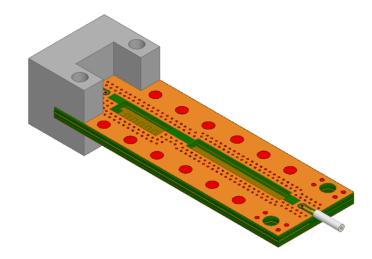

| 4.30 | Photograph of the fabricated 2 GHz SISL HPF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 128   |

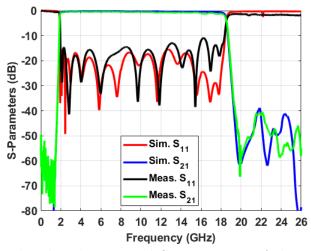

| 4.31 | Simulated and measured S-parameters of the proposed SISL HPF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .129  |

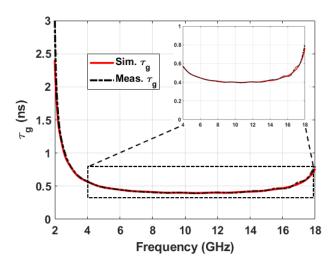

| 4.32 | Simulated and measured group delay of the proposed SISL HPF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 129 |

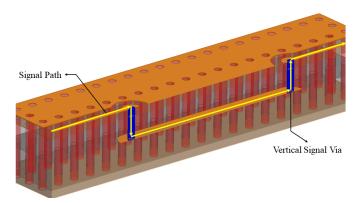

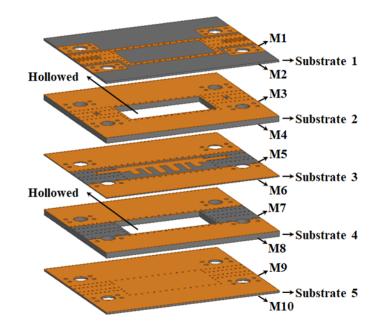

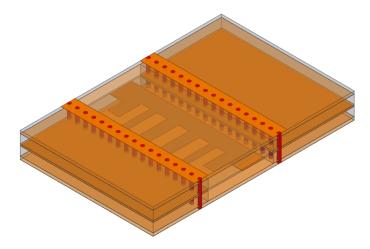

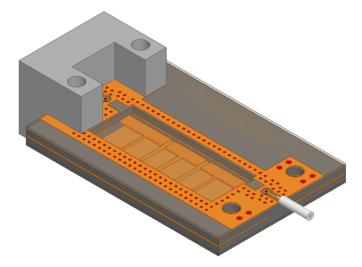

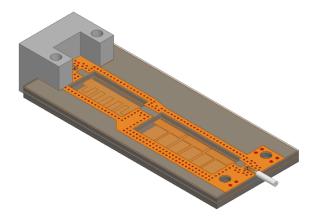

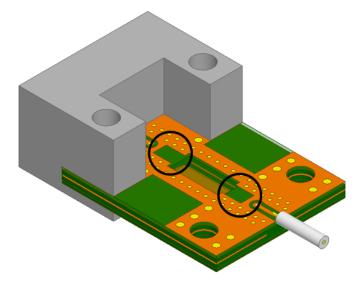

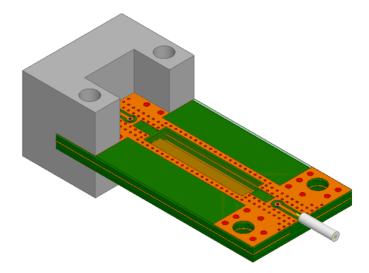

| 5.1  | 3-D exploded view of the proposed cascaded Chebyshev SISL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| 0.1  | BPF.         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . | 131   |

| 5.2  | Bottom 3-D exploded view of the proposed cascaded Chebyshev                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

|      | SISL BPF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 131   |

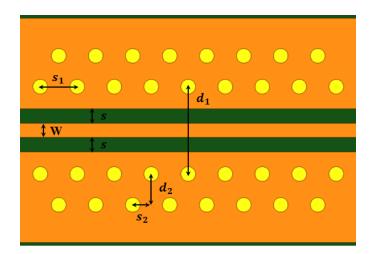

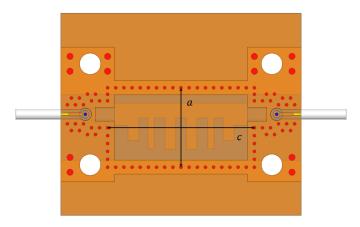

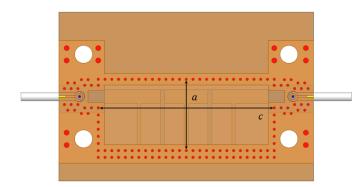

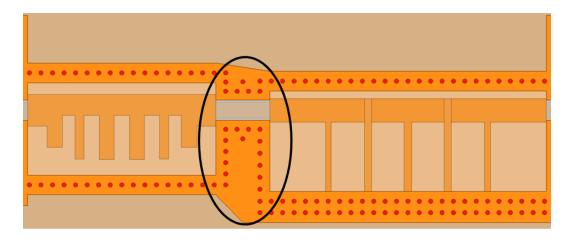

| 5.3  | Top-down and zoomed-in view of the proposed cascaded SISL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

|      | BPF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 133   |

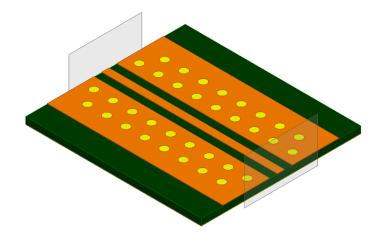

| 5.4  | 3-D view of the proposed 2-18 GHz cascaded SISL BPF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 134   |

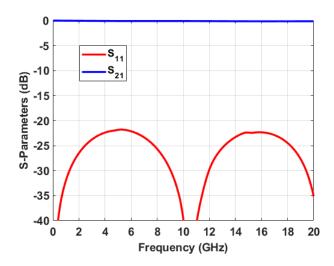

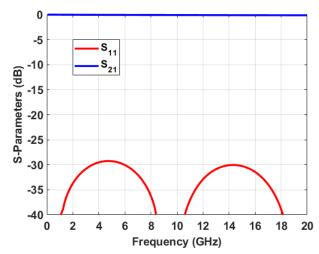

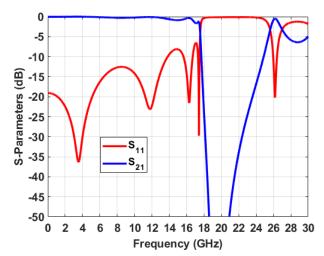

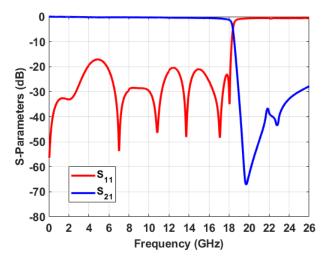

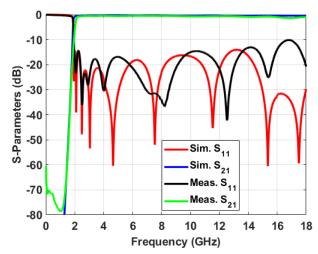

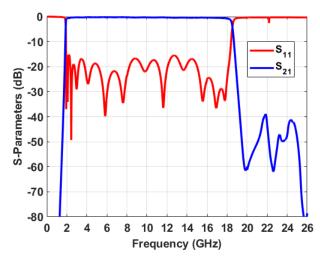

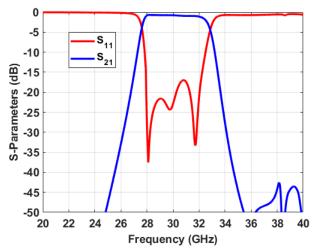

| 5.5  | HFSS simulated S-parameters of the proposed 2-18 GHz cas-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

|      | caded SISL BPF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 135   |

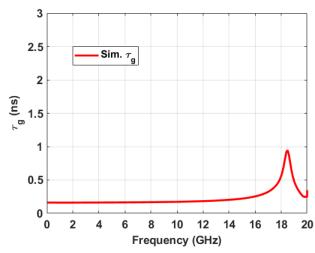

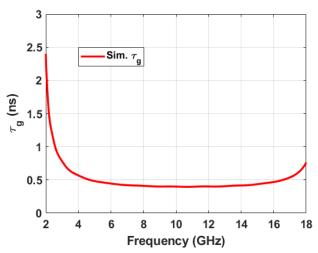

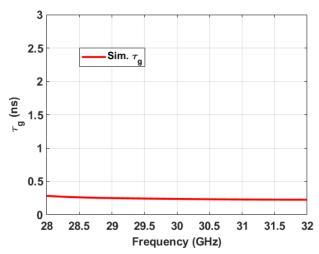

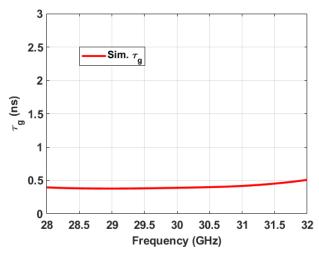

| 5.6  | HFSS simulated group delay of the proposed 2-18 GHz cascaded               |     |

|------|----------------------------------------------------------------------------|-----|

|      | SISL BPF                                                                   | 135 |

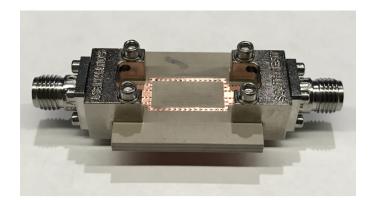

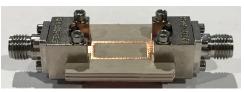

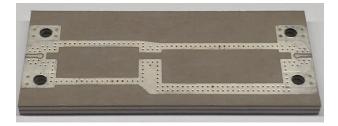

| 5.7  | Photograph of the fabricated 2-18 GHz cascaded SISL BPF. $% \mathcal{A}$ . | 135 |

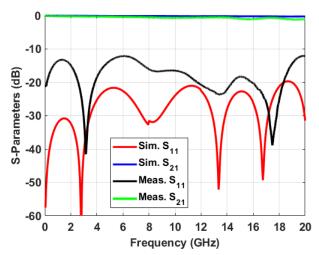

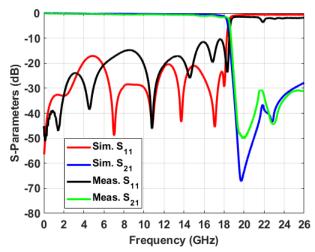

| 5.8  | Simulated and measured S-parameters of the proposed cascaded               |     |

|      | SISL BPF                                                                   | 136 |

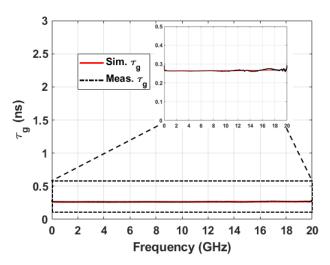

| 5.9  | Simulated and measured group delay of the proposed cascaded                |     |

|      | SISL BPF                                                                   | 137 |

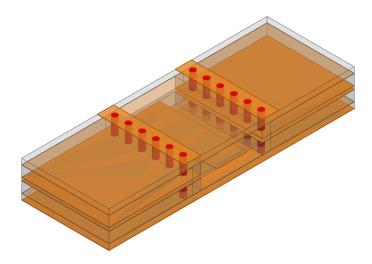

| 6.1  | 3-D exploded view of the proposed Ka-band SISL technology.                 | 139 |

| 6.2  | Cross-sectional view of the proposed Ka-band SISL technology.              | 139 |

| 6.3  | Top-view of the proposed SISL technology to illustrate L1                  | 140 |

| 6.4  | 3-D view of the vertical via transition including edge-launch              |     |

|      | connector                                                                  | 141 |

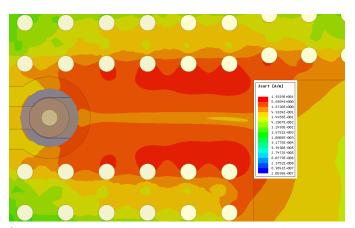

| 6.5  | Current density plot on L2 without blind vias or modified L1.              | 144 |

| 6.6  | Current density plot on L2 with blind vias                                 | 145 |

| 6.7  | 3-D view of the SISL technology with L1 modifications to avoid             |     |

|      | waveguide resonance in Substrate 1                                         | 145 |

| 6.8  | Current density plot on L2 with modification to L1                         | 146 |

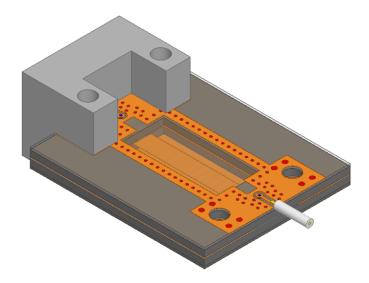

| 6.9  | 3-D view of the HFSS Ka-band SISL thru-line model                          | 147 |

| 6.10 | 3-D view of the HFSS Ka-band SISL Chebyshev LPF model                      | 148 |

| 6.11 | Layout representation of the distributed generalized Chebyshev             |     |

|      | LPF                                                                        | 149 |

| 6.12 | 3-D view of the HFSS Ka-band SISL Chebyshev HPF model                      | 150 |

| 6.13 | Layout representation of the distributed generalized Chebyshev             |     |

|      | HPF                                                                        | 150 |

| 6.14 | 3-D view of the HFSS Ka-band SISL Chebyshev BPF model.                     | 151 |

| 6.15 | Layout representation of the distributed generalized Chebyshev  |      |

|------|-----------------------------------------------------------------|------|

|      | BPF                                                             | 151  |

| 6.16 | Simulated S-parameters of the proposed Ka-band SISL thru-line.  | 152  |

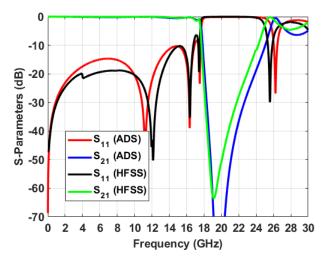

| 6.17 | Simulated S-parameters of the proposed Ka-band SISL Cheby-      |      |

|      | shev LPF                                                        | 153  |

| 6.18 | Simulated group delay of the proposed Ka-band Chebyshev LPF.    | .153 |

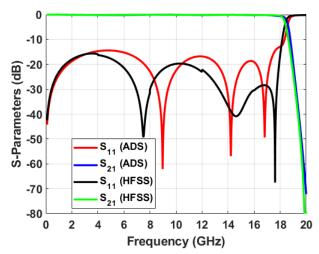

| 6.19 | Simulated S-parameters of the proposed Ka-band SISL Cheby-      |      |

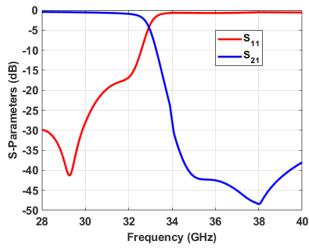

|      | shev HPF                                                        | 154  |

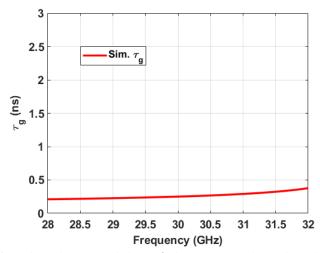

| 6.20 | Simulated group delay of the proposed Ka-band Chebyshev HPF.    | .155 |

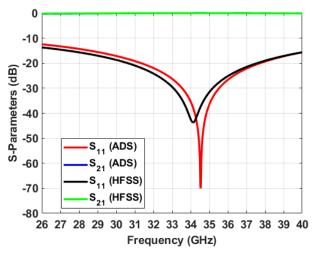

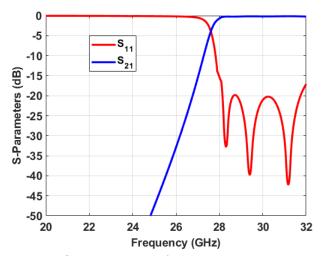

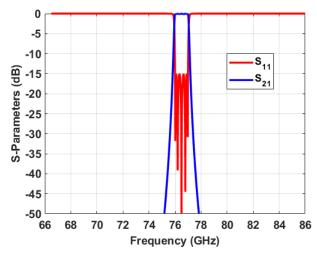

| 6.21 | Simulated S-parameters of the proposed Ka-band SISL Cheby-      |      |

|      | shev BPF                                                        | 155  |

| 6.22 | Simulated group delay of the proposed Ka-band Chebyshev BPF.    | .156 |

| 7.1  | 3-D exploded view of the proposed LTCC SISL BPF                 | 161  |

| 7.2  | Simulated S-parameters of the proposed LTCC SISL BPF            | 162  |

| A.1  | Material stack-up for tacking process                           | 187  |

| A.2  | Material stack-up for lamination of substrate layers 1-3        | 187  |

| A.3  | Material stack-up for lamination of substrate layers 1-5        | 187  |

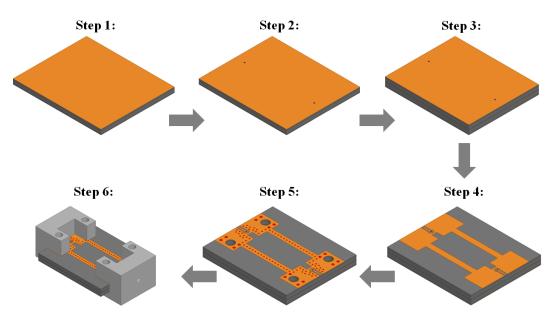

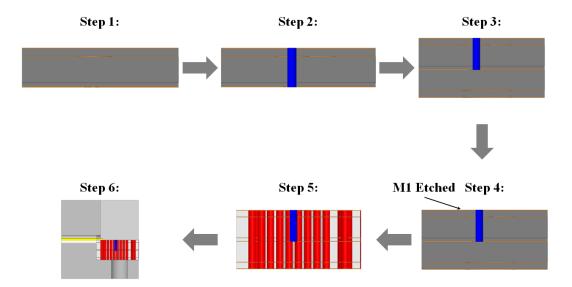

| A.4  | Fully-board embedded suspended integrated stripline compo-      |      |

|      | nent step by step fabrication procedure                         | 188  |

| A.5  | Cross-sectional view of the step by step fabrication procedure. | 188  |

### Abstract

The method in which the frequency spectrum is currently allocated is unsustainable. An increasing number of devices are becoming wireless, overcrowding an already crowded spectrum (e.g., the ISM band). Therefore, future systems will be forced to move to higher frequencies in order to be allocated an unused slice of the spectrum and accumulate the desired/required bandwidth. Furthermore, with the continued desire to implement a multitude of sensors on unmanned aerial vehicles (UAVs), as well as the need for conformal small-cell repeaters for 5G communications, next generation systems will have to achieve unprecedented reductions in size, weight, power, and cost (SWaP-C).

In order for future systems to become practical, several fundamental technological hurdles must be overcome including the development of low loss and highly integrated components used to build next generation systems. The RF/microwave filter is of particular interest, as it is not only crucial for conditioning the signal for transmission and/or digitization, but can also affect critical system parameters based on it's placement in the system. Due to the increased attenuative nature of the environment at microwave frequencies, the systems dynamic range will have to be maximized requiring an exceptionally low loss filter if placed close to the antenna in the receiver (Rx) chain, which is necessary for defense and adaptive/re-configurable systems. While low loss microwave filtering can be easily achieved using waveguide design techniques, it is much more difficult in a highly integrated planar design due to increased radiation and dielectric losses. A promising solution which minimizes these losses and offers a planar solution is the suspended integrated stripline (SISL) filter.

In this research, a low loss fully-board integrated lowpass and highpass filter, using the suspended integrated stripline technology, are designed and studied, pushing the stat-of-the-art in planar filtering technologies. A multilayer board stack-up, with internally buried hollowed cavities, is used to create the suspended stripline. The embedded filter is accessed through a co-planar waveguide-to-stripline vertical via transition and vice-versa. Simulated and measured results show that insertion losses of less than 1 dB are obtainable including the vertical via transition and associated trace losses. Compared to it's suspended substrate stripline (SSS) predecessor, the SISL filter is one order of magnitude smaller and lighter while achieving identical performance. Beyond the proposed filters, this technological solution can be applied to several other passive microwave components such as couplers, power dividers, and gain equalizers. The capabilities demonstrated in this research will be crucial to the design and integration of modern and next generation systems as it requires no mechanical housing, connectors, or assembly, resulting in a light weight, compact size, and low cost solution.

### Chapter 1

#### Introduction

### 1.1 Motivation

The recent trend in modern wireless and radio frequency (RF) system design has been to integrate several subsystems onto a single printed circuit board (PCB) through the use of multi-chip modules (MCM) [1], [2] or system on chip (SoC) [3]–[5] techniques. While a single custom designed application specific integrated circuit (ASIC) that could perform all the tasks required for a specific system is ideal, it is currently unrealistic due to cost and performance restrictions. Therefore, a more realistic approach is to integrate several amplifiers, switches, and attenuators onto a single ASIC and utilize an underlying multi-layer substrate stack-up to integrate and design the needed passive components (i.e. filters and antennas) [6]. This thrust area has been crucially influenced over the last decade to meet the reduced size, weight, power, and  $\cos t$  (SWaP-C) demands for wireless communication (5G) [7], [8] as well as automotive radar and un-manned aerial vehicle (UAV) sensors [9]. Furthermore, beyond the commercial market, the science and defense communities have also benefited from these higher forms of integration; specifically, in the areas of weather [10], remote sensing [11], and airborne electronic warfare [12]. This is in large part due to advances in active electronically scanned arrays (AESAs), which have been made more feasible over the last decade thanks to miniaturized transceiver modules that can be placed behind each element of a phased array antenna.