# THE PHILOSOPHY AND SYSTEM ORGANIZATION OF A SMALL DIGITAL COMPUTER

By

JOHN LEE FIKE, JR.

Bachelor of Science

Oklahoma State University

Stillwater, Oklahoma

1961

Submitted to the Faculty of the Graduate School of the Oklahoma State University in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE August, 1962

NOV 7 1962

# THE PHILOSOPHY AND SYSTEM ORGANIZATION OF A SMALL DIGITAL COMPUTER

Thesis Approved:

Thesis Advisor

Dean of the Graduate School

#### PREFACE

The number and usefulness of digital computers is constantly increasing. Similarly, the demand for engineers with an understanding of not only the applications, but also of the internal structure of digital computers is also increasing.

The availability of a quantity of computer components to the School of Electrical Engineering of the Oklahoma State University suggested that a small computer might be constructed for demonstration and instructional purposes in computer engineering courses. Before such a project could be undertaken, an overall organizational plan was required. Such a plan is presented in this paper.

The various applications of an instructional computer will be examined, and from these a "design philosophy" will be developed. These criteria will then be used in formulating the machine organization. Although many of the components available for construction are circa 1952, the writer has attempted to avoid designing another 1952 computer.

The author expresses sincere thanks to his adviser, Professor Paul A. Mc Collum, for his counsel and guidance. It is deeply appreciated. Also, the help and understanding of Professor William Granet, Acting Director of the Computing Center of the Oklahoma State University, are gratefully acknowledged.

My wife, Gail, and her mother, Mrs. Martha Raper, did all of the typing for this paper. Theirs was a true labor of love, and I thank them for it.

# TABLE OF CONTENTS

| Chapte | r                                            |    |   |     |   |   | Pa | age |

|--------|----------------------------------------------|----|---|-----|---|---|----|-----|

| ı.     | INTRODUCTION: DESIGN PHILOSOPHY              |    |   |     |   |   |    | 1   |

| I.I.   | THE OVERALL SYSTEM ORGANIZATION OF THE OSTIC | •  |   |     | 8 |   |    | 6   |

| III.   | MEMORY AND TIMING                            |    |   |     |   |   |    | 12  |

| IV.    | CYCLES AND CONTROL                           |    |   |     |   |   |    | 17  |

| v.     | DATA ACQUISITION AND TRANSMISSION            |    |   |     |   |   |    | 28  |

| VI.    | ACCUMULATOR OPERATIONS                       |    |   |     |   |   |    | 38  |

| VII.   | LOGICAL OPERATIONS                           | •  |   |     |   |   | •  | 62  |

| VIII.  | TESTING AND BRANCHING OPERATIONS             |    |   |     |   |   |    | 68  |

| IX.    | MISCELLANEOUS OPERATIONS                     |    |   |     |   |   | •  | 76  |

| x.     | INPUT/OUTPUT AND CONSOLE OPERAT              | IC | N |     |   |   |    | 80  |

| XI.    | PROGRAMMING AND OPERATION                    | •  |   |     |   | • | •  | 87  |

| XII.   | CONSTRUCTION AND MAINTENANCE .               |    |   |     |   |   |    | 93  |

| XIII.  | SUMMARY                                      |    |   |     |   | • |    | 95  |

| BIBLIC | OGRAPHY                                      |    |   |     |   |   |    | 97  |

| APPEN  | NDIX A                                       |    |   |     |   |   |    | 98  |

| APPE   | NDIX B                                       |    |   |     |   |   |    | 99  |

| APPE   | NDIX C                                       | •  | • |     | • |   | 1  | 04  |

| APPE   | NDIX D                                       | 21 | 2 | 257 |   |   | 1  | 06  |

### LIST OF TABLES

| Table                                                   | Page |

|---------------------------------------------------------|------|

| I. Binary Addition With End-Around Carry                | 41   |

| II . Rules for Accumulator Complement and Reset         | 47   |

| III. Rules for Accumulator Operation Code and Sign      | 47   |

| IV. Rules for Accumulator Add-In                        | 48   |

| V. Rules for Accumulator End-Around Carry and Overflow. | 48   |

| VI. Binary Multiplication                               | 54   |

| VII. Binary Logical Operations                          | 63   |

| VIII. Logical Ring Addition                             | 64   |

| IX . Logical OR Addition                                | 65   |

# LIST OF FIGURES

| Figure                                                                         |      | Page |

|--------------------------------------------------------------------------------|------|------|

| I. Logical Diagram number 1, Data Channel                                      |      | 9    |

| II. Memory, Timing, and Words                                                  |      | 13   |

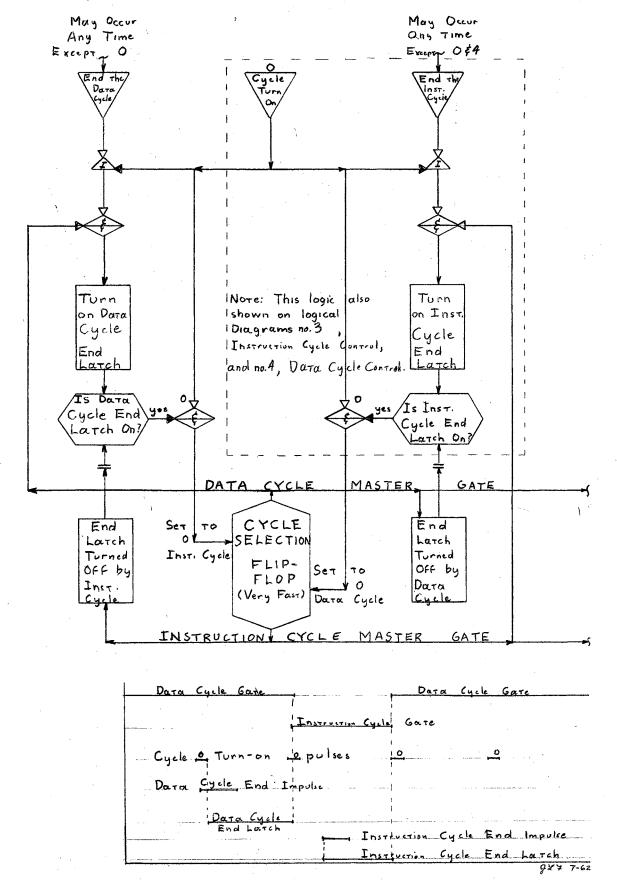

| II. Logical Diagram number 2, Master Cycle Control                             |      | 19   |

| IV. Logical Diagram number 3, Instruction Cycle Con                            | trol | 21   |

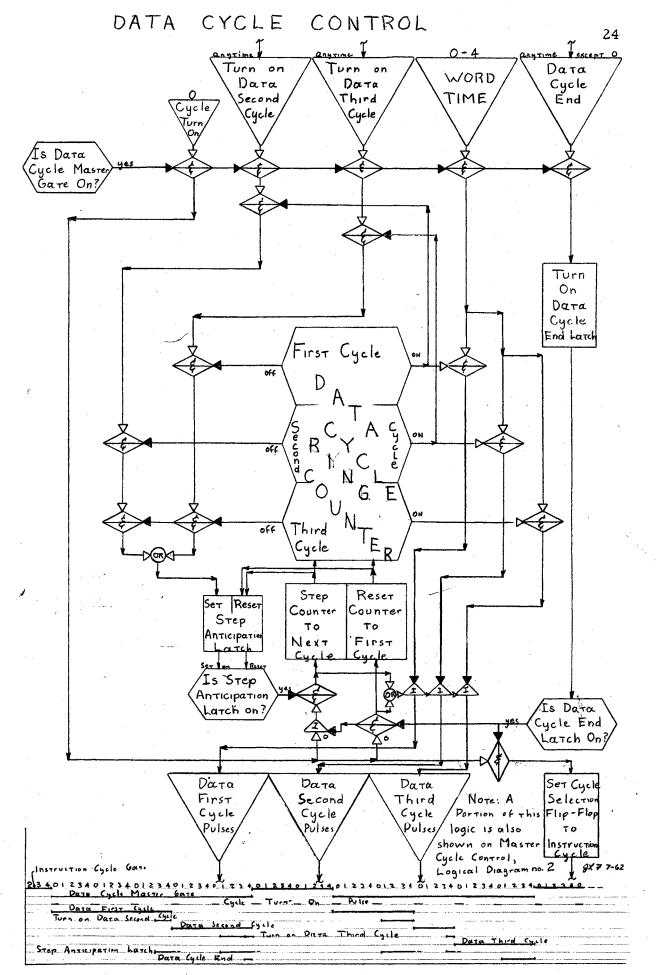

| V. Logical Diagram number 4, Data Cycle Control .                              |      | 24   |

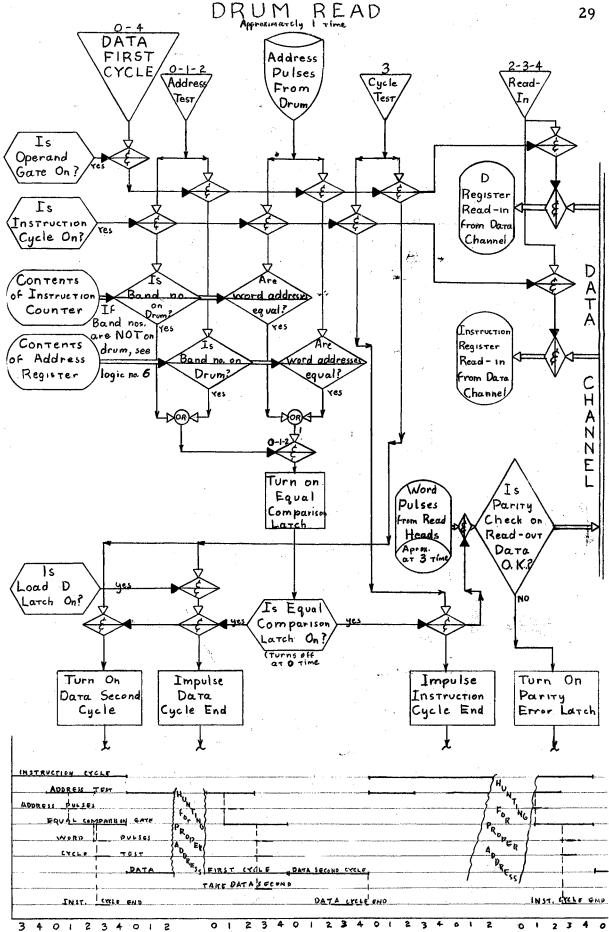

| VI. Logical Diagram number 5, Drum Read                                        |      | 29   |

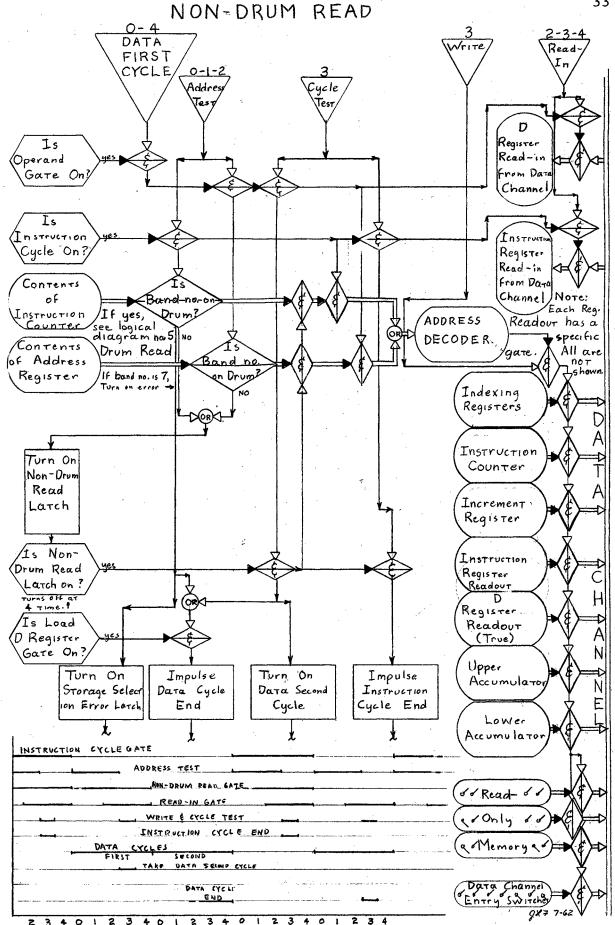

| VII. Logical Diagram number 6, Non-Drum Read                                   |      | 33   |

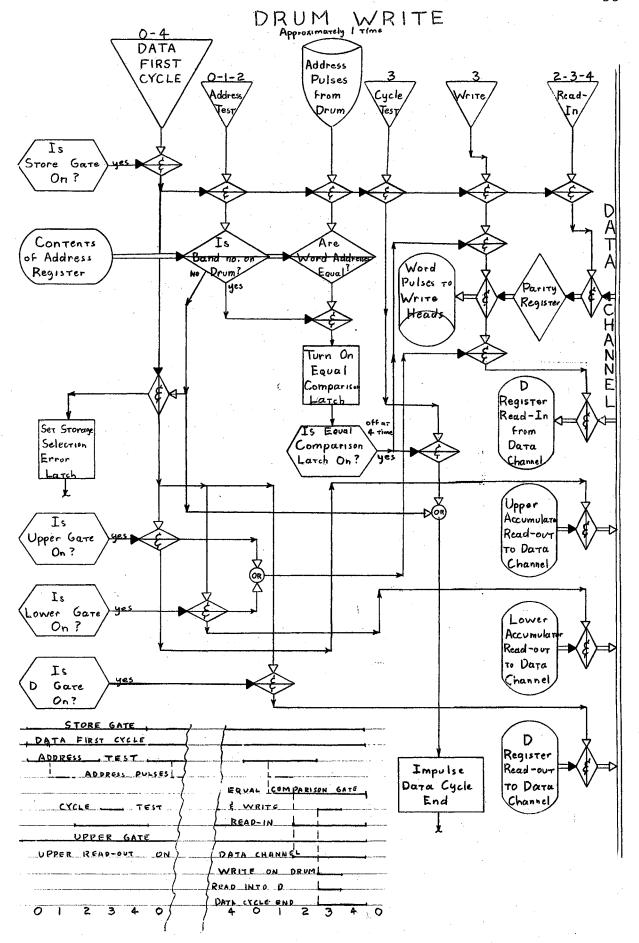

| VIII. Logical Diagram number 7, Drum Write                                     |      | 35   |

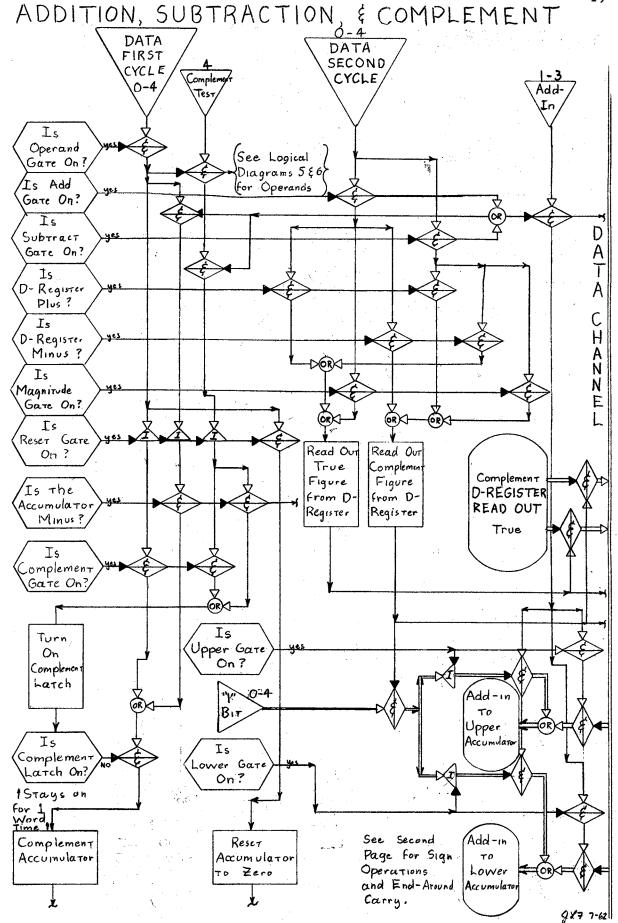

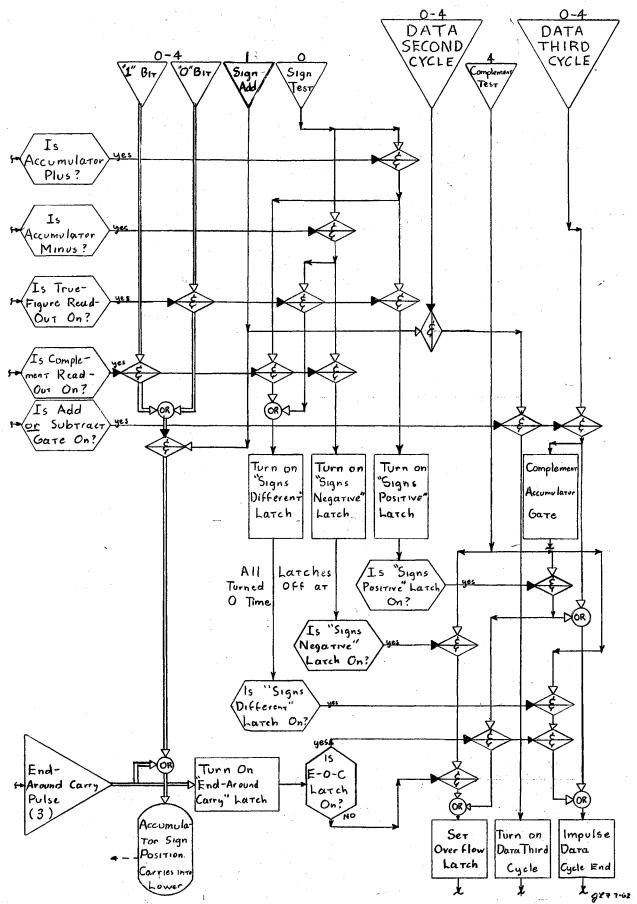

| IX-A. Logical Diagram number 8, sheet 1, Addition, Subtraction, and Complement |      | 49   |

| IX-B. Logical Diagram number 8, sheet 2                                        |      | 50   |

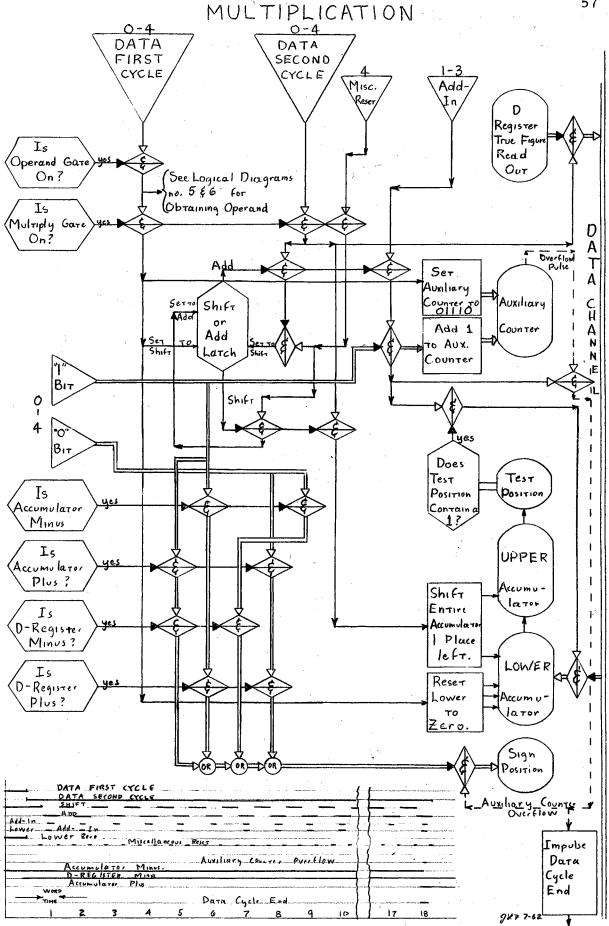

| X. Logical Diagram number 9, Multiplication                                    |      | 57   |

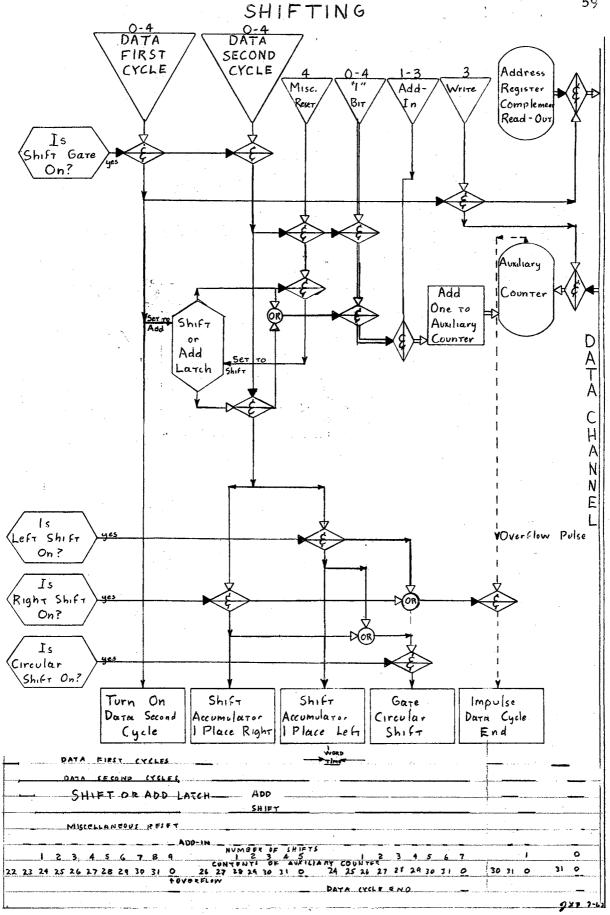

| XI . Logical Diagram number 10, Shifting                                       | •    | 59   |

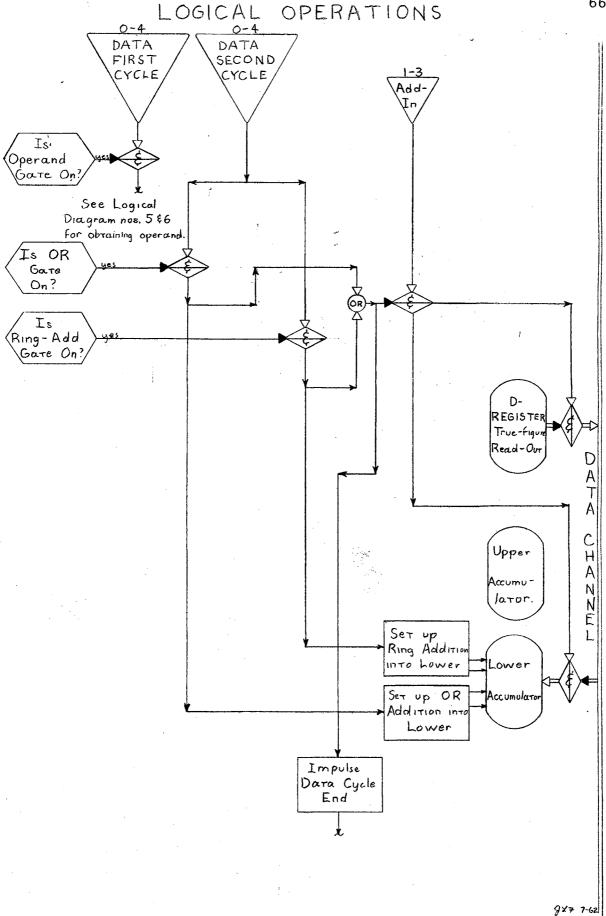

| XIL . Logical Diagram number 11, Logical Operations                            |      | 66   |

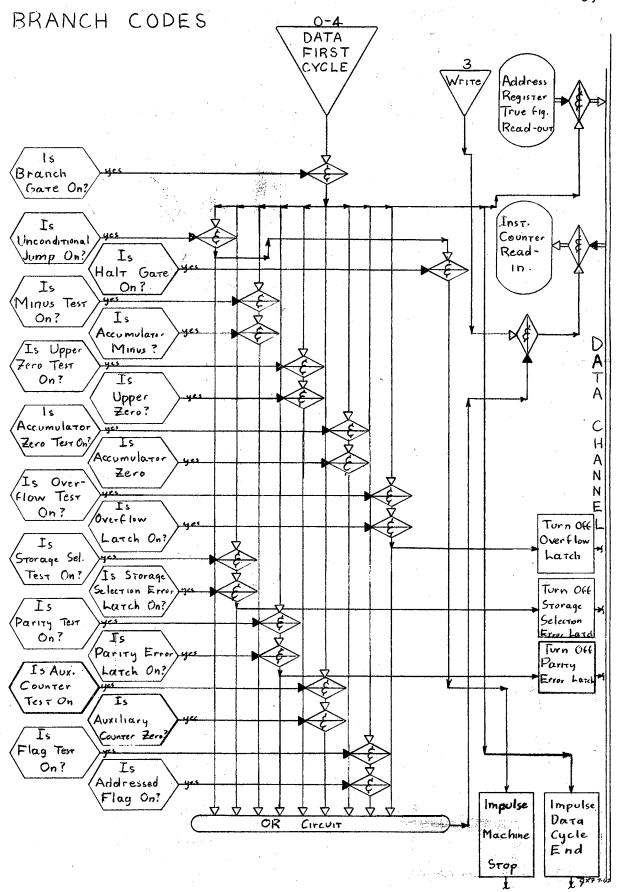

| XIII . Logical Diagram number 12, Branch Codes                                 |      | 69   |

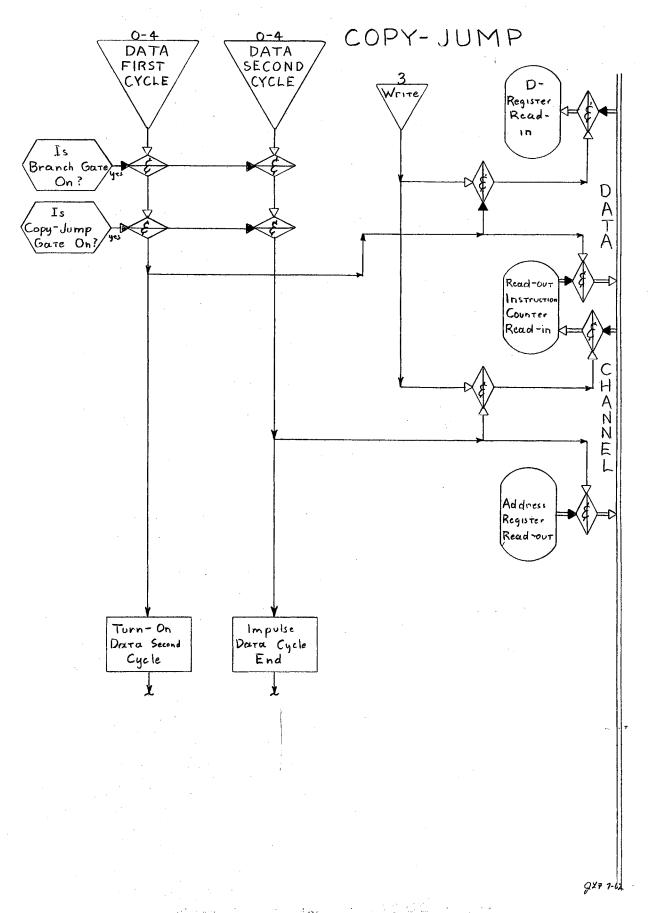

| XIV . Logical Diagram number 13, Copy-Jump                                     |      | 71   |

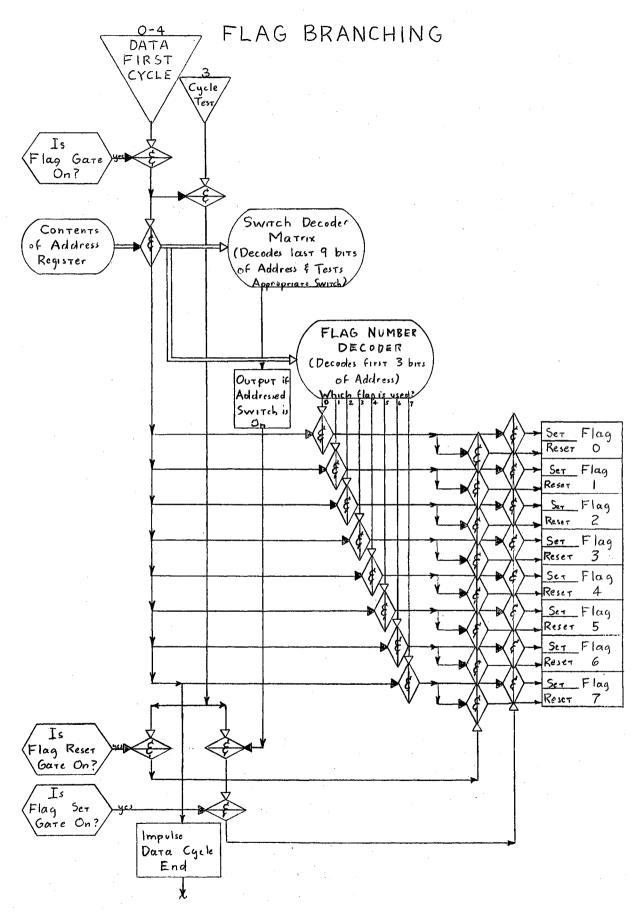

| XV . Logical Diagram number 14, Flag Branching                                 | •    | 74   |

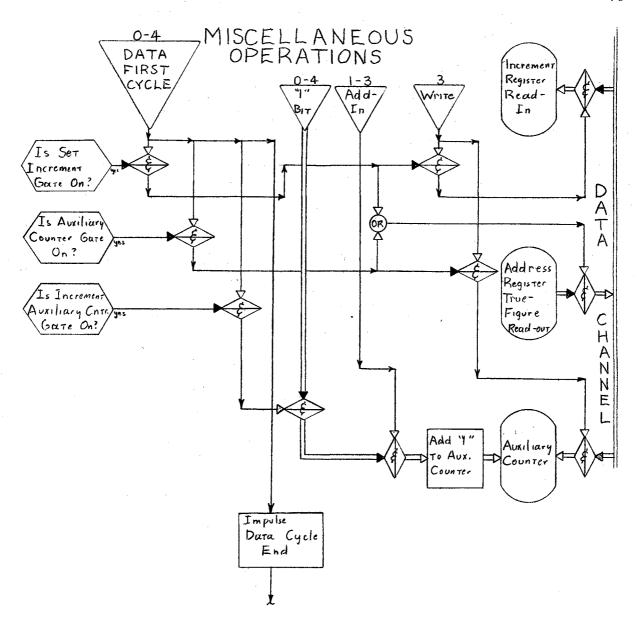

| XVI. Logical Diagram number 15, Miscellaneous Operations                       |      | 78   |

| XVII. Logical Diagram number 16, Timing and Stepping                           | •    | 82   |

| XVIII. Console                                                                 |      | 85   |

#### CHAPTER I

#### INTRODUCTION: DESIGN PHILOSOPHY

The design of a digital computer involves many separate levels, from the formulation of the overall purposes of the computer, to the final design and testing of the circuits to accomplish each specific task.

In this chapter, the Oklahoma State Instructional Computer (hereafter called the OSTIC) will be examined in the three areas of construction, operation, and maintenance. From the constraints brought out in this discussion, a "design philosophy", or set of design criteria, will be formulated for use in the remainder of this paper.

The principal source of components that will be used to construct the OSTIC is the remnants of a digital computer given to the School of Electrical Engineering of the Oklahoma State University, by the Continental Oil Company of Ponca City, Oklahoma. Components available include a magnetic drum with read write heads, motor, and a heavy-duty regulated power supply, together with numerous pluggable flip-flop modules, diode assemblies, and other electronic parts.

A number of important design parameters, such as component maximum operating speeds, voltage levels, and pulse shapes were thus already determined before the present design was conceived. It should also be mentioned that one of the design goals was to minimize the number of purchased components, such as flip-flops, and diodes, since, unlike some other computers constructed by universities, OSTIC will probably not receive a large amount of outside financial support.

As the name implies, this computer is primarily intended for use in computer logic design classes. It may be noted that a great deal

of the instructional value of such a machine lies in the actual construction and testing. It is the intent that the machine will be built, unit by unit, by graduate students under the direction of faculty members. In order to be certain that these efforts are of greatest benefit, an overall plan must be devised (preferably during the early stages of construction) that outlines the purpose, goals, and basic design criteria for the computer. This overall plan must be fairly complete and sufficiently detailed that no important questions (such as, "How does this machine add?") remain unanswered. At the same time, the plan must not attempt to present an overly detailed final design. In the first place, this would be much too time consuming for any one person to create; more important, the individuals doing the actual construction and testing may very likely find preferred ways to accomplish certain operations. Finally, and most important of all, the overall design should be straight-forward, and readily understandable by persons not possessing a large amount of experience in the area of digital computers. Students of this background will not only build the machine, but will later use it to learn how a computer operates.

It is anticipated that this machine will find varied applications in its role as an instructional computer. One of the most likely areas will be in classroom demonstrations. Here, the emphasis will be on how a digital computer functions internally, rather than (as is so often the case) how the computer brings in data and (somehow) turns out answers. Class demonstration requires two things: first, a console so designed that the students can clearly see the contents of the various registers; second, a provision for slow-speed operation so that the students can see each step of the computation as it is performed. Also, it is obvious that the demonstration machine should be sufficiently simple that it may be understood (both internally and externally) and

used by students in computer design courses.

Another possible application for such a machine would be as a test computer for various research and development projects involving pulse or digital circuitry. In other words, the computer might be called upon to serve as a programmable pulse generator. Perhaps the most important consideration here would be reliability. A student who is using the computer as a device to test, for example, a transistorized shift register, needs an extremely reliable machine. If the test set-up does not function properly, he should be quite certain that the failure is in his device, rather than in the computer. The example of a transistorized shift register points up another consideration: the OSTIC should have, in addition to a "standard" console (indicator lights and switches), a large patch panel where all computer pulses, gates, and register outputs are available for circuit use, together with adjustable power supply voltages. A panel of this type would not only be convenient for the application mentioned; it would be invaluable for machine maintenance. A third consideration might be mentioned here: test equipment should be easily set up and versatile in operation. The versatility may be taken care of by a flexible instruction list, but a large amount of set up time would be required if the user (who would probably need only a five- or ten-instruction program) had to enter each instruction into the drum memory, either by operating the console or by punching and then reading-in cards or paper tape. One solution to this problem might be a separate read-only memory of eight, sixteen, or thirty-two words, addressable by the computer in a manner similar to the regular memory and physically provided by a bank of toggle switches on the console.

The existence of a controls laboratory at OSU containing a number of analog computers suggests another possible application

for the OSTIC. This would be as an element in a digital control system, or in the area of real-time systems investigation. Here, the requirement is not only for reliability, but also for a high degree of flexibility in both programming and in data transfer. Programming flexibility would seem to imply the presence of a variety of test and branching codes, perhaps together with some sort of masking or logical operations. The emphasis here would not be on the standard arithmetic operations of addition, subtraction, multiplication, and division, but rather on the controlling functions. The problem of data transfer would imply flexibility in input/output equipment, with perhaps a number of buffered peripheral units.

Since this machine will be a digital computer, the question of computation for problem solving might be raised. It is anticipated that the OSTIC will be used little, if at all, for this type of operation, since computers are already available on campus with much more speed and many programming aids. The problems inherent in writing even a small program for a binary computer with no compiler or assembly routines available make such an application extremely unlikely, to say the least.

Finally comes the all-important question of maintenance.

This computer will be maintained by students and technicians who will probably not be overly familiar with computers in general, and who certainly cannot be expected to become intimately acquainted with the operation of each individual circuit. Also, there will be a continuing turnover in the student personnel associated with maintaining the computer. The entire machine must be designed with this in mind; maintenance procedures, especially those concerned with pin-pointing malfunctioning units, should be extremely simple and straight-forward.

Upon taking all of the foregoing considerations together,

one finds that a fairly clear-cut design philosophy emerges. It becomes clear that a simple machine organization is desirable, from the standpoint of the graduate student whose thesis project forms a part of the machine and who needs to understand its place in the overall design; from the standpoint of the school, since simplicity usually implies economy of components; from the standpoint of the student in a computer design course, whose first contact with the "insides" of a computer will probably be through the OSTIC; from the standpoint of the students (and faculty) who use the computer; and from the standpoint of the maintenance personnel, for whom an easily understood machine is usually an easily repaired machine.

The OSTIC should be an extremely reliable computer, both because a large amount of time (and money) will probably not be available to make constant repairs, and because some of the areas of greatest benefit will be those in which the computer is used as a means of testing and monitoring the performance of other equipment.

The final design criterion forces the designer to make so-called "engineering decisions". This is the requirement that the computer be practical; in other words, the OSTIC should be not only usable, but useful. It was noted that the uses for this machine would be primarily in the areas of demonstration, test, and system investigation. These applications necessitate a flexible computer, with perhaps a limited arithmetic command list, but with an extremely flexible list of testing and data-handling commands. Implicit also is a rather large console, with many operating options. In order to justify the effort that has been and will be put into the design and construction of this computer, a machine of maximum usefulness must be the constant goal.

#### CHAPTER II

#### THE OVERALL SYSTEM ORGANIZATION OF THE OSTIC

This chapter presents a discussion of the overall system organization developed using the criteria presented in the preceding chapter. The basic tenets set forth in this chapter are the foundations upon which the remainder of the design rests.

Because of the requirements of component economy, simplicity, and reliability, the binary number system was selected for use in the OSTIC. Practically every text on digital computers presents material on the choice of a number system (1,2,3,4); it will suffice to state here that this computer would be much more expensive and complicated if built as codeddecimal machine, and further, that the use of a binary computer in digital instructional courses is not a desadwantage to the student, since many computers in the "real world" are natural binary machines.

A second fundamental decision was that the OSTIC should be a parallel machine. "Parallel", as used here, means that the binary digits, or bits, of a given computer word are always transmitted and operated upon simultaneously. It was decided that the bits of any given word would be stored in parallel on the magnetic drum, that they would be read off of the drum in parallel, and that they would be moved about within the machine in parallel. The primary consideration in selecting parallel operation was that the OSTIC was to be used for slow speed or step-by-step demonstration in the classroom; it was felt that a parallel computer would be more readily understood by the students than would a serial machine. Also, a parallel computer can be

organized and built in a more straight-forward manner; if a separate wire is assigned to each bit, the circuit designer has fewer problems. Finally, it should be noted that most authors agree that a serial machine uses fewer components (1,4); in this case, the economy consideration was compromised somewhat for the sake of overall design simplicity.

The next problem was to select the method of instruction sequencing. Four-address, three-address, two-address, one-plus-one address, and single-address computers have been built, and each system has its advantages. The system chosen for the OSTIC was the singleaddress system, whereby the instruction word specifies the operation to be performed and (normally) the location of the operand. A special counter, called (in the OSTIC) the "Instruction Counter", keeps track of the location of the next instruction. The Instruction Counter is incremented at some time during the execution of each instruction, and it is presumed that the next instruction will always be placed (by the programmer) at the memory location corresponding to the contents of the Instruction Counter. Again, the singleaddress system was chosen for reasons of economy and simplicity of design; it is not an exaggeration to observe that a three-or fouraddress machine is a programmer's dream and a designer's nightmare.

Having decided upon parallel binary operation, using a magnetic drum memory for storage of both data and single-address instructions,

Some examples of computers using the various types of address structure are:

the rest of the functional units of the OSTIC may be specified. It was decided to use a double-length, doubly-addressable accumulator, and to refer to the two halves as the "UPPER" (high-order) and "LOWER" (low-order) ACCUMULATORS. A word distributor, or "D-REGISTER" was chosen for temporary storage of operands and to perform miscellaneous tasks. A register to store the current instruction is implicit in a digital computer; in the OSTIC this is called the "INSTRUCTION REGISTER", and may be further described as a combination of an "OPERATION REGISTER" and an "ADDRESS REGISTER". The INSTRUCTION COUNTER has been previously mentioned; it would operate in conjunction with an "INCREMENT REGISTER" that would perform operations associated with incrementing the INSTRUCTION COUNTER.

In addition to the units mentioned above, an "AUXILIARY COUNT-ER" was found to be necessary for certain operations. The possibility exists (although somewhat remote) that indexing registers might be added to the OSTIC; therefore, they should be included as functional units. It should be noted that the input/output equipment (except for the console) is not considered, since its characteristics do not enter into the internal organization.

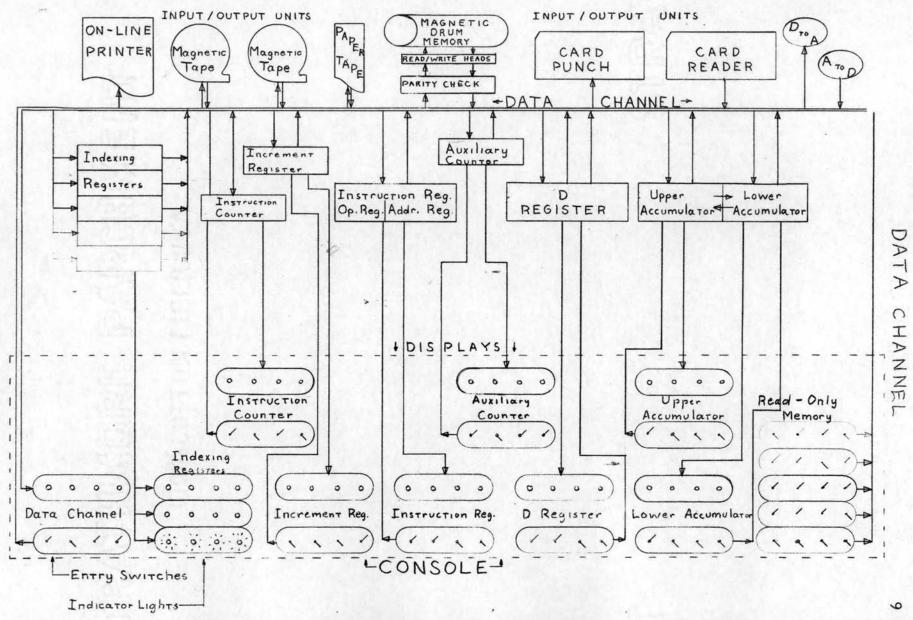

Logical Diagram number 1 (Figure 1) presents the functional units of the OSTIC, and the manner in which they are tied together for data transmission purposes. The common point is the "DATA CHANNEL", a group of bit lines that handle all data transmission between the drum and any register, between registers, and betweeh input/output units and the memory. Both data words and instruction words pass over the DATA CHANNEL. The cycle impulses, together with the output of the OPERATION DECODER, ADDRESS DECODER, or address comparison circuits (none of which are shown on Logical Diagram number 1), cause the output lines of a given unit to be

Figure 1. Logical Diagram number 1, Data Channel.

gated onto the DATA CHANNEL. A moment later the input lines of some other unit are gated from the DATA CHANNEL. After the transfer of data or an instruction has occurred, the DATA CHANNEL input gate is removed, and then the DATA CHANNEL output gate is removed. The entire operation of this computer is based upon the data channel concept, since the acquisition and execution of all computer instructions involves basically little more than the gating of the proper units onto and off of the data channel in some predetermined sequence.

Upon examination of Logical Diagram number 1, several other design concepts become apparent. One of the most important is that since all of the operating units share the same DATA CHANNEL, it is not at all difficult to make all of them addressable in the program. This concept is relatively new in computer design (5,6), and while simplifying the construction of the machine, it vastly increases the flexibility of programming.

It will be noted also that each unit communicates directly with the computer console, rather than indirectly through the DATA CHAN-NEL. While this approach results in a rather imposing console with many indicator lights and switches, it is felt that enabling the student to read the contents of all units simultaneously would be invaluable for classroom demonstration. The ability to enter data into any register by merely setting the data word in a row of toggle switches and pushing an "enter" button has advantages in ease of operation.

The "READ-ONLY MEMORY, as shown on Logical Diagram number 1, is simply a number of rows of toggle switches mounted in one section of the console. Each row would correspond to one word of memory and would be addressable for read-out in the same manner as the drum memory.

Finally, it should be pointed out that the various types of in-

put output units in Logical Diagram number lare shown for illustration only. It is presumed, however, that these units or their buffers will communicate with the DATA CHANNEL.

The remainder of this paper will describe the method of controlling the operation of the various units.

#### CHAPTER III

#### MEMORY AND TIMING

As is true with most digital computers using a rotating magnetic drum for the main memory, timing in the OSTIC is a function of the angular position of the drum. The drum in the OSTIC

rotates at a nominal 3450 rpm (one revolution equals approximately 17.4 milliseconds). It is 7 1/2 inches in diameter by 10 inches in

length. One-hundred-twenty-eight read/write heads are located

around the drum, and a permanently machined timing track providing 2560 timing pulses per drum revolution (one timing pulse

every 6.8 microseconds) is located at one end.

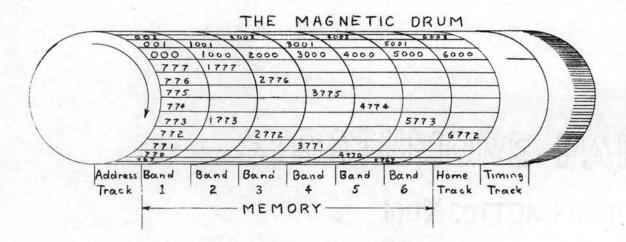

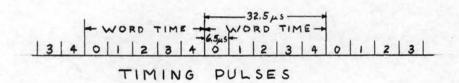

Since it was decided to read data onto and off of the drum in parallel, words could be located as desired. Accordingly, the 2560 timing pulses available were divided among 512 word times, providing five timing pulses per word (see Figure 2). word time in the OSTIC is then equal to approximately 34.0 microseconds. A "home" pulse will be provided on a separate timing track, and "address" tracks will be permanently recorded with the binary word addresses 000 000 000 to 111 111 111, which is equivalent to words 000 to 7778, or to words 000 to 51210 (note that the choice of 512 word times per revolution provides convenient addressing, since  $2^{9} = 512_{10}$ ). Word location  $000_{8}$  will immediately follow the home pulse in angular position, and location 7778 will immediately precede it. The five timing pulses for the ith word time will be denoted by  $T_i^0$ ,  $T_i^0$ ,  $T_i^2$ ,  $T_i^3$ , and T,4, or more generally (where the particular word time is unimportant) as 0 time, 1 time, 2 time, 3 time, and 4 time. This timing convention will be used throughout the remainder of this paper.

#### SUGGESTED BAND ADDRESSES

| Band number | Use                                                                   |

|-------------|-----------------------------------------------------------------------|

| 0-23456     | Registers, Read-only memory Band 1 Band 2 Band 3 Band 4 Band 5 Band 6 |

| 7           | Input / Output Equipment                                              |

Figure 2. Memory, Timing, and Words.

The timing pulses, home pulse, and address pulses will be read by read/write heads that have had their write circuits disabled. The pulses will go into a "CLOCK REGISTER" that will provide the various pulses and gates needed by the rest of the machine, as well as providing a constant check on the timing and address pulses to see that they occur in the proper order.

To reduce timing problems, the address pulses of word  $T_i$  will be permanently recorded in such a manner that they will be available for checking at  $T_i$  1 time. The bits of word  $T_i$  itself will be written onto and read off of the drum at  $T_i$ 3 time. Chapter 5 relates the use of address pulses in reading from and writing onto the drum.

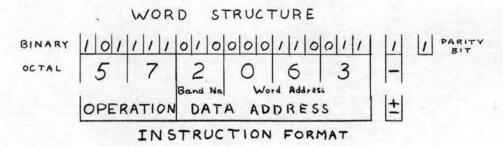

It was decided to use a word length of 18 bits in the OSTIC, together with a sign bit and a parity bit. The sign bit is transmitted with the word bits, but is not considered an integral part of the word for purposes of shifting and multiplication. The parity bit is used only in conjunction with drum storage; it is generated by the "PARITY REGISTER" on a "drum write" (store) operation, and is checked by the PARITY REGISTER on a "drum read" operation. The parity mode is "even parity", as is used by most parity-check devices; the total number of bits in a word, including sign and parity bit, is always supposed to be an even number.

The use of an 18 bit word for both data and instructions brings up the question of instruction format and addressing. It was stated previously that there were 512 word times during one revolution of the drum. In order to represent 512 separate addresses in binary form, 9 bits must be used  $(2^{9} = 512)$ . However, it would be desirable to have more than 512 memory locations; in fact, if a total of twenty bits are recorded on the drum for each word (18 word bits, 1 sign bit, 1 parity bit), a total of 20 read/write heads are all that are necessary to store 512 words, while some 128 read/write heads

are available. A further consideration is that since binary notation is somewhat unwieldly for everyday use, it would be very desirable if programming of the computer could be done in octal (base 8) notation. Octal requires 3 binary bits for each octal digit; therefore, binary addresses must be in multiples of 3 bits if they are to be represented in octal form.

In view of these considerations, it was decided to use 12 bits of the instruction word for the data address, and the remaining six bits for the operation code. This resulted in a 6 octal digit instruction (see Figure 2) the first two digits of which were the operation code, and the last four were the address. Further, the address may be divided into a "band address" for the first octal digit (first three bits) and a "word address" for the last three octal digits (last nine bits). The drum memory thus was planned to have six bands of 512 words each, for a maximum (if all are used) of 3072 words of drum memory.

In addition, it is proposed that OSTIC be provided with either sixteen or thirty-two words (a power of two would present fewer problems in the address circuits) of "read-only" memory in the form of switches on the control console. These memory words will be addressable only on read operations; the binary system in the computer will allow the use of relatively inexpensive single-pole double-throw toggle switches. The availability of a fairly large, quickly altered read-only memory would be invaluable for demonstrations and test programs.

It will be noted that since band numbers 0 and 7 are not used for drum addresses, there are 512 addresses of the form 0XXXg and and 512 addresses of the form 7XXXg also available. It is intended therefore, that the 0XXX addresses be reserved for internal machine use (register addresses, read-only memory, etc.), while the 7XXX addresses be reserved for input/output equipment.

It is intended that band addresses I through 6 be reserved for drum addresses, even though not all six bands are used at first.

The use of two octal digits for operation codes results in a possible command list of 6410 operation codes, ranging from 00 to 778. If the sign of an operation were also taken into consideration, a total of 12810 operation codes could be used. This, however, is not recommended. Further discussion of this point will be found in Chapter 10.

To summarize briefly, the drum memory is divided into six bands, numbered from one to six. Each band contains 512 words, numbered from 000 to 7778. Each word has eighteen bits, one sign bit, and (on the drum only) one parity bit, for a total of twenty bits. The instruction word uses the first two octal digits of the word for the operation code, and the last four for the address. The address is broken down into a one digit band number (or band address) and a three digit word address.

Internally, the machine uses five timing pulses per word time, called (for the ith word)  $T_i^0$ ,  $T_i^1$ ,  $T_i^2$ ,  $T_i^3$ , and  $T_i^4$ . Where the particular word is of no importance, 0 time, 1 time, 2 time, 3 time, and 4 time will be used. The word addresses corresponding to the addresses of the words in each band are recorded on special address tracks; these are available at 1 time, while the contents of the word itself are available at 3 time.

#### CHAPTER IV

#### CYCLES AND CONTROL

Almost every digital computer must perform, internally or externally, two basic functions. One of these is to acquire, by some means, the next instruction to be executed. The other is to execute that instruction.

No matter how simple or how complex the individual instruction, the computer performs its operations in this manner. It has been said that a digital computer is perhaps the most complex form of sequential machine, since at the start of a program the instructions and data stored internally will (if no input is assumed to occur during the program) determine the state of the machine at any later time until the program is completed.

Thus, the computer steps through a program, finding an instruction, executing it, finding the next instruction, executing it, etc. The time consumed in acquiring the next instruction in the OSTIC will be called the "instruction cycle", and the time consumed in executing that instruction will be called the "data cycle", although data may not always be transferred on all data cycles.

The term "cycle" should be further defined, since a misconception could easily result from its indiscriminate use. As used here, a "cycle" is one or more whole word times, a word time being considered to run from the leading edge of one 0 time pulse to the leading edge of the next 0 time pulse. A cycle may sometimes consist of only one word time, as, for example, the time required to acquire the next instruction from the D-register (see Chapter 5), or it may require many word times, as, for example, in the

case of acquiring a multiplicand from drum storage, then multiplying it by a multiplier in the upper accumulator. However, one rule is steadfast; in the OSTIC, a cycle is always composed of an integral number of whole word times.

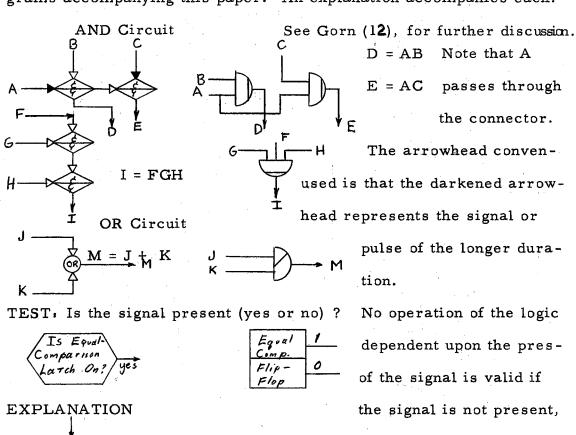

The method of execution of the various operations in this computer will be illustrated by Logical Diagrams, using special graphical symbols. The reader is referred to Appendix A for an explanation of the symbols used.

It is planned that the selection of the appropriate cycle (data or instruction) will be performed by a "CYCLE SELECTION FLIP-FLOP" (bistable multivibrator) as shown on Logical Diagram number 2 (Figure 3). When one side of this flip-flop is conducting, the computer will be in the data cycle mode; when the other side is conducting, the machine will be in the instruction cycle mode.

The general operation of cycle selection is also illustrated in Logical Diagram No. 2. Briefly, the CYCLE SELECTION FLIP-FLOP is set to one mode or the other by a "CYCLE TURN-ON" pulse at 0 time. The CYCLE-TURN ON pulse (a very sharp pulse of short duration) is allowed to set the CYCLE SELECTION FLIP-FLOP only when a "CYCLE END" impulse has turned on one of the two "CYCLE END latches" during the previous word time.

A detailed description of the operation will now be presented, using the timing chart on Logical Diagram No. 2. Reading from left to right, it is seen that the CYCLE SELECTION FLIP-FLOP is assumed to be set for data cycles, resulting in the DATA CYCLE MASTER gate being on at the start of the time interval under consideration. A "DATA CYCLE END" impulse is then assumed (upper left corner of diagram, reading downward). Although this

Figure 3. Logical Diagram number 2, Master Cycle Control.

pulse began at 0 time, it was inhibited by the CYCLE TURN-ON pulse. At 0 time, however, the CYCLE TURN-ON pulse is not present, while the DATA CYCLE MASTER gate is on, so the DATA CYCLE END pulse turns on the "DATA CYCLE END latch". This latch is simply a resettable flip-flop.

At 0 time of the next word time, since the DATA CYCLE END latch is on, the CYCLE TURN-ON pulse is able to set the CYCLE SELECTION FLIP FLOP to INSTRUCTION CYCLE. The INSTRUCTION CYCLE MASTER gate, turning on, causes the DATA CYCLE END latch to be reset, or turned off.

Sometime between 0 and 4 time of the instruction cycle, an INSTRUCTION CYCLE END pulse occurs. Since the CYCLE TURN-ON pulse is not present to inhibit it, and the INSTRUCTION CYCLE MASTER gate is present, the INSTRUCTION CYCLE END impulse turns on the INSTRUCTION CYCLE END latch. At 0 time of the following word time, the CYCLE TURN ON pulse is gated by the AND circuit from the INSTRUCTION CYCLE END latch to set the CYCLE SELECTION FLIP-FLOP to data cycle. The DATA CYCLE MASTER gate, turning on, resets the INSTRUCTION CYCLE END latch to the off position.

The salient points are that there exists either a DATA CYCLE MASTER gate or an INSTRUCTION CYCLE MASTER gate at all times; that these gates remain on until set to turn off by CYCLE END impulses; that the turn-off or END impulses may occur at 1, 2, 3, or 4 time for data cycles, or at 1, 2, or 3 time for instruction cycles; and that the MASTER GATES are always on from 0 time of one word time to 0 time of a later word time or, in other words, that the MASTER GATES are always on for integral multiples of word times.

Logical Diagram number 3 (Figure 4), Instruction Cycle Control, will now be examined. It will be noted that the INSTRUC-

Figure 4. Logical Diagram number 3, Instruction Cycle Control.

Instruction Cycle End Largh

Instruction Courter Increment

TION CYCLE MASTER gate, CYCLE TURN-ON pulse, and INSTRUCTION CYCLE END latch are repeated from the previous diagram.

Referring to the diagram and timing chart, it will be noted that as long as the INSTRUCTION CYCLE MASTER gate is on, the WORD TIME pulse is gated by an AND circuit to provide an INSTRUCTION CYCLE gate for the rest of the machine. In other words, the INSTRUCTION CYCLE MASTER gate does not itself provide instruction cycles to the rest of the computer; rather, it controls another impulse to provide this function. Also note that whenever the INSTRUCTION CYCLE END latch has been turned on by an INSTRUCTION CYCLE END impulse, the WORD TIME pulse is inhibited by the CYCLE TURN-ON pulse. This is to prevent signal race problems caused by a lag in the turning off of the INSTRUCTION CYCLE MASTER gate (7).

The only other item requiring explanation on Logical Diagram No. 3 is the procedure for incrementing the INSTRUC-TION COUNTER. It was mentioned previously that the location of the next instruction will always be found in this counter; therefore, after an instruction is acquired on an instruction cycle, the INSTRUCTION COUNTER should be incremented so that it will contain the address of the next instruction. Note that nothing has yet been said concerning the size of this increment. Most, if not all, single address computers are constructed so as to take the next instruction from the location immediately following the last instruction. For example, an instruction might be stored in location 2301, the next instruction in 2302, the next in 2303, and so on. This would imply an increment of one. It is proposed that the OSTIC be equipped to increment the INSTRUCTION COUNTER by 1, 2, 4,  $8_{10}$ ,  $16_{10}$ ,  $32_{10}$ ,  $64_{10}$ , or  $128_{10}$ . Since the OSTIC's instruction counter is a binary

device, this method of variable incrementation is seen to be merely a matter of adding a 1 into the first, second, third, fourth, fifth, sixth, seventh, or eighth position of the twelve-position binary counter. It can be shown that this relatively simple device will greatly increase the operating speed of the computer (see Chapter 11).

The desired increment is placed in the INCREMENT REGISTER some time beforehand (see Chapter 9 for details), and thus the problem here is simply to provide an INCREMENT pulse to the INCREMENT REGISTER at the proper time. This pulse will be gated by the INCREMENT REGISTER into the proper position of the INSTRUCTION COUNTER. Incrementing is accomplished by the INSTRUCTION COUNTER INCREMENT pulse, occurring at 4 time, which is gated by the INSTRUCTION CYCLE MASTER gate. If the INSTRUCTION CYCLE END latch is on, an AND circuit will allow the INCREMENT pulse to enter the INCREMENT REGISTER. It will be noted that the only time the INSTRUCTION COUNTER can be incremented is at 4 time of the last word time of an instruction cycle; this must be so, because during any other part of the instruction cycle the machine will be using the contents of the INSTRUCTION COUNTER in seeking the next instruction. This also explains why INSTRUC-TION CYCLE END pulses must occur prior to 4 time.

Logical Diagram No. 4 (Figure 5) illustrates the logic used on data cycles. This logic is necessarily more complex than the instruction cycle logic, because while essentially the only operation performed by the computer on the instruction cycle is to search for and acquire the next instruction, data cycles involve the testing, adding, shifting, and so on necessary to carry out the instructions. In general, the data cycle is broken up into one, two, or three sub-cycles (each of which may

Figure 5. Logical Diagram number 4, Data Cycle Control.

be one or many word times in length). These sub-cycles are called "DATA FIRST CYCLE", "DATA SECOND CYCLE", and "DATA THIRD CYCLE". Whenever the computer goes from instruction cycle operation to data cycle operation, the first word time of the data cycle is always a DATA FIRST CYCLE. If an impulse is received during that word time to turn on a DATA SECOND CYCLE, the next word time will be a DATA SECOND CYCLE; if no such impulse is received, the machine will remain in DATA FIRST CYCLE operation until either a TURN-ON DATA THIRD CYCLE or a DATA CYCLE END impulse is received. If the machine is in DATA THIRD CYCLE operation, the only impulse that will bring about a change is a DATA CYCLE END impulse. The computer can never go from DATA THIRD CYCLE back to DATA FIRST CYCLE or DATA SECOND CYCLE nor can it go from DATA SECOND CYCLE to DATA FIRST CYCLE. In other words, the operation always starts with DATA FIRST CYCLE and proceeds (when so directed by "TURN-ON" impulses) to DATA SECOND CYCLE, and thence to DATA THIRD CYCLE. The data cycle may be ended at the end of any word time by a DATA CYCLE END impulse at any time (other than 0 time) of that word time, regardless of the occurrence of a TURN-ON impulse at any time during that word time. In other words, DATA CYCLE END takes precedence over a TURN-ON impulse.

The operation of the data cycle control will be illustrated using the timing chart and Logical Diagram number 4 (Figure 5). It is assumed that an instruction cycle precedes the data cycle. The instruction cycle ends at 0 time, and the DATA CYCLE MASTER gate turns on. The DATA CYCLE RING COUNTER has been previously reset to first cycle, and the STEP ANTIC-IPATION latch has been reset. Thus, as soon as the DATA

CYCLE MASTER gate is available, it gates the WORD TIME pulse to the first cycle AND circuit. Since the DATA CYCLE RING COUNTER is set to first cycle, the WORD TIME pulse is available to the rest of the machine as a DATA FIRST CYCLE pulse. The DATA FIRST CYCLE pulses are available for three word times. During the third word time, a TURN-ON DATA SECOND CYCLE impulse is received. Since the DATA CYCLE MASTER gate is on, the first cycle stage of the DATA CYCLE RING COUNTER is on, and both the second and third stages are off, the TURN ON pulse sets the STEP ANTICIPATION latch. At 0 time of the next word time, the CYCLE TURN-ON pulse is available through an AND gate controlled by the DATA CYCLE MASTER gate. The CYCLE TURN ON pulse tests the setting of STEP ANTICIPATION latch by means of an AND circuit. If the STEP ANTICIPATION latch is set, the CYCLE TURN ON pulse momentarily inhibits the output of the WORD TIME pulses until the DATA CYCLE RING COUNTER can advance, and also resets the STEP ANTICIPATION latch. WORD TIME pulses are then available from the DATA SECOND CYCLE output.

The timing chart shows the DATA SECOND CYCLE pulses as being available for two word times. During the second word time, a TURN-ON DATA THIRD CYCLE impulse is received, which (since first and third cycles are off, and second cycle is on) turns on the STEP ANTICIPATION latch. Later, during the same word time, a DATA CYCLE END impulse is received (this pulse sequence can occur on accumulator add-in operations, among others; see Chapter 6). The DATA CYCLE END impulse turns on the DATA CYCLE END latch. At 0 time of the next word time, the CYCLE TURN-ON pulse is prevented

by the DATA CYCLE END latch from advancing the RING COUNTER. Instead, the CYCLE TURN-ON pulse resets the RING COUNTER to first cycle, resets the STEP ANTICIPATION latch, inhibits the WORD TIME pulse (to prevent signal race problems), and sets the CYCLE SELECTION FLIP-FLOP to data cycle (see, also, Logical Diagram number 2).

Two word times of instruction cycle are then shown on the timing chart. Following that come two word times of DATA FIRST CYCLE pulses, followed by one word time of DATA SECOND CYCLE. During this word time a TURN-ON DATA THIRD CYCLE is received, as before. Since no DATA CYCLE END pulse is received, however, the CYCLE TURN-ON pulse can then step the RING COUNTER to third cycle and reset the STEP ANTICIPATION latch. Two word times of DATA THIRD CYCLE follow, during the second of which a DATA CYCLE END impulse sets the DATA CYCLE END latch. The operation of resetting the various latches and changing to the instruction cycle proceeds as before.

It is important to remember that a data cycle may consist of a DATA FIRST CYCLE, DATA SECOND CYCLE, and DATA THIRD CYCLE. These cycles may consist of one or more word times, and are changed by TURN-ON DATA SECOND CYCLE or TURN-ON DATA THIRD CYCLE impulses. The first cycle taken after the machine goes into data cycle operation is the DATA FIRST CYCLE. If a DATA CYCLE END impulse occurs, data cycle operation ceases at the end of that word time, regardless of any TURN-ON pulses.

#### CHAPTER V

#### DATA ACQUISITION AND TRANSMISSION

Having developed the logic of providing control cycles for the computer, attention will now be directed toward the matters of acquiring data and instructions for immediate use, and storing data for future use.

Basically, the computer acquires a word for one of two purposes; either on a data cycle for use in arithmetic operations, in which case the word would be called an "operand", or on an instruction cycle, in which case the word would be used as the next instruction. Various miscellaneous transfers of words or portions of words may be made during the execution of certain instructions, but these will be of no concern in this chapter. The computer may acquire a word from either the magnetic drum, which will be called a "drum read" operation, or from an internal register, which will be called a "non-drum read" operation. Storage of words onto the magnetic drum will be termed a "drum write" operation, and may occur only during a data cycle (storage occurring during input operations is not considered here; see Chapter 10).

Drum Read operation is illustrated on Logical Diagram number 5 (Figure 6), and its associated timing chart. The basic operation is simply that the contents of some drum address is desired. The address is sought, and, when found, the bits in that location are read onto the DATA CHANNEL and thence into the appropriate register.

Read operations during a data cycle will only occur on DATA FIRST CYCLES. The presence of the OPERAND gate

Figure 6. Logical Diagram number 5, Drum Read.

(from the OPERATION DECODER) signals that it is desired to read the contents of some storage location (or register) into the D-REGISTER. Read operations during an instruction cycle will be signaled simply by the presence of an INSTRUCTION CYCLE gate (since the only purpose of an instruction cycle is to acquire the next instruction). The contents of the desired storage location (or register) will be read into the INSTRUCTION REGISTER.

The ADDRESS pulses are available from the read heads at approximately 1 time, and are compared against the contents of the INSTRUCTION COUNTER (on instruction cycles) or against the contents of the ADDRESS REGISTER (on data cycles). If an equal comparison is detected, the contents of the word are read onto the DATA CHANNEL when the bit pulses are available from the read heads at 3 time, and are read in from the DATA CHANNEL into the appropriate register.

using the timing chart at the bottom of Logical Diagram number 5, it is seen that at the beginning of the interval the INSTRUCTION CYCLE gate is assumed to be on. At 0-1-2 time the ADDRESS TEST pulse is gated by the INSTRUCTION CYCLE gate to interrogate the band number of the address contained in the INSTRUCTION COUNTER. If the band number is in the range 1 through 6, the ADDRESS TEST pulse is allowed to gate the ADDRESS pulses from the word address comparison circuitry. These ADDRESS pulses are read from the address track at approximately 1 time and, if the INSTRUCTION CYCLE gate is on, are compared with the word address portion of the INSTRUCTION COUNTER. If an unequal comparison occurs, no output results, and the comparison is made again with the next set of ADDRESS pulses. If, as in the timing chart, an equal comparison occurs, a 1 time pulse appears at the output

Commence of Agency of

of the word address comparison circuit. This pulse is gated by the ADDRESS TEST pulse to turn on the EQUAL COMPARISON latch. At 2-3-4 time the READ IN pulse, gated by the INSTRUC-TION CYCLE gate, gates the INSTRUCTION REGISTER to read in from the DATA CHANNEL. At approximately 3 time the EQUAL COMPARISON latch gates the bit pulses of the desired word into the PARITY REGISTER and thence onto the DATA CHANNEL, from which they are read into the INSTRUCTION REGISTER. The word is always read through the PARITY REGISTER onto the DATA CHANNEL, and if the parity is incorrect, the PARITY ERROR latch is turned on for future use. At 3 time the CYCLE TEST pulse tests the circuit, and since the INSTRUCTION CYCLE gate and the EQUAL COMPARISON latch are on, the CYCLE TEST impulses INSTRUCTION CYCLE END. The EQUAL COMPARISON latch, if on, is turned off at 0 time (not shown).

The next word time after an INSTRUCTION CYCLE END impulse is automatically a DATA FIRST CYCLE (see Chapter 4). If the OPERAND gate is on, the DATA FIRST CYCLE impulse allows the ADDRESS TEST pulse to test the band address of the ADDRESS REGISTER and the ADDRESS pulses from the word address track to be compared with the word address in the ADDRESS REGISTER. As is shown on the timing chart, several word times (512 maximum) may pass before the equal comparison occurs. When it does occur, the ADDRESS TEST pulse provides a gate allowing the equal comparison pulse to turn on the EQUAL COMPARISON latch. At 2-3-4 time the READ-IN pulse is gated by the DATA FIRST CYCLE-OPERAND gate to allow the D-REGISTER to be read in from the DATA CHANNEL, and at 3 time the bit pulses of the desired word are gated by the EQUAL COMPARISON latch to pass through the PARITY REGISTER, onto the

DATA CHANNEL, and into the D-REGISTER. Also at 3 time the CYCLE TEST pulse is gated by the DATA FIRST CYCLE-OPERAND gate to test the circuit. If the LOAD D-REGISTER gate were on, this would imply that the only operation desired was to read the desired word into the D-REGISTER, and as soon as this was accomplished, DATA CYCLE END would be impulsed. It will be noted that TURN-ON DATA SECOND CYCLE is always impulsed at 3 time of the word time during which the operand is acquired, and DATA CYCLE END is also impulsed if LOAD D is on.

Non-drum read, Logical Diagram number  $\theta$  (Figure 7), is similar to drum read, except that the desired word is located somewhere other than on the magnetic drum. The operation is exactly the same as far as the testing of the band numbers is concerned. However, the presence of a 0 band number indicates a non-drum location, and the operation proceeds somewhat differently from that point.

Using the timing chart on Logical Diagram number 6, it is found that a data cycle is the first complete cycle shown. At 0 time the DATA FIRST CYCLE pulse is gated by the OPERAND gate and allows the ADDRESS TEST pulse to test the band number of the ADDRESS REGISTER. The NON-DRUM READ latch is turned on at approximately 0 time (if a 7 band number were detected, the STORAGE SELECTION ERROR latch would also be turned on. The NON-DRUM READ latch, together with the DATA FIRST CYCLE-OPERAND pulse, gates the contents of the ADDRESS REGISTER in to the ADDRESS DECODER. The DATA FIRST CYCLE-OPERAND gate also allows the READ-IN pulse to gate the D-REGISTER for read-in from the DATA CHANNEL at 2-3-4 time. Meanwhile, the ADDRESS DECODER has selected the desired register, and at 3 time a WRITE pulse reads the contents

Figure 7. Logical Diagram number 6, Non-Drum Read

of the desired register onto the DATA CHANNEL and thence into the D-REGISTER. Also at 3 time the CYCLE TEST pulse interrogates the circuit through an AND gate from the DATA FIRST CYCLE-OPERAND gate. TURN-ON DATA SECOND CYCLE is always impulsed, and if the LOAD D-REGISTER gate is on, DATA CYCLE END is impulsed. The NON-DRUM READ latch is reset at 4 time. Note that only one word time is needed to acquire a non-drum operand.

If the INSTRUCTION CYCLE gate is on, the ADDRESS TEST pulse interrogates the band number of the INSTRUCTION COUNTER. If the band number is 0, the NON-DRUM READ latch is turned on and the contents of the INSTRUCTION COUNTER gated into the ADDRESS DECODER. The INSTRUCTION CYCLE gate allows the READ-IN pulse to gate the INSTRUCTION REGISTER to read in from the DATA CHANNEL at 2-3-4 time, and the WRITE pulse, together with the ADDRESS DECODER output, reads out the proper register onto the DATA CHANNEL. The CYCLE TEST pulse passes through the INSTRUCTION CYCLE gate and NON-DRUM READ latch gate to impulse INSTRUCTION CYCLE END at 3 time. The NON-DRUM READ latch is reset at 4 time to prevent transient outputs from the ADDRESS DE-CODER caused by the INSTRUCTION COUNTER being incremented at 4 time. Note that this seemingly innocuous Logical Diagram implies that the contents of any register may be used as either data or as the next instruction. This is a feature that is comparatively rare in computer design. (6).

The last class of operations covered in this chapter will be the "drum write" or "store" operations, Logical Diagram number 7, (Figure 8). In the OSTIC, a store operation will only occur on a data cycle, and is only valid for a drum address. The operation will be illustrated using a "store-upper accumulator"

Figure 8. Logical Diagram number 7, Drum Write

operation, in which the contents of the UPPER ACCUMULATOR will be written onto the drum in the location specified by the contents of the ADDRESS REGISTER, and simultaneously read into the D-REGISTER.

The STORE gate allows a DATA FIRST CYCLE pulse to gate the ADDRESS TEST pulse at 0-I-2 time. If the band number of the ADDRESS REGISTER is on the drum, the ADDRESS TEST pulse provides a gate for EQUAL COMPARISON pulses. When the ADDRESS pulses from the address track of the drum are equal to the word address portion of the ADDRESS REGISTER, the EQUAL COMPARISON pulse is gated by the ADDRESS TEST pulse to turn on the EQUAL COMPARISON latch. The DATA FIRST CYCLE-STORE pulse is gated by the UPPER gate to read the contents of the UPPER ACCUMULATOR onto the DATA CHANNEL. At 2-3-4-time the READ-IN pulse is gated by the DATA FIRST CYCLE-STORE to allow the contents of the DATA CHANNEL ato be read into the PARITY REGISTER, where the proper parity bit is generated. At 3 time the WRITE pulse is gated by the DATA FIRST CYCLE-STORE and the EQUAL COM-PARISON latch to write the PARITY REGISTER output into the desired drum location, and also by the UPPER gate (or LOWER, if on) to read the contents of the DATA CHANNEL into the D-REGISTER. Also at 3 time the CYCLE TEST pulse is gated by DATA FIRST CYCLE-STORE and the EQUAL COMPARISON latch to impulse DATA CYCLE END.

Note that a non-drum band number will cause the ADDRESS TEST pulse to set the STORAGE SELECTION ERROR latch and impulse DATA CYCLE END. Also note that the presence of either an UPPER or LOWER gate will cause the contents of the appropriate register to be stored onto the drum and read into the D-REGISTER simultaneously, but the presence of a D gate

will cause only the contents of the D-REGISTER to be read out and stored.

DATA FIRST CYCLES when the OPERAND gate is on, or into the INSTRUCTION REGISTER when the INSTRUCTION CYCLE gate is on. The contents of either a drum location or a machine register may be read in this manner. Store operations, on the other hand, are valid only for drum addresses. These also take place on DATA FIRST CYCLE. The contents of the UPPER ACCUMULATOR or LOWER ACCUMULATOR may be stored on the drum and also automatically placed in the D-REGISTER. The contents of the D-REGISTER may also be stored on the drum.

#### CHAPTER VI

## ACCUMULATOR OPERATIONS

The heart of a digital computer is the accumulator, for it is there that the majority of the operations that justify the existence of the computer are performed.

It is not within the purview of this paper to deal extensively with the detailed design of the accumulator circuits. The writer's philosophy is that the computer will present various gates and pulses to the accumulator at the proper time, and it is then up to those who design the accumulator to provide the desired results at the proper time.

The method of representation of numbers within the OSTIC will be in "sign and magnitude" binary form. In other words, a plus 27<sub>10</sub> would be represented as 00000000000011011 with a 0 (plus) sign. A minus 27<sub>10</sub> would be 0000000000011011 with a 1 (minus) sign. Numbers will always be stored as sign and magnitude, and will usually be used in this form.

The arithmetic operation performed by the accumulator will be that of binary addition of the DATA CHANNEL output to the either the UPPER or LOWER ACCUMULATOR, with end-around carry. In this case, both accumulators will be considered together as a single 36 bit ACCUMULATOR with the sign bit to the right of the low-order position (only one sign bit is used for the entire ACCUMULATOR). On add and subtract operations (but not multiply, shift, or logical operations), the sign bits will be added in a manner similar to the magnitude bits of the words, and a carry (if one occurs) is allowed to propagate from the sign position into the low-order position of the LOWER and

from the high-order position of the UPPER into the sign position. This is called an "end-around carry". For example, in adding +27<sub>10</sub> in the D-REGISTER to +55<sub>10</sub> in the LOWER, the entire ACCUMULATOR and D-REGISTER would appear as

Although the ACCUMULATOR actually consists of two eighteen-bit numbers and a sign bit, to which is added an eighteen-bit

number and a sign bit, most of the remaining examples in this

paper will show an ACCUMULATOR consisting of a ten-bit word

and a sign, to which is added a five-bit word and a sign. The

preceding example should serve to illustrate how unwieldly

eighteen- and thirty-six-bit examples can become. The use

of a shorter word for purposes of explanation does not, of

course, alter the manner in which the operations take place.

Consider, for example, the case in which the ACCUMULATOR

contains a +15, and a +17 is added from the D-REGISTER into

the LOWER.

D-REGISTER (17) 10001 0 ACCUMULATOR (15) 0000001111 0 (32) 0000100000 0

No sea jako katalokaretiima

Subtraction is accomplished in the OSTIC by entering the sign-and-magnitude value of the number to be subtracted (subtrahend) into the D-REGISTER. The 1's complement value of the magnitude portion is then read onto the DATA CHANNEL and added into the ACCUMULATOR. A 1 is also added into the sign position. If the ACCUMULATOR has a minus sign, the magnitude of the number in the ACCUMULATOR must be placed in 1's complement form before the addition operation takes place. If the sign of the result is minus (1), the ACCUMULATOR must

be complemented after addition in order to reflect the correct sign-and-magnitude answer. On subtraction, an eighteen-bit word composed entirely of l's (l's complement of zero) must be added into the LOWER if the l's complement of the D-REGISTER is added into the UPPER, and similarly, l's must be added into the UPPER if the complement of the D-REGISTER is added into the LOWER. If two negative numbers are added, an end-around carry from the high-order position of the UPPER into the sign position must take place and a complement cycle must be taken following the addition. If the end-around carry does not occur, then a number too large for the ACCUMULATOR (overflow) has been generated. If two positive numbers are added, an end-around carry must not take place, and no complement cycle is necessary. If an end-around carry does take place, then an overflow has occurred. If two numbers of opposite sign are added, an overflow is simply not possible, and the presence of an end-around carry indicates that no complement cycle is needed, while the absence of an end-around carry indicates that a complement cycle must follow. Table I will serve to illustrate the above-mentioned rules, using a five-bit UPPER, a five-bit LOWER, and a five-bit D-REGISTER.

This chapter relates the logical operations necessary to accomplish; sixteen possible combinations of resetting the ACCUMULATOR prior to the operation, addition of the D-REGISTER contents to the UPPER or to the LOWER, subtraction of the D-REGISTER contents from the UPPER or from the LOWER. Furthermore, each operation may be executed in algebraic fashion or by using the absolute value (magnitude) of the operand. It is necessary, therefore, to examine the combinations of signs and operations which imply the use of true or complement values.

### TABLE I

## BINARY ADDITION WITH END-AROUND CARRY

| .11111     | 0 | D-REGISTER at start.  |

|------------|---|-----------------------|

| 0010111111 | 0 | ACCUMULATOR at start. |

| 0011011110 | 0 | Correct answer.       |

No end-around carry occurs. No complement cycle needed.

## Example 2. Add D to UPPER.

| 01111      | 0 | D-REGISTER at start.  |

|------------|---|-----------------------|

| 0010111111 | 0 | ACCUMULATOR at start. |

| 1010011111 | 0 | Correct answer.       |

Note that if the sign bit of the number added is 0 (plus), nothing need be added to the LOWER when the D-REGISTER is added to the UPPER, and vice-versa.

## Example 3. Add D to LOWER.

| 00001      | 0 | D-REGISTER at start.  |

|------------|---|-----------------------|

| 1111111111 | 0 | ACCUMULATOR at start. |

| 000000000  | 0 | Partial Sum.          |

|            | 1 | End-around carry.     |

| 000000000  | 1 | Incorrect answer.     |

This example illustrates an overflow. Note that, if both numbers are plus, an end-around carry signals an overflow.

Case II. Two negative numbers are added.

## Example 1. Add D to LOWER.

| 11111      | 1 | D-REGISTER at start.     |

|------------|---|--------------------------|

| 0010111111 | 1 | ACCUMULATOR at start.    |

| 00000      | 1 | D-REGISTER complement.   |

| 11111      |   | l's added into UPPER.    |

| 1101000000 | 1 | ACCUMULATOR complement.  |

| 1100100001 | 0 | Partial sum.             |

| , .        | 1 | End-around carry.        |

| 1100100001 | T | Complement is necessary. |

| 0011011110 | 1 | Correct answer.          |

|            |   |                          |

Note that the end-around carry is necessary to correct the sign, and that a complement cycle is needed after addition.

#### Times 1 1 4. I il I (Continued)

### Example 2. Add D to UPPER

### Example 3. Add D to LOWER

| 00001         | 1  | D-REGISTER at start                     |  |  |

|---------------|----|-----------------------------------------|--|--|

| -111111111111 | 1  | ACCUMULATOR at start                    |  |  |

| 11110         | 1  | D-REGISTER Complement                   |  |  |

| 11111         |    | l's added into UPPER                    |  |  |

| 000000000     | _1 | ACCUMULATOR Complement                  |  |  |

| 1111111111    | 0  | Partial sum                             |  |  |

|               | ?  | No end-around carry, therefore an over- |  |  |

|               |    | flow has occurred                       |  |  |

| 000000000     | 0  | Incorrect answer                        |  |  |

Case III. Numbers of opposite signs are added.

Example 1. D-REGISTER is positive, ACCUMULATOR negative. Add D to LOWER. Result is negative.

```

11111 0 D-REGISTER at start

0010111111 1 ACCUMULATOR at start

11111 0 D-REGISTER true-figure.

1101000000 1 ACCUMULATOR Complement.

1101011111 1 Partial sum.

No end-around carry occurs; therefore,

complement result.

0010100000 1 Correct answer.

```

Example 2. D-REGISTER is positive, ACCUMULATOR negative. Add D to UPPER. Result is positive.

| 11111      | 0 | D-REGISTER at start.                  |  |  |

|------------|---|---------------------------------------|--|--|

|            |   | ACCUMULATOR at start.                 |  |  |

| 11111      | 0 | D-REGISTER true-figure.               |  |  |

|            |   | Partial sum.                          |  |  |

|            | 1 | End-around carry means no complement. |  |  |

| 1100100001 | 1 | Correct answer.                       |  |  |

#### I (Continued)

Example 3. D-REGISTER is positive, ACCUMULATOR negative. Add D to UPPER. Result is negative.

10111 0 D-REGISTER at start.

1111111111 1 ACCUMULATOR at start.

10111 0 D-REGISTER true-figure.

0000000000 1 ACCUMULATOR Complement.

1011100000 1 Partial sum.

No end-around carry, therefore complement result.

0100011111 1 Correct answer.

Example 4. D-REGISTER is positive, ACCUMULATOR negative. Values are equal. Add D to LOWER. Result is zero.

11011 0 D-REGISTER at start.

0000011011 1 ACCUMULATOR at start.

11011 0 D-REGISTER true-figure.

1111100100 1 ACCUMULATOR Complement.

1111111111 1 Partial sum.

No end-around carry occurs; therefore,

complement result.

0000000000 1 Correct answer.

Note that it is possible to develop a negative zero.

Example 5. D-REGISTER is negative. ACCUMULATOR is positive. Add D to LOWER. Result is positive.

11111 1 D-REGISTER at start.

0010111111 0 ACCUMULATOR at start.

00000 1 D-REGISTER Complement.

11111 1 1 s added into UPPER.

0010111111 0 ACCUMULATOR (not complemented).

0010011111 1 Partial sum.

1 End-around carry occurs; therefore, do not complement result.

0010100000 0 Correct answer.

#### I (Continued)

Example 6. D-REGISTER is negative, ACCUMULATOR positive. Add D to UPPER. Result is negative.

11111 1 D-REGISTER at start.

0010111111 0 ACCUMULATOR at start.

00000 1 D-REGISTER complement.

11111 1's added into LOWER.

0010111111 0 ACCUMULATOR (not complemented).

0011011110 1 Partial sum.

No end-around carry occurs; therefore,

complement result.

1100100001 1 Correct answer.

Example 7. D-REGISTER is negative, ACCUMULATOR positive. Add D to UPPER. Result is positive.

10111 1 D-REGISTER at start.

1111111111 0 ACCUMULATOR at start.

01000 1 D-REGISTER complement.

11111 1's added into LOWER.

1111111111 0 ACCUMULATOR (not complemented).

0100011110 1 Partial sum.

1 End-around carry occurs. Do not complement result.

0100011111 0 Correct answer.

Example 8. D-REGISTER is negative, ACCUMULATOR positive. Values are equal. Add D to LOWER. Result is zero.

11011 1 D-REGISTER at start.

0000011011 0 ACCUMULATOR at start.

00100 1 D-REGISTER complement.

11111 1's added into UPPER.

0000011011 0 ACCUMULATOR (not complemented).

1111111111 1 Partial sum.

No end-around carry occurs. Complement result.

0000000000 1 A correct answer of a negative zero is developed.

### I (Continued)

Example 9. D-REGISTER is negative, ACCUMULATOR positive. Values are equal. Add D to UPPER. Result is zero.

```

10101 1 D-REGISTER at start.

0101000000 0 ACCUMULATOR at start.

01010 1 D-REGISTER complement.

11111 1's added into LOWER.

1010100000 0 ACCUMULATOR (not complemented).

1111111111 1 Partial sum.

No end-around carry occurs. Complement result.

000000000000 1 Correct answer.

```

Example 10. Add a positive number in the D-REGISTER to a negative zero in the ACCUMULATOR. Result should be same as D-REGISTER. Use add to LOWER.

| 10101       | 0   | D-REGISTER at start.                     |

|-------------|-----|------------------------------------------|

| 000000000   | . 1 | ACCUMULATOR at start.                    |

| 10101       | 0   | D-REGISTER true-figure.                  |

| 11111111111 | 1   | ACCUMULATOR complement.                  |

| 0000010100  | 1   | Partial sum.                             |

|             | 1   | End-around carry occurred; therefore, do |

|             |     | not complement result.                   |

| 0000010101  | 0   | Correct answer.                          |

Example 11. Add a negative number in the D-REGISTER to a negative zero in the ACCUMULATOR. Result should be same as D-REGISTER. Use add to LOWER.

| 10101       | 1 | D-REGISTER at start.     |

|-------------|---|--------------------------|

| 000000000   | 1 | ACCUMULATOR at start.    |

| 01010       | 1 | D-REGISTER complement.   |

| 11111       |   | l's added to LOWER.      |

| 11111111111 | 1 | ACCUMULATOR complement   |

| 1111101010  | 0 | Partial sum.             |

| ·           | 1 | End-around carry         |

| 1111101010  | 1 | Complement is necessary. |

| 0000010101  | 1 | Correct answer.          |

Note that Examples 10 and 11 illustrate that addition of a positive or a negative number to a negative zero will result in the proper sum.

If the operation is an "Add Magnitude" (or "Reset Add Magnitude") operation, the contents of the D-REGISTER will be given a plus sign and the true value will be added into either the UPPER, or into the LOWER. If the operation is "Add" (or "Reset Add"), and the D-REGISTER is plus, the contents of the D-REGISTER will be given a plus sign and the true value will be added into either the UPPER, or into the LOWER. If the operation is "Add" (or "Reset Add"), and the D-REGISTER is minus, the contents of the D-REGISTER will be given a minus sign and the complement value will be added into either the UPPER, or into the LOWER.

If the operation is a "Subtact Magnitude" (or "Reset Subtract Magnitude") operation, the contents of the D-REGISTER will be given a minus sign and the complement value will be added into either the UPPER, or into the LOWER. If the operation is "Subtract" (or "Reset Subtract"), and the D-REGISTER is plus, the contents of the D-REGISTER will be given a minus sign and the complement value will be added into either the UPPER, or into the LOWER. If the operation is "Subtract" (or "Reset Subtract") and the D-REGISTER is minus the contents of the D-REGISTER will be given a plus sign and the true value will be added into either the UPPER, or into the LOWER.

At this point, it will be helpful to tabulate in Table II the rules established for ACCUMULATOR addition operations (the OSTIC's ACCUMULATOR, it will be remembered, only adds).

Logical Diagram number 8 (Figure 9A and 9-B) illustrates the embodiment of the rules in computer logic. No timing chart accompanies the diagram; it is felt that the above listed rules, together with several detailed examples, will better enable the reader to understand the operation.

TABLE II

RULES FOR ACCUMULATOR COMPLEMENT AND RESET

Accumulator Sign

|      |     | Plus                          | Minus                       |

|------|-----|-------------------------------|-----------------------------|

|      |     | Reset entire Accumulator      | Reset entire Accumulator to |

|      | Yes | to plus zero before addition. | plus zero before addition.  |

| gate | No  | Do nothing to Accumulator     | Take 1's complement of      |

|      |     | or to sign bit.               | entire Accumulator. Sign    |

|      |     |                               | bit remains one.            |

TABLE III

RULES FOR ACCUMULATOR OPERATION CODE AND SIGN

Operation

|             | Add                    | Subtract                      |

|-------------|------------------------|-------------------------------|

| Magnitude   | Read out true value of | Read out complement value of  |

| gate is on. | D onto Data Channel.   | D onto Data Channel.          |

| Magnitude   | Read out true value of | Read out complement value of  |

| not on, D+  | D onto Data Channel.   | D onto Data Channel.          |

| Magnitude   | Read out complement    | Read out true value of D onto |

| not on, D - | value of D onto Data   | Data Channel.                 |

|             | Channel.               |                               |

TABLE IV

RULES FOR ACCUMULATOR ADD-IN

| ٠.                                    | Upper Gate On        | Lower Gate On                     |

|---------------------------------------|----------------------|-----------------------------------|

| True value                            | Add contents of Data | Add contents of Data Channel into |

| read out of                           | Channel into Upper.  | Lower. Add in a 0 sign bit.       |

| D-Register                            | Add in 0 sign bit.   |                                   |

| Complement                            | Add contents of Data | Add contents of Data Channel into |

| value read                            | Channel into Upper.  | Lower. Add l's into Upper. Add    |

| out of D                              | Add l's into Lower.  | in a l sign bit.                  |

| · · · · · · · · · · · · · · · · · · · | Add in a l sign bit. |                                   |

TABLE V

RULES FOR ACCUMULATOR END-AROUND CARRY AND OVERFLOW

|         | True figure add- | Complement add-  | True figure add-in is |

|---------|------------------|------------------|-----------------------|

| e.      | in is on. Accum- | in is on. Accum- | on, and Accumulator   |

|         | ulator is plus   | ulator is minus  | is -, or complement   |

|         | before addition. | before addition. | add-in is on, and     |

|         |                  |                  | Accumulator is +.     |

| End-    | Set Overflow     | Turn on Data     | Impulse Data Cycle    |

| around  | latch. Impulse   | Third Cycle.     | End.                  |

| carry.  | Data Cycle End.  | 1                |                       |

| No end- | Impulse Data     | Turn on Data     | Turn on Data          |

| around  | Cycle            | Third Cycle. Set | Third Cycle.          |

| carry   | End.             | Overflow latch.  |                       |

Figure 9-A. Logical Diagram number 8-Addition, Subtraction, and Complement.

Figure 9-B. Logical Diagram number 8-Addition, Subtraction, and Complement.

The first example considered will be an operation, where both values are plus, and no overflow results. The presence of an OPERAND gate and DATA FIRST CYCLE causes the computer to find the desired operand, as described in Chapter 5. The RESET gate is not on, and the ACCUMULATOR sign is plus, so neither reset nor complement takes place. When the operand is found, it is placed in the D-REGISTER and TURN ON DATA SECOND CYCLE occurs. The DATA SECOND CYCLE pulse tests the signs of the registers, and, since both the D-REGISTER and ACCUMULATOR are plus, gates the D-REGISTER to read out its true figure onto the DATA CHANNEL. At 1-3 time the ADD-IN pulse adds the contents of the DATA CHANNEL and a "0" (plus) sign into the LOWER ACCUMULATOR and the SIGN POSITION, respectively (second sheet). At 0 time of the same word time, a SIGN TEST pulse had set up the end-around carry test circuits, and since a TRUE FIGURE READ OUT gate and an ACCUMULATOR PLUS gate were on, turned on the SIGNS POSITIVE latch. No end-around carry occurs, so the COMPLE-MENT TEST pulse at 4 time impulses DATA CYCLE END.

The second example will be a "Reset Subtract Magnitude Upper" operation, using a positive operand. In this case, as before, the operand is acquired and placed in the D-REGISTER on DATA FIRST CYCLE. Meanwhile, on the first word time of DATA FIRST CYCLE, the ACCUMULATOR is reset to plus zero. When the operand is found and DATA SECOND CYCLE is turned on, the SUBTRACT, D-REGISTER PLUS, and MAGNITUDE gates are all on, so the D-REGISTER complement readout is gated onto the DATA CHANNEL. Since the COMPLEMENT READ-OUT and UPPER gates are on, a word of 18 1's is added into the LOWER by the use of inhibit gates. The actual add-in

to both ACCUMULATORS is accomplished by the ADD-IN pulse. Since COMPLEMENT ADD-IN is on, a "l" is added into the sign position at l time by the SIGN ADD pulse (the ADD-IN pulse is not used, because of possible conflicts with an end-around carry). Also, the SIGN TEST pulse at 0 time turns on the "SIGNS DIFFERENT" latch. An end-around carry will not occur when any number is added to zero; therefore, the COMPLEMENT TEST pulse finds the END-AROUND CARRY latch off at 4 time and, since TURN-ON DATA THIRD CYCLE has been previously impulsed by the SIGN ADD pulse, a DATA THIRD CYCLE pulse complements the ACCUMULATOR and impulses DATA CYCLE END.

The last example used will be an "Add Lower" operation, where both the ACCUMULATOR and the operand are minus beforehand. It is assumed that an overflow will occur.

The DATA FIRST CYCLE pulse finds the RESET GATE off, the ADD gate on, the ACCUMULATOR MINUS gate on, and therefore complements the contents of the accumulator. At 4 time the DATA FIRST CYCLE-OPERAND gate and ACCUMULATOR MINUS gate allow the COMPLEMENT TEST pulse to turn on the COMPLEMENT latch. This latch will remain on until 4 time of the next word time, when it is turned on again by the COMPLEMENT TEST. The purpose of the COMPLEMENT latch is to prevent continuous re-complementing of the ACCUMULATOR.

The DATA SECOND CYCLE pulse finds the ADD GATE and the D-REGISTER MIN US gates on, and therefore provides a COMPLEMENT READ-OUT gate to the D-REGISTER. The COMPLEMENT READ-OUT and the LOWER gate cause 1's to be added into the UPPER, while the contents of the DATA CHANNEL is being added to the LOWER by the ADD-IN pulse. A "1" bit is added into the SIGN POSITION, and the SIGN TEST

pulse turns on the "SIGNS NEGATIVE" latch. It was assumed that an overflow occurred; for both signs negative, an over-flow occurs when an end-around carry does not occur. At 4 time, the COMPLEMENT TEST pulse finds the SIGNS NEGATIVE latch on and the END AROUND CARRY latch off, and therefore turns on the OVERFLOW latch. The complement cycle is still taken, however.

Note that DATA THIRD CYCLE is always turned on, and that DATA CYCLE END is then impulsed if necessary. This takes advantage of the fact that DATA CYCLE END overrides any TURN ON pulse (see Chapter 4). Also note that provision is made for a separate COMPLEMENT operation; see Chapter 7 for further discussion.