# ADAPTIVE AND HYBRID SCHEMES FOR EFFICIENT PARALLEL SQUARING AND CUBING UNITS

By

Son Viet Bui

Bachelor of Science in Electrical Engineering Hanoi University of Science and Technology Hanoi, Vietnam 2000

Master of Science in Electrical Engineering Hanoi University of Science and Technology Hanoi, Vietnam 2002

> Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of DOCTOR OF PHILOSOPHY December, 2014

# COPYRIGHT © By Son Viet Bui

December, 2014

# ADAPTIVE AND HYBRID SCHEMES FOR EFFICIENT PARALLEL SQUARING AND CUBING UNITS

Dissertation Approved:

Dr. James E. Stine Jr.

Dissertation Advisor

Dr. Keith A. Teague

Dr. Qi Cheng

Dr. Jaeun Ku

### ACKNOWLEDGMENTS

Foremost, I would like to express my sincere gratitude to my advisor Dr. James E. Stine for his fundamental role in my Ph.D study and research. His patience, motivation, and immense knowledge helped me in all the time of research and writing this thesis.

My sincere thanks also goes to all committee members Dr. Keith A. Teague, Dr. Qi Cheng, and Dr. Jaeun Ku. Thank you all for everything you have done to help through

I am deeply thankful to my wife and my children for their love, support, and sacrifices. Without them, this thesis would never have been written.

Last but not the least, I would like to thank my parents for giving birth to me and supporting me spiritually throughout my life.

Acknowledgements reflect the views of the author and are not endorsed by committee members or Oklahoma State University.

Name: SON VIET BUI

Date of Degree: December, 2014

# Title of Study: ADAPTIVE AND HYBRID SCHEMES FOR EFFICIENT PARALLEL SQUARING AND CUBING UNITS

Major Field: Electrical and Computer Engineering

Squaring  $(X^2)$  and cubing  $(X^3)$  units are special operations of multiplication used in many application, such as image compression, equalization, decoding and demodulation, 3D graphics, scientific computing, artificial neural networks, logarithmic number system, and multimedia application. They can also be an efficient way to compute other basic functions. Therefore, improving their performances is a goal for many researchers. This dissertation will discuss modification to algorithms to compute parallel squaring and cubing units in both signed and unsigned representation. After that, truncated technique is applied to improve their performance. Each unit is modeled and estimated to obtain its area, delay by using linear evaluation model. A C program was written to generate Hardware Description Language files for each unit. These units are simulated and verified in simulation. Moreover, area, delay, and power consumption are calculated for each unit and compared with those ones in previous approaches for both Virtex 5 Xilinx FPGA and IBM 65nm ASIC technologies.

# TABLE OF CONTENTS

| Chapter  |      |                                                                                      | Page |  |  |

|----------|------|--------------------------------------------------------------------------------------|------|--|--|

| 1        | Intr | ntroduction                                                                          |      |  |  |

|          | 1.1  | Motivation                                                                           | 2    |  |  |

|          | 1.2  | Research Contributions                                                               | 4    |  |  |

|          | 1.3  | Dissertation Organized                                                               | 5    |  |  |

| <b>2</b> | Mu   | ltiplication                                                                         | 6    |  |  |

|          | 2.1  | Carry Save Concept                                                                   | 9    |  |  |

|          | 2.2  | Carry-Save Array Multipliers (CSAM)                                                  | 10   |  |  |

|          | 2.3  | Tree Multipliers                                                                     | 13   |  |  |

|          |      | 2.3.1 Wallace Tree Multipliers                                                       | 14   |  |  |

|          |      | 2.3.2 Dadda Tree Multipliers                                                         | 17   |  |  |

|          |      | 2.3.3 Reduced Area (RA) Multipliers                                                  | 18   |  |  |

|          | 2.4  | Baugh and Wooley Multiplication                                                      | 20   |  |  |

|          | 2.5  | Modified Booth Multipliers with Radix 4                                              | 24   |  |  |

| 3        | Tru  | ncated Multipliers                                                                   | 28   |  |  |

|          | 3.1  | Truncated Multiplication with Correction Constant (CCT) $\ldots \ldots$              | 31   |  |  |

|          | 3.2  | Truncated Multiplication with Variable Correction (VCT) $\ldots \ldots$              | 37   |  |  |

|          | 3.3  | Truncated Multiplication with Hybrid $\operatorname{Correction}(\operatorname{HCT})$ | 41   |  |  |

| 4        | Squ  | aring Unit Architectures                                                             | 45   |  |  |

|          | 4.1  | Unsigned Squaring Unit Architectures                                                 | 45   |  |  |

|          |      | 4.1.1 Folded Squaring Units                                                          | 45   |  |  |

|          |                 | 4.1.2  | Merged Squaring Units                                          | 46        |  |  |

|----------|-----------------|--------|----------------------------------------------------------------|-----------|--|--|

|          |                 | 4.1.3  | Divide and Conquer Squaring Unit                               | 49        |  |  |

|          |                 | 4.1.4  | Proposed Squaring Unit                                         | 50        |  |  |

|          | 4.2             | Signed | l Squaring Unit Architectures                                  | 55        |  |  |

|          |                 | 4.2.1  | Booth Folding Squaring Unit                                    | 55        |  |  |

|          |                 | 4.2.2  | Booth 2 Left-to-Right Dual Recoding Squaring Unit              | 59        |  |  |

| <b>5</b> | Cubing Units 62 |        |                                                                |           |  |  |

|          | 5.1             | Liddic | oat and Flynn Cubing Units                                     | 65        |  |  |

|          | 5.2             | Stine  | and Blank Cubing Units                                         | 67        |  |  |

|          | 5.3             | Divide | e and Conquer Cubing Units                                     | 68        |  |  |

|          | 5.4             | Propo  | sed Cubing Unit                                                | 71        |  |  |

| 6        | Tru             | ncated | l Squaring and Cubing Units                                    | <b>74</b> |  |  |

|          | 6.1             | Trunc  | ated Squaring Units                                            | 74        |  |  |

|          |                 | 6.1.1  | Truncated Squaring Units using Booth 2 Folding Technique $\ .$ | 74        |  |  |

|          |                 | 6.1.2  | Truncated Squaring Unit using Booth 2 Left-to-Right Encoding   |           |  |  |

|          |                 |        | Technique                                                      | 76        |  |  |

|          |                 | 6.1.3  | Truncated Squaring Unit using Divide and Conquer Technique.    | 78        |  |  |

|          |                 | 6.1.4  | Proposed Truncated Squaring Unit                               | 79        |  |  |

|          | 6.2             | Trunc  | ated Cubing Units                                              | 81        |  |  |

|          |                 | 6.2.1  | Truncated Cubing Unit using Divide and Conquer Technique.      | 81        |  |  |

|          |                 | 6.2.2  | Proposed Truncated Cubing Unit                                 | 83        |  |  |

|          | 6.3             | Errors | Comparison                                                     | 88        |  |  |

| 7        | Are             | a and  | Delay Analyses                                                 | 93        |  |  |

|          | 7.1             | Area l | Estimation of Squaring Units                                   | 94        |  |  |

|          |                 | 7.1.1  | Folded Squaring Unit.                                          | 94        |  |  |

|          |                 | 7.1.2  | Merged Squaring Unit.                                          | 95        |  |  |

|   |      | 7.1.3  | Divide & Conquer Squaring Unit    | 96  |

|---|------|--------|-----------------------------------|-----|

|   |      | 7.1.4  | Proposed Squaring Unit.           | 97  |

|   |      | 7.1.5  | Booth 2 Folding Squaring Unit     | 98  |

|   |      | 7.1.6  | Booth 2 Left-to-Right Recoding    | 99  |

|   | 7.2  | Delay  | Estimation of Squaring Units      | 100 |

|   | 7.3  | Area l | Estimation of Cubing Units        | 103 |

|   |      | 7.3.1  | Liddicoat and Flynn Method        | 103 |

|   |      | 7.3.2  | Stine and Blank method            | 105 |

|   |      | 7.3.3  | Divide and Conquer method.        | 106 |

|   |      | 7.3.4  | Proposed method                   | 110 |

|   | 7.4  | Delay  | Estimation of Cubing Units        | 112 |

| 8 | Har  | dware  | Implementation and Conclusions    | 113 |

|   | 8.1  | Hardw  | vare Implementation               | 113 |

|   |      | 8.1.1  | Implementation on FPGA Technology | 113 |

|   |      | 8.1.2  | Implementation on ASIC Technology | 115 |

|   | 8.2  | Summ   | nary and Future Work              | 116 |

| R | EFE] | RENC   | ES                                | 124 |

# LIST OF TABLES

| Table | Pa                                                                                         | age |

|-------|--------------------------------------------------------------------------------------------|-----|

| 2.1   | Partial Product Selection                                                                  | 25  |

| 4.1   | Truth Table of Stage 1                                                                     | 51  |

| 4.2   | Truth Table of A Special Adder in Stage 2                                                  | 52  |

| 4.3   | Truth Table of Stage 3                                                                     | 54  |

| 4.4   | Truth Table for Partial Product ${\cal P}_i$ in Booth 2 Folding Technique $~$ .            | 58  |

| 4.5   | Truth Table of $P_i$ in Left-to-Right Dual Recoding Method $\ldots \ldots$                 | 60  |

| 6.1   | Errors Comparison for Truncated Squaring Units in $[11]$                                   | 88  |

| 6.2   | Errors Comparison for Truncated Squaring Units in [74]                                     | 89  |

| 6.3   | Errors Comparison for Truncated Squaring Units in [71]                                     | 90  |

| 6.4   | Errors Comparison for Truncated Squaring Units in $[77]$                                   | 90  |

| 6.5   | Rounding to Nearest Even (RNE) Errors of Squaring Unit $\ldots$                            | 91  |

| 6.6   | Errors Comparison for Truncated Cubing Unit in $[75]$                                      | 91  |

| 6.7   | Errors Comparison for Truncated Cubing Unit in $[76]$                                      | 91  |

| 6.8   | Error Comparison of Rounding to Nearest $\operatorname{Even}(\operatorname{RNE})$ $\ldots$ | 92  |

| 8.1   | Area, Delay, and Power Comparison of Squaring Units on Virtex 5 FPGA                       | 118 |

| 8.2   | Performances Truncated Squaring Units on FPGA Virtex 5                                     | 119 |

| 8.3   | Gates, Delay, and Power Comparison of Cubing Units on FPGA Virtex 52                       | 120 |

| 8.4   | Comparison for Truncated Cubing Units in Virtex 5 FPGA                                     | 120 |

| 8.5   | Area, Delay, and Power Comparison of Squaring Units on $ASIC\ IBM$                         |     |

|       | 65nm                                                                                       | 121 |

| 8.6 | Performances Truncated Squaring Units on ASIC IBM $65nm$       | 122 |

|-----|----------------------------------------------------------------|-----|

| 8.7 | Gates, Delay, and Power Comparison of Cubing Units in ASIC IBM |     |

|     | 65nm                                                           | 123 |

| 8.8 | Comparison of Truncated Cubing Units on ASIC                   | 123 |

# LIST OF FIGURES

| Figure    |                                                                   | Page |

|-----------|-------------------------------------------------------------------|------|

| 2.1       | Partial Products Matrix of Multiplication.                        | 7    |

| 2.2       | 8x8-bit Dot Matrix Diagram of Multiplication.                     | 8    |

| 2.3       | A Carry-Save Adder or (3, 2) Counter.                             | 9    |

| 2.4       | An Example of Carry-Save Concept Adder                            | 11   |

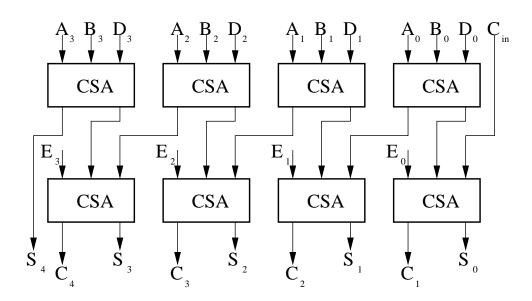

| 2.5       | A Four Operands 4-bit Multi-Operand Adder                         | 11   |

| 2.6       | $8 \times 8$ -bit Carry-Save Array Multiplier                     | 12   |

| 2.7       | Modified Half Adder and Full Adder.                               | 13   |

| 2.8       | (2, 2) and $(3, 2)$ Counters in Tree Multiplier                   | 14   |

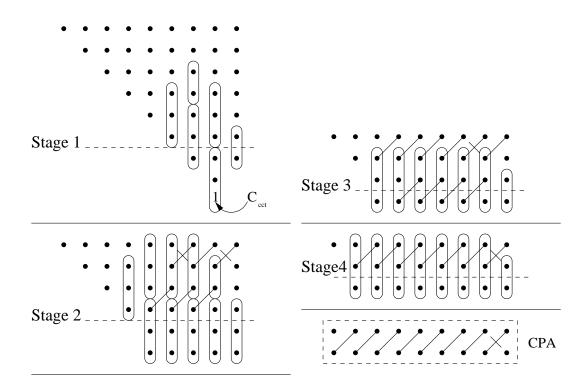

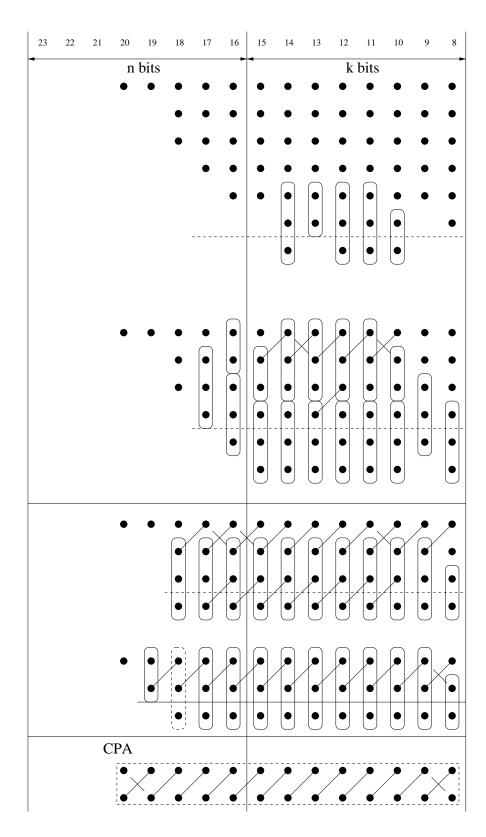

| 2.9       | Wallace Tree Multiplier.                                          | 16   |

| 2.10      | ) Dadda Tree Multiplier                                           | 19   |

| 2.11      | Reduce Area Multiplier                                            | 21   |

| 2.12      | 2 PPM of Baugh and Wooley Multiplier                              | 22   |

| 2.13      | B Implementation of Baugh and Wooley Multiplier                   | 23   |

| $2.1_{-}$ | 4 PPM of Booth 2 Multiplier                                       | 26   |

| 2.15      | 5 Sign Extension Bit of MBP                                       | 26   |

| 2.16      | 6 Partial Product Generation of Booth 2                           | 27   |

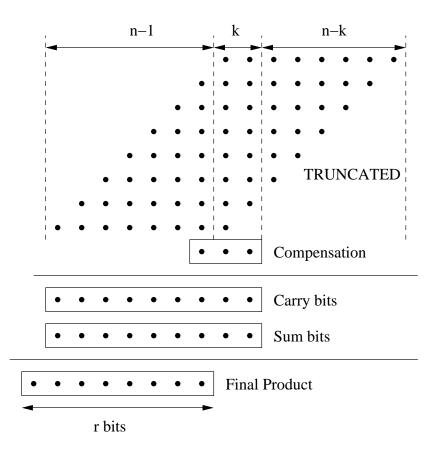

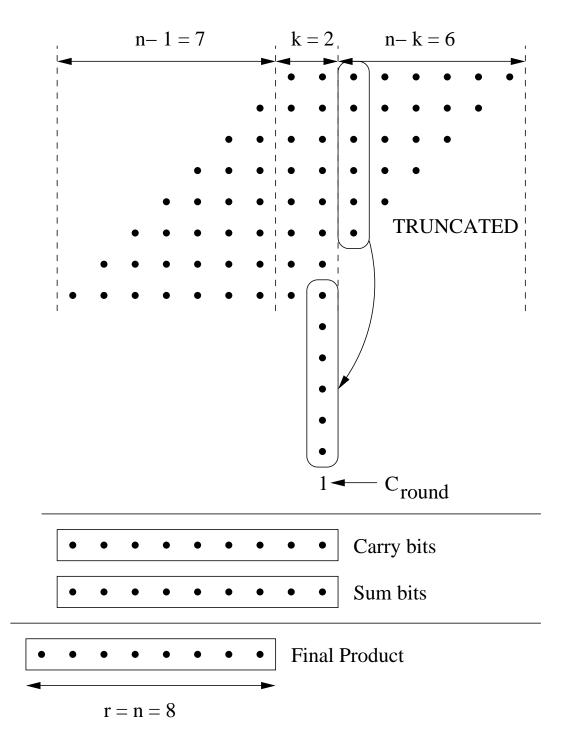

| 3.1       | Product Matrix of Truncated Multiplier                            | 31   |

| 3.2       | PPM of $8 \times 8$ -bit Truncated Multiplier in CCT with $k = 2$ | 34   |

| 3.3       | $8 \times 8$ -bit CCT with $k = 2$ in CSAM Implementation.        | 35   |

| 3.4       | Special Half Adder.                                               | 36   |

| 3.5       | $8 \times 8$ -bit CCT with $k = 2$ in Dadda Tree Reduction.       | 36   |

| - 0       |                                                                   |      |

| 3.6  | PPM of $8 \times 8$ -bit VCT with $k = 2$ .                                  | 38 |

|------|------------------------------------------------------------------------------|----|

| 3.7  | $8 \times 8$ -bit VCT with $k = 2$ in CSAM Implementation.                   | 39 |

| 3.8  | $8 \times 8$ -bit VCT with $k = 2$ in Dadda Tree Reduction.                  | 40 |

| 3.9  | $8\times 8\text{-bit}$ HCT with $k=2,p=0.5$ in CSAM Implementation           | 43 |

| 3.10 | $8\times 8\text{-bit}$ HCT with $k=2,p=0.5$ in Dadda Tree Implementation     | 44 |

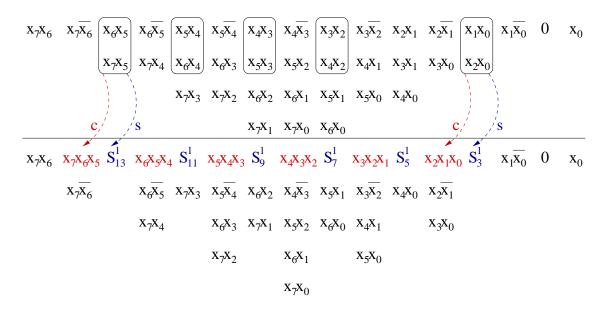

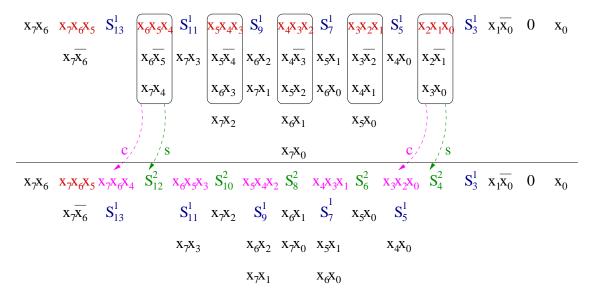

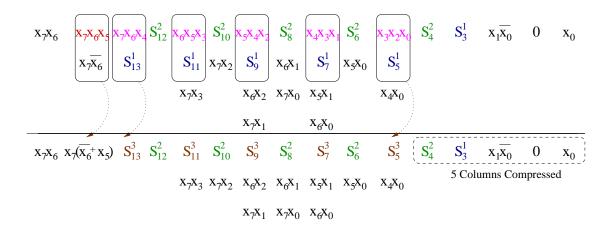

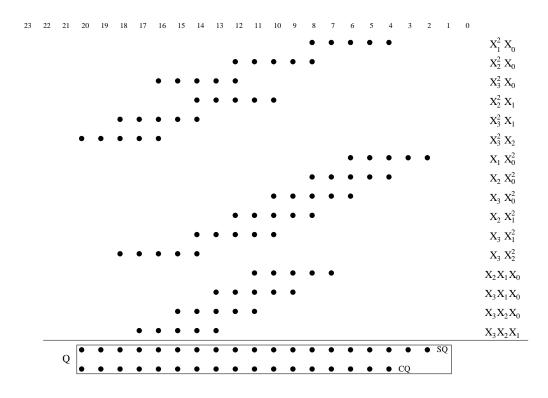

| 4.1  | PPM of Folded Squaring Unit with $n = 7 \dots \dots \dots \dots \dots$       | 47 |

| 4.2  | PPM of Folded Squaring Unit with $n = 8 \dots \dots \dots \dots \dots \dots$ | 48 |

| 4.3  | PPM of Merged Squaring Unit with $n = 7$                                     | 49 |

| 4.4  | PPM of Merged Squaring Unit with $n = 8$                                     | 49 |

| 4.5  | PPM of a Squaring Unit in Divide and Conquer Method $\ldots$                 | 50 |

| 4.6  | PPM of 4-bit Squaring Unit in Divide and Conquer Method $\ .\ .\ .$ .        | 51 |

| 4.7  | Optimization of a Squaring Unit at Stage 1                                   | 53 |

| 4.8  | Optimization of a Squaring Unit at Stage 2                                   | 53 |

| 4.9  | Optimization of a Squaring Unit at Stage 3                                   | 55 |

| 4.10 | PPM of Folding Squaring Unit in Booth 2                                      | 56 |

| 4.11 | PPM of a Squaring Unit in Booth 2 Folding Technique $\ldots \ldots \ldots$   | 59 |

| 4.12 | PPM of Squaring Unit in Booth 2 Left-to-Right Dual Recoding $\ .$ .          | 61 |

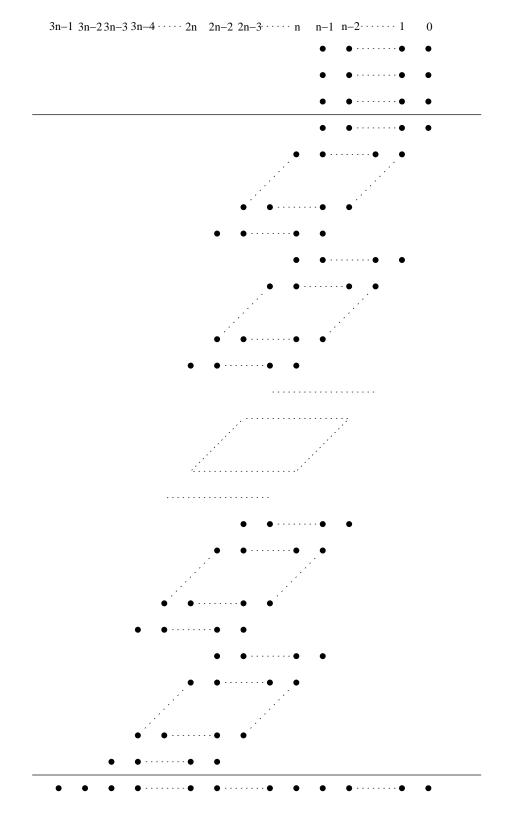

| 5.1  | Partial Product Matrix of Cubing Unit                                        | 64 |

| 5.2  | Liddicoat and Flynn Method for Step 1                                        | 66 |

| 5.3  | Liddicoat and Flynn Method for Step 2                                        | 66 |

| 5.4  | Stine and Blank Method Stage 1                                               | 68 |

| 5.5  | Stine and Blank Method Stage 2                                               | 69 |

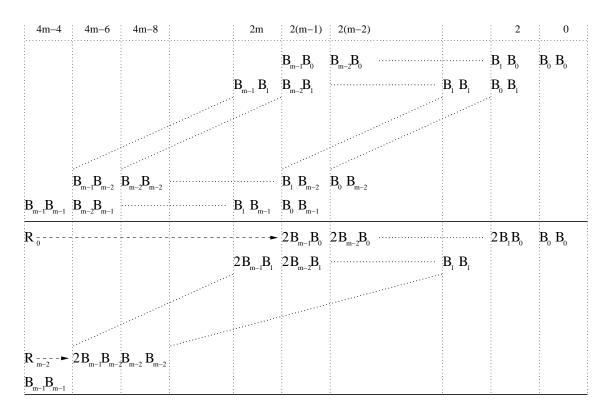

| 5.6  | PPM of a Cubing Unit in Divide and Conquer Technique                         | 70 |

| 5.7  | PPM of 4-bit Cubing Unit in Divide and Conquer Technique                     | 70 |

| 5.8  | Partial Product Matrix for Proposed Cubing Unit at Step 1, 2 $\ldots$        | 72 |

| 5.9  | Partial Product Matrix for Proposed Cubing Unit at Step 3 $\ldots$ .         | 72 |

|      |                                                                              |    |

| 6.1  | PPM of Truncated Squaring Unit in [56]                                                                                                            | 74  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|

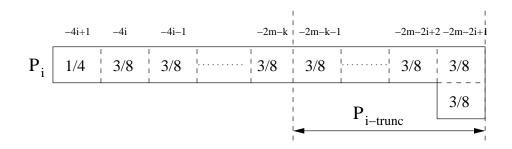

| 6.2  | Truncation of $P_i$ in [56]                                                                                                                       | 76  |

| 6.3  | Partial Product Matrix of Truncated Squaring Unit In [74] $\ldots$ .                                                                              | 77  |

| 6.4  | Truncation of $P_i$ in Left-to-Right Encoding                                                                                                     | 78  |

| 6.5  | PPM of Truncated Squaring Unit in [71]                                                                                                            | 79  |

| 6.6  | PPM of Proposed Truncated Squaring Unit                                                                                                           | 80  |

| 6.7  | PPM of Truncated Cubing Unit in [75]                                                                                                              | 81  |

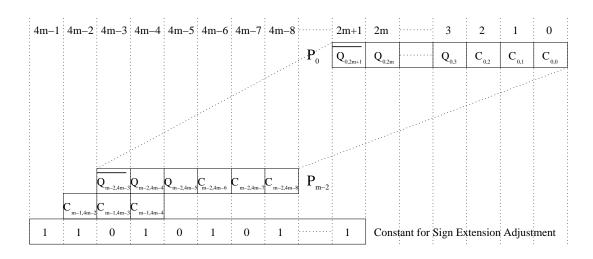

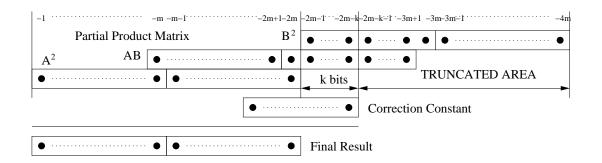

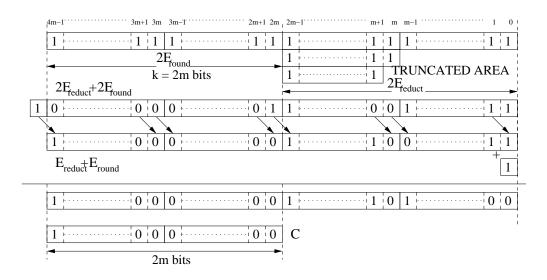

| 6.8  | Correction Constant for Truncated Cubing Unit in [75] when $k = 2m$ .                                                                             | 82  |

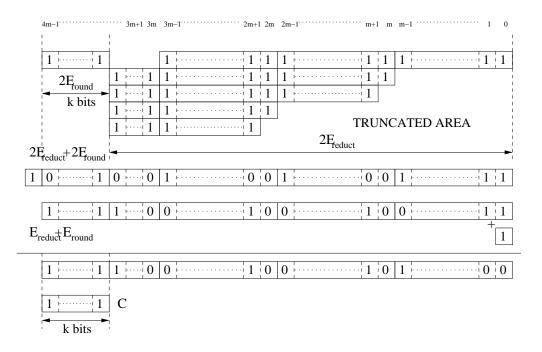

| 6.9  | Correction Constant for Truncated Cubing Unit in [75] when $0 < k < m$ .                                                                          | 83  |

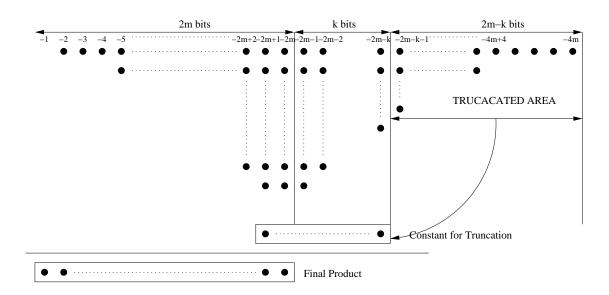

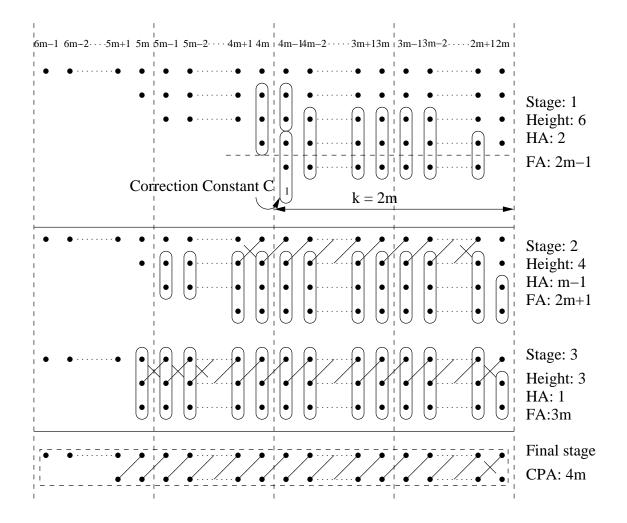

| 6.10 | Dadda Tree of Truncated Cubing Unit in [75] when $k = 2m$                                                                                         | 84  |

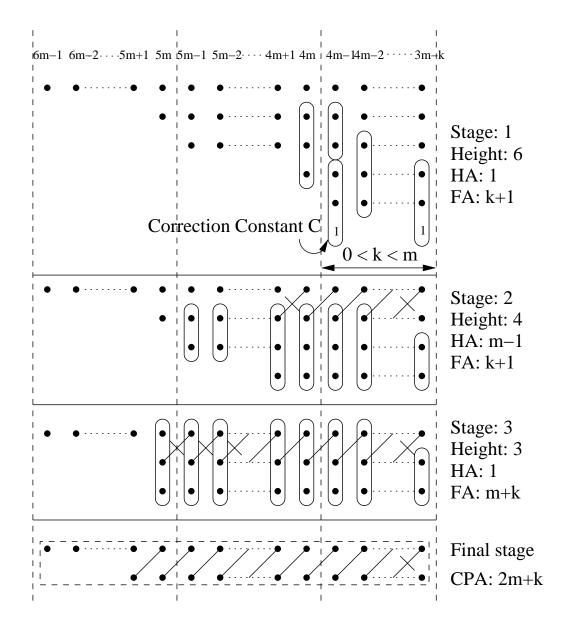

| 6.11 | Dadda Tree of Truncated Cubing Unit in [75] when $0 < k < m$                                                                                      | 85  |

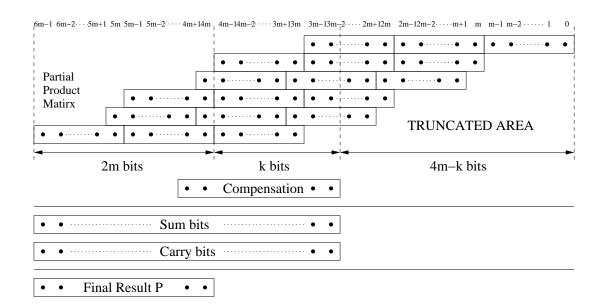

| 6.12 | PPM for Truncated Proposed Cubing Unit at Step 1, 2 $\ldots$ .                                                                                    | 86  |

| 6.13 | Partial Product Matrix for Proposed Cubing Unit at Step 3 $\ldots$ .                                                                              | 87  |

| 7.1  | Half Adder Implementation                                                                                                                         | 94  |

| 7.2  | Dadda Tree Reduction of a 4 Cubing Unit in Vedic Mathematics 1                                                                                    | 108 |

| 7.3  | Implementation of $X_i X_j X_k \dots \dots$ | 111 |

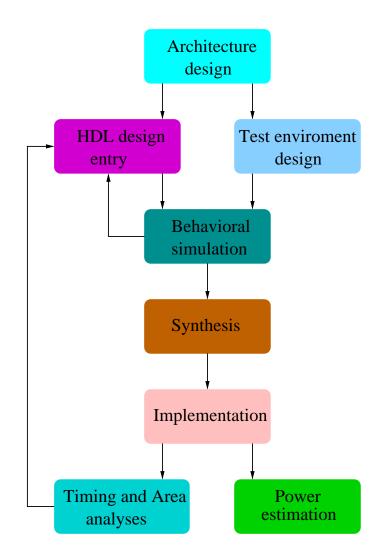

| 8.1  | FPGA Flow Diagram                                                                                                                                 | 114 |

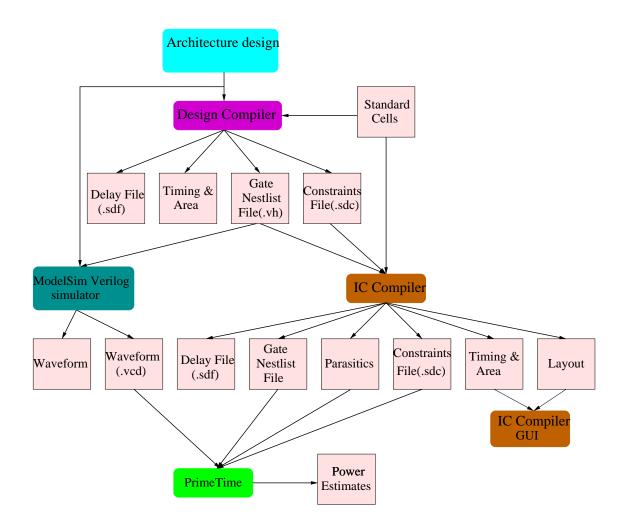

| 8.2  | ASIC Flow Diagram                                                                                                                                 | 115 |

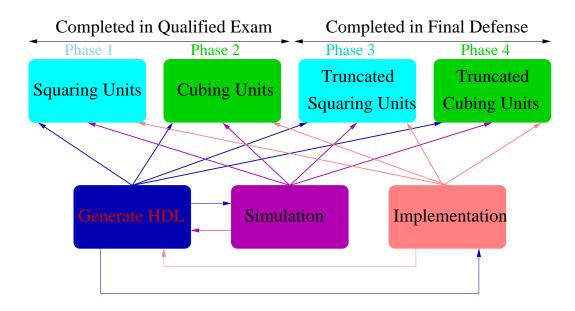

| 8.3  | Research Flow Diagram                                                                                                                             | 117 |

$\mathbf{C}\mathbf{C}$

# CHAPTER 1

#### Introduction

#### 1.1 Motivation

In computer arithmetic, multiplication is not commonly utilized as much as addition, but it plays an important role for microprocessors, digital signal processors, and graphics engines [1]. Computers spend a large amount of time and power when performing multiplication, whether it is utilized in software or hardware. Early computers used only parallel adders and a few storage registers, so multiplication was often performed via a sequence of add and shift instructions [2]. Subsequently, future designs utilized high-speed multipliers by employing faster adders as well as better and more optimized memory.

With a multiplication operation, difficulty occurred when the input operands are two's complement. Shaw [2] developed an algorithm for two's complement multiplication, but these algorithms usually require more hardware, therefore, the complexity of distorted systems increased. To solve this problem, some designers utilize different numeric recoding such as Booth multiplier [3]. This algorithm utilizes a number shift and serial multiplication operations along with some recoding to handle two's complement number.

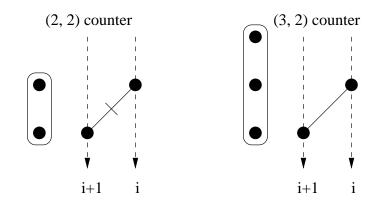

Another multiple algorithm proposed in [4] is a fully parallel multiplier called a *Wallace* tree. This algorithm uses a group of (3, 2) and (2, 2) counters to reduce the number of partial product bits to 2 operands (carry and sum), then they are added by using a faster adder. A new scheme presented in [5], called *Dadda* tree, utilized the lower bound of combining different types of counters to optimize the number of (3, 2)

and (2, 2) counters. Later, in [6], this tree was optimized to find optimum building block for implementing of a multiplier with a larger input size.

Over the several decades, Very Large Scale Integration (VLSI) technology and integrated circuit processing have dramatically improved. According to Moore's Law, the number of transistors in a die doubles approximately every 18 months [1]. As the number of transistors and speed in a chip increase, more specific units and elementary functions are added to computer's arithmetic unit, allowing it to run faster. Therefore, computer's performance is improved and more complex scientific problems can be solved.

Squaring is a special operation of multiplication. It plays an important role in a computer's arithmetic unit and many applications such as, image compression [7, 8], equalization [9], multimedia applications [10–12], and decoding and demodulation [13, 14]. It can also be an efficient way to compute other basic functions [15–17]. Therefore, improving the performances of squarer is a goal for many researchers.

Another type of multiplication is powering function  $(X^Y)$ . It is also needed for computer 3D graphics, digital signal processing (DSP), scientific computing, artificial neural networks, logarithmic number systems, and multimedia applications [12], and other important functions [15]. Cubing  $(X^3)$  is a special instance of powering and plays an important role in many algorithms, like signal processing, image processing, cryptography [18, 19], and elementary function approximation [20–23].

Recently, with the increment of density of gates in each die, parallelism through single instruction multiple data (SIMD) processing can optimize processing for more than one operation. By enhancing application specific and embedded processors are ways to provide higher levels of parallelism [24]. These enhancements are combined with an extended instruction set that takes advantage of additional hardware by allowing more operations to be encoded in a single instruction. With this increased parallelism and the shrinking feature sizes, the next generation of application-specific processor can execute significantly more work. Consequently, new techniques for calculating the squaring and cubing units in parallel without the use of basic multipliers or tables becomes an attractive alternative.

For these reasons, squaring and cubing operations still are objects of many researchers. They should be calculated with a minimum amount of latency as to not slow down these calculations, especially for real-time systems [25].

#### **1.2** Research Contributions

This dissertation will discusses modification to algorithms to compute parallel squaring and cubing units in both unsigned and signed representation. After that truncated techniques are applied to get an optimal performance.

Each unit is modeled and estimate its area, delay by linear evaluation. Hardware design using Verilog code is used in this dissertation. A C program is used to generate Verilog code for each unit. These units are simulated and verified in Hardware Description Language (HDL) simulators. Area, delay, and power consumption are calculated for each of the designs and compared with previous approaches in both Virtex 5 Xilinx FPGAs and IBM 65nm ASIC standard-cell libraries. The following are contributions of this work

- 1. Propose a new model for unsigned squaring and cubing unit.

- 2. Investigate signed squaring, cubing units.

- 3. Estimate the Area, Delay, and Power of these units by using linear model.

- 4. Propose a model for truncated squaring, cubing units.

## 1.3 Dissertation Organized

The remaining portion of this thesis is structured as follows : Chapter 2 will review the background information on the parallel multiplication. Chapter 3 presents various ideas of truncated multiplication . Chapter 4 illustrates squaring units and proposed a new model to improve their performance. Chapter 5 gives information on parallel cubing units and propose a new way to implement it. Chapter 6 analyses truncated squaring and cubing units with previous technique presented in Chapter 3. Chapter 7 used *Linear-Delay* model for analyzing area and delay of each units. Chapter 8 is an implementation of squaring and cubing units in both techniques FPGA and ASIC and conclusion.

# CHAPTER 2

### Multiplication

Multiplication is frequently required in digital signal processing applications (digital filtering, FFT, convolution,...). Parallel multipliers [4,5] provide fast multiplication for these applications, but require large amount of area. This parameter increases proportionally with the square of the word size. Therefore a large number of transistors are needed, hence, multipliers consume a large amount of power [26].

A multiplier is one of vital parts in application-specific processors, such as digital signal processing (DSP) systems. This is because many signal processing algorithms heavily utilize multiplication. To improve performances of multipliers, high speed parallel architectures are often used. These architectures contribute significantly to the overall power dissipation of these systems [27]. Consequently, reducing power consumption of parallel multipliers is important in design of digital signal processing systems. In the past, several techniques have been proposed to reduce power dissipation of parallel multipliers. Some of them tried to reduce dynamic power dissipation by eliminating spurious transitions [28]. The others tried to develop multiplier architectures [29]. Although these techniques help reduce power dissipation, but further reductions are needed for future DSP systems [28].

Since current and future portable devices using DSP hardware have become popular. As more of these devices increase, so does the power consumption. Hence, long battery life is a higher priority feature for most users.

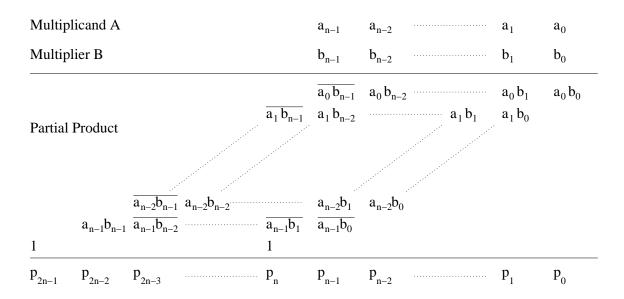

To illustrate multiplication algorithms, a partial product matrix is often used. A  $m \times n$  bits multiplication can be viewed as forming n partial products of m bits each

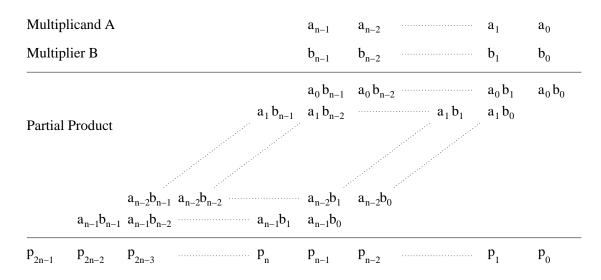

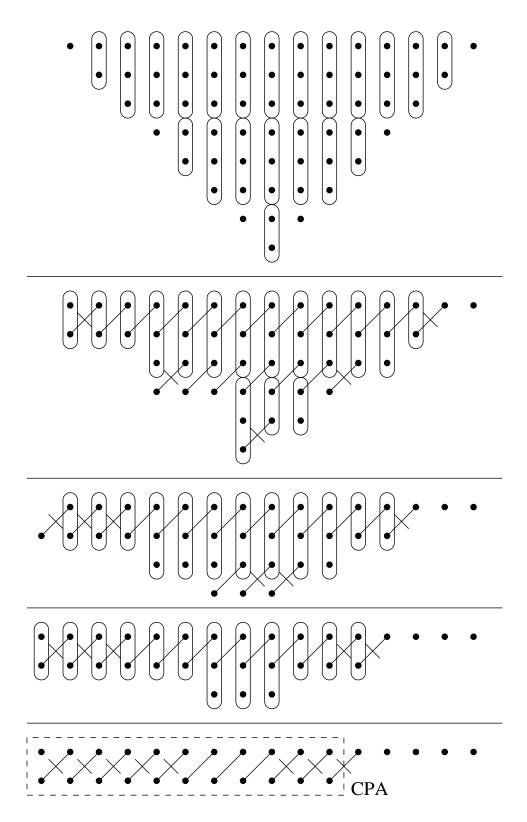

Figure 2.1: Partial Products Matrix of Multiplication.

and then summing the appropriately shifted partial products to produce (m + n)-bit result P. Theoretically, multiplication of two n bits unsigned fraction A and B will yield 2n bits products P, as shown below:

$$\begin{cases}

A = \sum_{i=0}^{n-1} a_i \cdot 2^{-n+i} \\

B = \sum_{i=0}^{n-1} b_i \cdot 2^{-n+i} \\

P = \sum_{i=0}^{2n-1} p_i \cdot 2^{-2n+i}

\end{cases}$$

(2.1)

Digital architectures for multiplication usually involve three separate steps:

- 1. Partial Product Generation (*PPG*) to utilize a collection of gates to generate the partial product bits.

- 2. Partial Product Reduction (*PPR*) to utilize adders to reduce the partial products to sum and carry vectors.

- 3. Final Carry Propagate Addition (*CPA*) to add the sum and carry arrays to produce the product.

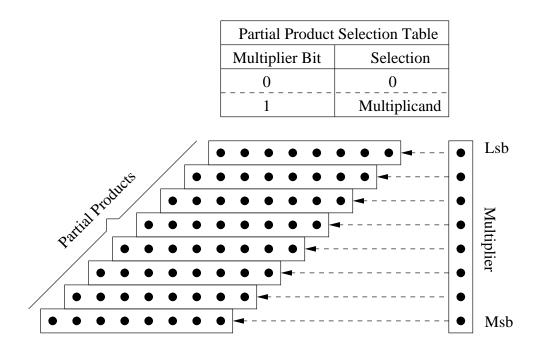

Figure 2.1 illustrates the generation and summing of partial products in  $n \times n$  bits multiplication. When A and B become larger, dot diagram is used to represent partial products more conveniently. For example, Figure 2.2 shows a dot diagram for an 8-bit

Figure 2.2: 8x8-bit Dot Matrix Diagram of Multiplication.

multiplier. Each dot is equal to each bit in partial product matrix. It can be either "0" or "1" depends on the value of multiplicand and multiplier.

There are several techniques that can be used to implement multiplication. In general, the choice is base upon factors such as latency, throughput, area, and design complexity. The latency factor is related to the height of the dot diagram. This relationship can vary from logarithmily to linearly [30]. The simplest way to implement a multiplier is used an (n + 1)-bit CPA to add the first two partial product arrays, then another CPA to add the third one to the running sum, and so forth. This technique will require (n - 1) CPAs, so it is slow even if a fast CPA is being used. More efficient parallel approaches use some sort of array or a tree of full adders to sum the partial product bits and using pipeline to reduce the cycle time and increase the throughput. In addition, this technique can save a large amount of area.

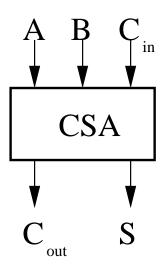

Figure 2.3: A Carry-Save Adder or (3, 2) Counter.

## 2.1 Carry Save Concept

After finishing first step PPG, all bits in this matrix will be added to get the final result by utilizing adders to reduce the execution time. Because the major delay of adders is come from the carrier chain, therefore, it is important to reduce the total time is involved in summing carries [31]. There are two principles to help save time arriving at a product:

- Carry-Save Addition (CSA): idea of utilizing addition without the carriers connected in series, but just to count.

- Carry-Propagate Addition (*CPA*): idea of the carries connected in series to produce a result in either conventional or redundant notation.

For these methods, each adder above acts the same as the full adder, however, the view in which each connection is made from adder to adder is where the main difference lies. Because both adders compute both carry and save information, sometimes VLSI designers refer to it as a Cary-Save Adder (CSA) [31]. The summation of the partial product bits is done by using a CSA, each adder attempts to count the number of inputs that are "1", so it also referred as a counter. These counters can be connected by several different topologies. These topologies are referred as regular and irregular ones. In the former, the counters are connected in a normal pattern that is replicated so that the design of partial product array can be connected as a hierarchical design. On the other hand, in the latter, the counter are connected in order to minimize the delay. The different of these topologies can be seen in array or tree multipliers.

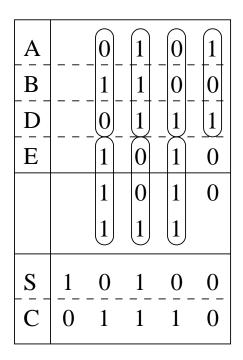

A (c, d) counter is a special adder, in which c is the number of columns to be added and d is the number of outputs. For example, a (3, 2) counter counts its inputs with the same weight and has 2 outputs. Fig 2.3 shows a typical (3, 2) counter. Therefore, a n-bit CSA has three n-bit input operands and two n-bit outputs, one for sum and the other for carry. Large operand sizes would require more CSAs to produce a result. However, a CPA would be required to produce the correct result [31]. For example, Figure 2.4 shows how to add four operands together A + B + D + E with the value 5 + 12 + 7 + 10. The implementation utilizing carry-save concept for this example is shown in Figure 2.5. Higher order counters can be created by putting together various sized counters. A higher counter (p,q) takes p input bits and produces q output bits. Because q is a number between 0 and  $2^q - 1$  so the value of p must be smaller than  $2^q$ .

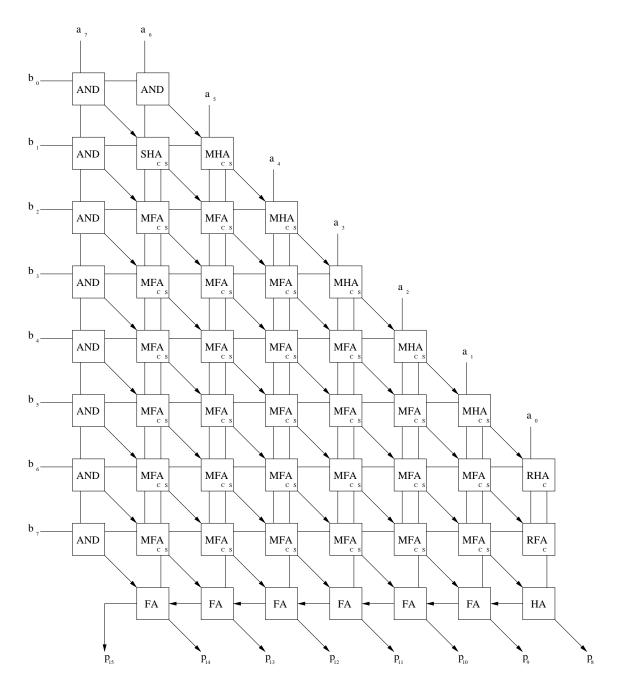

#### 2.2 Carry-Save Array Multipliers (CSAM)

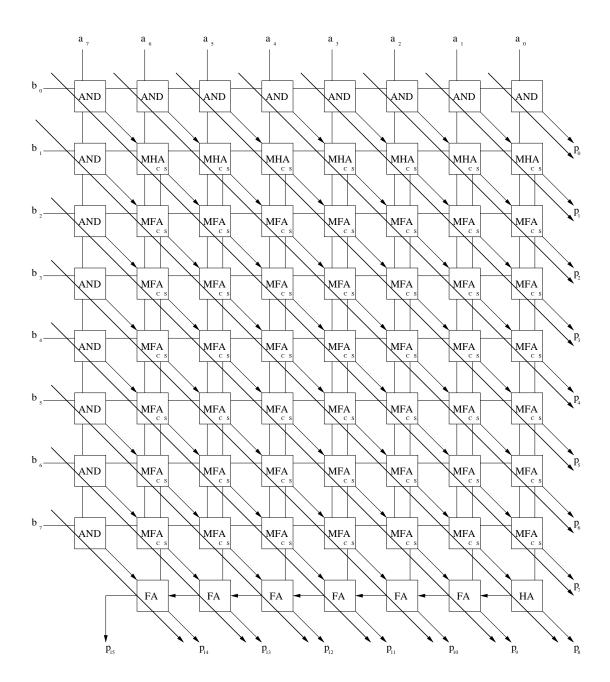

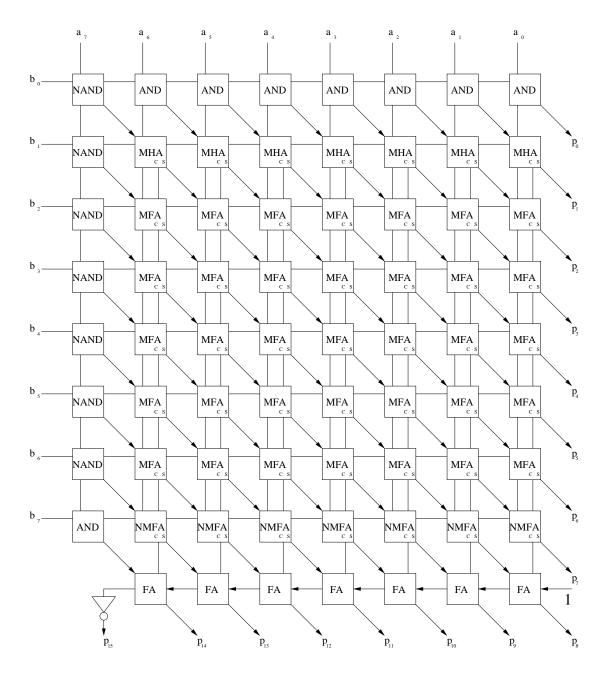

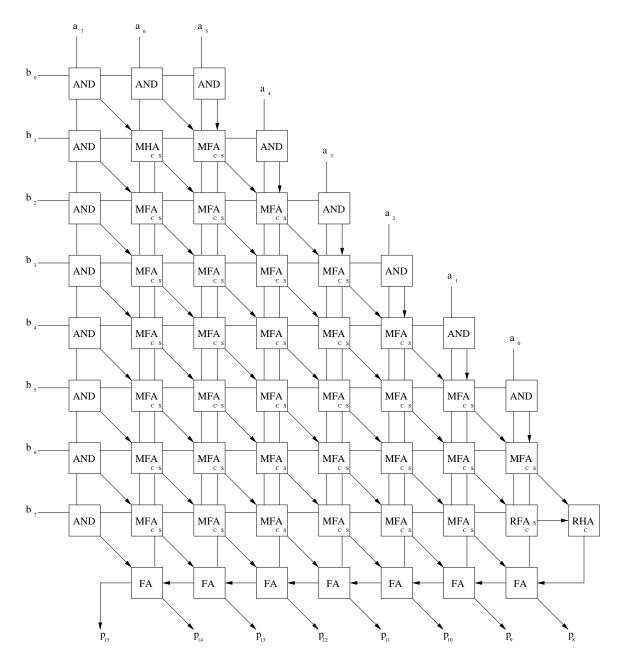

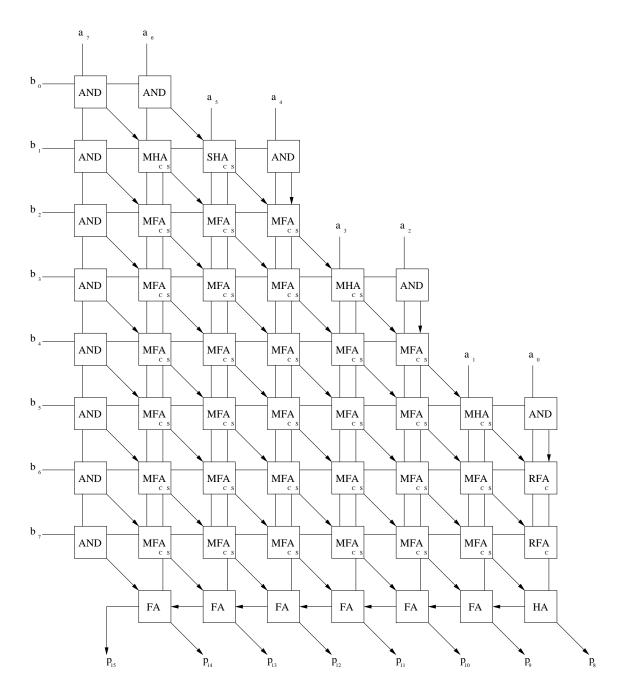

A Carry-Save Array Multipliers is the simplest multiplier in which each partial product bit is being added [32] similar to paper and pencil multiplication is performed. Its operation is based on paper and pencil style multiplication where each partial product bit is added in array. The topology of a CSAM is a regular one, so it is easy be built by a hierarchical design. Figure 2.6 shows an implementation of a  $8 \times 8$ -bit unsigned multiplier. Each diagonal in CSAM corresponds to a column in the multiplication matrix shown by the bold line in Figure 2.6. Because of implementing in

Figure 2.4: An Example of Carry-Save Concept Adder.

Figure 2.5: A Four Operands 4-bit Multi-Operand Adder.

Figure 2.6:  $8 \times 8$ -bit Carry-Save Array Multiplier.

a square shape, CSAMs allow metal tracks or interconnect to have less congestion, thus, reducing capacitance as well as it is easier to organize [31].

A CSAM generates partial product bits by utilizing AND gates and uses an array of CSA's to perform reduction. These AND gates form the partial product's and the CSA's will be used to sum these products together or reduce them. Because half the lower part of the product is computed by the reduction, therefore, only

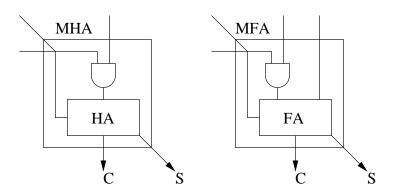

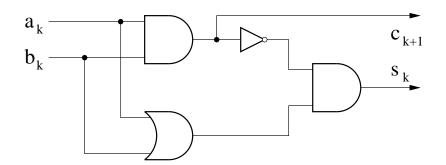

Figure 2.7: Modified Half Adder and Full Adder.

the upper half of the product need to be added in the final CPA [31]. To perform CSAM, each adder is modified so that it can perform partial product generation and addition. Two type of adders are used for CSAM and called the modified half adder (MHA), and the modified full adder (MFA). A MHA consists of an AND gate to generate the partial product bit and one half adder (HA) to add this partial product bit with another one from the previous row. A MFA consists of an AND gate for generating partial product bit, and a full adder FA. This FA is used to add this partial product bit with the sum and carry bits from previous row. Figure 2.7 shows the block diagram of the MHA and the MFA.

#### 2.3 Tree Multipliers

Tree topologies are a fast way for summing partial products. In a tree, counters are connected in different ways for each slice [30]. Therefore, to reduce the delay of array multipliers, tree reduction are often employed. A tree multiplier, which have O(log(n)) delay [31], uses an idea of reduction to reduce their partial product height down until it is equal 2, then a high speed CPA is applied to get the final result. Tree multipliers vary in a way that each CSA performs partial product reduction. The main objective is to reduce the its height by utilizing the carry-save concept. Each partial product bit is reorganized, so that it can achieve an efficient reduction

Figure 2.8: (2, 2) and (3, 2) Counters in Tree Multiplier.

in the column. This is possible for multiplication, because each bit in the matrix is commutative and associative with respect to addition.

The first trees were introduced in [4],called a Wallace tree, by utilizing a reduction using (3,2) and (2,2) counters in parallel. A Dadda tree [5] is an improvement of Wallace tree in which the number of reduction stages are minimized. Another tree presented in [33] improved multiplier's area compared with both Wallace and Dadda trees. In a tree multiplier, (3,2) and (2,2) counters are defined and used as in Figure 2.8.

#### 2.3.1 Wallace Tree Multipliers

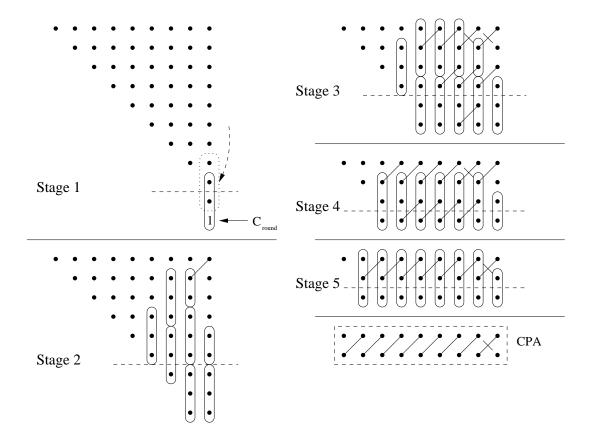

In 1964, a fast multiplier is defined using a column compression technique [4]. Partial product bits in the matrix of multiplier are reduced to two arrays carry and sum. In the final stage, a fast CPA is utilized by adding these two arrays together to get a final product. This technique has a total delay which is proportional to the logarithm of the operand word length, so these multipliers are faster than array multipliers [35].

Because all bits in the partial product matrix can be moved and interchanged as long as they are kept in the same column. Therefore, they can be reorganized in a proper way. Following are steps to implement a Wallace tree multiplier:

1. Reorganize dot matrix into inverted pyramid.

- 2. Group rows into a group of 3.

- 3. Starting at rightmost column using (2,2) and (3,2) counters as long as each subset of 3 has at least 3 rows.

- 4. Repeat Step 2 and 3 until the final height of the reorganized matrix is 2.

As can be seen in the Figure 2.9, each row are grouped in to set of three by using (3, 2) counter as maximum as possible, the rest is group into set of two by using (2, 2) counter. Rows that are not part of a three row set or two row set is transferred to the next reduction stage. The height of the matrix in the  $j^{th}$  reduction stage is  $w_j$  will be defined by the following recursive equation:

$$w_0 = n$$

$$w_{j+1} = 2 \times \left\lfloor \frac{w_j}{3} \right\rfloor + (w_j \mod 3)$$

(2.2)

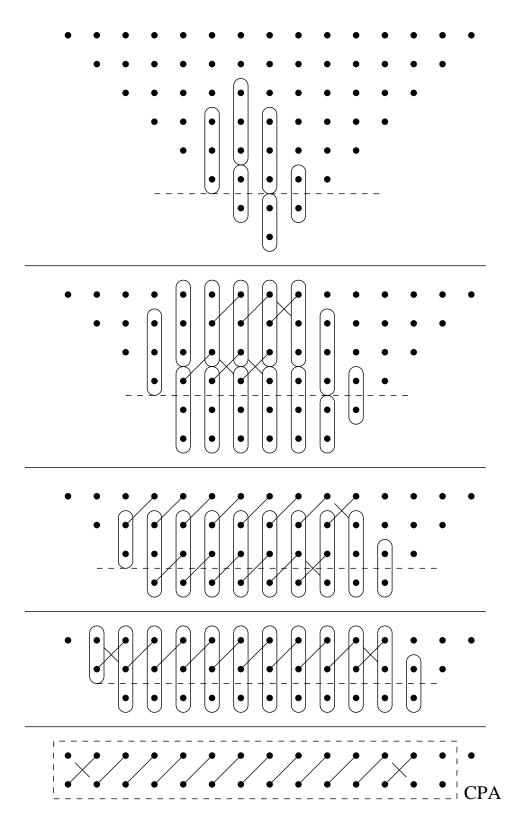

For example, apply Equation 2.2 to the case of n = 8, four stages with their height  $w_1 = 8$ ,  $w_2 = 6$ ,  $w_3 = 4$ , and  $w_4 = 3$  can be computed, respectively. Figure 2.9 is an implementation of  $8 \times 8$ -bit Wallace tree multiplier. As can be seen in this figure, four steps of reduction are processed step by step. In the first stage,  $16 \ FAs$  and  $5 \ HAs$  will be used to reduce matrix to the new one with the height is equal to 6. In the second stage,  $10 \ FAs$  and  $6 \ HAs$  are employed to get a new matrix with its height is 4. In the third stage,  $7 \ FAs$  and  $5 \ HAs$  will be used. In the last stage,  $3 \ FAs$  and  $8 \ HAs$  are employed to reduce the matrix height to 2. The final product is generated by using an 11-bit length CPA. Hence, this multiplier requires  $64 \ AND$  gates,  $36 \ FAs$ ,  $24 \ HAs$  and an 11-bit CPA. The total delay is the sum of one AND gate delay,  $4 \ FA$  delay (through 4 stages) and the delay of the 11-bit length CPA. In general, the total HA, FA, and the length of CPA can be expressed as in [26].

Figure 2.9: Wallace Tree Multiplier.

#### 2.3.2 Dadda Tree Multipliers

In 1965, Wallace tree was modified in [5], in which, a unique placement strategy for the stages reduction was proposed. This technique minimizes the number of (3, 2)and (2, 2) counters [34], but increases the *CPA* length. Therefor the number of intermediate stages is set in term of lower bound. According to [31], the height of partial product matrix (Dadda sequence) can be defined as:

$$2 \rightarrow 3 \rightarrow 4 \rightarrow 6 \rightarrow 9 \rightarrow 13 \rightarrow 19 \rightarrow 28 \rightarrow 42 \rightarrow 63 \cdots$$

Following are stages to implement Dadda tree multipliers:

- 1. Reorganize dot matrix into inverted pyramid (optional).

- 2. Figure out Dadda sequence and where the height of the dot matrix falls within this sequence:

$$\begin{cases} h_0 = 2\\ h_{i+1} = \left\lfloor h_i \times \frac{3}{2} \right\rfloor. \end{cases}$$

(2.3)

Where  $h_i$  is the height for the  $i^{th}$  stage from the end

- 3. Draw a dotted line within Dadda multiplier representing next Dadda sequence.

- Starting at right most column, reduce stage until Dadda sequence is meet from Step 3.

- 5. Repeat from Step 3 until final height is 2.

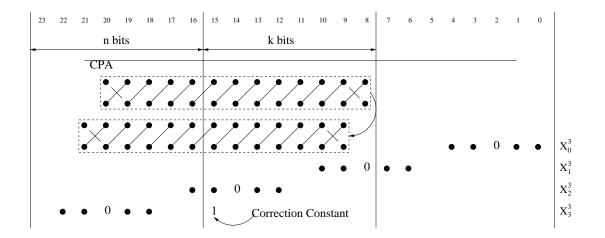

For example, when n = 8, Equation (2.3) is applied, the height sequence  $h_0 = 2$ ,  $h_1 = 3$ ,  $h_2 = 4$ ,  $h_3 = 6$ , and  $h_4 = 8$ , consecutively is established. Four stages are needed for this tree reduction. Figure 2.10 represents an  $8 \times 8$ -bit Dadda tree multiplier. In the first stage, a dotted line divides the matrix into 2 sections with the heights are  $h_3 = 6$ . As can be seen in this figure, starting form the right most to the 5<sup>th</sup> column, each of them has a height smaller or equal to 6, but from the 6<sup>th</sup> column, its height is 7, so one (2, 2) counter must be employed to reduce its height to 6. This counter will bring one carry to the 7<sup>th</sup> column. Hence, one (3, 2) and one (2, 2) counter should be used to reduce the height of 7<sup>th</sup> column to 6. The process continues to the next until the left most column, and hence, a new matrix with the maximum height is 6 is established. Further steps are continued until the height of the final matrix is 2. In the final stage, a 14-bit CPA is used for generating final product. Figure 2.10 shows that this unit requires 64 AND gates, 33 FAs, 9 HAs and one 14-bit length CPA. The total delay of this multiplier is the sum of one AND gate, 4 FA (though four stage reduction) and the delay through the 14-bit length CPA.

In general, the number of (3, 2) and (2, 2) counters and the length of CPA in a Dadda tree is computed in [35]:

$$N_{(3,2)counters} = n^2 - 4n + 3$$

$$N_{(2,2)counters} = n - 1$$

$$CPA_{length} = 2n - 2$$

(2.4)

# 2.3.3 Reduced Area (RA) Multipliers

The RA multiplier is another way to improve both Wallace and Dadda reduction techniques. The difference among RA and Wallace, Dadda tree multiplier is that the maximum number of FAs are utilized as early as possible, and HAs are carefully placed to reduce the word size of the CPA. This is an algorithm that is typically classified as a greedy algorithm. The following is the algorithm for a RA multiplier:

- 1. Reorganize dot matrix into inverted pyramid.

- 2. For each stage, the number of FAs used in column  $i^{th}$  is equal  $\lfloor \frac{b_i}{3} \rfloor$ , where  $b_i$  is the number of bits in column  $i^{th}$

- 3. HAs are only used as follows:

Figure 2.10: Dadda Tree Multiplier.

- (a) In the right most column.

- (b) When required according to Dadda.

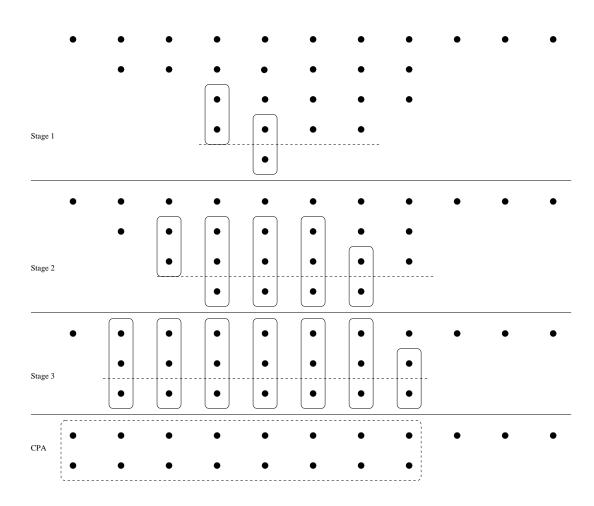

Figure 2.11 shows a PPM for  $8 \times 8$ -bit RA tree multiplier. In the first stage, step 2 is applied to through column  $2^{th}$  to  $12^{th}$ , and only step 3(a) is applied to the column  $1^{th}$ . In the second stage, step 2 is applied to through column  $3^{th}$  to  $12^{th}$ , step 3(a) is applied to the column  $2^{th}$ , and step 3(b) is applied to the column  $8^{th}$  because of violating Dadda sequence. Third and fourth stage will be continue doing in the same way to get carry/sum arrays. The last stage is implemented by using a 10-bit length CPA to get the final result.

As can be seen in Figure 2.11, a  $8 \times 8$ -bit RA tree multiplier requires 64 AND gates, 39 FAs, 7 HAs, and one 10-bit CPA. The total delay for generating final product is the sum of the one AND gate, 4 FA (through 4 stages reduction), and the delay through the 10-bit CPA.

## 2.4 Baugh and Wooley Multiplication

The previous section gave a general idea for unsigned multiplication. For signed ones, Baugh and Wooley [36] proposed a straightforward way for calculating the output product. Using n-bit length multiplier A and multiplicand B, presented in two's

Figure 2.11: Reduce Area Multiplier.

Figure 2.12: PPM of Baugh and Wooley Multiplier.

complement number system, and P is an output product, they can be expressed as:

$$A = -a_{n-1} \cdot 2^{n-1} + \sum_{i=0}^{n-2} a_i \cdot 2^i$$

$$B = -b_{n-1} \cdot 2^{n-1} + \sum_{i=0}^{n-2} b_i \cdot 2^i$$

$$P = a_{n-1} \cdot b_{n-1} \cdot 2^{2n-2} + \sum_{i=0}^{n-2} \sum_{j=0}^{n-2} a_i \cdot b_j \cdot 2^{i+j}$$

$$-[\sum_{j=0}^{n-2} a_{n-1} \cdot b_j 2^{n-1+j} + \sum_{i=0}^{n-2} a_{n-1} \cdot b_i \cdot 2^{n-1+i}]$$

$$= a_{n-1} \cdot b_{n-1} \cdot 2^{2n-2} + \sum_{i=0}^{n-2} \sum_{j=0}^{n-2} a_i \cdot b_j \cdot 2^{i+j}$$

$$+[\sum_{j=0}^{n-2} \overline{a_{n-1} \cdot b_j} \cdot 2^{n-1+j} + \sum_{i=0}^{n-2} \overline{a_{n-1} \cdot b_i} \cdot 2^{n-1+i}]$$

$$+2^{2n-1} + 2^n$$

(2.5)

The PPM of this multiplier can be established as in Figure 2.12. To implement this matrix, some of NAND gates are used instead of AND gates, two bits "1" are added in proper columns for signed adjustment. Figure 2.13 is an implementation of  $8 \times 8$ -bit *Baugh* and *Wooley* multiplier in hardware.

Figure 2.13: Implementation of Baugh and Wooley Multiplier.

#### 2.5 Modified Booth Multipliers with Radix 4

A recoding scheme introduced by Booth [3] reduces the number of partial product bits and the height of its matrix nearly by half, hence, reduces hardware requirement and improve multiplier's performance. Straightforward extensions of the Booth recoding scheme [37, 38] called Modified Booth Multiplier (MBP) can further reduce the number of partial product bits. A digit  $i^{th}$  of a MBP with radix 4 (sometimes called Booth 2) can be recoded as

$$B_{i} = x_{i+1}x_{i}x_{i-1}$$

=  $-2 \cdot x_{i+1} + x_{i} + x_{i-1}$  (2.6)

A signed number X presented in two's complement can be expressed as

$$X = x_{2n-1}x_{2n-2}\cdots x_{1}x_{0}$$

$$= -x_{2n-1} \cdot 2^{2n-1} + \sum_{i=0}^{2n-2} x_{i} \cdot 2^{i}$$

$$= (-2 \cdot x_{2n-1} + x_{2n-2} + x_{2n-3}) \cdot 2^{2(n-1)}$$

$$+ (-2 \cdot x_{2n-3} + x_{2n-4} + x_{2n-5}) \cdot 2^{2(n-2)}$$

$$+ \cdots + (-2 \cdot x_{3} + x_{2} + x_{1}) \cdot 2^{2}$$

$$+ (-2x_{1} + x_{0} + 0) \cdot 2^{0}$$

$$= B_{n-1}B_{n-2}\cdots B_{1}B_{0}$$

$$= \sum_{i=0}^{n-1} B_{i} \cdot 2^{2i}$$

(2.7)

The output of a multiplier unit can be expressed as

$$P = X \cdot Y$$

=

$$\sum_{i=0}^{n-1} (B_i \cdot Y) \cdot 2^{2i}$$

(2.8)

Because  $B_i$  is recoded as in Equation 2.6, so the value of  $B_i$  will be in the set  $\{-2, -1, 0, 1, 2\}$ , hence, each partial product row  $B_i \cdot Y$  will come from the set

| $x_{2i+1}$ | $x_{2i}$ | $x_{2i-1}$ | $B_i \cdot Y$            |

|------------|----------|------------|--------------------------|

| 0          | 0        | 0          | 0                        |

| 0          | 0        | 1          | + Multiplicand           |

| 0          | 1        | 0          | + Multiplicand           |

| 0          | 1        | 1          | $+2 \times Multiplicand$ |

| 1          | 0        | 0          | $-2 \times Multiplicand$ |

| 1          | 0        | 1          | - Multiplicand           |

| 1          | 1        | 0          | - Multiplicand           |

| 1          | 1        | 1          | - 0                      |

Table 2.1: Partial Product Selection

$\{-2Y, -Y, 0, Y, 2Y\}$ . Table 2.1 is selection table for partial product in Booth 2 multiplication.

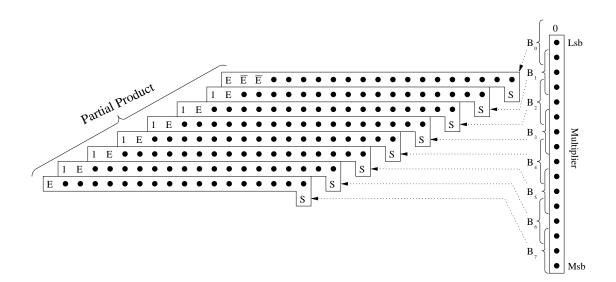

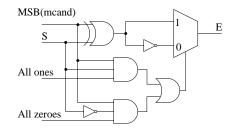

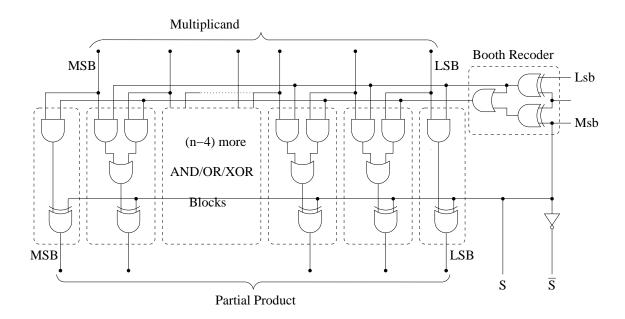

Because it is signed multiplication, the most significant partial product bit of multiplicand operand is kept at the same, no more bits is added to guarantee a positive result . When  $\pm$  Multiplicand (entries 1, 2, 5 and 6 from the partial product selection table) is selected, the n+1 bit section of the effected partial product is filled with a sign extended copy of the multiplicand. This sign extension occurs before any complementing that is necessary to obtain -multiplicand. The *PPM* of Booth 2 multiplier can be viewed as in the Figure 2.14, in which, S is signed bit of  $B_i$ , and E is signed extension bit. The leading "1" strings, created by assuming that all partial products were negative, are cleared in each partial product under a slightly different condition. The leading "1" string for a particular partial product is cleared when that one is positive. For signed multiplication this occurs when the multiplicand is positive and the multiplier select bits chooses a positive multiple, and also when the multiplicand is negative and the multiplier select bits choose a negative multiple. A simple EXCLUSIVE - NOR between the sign bit of the multiplicand and the

Figure 2.14: PPM of Booth 2 Multiplier.

Figure 2.15: Sign Extension Bit of MBP.

high order bit of the partial product selection bits in the multiplier generates the one to be added to clear the leading "1"s correctly [38]. Although the sign extension presented in [38] is efficient at creating two's complement multipliers, it ultimately has a negative effect in that it does not compute positive results well. The reason for incorrect result occurs is that -0 and +0 is really not specified as a multiplicand partial product [39]. To fix that, sign extension bit is synthesized as in Figure 2.15. Each row of dots in the Figure 2.14 is a partial product row and can be generated by using logic functions as in the Figure 2.16.

Figure 2.16: Partial Product Generation of Booth 2.

## CHAPTER 3

#### **Truncated Multipliers**

In most DSP systems, the results of the basic operation are kept at a constant word length. This action is applied for multiplications that uses two n bits inputs and produces a product of 2n bits. The output then rounded to n bits. Consequently, the full addition of the partial product is executed before rounding to get accurate results. Is there any efficient way to do that, so the area and power consumption of a multiplier can be reduce is the goal of many designers. Truncated multipliers are the answer for this question.

Truncated multiplier can produce a fairly accurate result while significantly lowering area requirements. In addition, because of neglecting partial product bits in the least significant columns, truncated multipliers save a large amount of power consumption [28]. The first idea of truncated multiplier was introduced in [40], in which, there are two main methods for compensating the error caused by truncated the less significant part. The first one used a constant to estimate the weight of the truncated part. The second one, called conditional correction, used sum of the first rpartial product terms in the  $(n + k)^{th}$  column to estimate the sum of the first rpartial product terms of the  $(n + k + j)^{th}$  and  $(n + k + j + 1)^{th}$  column.

The constant correction method was refined by Schulte and Swartzlander [41]. Their idea is to use a similar method to [40], except that they used a rounding error to add to the constant. The value of the constant is total of rounding error and the mean of the truncated partial product terms. This idea developed further in [42] in which nearly half of the area of multiplier is truncated. This scheme saves significant area, but produces a large error [43], especially when the width of the multiplicand and multiplier increase. The reason that the error in [42] is larger than that one in [41] is because only one bit '1' is used for compensation. To get results with more accuracy, one more parameter k is used [28,41]. When k increases, the error decreases, but the area and delay of the truncated multiplier increase. It is a trade-off between accuracy and area. Because of using a constant for compensating the error, all multipliers depend on this method are called correction constant truncated multiplier (CCT).

According to [44], the CCT method is easy for implementation, but has larger error compared with other methods. There are two main issues with error of CCTmethod. First, because of adding a constant for all data inputs, the resulting product will have non-zero DC component. Second, to limit the range of the maximum error to be less than an LSB of the data path, the area and power saving cannot be maximized. To reduce the error more, another technique was introduced in [21,44–46], in which, the sum of all partial product bits in the most significant column of truncated part is used for compensating the reduction operation. One additional element of the rounding error in the CCT method is also used. Because the value of that sum is a variable that depends on the inputs of multiplier, hence, this is called variable correction truncated multiplier (VCT).

Many researchers extended the idea of VCT to develop their own variant truncated multipliers. In [43, 47, 48] proposed a scheme, in which half of columns in partial product matrix are truncated. To compensate the error, a circuit made by AND-ORgates is used to generate carries to the next column. The inputs of this circuit are get from two most significant columns in the truncated part. A similar approach presented in [42] saves a lot of area but the circuit has a long critical delay part and no guarantee that the error can be compensated. To solve this problem, [49] proposed a fixed-width signed multiplier in which the circuit generates carries like in [43] are generalized by considering either the partial product terms in the n + k + 1<sup>th</sup> column or their complements. This technique then is extended to the different value of h [50]. Another scheme presented in [51] attempts to explain the result obtained in [50], but the circuit is complicated for implementation and does not improve the performance compared to [50]. Others attempt in [52–54] represented a truncated scheme utilized a modified Booth encoding technique to reduce more area.

According to [45], the maximum error of VCT is smaller than that one of CCT, but it can be costly for the implementation. Another restriction of both CCT and VCT is that the error is not symmetrical. To overcome this restriction, another scheme in [55] was proposed. This architecture looks like VCT except that one more logic circuit is used to adjust VCT error.

Another technique called hybrid correction truncated multiplier (HCT) presented in [28] also tried to reduce error. This technique used a parameter that is the percentage of partial product bits in the most significant column of the truncated area to calculate a constant for compensation. HCT actually is the combination of CCTand VCT methods. The maximum error of the HCT is greater than that one of the VCT, but smaller than that one of the CCT method [28].

Recently, there was another approach [56–61], in which, mean square error of a truncated multiplier is minimized. This approach uses the idea of the VCT, but a function with inputs are the terms in  $(n + k + 1)^{th}$  column are used instead of a variable. In [62] was additional method with mean error is reduced but mean square error is increased compared with that one in [56].

Another technique presented in [63] tried to predict and select a carry bit in a proper way. This technique is suitable when the width of multiplier is small, but not applicable when the width is high, due to the fast growing computational cost of the prediction process.

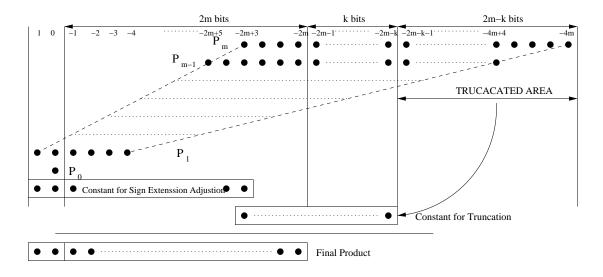

Truncated multiplier can be illustrated as in Figure 3.1. All (n-k) less significant columns in the matrix are omitted, they are not participate in to form the product

Figure 3.1: Product Matrix of Truncated Multiplier

result. As can be seen in this figure, only (n + k - 1) most significant columns are used to compute the product. After that, the product is rounded to r-bit. Because of the truncation and rounding actions, there is a difference between the real result and the truncated result. To make the value of this error becomes smaller, an amount of correction is needed. Depending on the method of compensating for the error is the type of truncated multipliers.

# 3.1 Truncated Multiplication with Correction Constant (CCT)

Parallel multipliers are typically implemented as either carry-save array or tree multiplier [35]. An unsigned *n*-bit multiplicand A is multiplied by an unsigned *n*-bit multiplier B will produce an unsigned 2n-bit product P. For fractional number, the value of A, B, P can be expressed as in the Equation 2.1. In many systems, the 2*n*-bit products are rounded to *r*-bit avoid growth in word size. This idea was introduced in [40] and then developed in [41]. In this method, a constant is added to truncated partial product matrix for compensating the value of the less significant columns that are truncated. As can be seen in Figure 3.1, define P is the true product,  $E_{reduct}$  is the error that caused by the truncation of the less significant columns,  $E_{round}$  is an error that caused by rounding to *r*-bit, Cis the constant for compensating error, and  $\hat{P}$  is the computed product, they can be expressed as:

$$\hat{P} = P + E_{reduct} + E_{round} + C \tag{3.1}$$

The error between computed  $\hat{P}$  and real product P is

$$\epsilon = \hat{P} - P = E_{reduct} + E_{round} + C \tag{3.2}$$

To minimize this error, the correction constant C is selected as the inverse of  $E_{reduct}$ +  $E_{round}$  that depends on the value of input A and B. As can be seen, the probability of any input bit  $a_i$  or  $b_j$  being one is $\frac{1}{2}$ , therefore the partial product bit  $a_i b_j$  being one is  $\frac{1}{4}$ , hence, the expectation value of this partial product bit is  $\frac{2^{-(m+n)+i+j}}{4}$ . On the other hand, column  $k^{th}$  in the partial product matrix has (k+1)-bit, so the reduction error is the inverse of the sum of all partial product bits in the truncated area.

$$E_{reduct} = -\frac{1}{4} \sum_{i=0}^{n-k-1} (i+1)2^{-2n+i}$$

(3.3)

Figure 3.1 also shows that n + k - 1 columns of the most significant part are used to compute n + k-bit product, that is rounded to r bits. Therefore, all bits from column  $(n - k)^{th}$  to  $(r - 1)^{th}$  cause rounding error. Because the probability of  $p_i$  being one is  $\frac{1}{2}$ , the rounding error can be calculated as

$$E_{round} = -\frac{1}{2} \sum_{i=n-k}^{r-1} 2^{-2n+i}$$

(3.4)

The total error that caused by truncation and rounding operations is

$$E_{total} = E_{reduct} + E_{round} \tag{3.5}$$

The constant C is obtained by rounding  $E_{total}$  to r + k fractional bits such that

$$C_{CCT} = \frac{round(2^{r+k}E_{total})}{2^{r+k}}$$

(3.6)

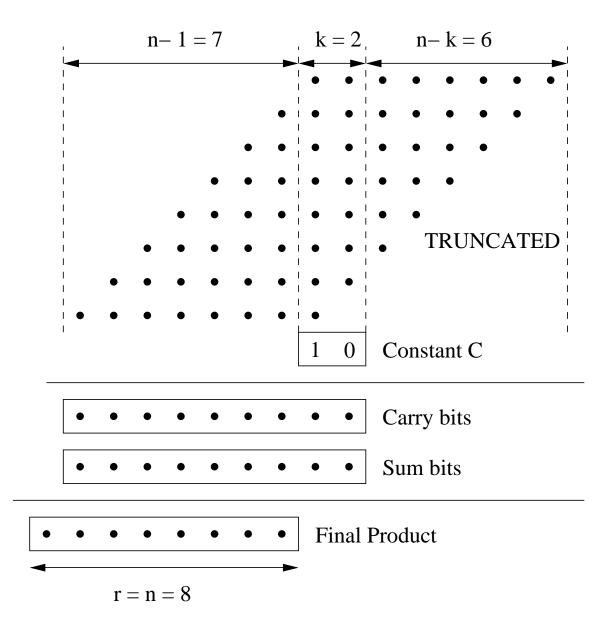

where round(x) indicates that x is rounded to the nearest integer. For example, if n = r = 8 and k = 2, errors and correction constant C can be calculated as:

$$E_{reduct} = -\frac{1}{4} \sum_{i=0}^{5} (i+1)2^{-16+i}$$

$$= -0.001224517822265625$$

$$E_{round} = -\frac{1}{2} \sum_{i=6}^{7} 2^{-16+i}$$

$$= -0.00146484375$$

$$E_{total} = E_{reduct} + E_{round}$$

$$= -0.002689361572265625$$

$$C_{CCT} = -\frac{round(2^{n+k}E_{total})}{2^{n+k}}$$

$$= 0.001953125$$

$$= 2^{-9}$$

(3.7)

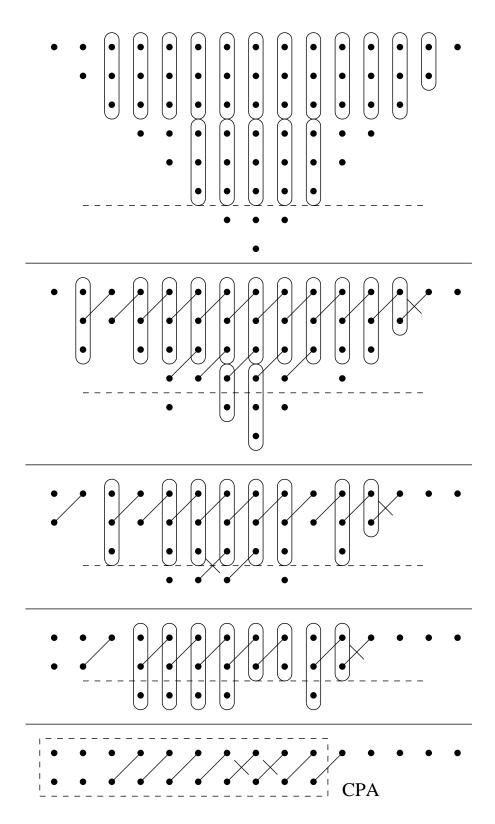

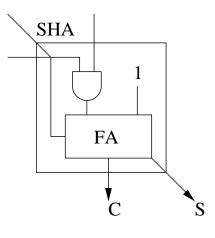

Figure 3.2 represents partial product matrix and Figure 3.3 is hardware implementation of this example. A specialized half adder (SHA) is used for adding the constant C to proper columns in the matrix. The architecture of a SHA is equivalent to a MFA, but it has an internal input which is set to "1" corresponded to the value of the constant C. Figure 3.4 is a hardware implementation of a SHA unit. As can be seen in Figure 3.3, to save more area, a reduced half adder (RHA) and a reduced full adder (RFA), which are the same as a HA and a FA, respectively, but produce only a carry output.

To improve performances of this multiplier, one of three methods in Section 2.3 is applied. Figure 3.5 is Dadda tree diagram for this truncated multiplier, in which, a bit '1' in the column  $1^{th}$  is represented for correction constant C.

Figure 3.2: PPM of  $8 \times 8$ -bit Truncated Multiplier in CCT with k = 2.

Figure 3.3:  $8 \times 8$ -bit CCT with k = 2 in CSAM Implementation.

Figure 3.4: Special Half Adder.

Figure 3.5:  $8 \times 8$ -bit CCT with k = 2 in Dadda Tree Reduction.

As can be seen, the maximum absolute error occurs when all partial product bits in truncated area and the bits in the column 2n - r - k to 2n - r - 1 are '1' or they are all '0'. When they are all "0", the absolute error is C. When they are all "1" the absolute error is

$$\epsilon = \sum_{q=0}^{2n-r-k-1} (q+1) \times 2^{-2n+q} + 2^{-r}(1-2^k)$$

(3.8)

So the maximum absolute error is

$$E_{max} = max(C, \sum_{q=0}^{2n-r-k-1} (q+1) \times 2^{-2n+q} + 2^{-r}(1-2^k))$$

(3.9)

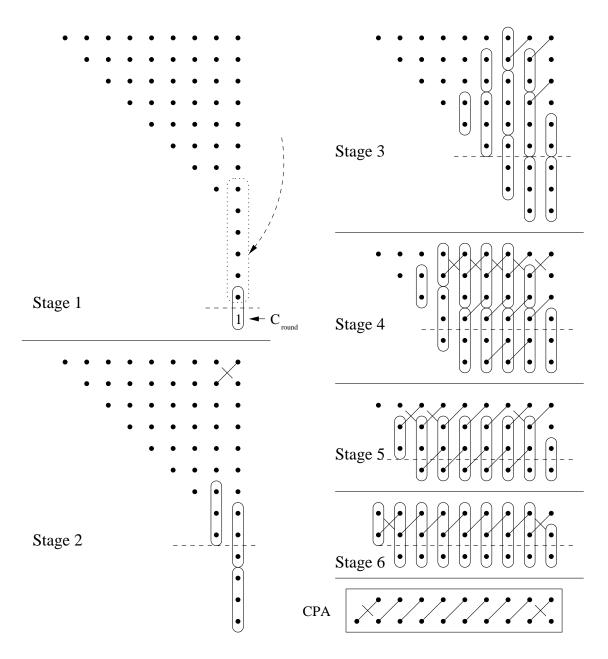

# 3.2 Truncated Multiplication with Variable Correction (VCT)

Truncated multiplier with variable correction was introduced in [44]. To compensate the error made by truncation, the partial product bits in the column  $(n - k - 1)^{th}$ are added to the column  $(n - k)^{th}$ . For rounding error, a constant is added through column  $(n - 2)^{th}$  to column  $(n - k)^{th}$ , so the value of  $C_{round}$  is

$$C_{round} = 2^{-n-1}(1 - 2^{-k+1}) \tag{3.10}$$

For example,  $8 \times 8$ -bit VCT with k = 2,  $C_{round}$  can computed as

$$C_{round} = 2^{-8-1}(1 - 2^{-2+1}) = 2^{-10}$$

(3.11)

Figure 3.6 shows the partial product matrix for this example. Six terms in the column  $5^{th}$  and one bit '1' for  $C_{round}$  are added to the column  $6^{th}$ . Like the CCT method, the VCT multiplier can also be implemented in CSAM, Wallace, Dadda, or RA tree. Figure 3.7 represents this multiplier in a CSAM implementation, and Figure 3.8 is Dadda tree implementation. The maximum error of VCT can be calculated as

$$|E_{VCT}| = 2^{-1} + 2^{-r-k-1} + \sum_{q=1}^{\lfloor \frac{n-k}{2} \rfloor} (n-k+2-2q)2^{-r-k-2q-1}$$

(3.12)

Figure 3.6: PPM of  $8 \times 8$ -bit VCT with k = 2.

Figure 3.7:  $8 \times 8$ -bit VCT with k = 2 in CSAM Implementation.

Figure 3.8: 8  $\times$  8-bit VCT with k=2 in Dadda Tree Reduction.

These errors occur when two operand and the k product bits from the column  $(n-k)^{th}$ to  $(n-1)^{th}$  are

$$a_{n-k-1}\cdots a_{0}, b_{n-k-1}\cdots b_{0} = \begin{cases} 0x\overline{x}\cdots x\overline{x}1, 0x\overline{x}\cdots x\overline{x}1 & \text{if } n-k \text{ is even} \\ 0x\overline{x}\cdots \overline{x}x1, 0x\overline{x}\cdots \overline{x}x1 & \text{if } n-k \text{ is odd} \end{cases}$$

$$p_{n-1}\cdots p_{n-k} = 1\cdots 1 \qquad (3.13)$$

Where x is either "0" or "1". When these inputs fall in these patterns, all bits in the column  $(n - k - 1)^{th}$  are "0". Therefore, the partial product bits in truncated area make the maximum error occurs with the k-bit truncated product from  $(n - 1)^{th}$  to  $(n - k)^{th}$ . The maximum error of the k-bit final product from  $(n - 1)^{th}$  to  $(n - k)^{th}$  is a half of unit in the last place of the n-bit result since the constant rounding  $C_{round}$  is added.

### 3.3 Truncated Multiplication with Hybrid Correction(HCT)

According to previous sections, the maximum error of VCT is less than that one of CCT for a given value of r and k, but the area of VCT is greater than that one of CCT because it uses more partial product bits in the PPM. To improve the VCT, a new method that use both constant and variable correction to make a compromise between both method was introduced in [28]. Since CCT has a maximum absolute error when all bit in truncated area is "1", and VCT has maximum absolute error when all that bits close to "0", HCT multiplier achieves a lower average and maximum absolute error compared to CCT and VCT multipliers.

To implement HCT, a new parameter p, that is the percentage of variable correction is used. This parameter shows that how many partial product bits in the column  $(n - k - 1)^{th}$  will be used to add into the next column. The number of that bits is computed as:

$$N_{HCT} = \lfloor (N_{VCT} \times p) \rfloor \tag{3.14}$$

The constant for HCT can be expressed as

$$C_{HCT} = \frac{1}{2} \times 2^{-r-k-1} \times N_{HCT}$$

(3.15)

A new constant is established based on the difference between the new variable and the constant in CCT method in Equation 3.6. Hence, rounding constant for this method can be expressed as

$$C_{round_{HCT}} = \frac{round((C_{CCT} - C_{HCT}) \times 2^{r+k})}{2^{r+k}}$$

(3.16)

Using the same example like in the previous section n = r = 8, k = 2 and p = 0.5, parameters of *HCT* can be calculated as

$$N_{HCT} = \lfloor (6 \times 0.5) \rfloor$$

= 3

$$C_{HCT} = \frac{1}{2} 2^{-11} \times 3$$

= 3<sup>-12</sup>

$$C_{round_{HCT}} = \frac{round((2^{-9} - 3 \times 2^{-12}) \times 2^{10})}{2^{10}}$$

= 2<sup>-10</sup> (3.17)

Because  $N_{HCT} = 3$ , it means that only 3 bits in the column 5<sup>th</sup> are used to add to the next column. Not lose the generality, these terms  $a_4b_1$ ,  $a_2b_3$  and  $a_0b_5$  are chosen. Figure 3.9 is CSAM and Figure 3.10 is Dadda tree implementation of a HCT multiplier for this example.

Figure 3.9:  $8\times 8\text{-bit}$  HCT with  $k=2,\ p=0.5$  in CSAM Implementation.

Figure 3.10: 8  $\times$  8-bit HCT with  $k=2,\,p=0.5$  in Dadda Tree Implementation.

# CHAPTER 4

#### **Squaring Unit Architectures**

## 4.1 Unsigned Squaring Unit Architectures

Theoretically, a n-bit unsigned integer X is input operand and P is the output of a squaring unit, can be express as

$$X = x_{n-1}x_{n-2}\dots x_1x_0$$

=  $\sum_{i=0}^{n-1} x_i \cdot 2^i$

$$P = X^2$$

=  $(\sum_{i=0}^{n-1} x_i \cdot 2^i)^2$

=  $\sum_{i=0}^{n-1} x_i \cdot 2^{2i} + \sum_{i=0}^{n-2} \sum_{j=i+1}^{n-1} x_i \cdot x_j \cdot 2^{i+j+1}$  (4.1)

Generally, to calculate an output of a squaring unit, the same number is supplied to the inputs of a multiplier as the multiplicand and the multiplier. This is simplest way, but a regular multiplier used as a squaring unit will be redundant [64], and also requires more area, power and delay [65]. To improve its performance, a dedicate squaring unit is necessary

# 4.1.1 Folded Squaring Units

The folding technique, first introduced in [66] and then developed in [67], utilized the symmetrical characteristic of squarer's PPM to reduce the number of its bits and height by nearly a half as in the Equation 4.1. The folding technique for squaring units employs the following steps:

- 1. Optimization of PPM

- (a) A pair of partial product bits  $x_i \cdot x_j$  and  $x_j \cdot x_i$  with  $i \neq j$  in the column  $(i+j)^{th}$  is reduced to one bit  $x_i x_j$ , then shifted to the left one position in the column  $(i+j+1)^{th}$ .

- (b) All bits  $x_i \cdot x_i$  in the column  $(2i)^{th}$  are reduced to  $x_i$  and kept in the same column.

- The matrix height reduction is applied by column compression techniques, such as Dadda [5], to obtain the carry/sum arrays.

- 3. Applying a *CPA* to the carry and sum arrays to obtain the final result.

According to [68], the form of the folded partial product matrix varies slightly based on the value of n is whether odd or even. Figure 4.1 and 4.2 illustrate folded partial product matrix for n = 7 and n = 8, respectively. Due to the symmetry in the *PPM* of a squaring unit, specialized *n*-bit squaring circuits requires less hardware and delay than those ones in a regular  $n \times n$  multiplier.

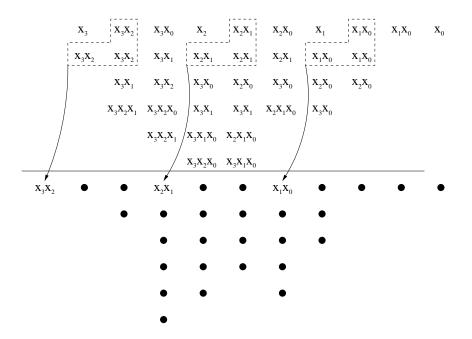

#### 4.1.2 Merged Squaring Units

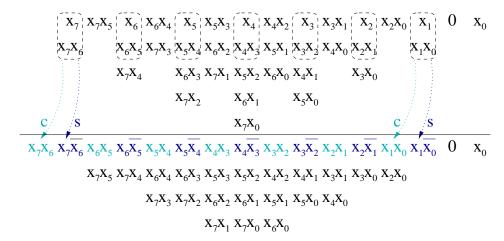

The merging technique presented in [69] and developed in [68,70] augments the conventional folding technique, and reduces the critical path by shifting the partial products on the diagonal by one column to the left. Depending on whether the value of n is odd or even, the height of the PPM is reduced by one compared with that one in folded technique. The idea of this technique is combine to bits  $x_i \cdot x_{i-1}$  and  $x_i$  in the row  $(2i)^{th}$  of the folded PPM together. The equation of this technique can be represented as

$$(x_i \cdot x_{i-1} + x_i) \cdot 2^{2i} = x_i \cdot x_{i-1} \cdot 2^{2i+1} + x_i \cdot \overline{x_{i-1}} \cdot 2^{2i}$$

$$(4.2)$$

Figure 4.1: PPM of Folded Squaring Unit with n = 7

Figure 4.2: PPM of Folded Squaring Unit with n = 8

$$\begin{bmatrix} X_{6} \\ X_{6}X_{4} \\ X_{5} \\ X_{4} \\ X_{5}X_{4} \\ X_{6}X_{2} \\ X_{5}X_{4} \\ X_{6}X_{2} \\ X_{4}X_{3} \\ X_{5}X_{4} \\ X_{6}X_{2} \\ X_{4}X_{3} \\ X_{5}X_{2} \\ X_{6}X_{3} \\ X_{5}X_{2} \\ X_{6}X_{3} \\ X_{5}X_{2} \\ X_{6}X_{3} \\ X_{5}X_{2} \\ X_{6}X_{3} \\ X_{5}X_{2} \\ X_{6}X_{5} \\ X_{6}X_{1} \\ X_{5}X_{1} \\ X_{$$

Figure 4.3: PPM of Merged Squaring Unit with n = 7

Figure 4.4: PPM of Merged Squaring Unit with n = 8

Applied this equation to the folded PPM, n-1 terms are moved one column to the left hand side. The same like in the folded method, the merged PPM is slightly changed when the length of the input n is odd or even. Figure 4.3 and 4.4 illustrate PPM for this method with n = 7 and n = 8. As observed in these figures, when n is even, the height of merged PPM is smaller than that one in the folded PPM.

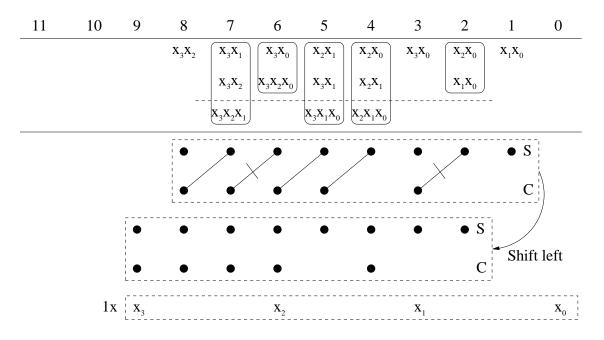

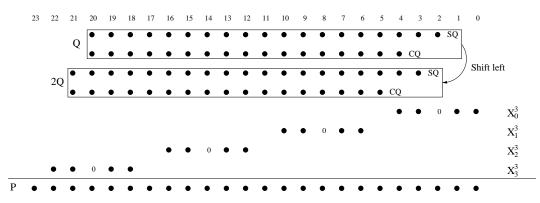

# 4.1.3 Divide and Conquer Squaring Unit

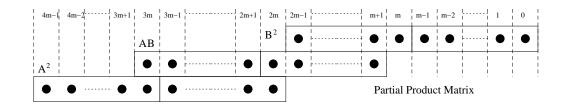

This method was presented in [71, 72], bases on *Vedic* mathematics. A squaring unit base on this method is implemented by the following steps

Figure 4.5: PPM of a Squaring Unit in Divide and Conquer Method

1. Step 1: The input operand X is divided into two parts  $A = x_{2m-1} \dots x_m$  and  $B = x_{m-1} \dots x_0$ , each part contains *m*-bit, and the final result P can be represented as

$$X = A \cdot 2^{m} + B$$

$$P = X^{2}$$

$$= (A \cdot 2^{m} + B)^{2}$$

$$= A^{2} \cdot 2^{2m} + A \cdot B \cdot 2^{m+1} + B^{2}$$

(4.3)

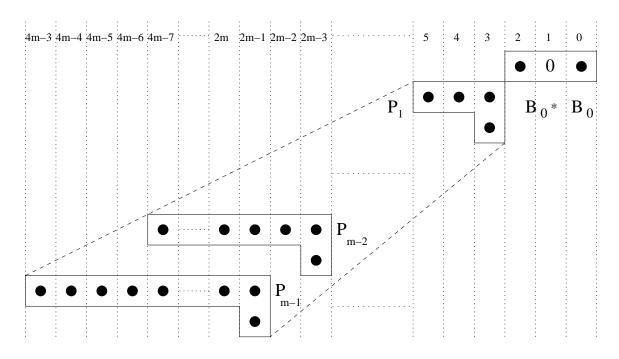

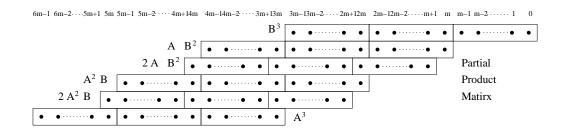

Because each operand A and B has m-bit length, each term  $A^2$ ,  $A \cdot B$ ,  $B^2$  will have 2m-bit length. Therefore, when all the value of  $A^2$ ,  $A \cdot B$ ,  $B^2$ , are known, PPM of this squaring unit is established and the value of P can be computed. This means that this method can only be applied to input operands that are power of two and also each squaring operation is completed in repeated serial steps. Figure 4.5 is PPM for an 2m-bit squaring unit.

- 2. Step 2: Repeat Step 1 until n = 4.

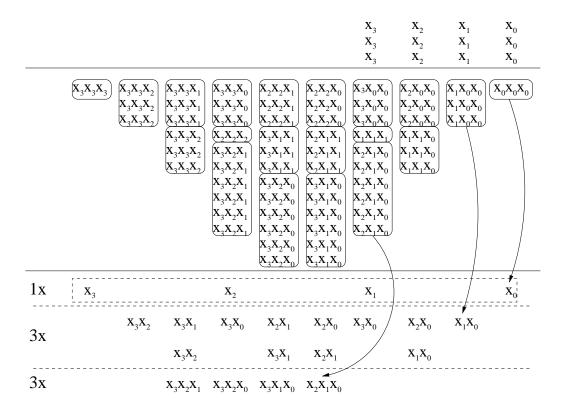

- Step 3: Implement a squaring unit of 4-bit input. X = x<sub>3</sub> ⋅ x<sub>2</sub> ⋅ x<sub>1</sub> ⋅ x<sub>0</sub>, hence,

A = x<sub>3</sub> ⋅ x<sub>2</sub>, B = x<sub>1</sub> ⋅ x<sub>0</sub>. All terms A<sup>2</sup>, B<sup>2</sup>, A ⋅ B will have only 4-bit length and have been expressed as in Figure 4.6

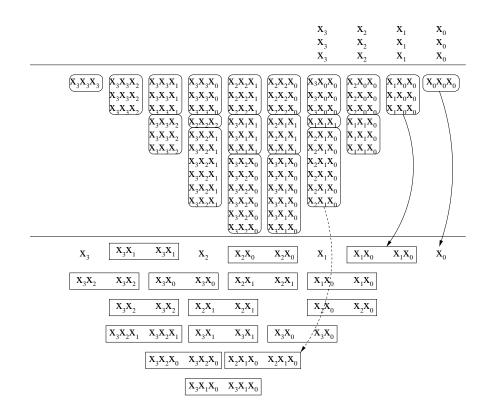

#### 4.1.4 Proposed Squaring Unit

This section proposes a new method that utilizes more regularity of merged PPM to reduce more bits and its height. Following are stages for optimizing its PPM:

|                               |                         | $A^2$                             |                            | <b>B</b> <sup>2</sup>                |                                           |   |     |  |

|-------------------------------|-------------------------|-----------------------------------|----------------------------|--------------------------------------|-------------------------------------------|---|-----|--|

| X <sub>3</sub> X <sub>2</sub> | $X_{3}\overline{X_{2}}$ | 0                                 | X 2                        | $\mathbf{X}_{_{1}}\mathbf{X}_{_{0}}$ | $\mathbf{X}_{1}\overline{\mathbf{X}_{0}}$ | 0 | X , |  |

| AB                            | $X_{3}X_{1}X_{0}$       | $X_{3}X_{1}\overline{X_{2}X_{0}}$ | $X_{3}X_{0}^{*}X_{2}X_{1}$ | $X_{2}X_{0}$                         |                                           |   |     |  |

Figure 4.6: PPM of 4-bit Squaring Unit in Divide and Conquer Method

| Table 4.1: Truth Table of Stage 1 |           |           |               |                  |            |                |  |  |

|-----------------------------------|-----------|-----------|---------------|------------------|------------|----------------|--|--|

| $x_i$                             | $x_{i-1}$ | $x_{i-1}$ | $x_i x_{i-1}$ | $x_{i-1}x_{i-2}$ | $C_{2i}^1$ | $S^{1}_{2i-1}$ |  |  |

| 0                                 | 0         | 0         | 0             | 0                | 0          | 0              |  |  |

| 0                                 | 0         | 1         | 0             | 0                | 0          | 0              |  |  |

| 0                                 | 1         | 0         | 0             | 0                | 0          | 0              |  |  |

| 0                                 | 1         | 1         | 0             | 1                | 0          | 1              |  |  |

| 1                                 | 0         | 0         | 0             | 0                | 0          | 0              |  |  |

| 1                                 | 0         | 1         | 1             | 0                | 0          | 1              |  |  |

| 1                                 | 1         | 0         | 0             | 0                | 0          | 0              |  |  |

| 1                                 | 1         | 1         | 1             | 1                | 1          | 0              |  |  |

Table 4.1: Truth Table of Stage 1

Stage 1: From the merged PPM, two bits x<sub>i</sub> ⋅ x<sub>i-2</sub> and x<sub>i-1</sub> ⋅ x<sub>i-2</sub> in the column (2i − 1)<sup>th</sup> are added together. As can be seen in Table 4.1, the carry and sum bits of this adder can be calculated as:

$$S_{2i-1}^{1} = x_{i} \cdot \overline{x_{i-1}} \cdot x_{i-2} + \overline{x_{i}} \cdot x_{i-1} \cdot x_{i-2}$$

$$C_{2i}^{1} = x_{i} \cdot x_{i-1} \cdot x_{i-2}$$

(4.4)

Figure 4.7 is an illustration for this stage

Stage 2: In this stage, carry bit from Stage 1 C<sup>1</sup><sub>2i</sub> = x<sub>i</sub> ⋅ x<sub>i-1</sub> ⋅ x<sub>i-2</sub> = M is combined with 2 bits x<sub>i</sub> ⋅ x<sub>i-1</sub> = N and x<sub>i+1</sub> ⋅ x<sub>i-2</sub> = Q in row (2i)<sup>th</sup> to form a special full adder. As can be seen in Table 4.1.4, carry and sum outputs of this special full adder are represented as:

$$S_{2i}^{2} = x_{i+1} \cdot \overline{x_{i}} \cdot x_{i-2} + \overline{x_{i+1}} \cdot x_{i} \cdot x_{i-2} + x_{i} \cdot \overline{x_{i-1}} \cdot \overline{x_{i-2}}$$

$$C_{2i+1}^{2} = x_{i+1} \cdot x_{i} \cdot x_{i-2}$$

$$(4.5)$$

| $x_{i+1}$ | $x_i$ | $x_{i-1}$ | $x_{i-2}$ | M | N | Q | $C_{2i+1}^2$ | $S_{2i}^{2}$ |

|-----------|-------|-----------|-----------|---|---|---|--------------|--------------|

| 0         | 0     | 0         | 0         | 0 | 0 | 0 | 0            | 0            |

| 0         | 0     | 0         | 1         | 0 | 0 | 0 | 0            | 0            |

| 0         | 0     | 1         | 0         | 0 | 0 | 0 | 0            | 0            |

| 0         | 0     | 1         | 1         | 0 | 0 | 0 | 0            | 0            |

| 0         | 1     | 0         | 0         | 0 | 1 | 0 | 0            | 1            |

| 0         | 1     | 0         | 1         | 0 | 1 | 0 | 0            | 1            |

| 0         | 1     | 1         | 0         | 0 | 0 | 0 | 0            | 0            |

| 0         | 1     | 1         | 1         | 0 | 0 | 1 | 0            | 1            |

| 1         | 0     | 0         | 0         | 0 | 0 | 0 | 0            | 0            |

| 1         | 0     | 0         | 1         | 1 | 0 | 0 | 0            | 1            |

| 1         | 0     | 1         | 0         | 0 | 0 | 0 | 0            | 0            |

| 1         | 0     | 1         | 1         | 1 | 0 | 0 | 0            | 1            |

| 1         | 1     | 0         | 0         | 0 | 1 | 0 | 0            | 1            |

| 1         | 1     | 0         | 1         | 1 | 1 | 0 | 1            | 0            |

| 1         | 1     | 1         | 0         | 0 | 0 | 0 | 0            | 0            |

| 1         | 1     | 1         | 1         | 1 | 0 | 1 | 1            | 0            |

Table 4.2: Truth Table of A Special Adder in Stage 2

Figure 4.7: Optimization of a Squaring Unit at Stage 1

Figure 4.8: Optimization of a Squaring Unit at Stage 2

Figure 4.8 is an illustration for this stage

Stage 3: In this stage, carry and sum bits from previous stages C<sup>2</sup><sub>2i+1</sub> = x<sub>i+1</sub> ⋅ x<sub>i</sub> ⋅ x<sub>i-2</sub> and S<sup>1</sup><sub>2i+1</sub> = x<sub>i+1</sub> ⋅ x<sub>i</sub> ⋅ x<sub>i-1</sub> + x<sub>i+1</sub> ⋅ x<sub>i</sub> ⋅ x<sub>i-1</sub> are combined together. Because these two bits are not equal to 1 at the same time, therefore, the result will be only 1 bit, which means that one bit in *PPM* can be saved. As can be seen in Table 4.1.4, the sum of these bits can be expressed as:

| Table 4.5. Truth Table of Stage 5 |       |           |           |              |                |                |

|-----------------------------------|-------|-----------|-----------|--------------|----------------|----------------|

| $x_{i+1}$                         | $x_i$ | $x_{i-1}$ | $x_{i-2}$ | $C_{2i+1}^2$ | $S^{1}_{2i+1}$ | $S^{3}_{2i+1}$ |

| 0                                 | 0     | 0         | 0         | 0            | 0              | 0              |

| 0                                 | 0     | 0         | 1         | 0            | 0              | 0              |

| 0                                 | 0     | 1         | 0         | 0            | 0              | 0              |

| 0                                 | 0     | 1         | 1         | 0            | 0              | 0              |

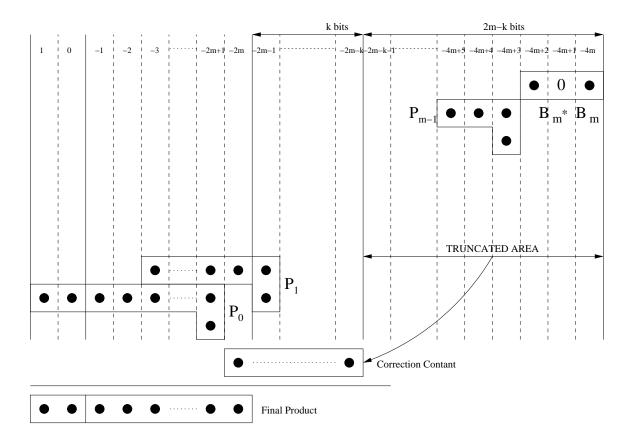

| 0                                 | 1     | 0         | 0         | 0            | 0              | 0              |