## THE STATE MATRIX METHOD FOR

### THE SYNTHESIS OF DIGITAL

### LOGIC SYSTEMS

$\mathbf{By}$

ROBERT L. WOODS () Bachelor of Science

Southern Methodist University

Dallas, Texas

1967

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of MASTER OF SCIENCE May, 1970 THE STATE MATRIX METHOD FOR

STATE

5 1970

TAL PSIT

LOGIC SYSTEMS

# Thesis Approved:

a esiş Advisen Graduate College Dean theof

### ACKNOWLEDGMENTS

I would like to take this opportunity to express my thanks to those people involved in this thesis. In particular, I wish to thank Messrs. Engelland, Brun, and Gertsen for their encouragement during the earily stages of development of this synthesis philosophy.

Thanks are in order to my committee, Professors K. N. Reid, E. C. Fitch, and P. A. McCollum, and a special thanks to Dr. Reid for serving as my thesis adviser.

I also wish to thank Dr. Fitch for allowing this thesis to be published under the Basic Fluid Power Research Program even though this work was not supported by BFPR.

I want to thank Velda Davis for providing such an excellent typing service. It is greatly appreciated.

Those of you who have not undertaken a formal writing such as this cannot realize how important a good wife can be. Those who have, know what I mean when I say, thank you, Brenda.

iii

## TABLE OF CONTENTS

| Chapter | <b>•</b>                                                          | Page                       |

|---------|-------------------------------------------------------------------|----------------------------|

| I.      | INTRODUCTION                                                      | 1                          |

|         | Background                                                        | 2<br>3<br>5                |

| II.     | THE FEEDBACK SEQUENTIAL STATE MATRIX<br>SYNTHESIS PROCEDURE       | 7                          |

|         | Formal Matrix Representation Persistent States                    | 7<br>11<br>19<br>23<br>26  |

| III.    | THE STATE MATRIX SYNTHESIS PROCEDURE<br>FOR RANDOM INPUT CIRCUITS | 34                         |

|         | The Primitive Flow Table                                          | 34<br>39<br>41<br>43<br>46 |

| IV.     | DIGITAL EQUATION SIMULATION AND THE<br>CANONICAL FLOW TABLE       | 54                         |

|         | Digital Equation Simulation                                       | 55<br>61                   |

| v.      | DIGITAL COMPUTER PROGRAMS                                         | 67                         |

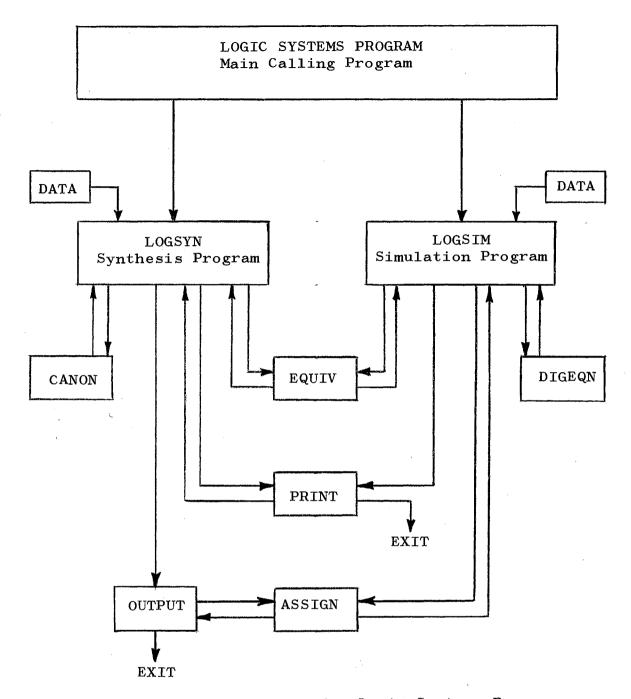

|         | Synthesis Program LOGSYN                                          | 68<br>70                   |

| VI.     | SUMMARY AND CONCLUSIONS                                           | 72                         |

|         | Summary                                                           | 72<br>73<br>77             |

| A SELEC | CTED BIBLIOGRAPHY                                                 | 80                         |

| Chapter                                   | Page |

|-------------------------------------------|------|

| APPENDIX A - THE PASSIVE MEMORY           | 81   |

| APPENDIX B - LISTING OF COMPUTER PROGRAMS | 90   |

| APPENDIX C - EXAMPLE COMPUTER SOLUTIONS   | 104  |

|                                           |      |

| y.                                        |      |

|                                           |      |

· .

$\mathbf{v}$

# LIST OF TABLES

| Table      |                                                                                                                                                            | Page |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| I.         | The Developing State Matrix Relation<br>for the Sequence $Z_1$ , $Z_2$ , $\overline{Z}_1$ , $\overline{Z}_2$                                               | 10   |

| II.        | The State Matrix Relation for the Sequence $Z_1$ , $\overline{Z}_1$ , $Z_2$ , $\overline{Z}_2$                                                             | 12   |

| III.       | The State Matrix Relation for $Z_1$ , $Z_2$ , $\overline{Z}_1$ , $\overline{Z}_2$ , $Z_1$ , $\overline{Z}_1$ , $\overline{Z}_2$ , $Z_1$ , $\overline{Z}_1$ | 20   |

| IV.        | The State Matrix for a 2, 2, 1 Counter                                                                                                                     | 24   |

| <b>V</b> . | Primitive Flow Table for Example 3.1                                                                                                                       | 36   |

| VI.        | Primitive Flow Table for Example 3.2                                                                                                                       | 37   |

| VII.       | Canonical Flow Table for Example 3.2                                                                                                                       | 38   |

| VIII.      | The State Matrix Relation for Example 3.1                                                                                                                  | 40   |

| IX.        | The State Matrix Relation for Example 3.2                                                                                                                  | 41   |

| Χ.         | The Unique State Matrix Relation for<br>Example 3.2                                                                                                        | 43   |

| XI.        | The Primitive Flow Table for Example 3.3                                                                                                                   | 51   |

| XII.       | Step-By-Step Development of Digital<br>Equation Simulation                                                                                                 | 58   |

| XIII.      | The Development of the Canonical Flow Table                                                                                                                | 63   |

vi

### LIST OF FIGURES

| Figu | re                                                                                                                                | Page |

|------|-----------------------------------------------------------------------------------------------------------------------------------|------|

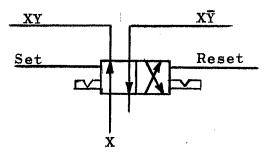

| 1.   | Hydraulic Circuit Illustrating Notation                                                                                           | 8    |

| 2.   | Synthesized Hydraulic Circuit for $Z_1$ , $\overline{Z}_1$ , $Z_2$ , $\overline{Z}_2$                                             | 16   |

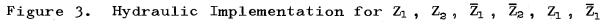

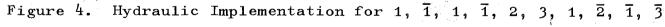

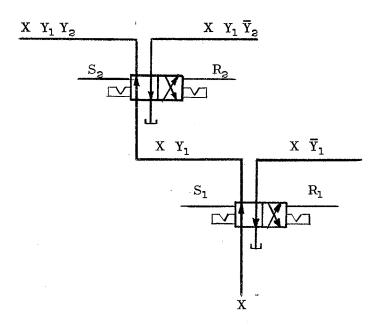

| 3.   | Hydraulic Implementation for $Z_1$ , $Z_2$ ,<br>$\overline{Z}_1$ , $\overline{Z}_2$ , $Z_1$ , $\overline{Z}_1$                    | 22   |

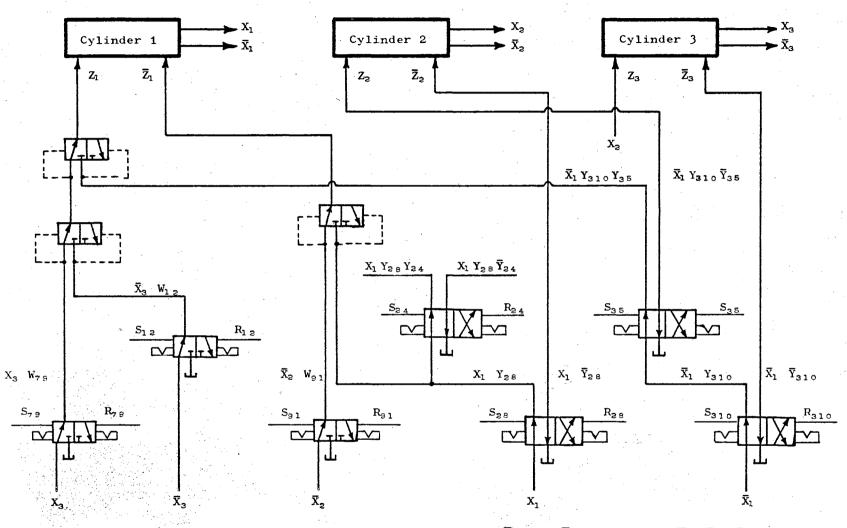

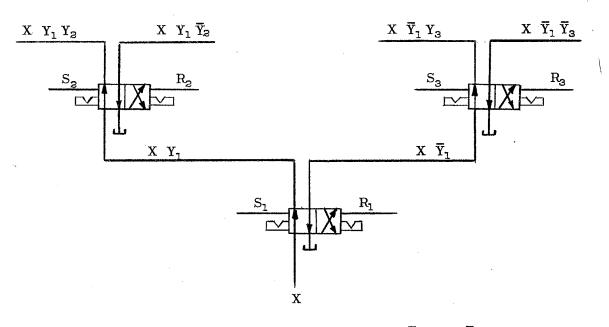

| 4.   | Hydraulic Implementation for<br>1, $\overline{1}$ , 1, $\overline{1}$ , 2, 3, 1, $\overline{2}$ , $\overline{1}$ , $\overline{3}$ | 33   |

| 5.   | Logic Circuit for Example 3.3                                                                                                     | 53   |

| 6.   | Flow Chart for Simulation Method                                                                                                  | 56   |

| 7.   | Flow Diagram for Logic Systems Program                                                                                            | 69   |

| 8.   | Passive Memory Valve                                                                                                              | 82   |

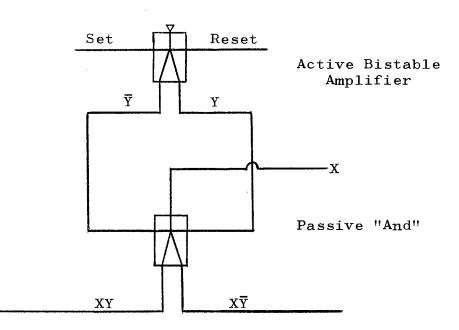

| 9.   | Fluidic Memory Circuit                                                                                                            | 84   |

| 10.  | Passive Memory Assignment Circuits                                                                                                | 86   |

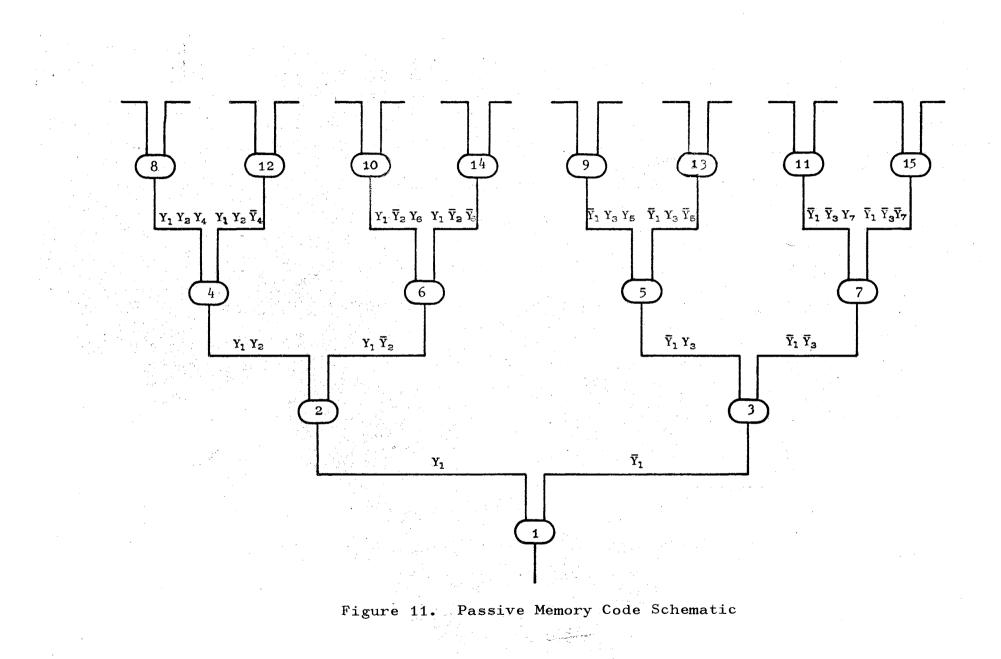

| 11.  | Passive Memory Code Schematic                                                                                                     | 87   |

### CHAPTER I

### INTRODUCTION

The technology of switching circuit theory, although relatively young, has found great application and utility in modern design. Most of the theory has been developed for application in electrical engineering since electronics has dominated the field of computation and logic for the last dew decades.

Recent years have seen a rebirth of the use of a fluid medium to perform the logic and computation in sequential machines. The newly emerging field of fluid technology termed "fluidics" is one major reason for this rebirth of fluid logic. Since fluid power is often used as the muscle of machines, it is convenient also to use the fluid itself for the required computation in order to avoid the electrical to fluid interfaces.

To realize maximum utilization of fluid logic devices, it is necessary to develop a technology of switching circuits applicable to fluid circuits. The theory should consider the unique properties of fluid devices not only in the implementation of circuits, but also in the synthesis procedure itself. The synthesis procedure presented in this

thesis does take advantage of the unique properties of devices in order to produce simple fluid circuits containing minimal hardware.

### Background

Modern switching theory had its origin in 1938 when C. E. Shannon (9), of M.I.T., applied the laws of Boolean algebra to the representation of electrical switches.<sup>1</sup> Although this was a great advancement for combinational switching circuits, there was no formal procedure for the synthesis of sequential switching circuits until 1954 when D. A. Huffman (3) and E. F. Moore (8) independently developed the synthesis technique which is used today. This technique has gained such widespread use and application that today it is taught at every major university and is even referred to as the "classical method". The synthesis procedure presented in this thesis relies upon much of the notation of the classical method. The reader not familiar with this method, should refer to a book on classical switching theory (2), (5), (7), (8).

E. C. Fitch (2), of Oklahoma State University, was one of the first authors to apply the methods of sequential switching circuit theory to hydraulics. However, his work did not take into account any special properties of hydraulic valves except in the implementation of logic circuits.

<sup>&</sup>lt;sup>1</sup>Numbers in parentheses refer to references in the Selected Bibliography.

Later work at Oklahoma State University by J. H. Cole (1) did consider the properties of devices in the synthesis procedure. Dr. Cole used the properties of the passive memory devices to produce extremely simple circuits for the feedback sequential type problem. This work has been a major advancement for the field even though its scope of application is limited.

G. E. Maroney (6) extended Cole's tabular method to include the random input type circuit. This method was fundamentally the same as Cole's except that the random input possibility necessarily complicated the execution of the method. This technique also utilized the passive memory effect to reduce hardware.

Development of the State Matrix Method

The state matrix synthesis procedure evolved from the assumption that the outputs are related to the inputs and the past state of the system. This relationship can be written in matrix form as:

$$\begin{bmatrix} \mathbf{Z} \end{bmatrix} = \begin{bmatrix} \mathbf{M} \end{bmatrix} \begin{bmatrix} \mathbf{X} \end{bmatrix}.$$

Here, the outputs are contained in the  $\begin{bmatrix} Z \end{bmatrix}$  vector, the  $\begin{bmatrix} X \end{bmatrix}$  vector contains the inputs, and the matrix  $\begin{bmatrix} M \end{bmatrix}$  contains output and memory information. This binary matrix changes with time to yield different outputs representing the different states of a sequence.

Early experiments with this type of synthesis were restricted to the feedback sequential type problems because of their simplicity. A close examination of the resulting equations revealed that they were essentially identical to those obtained from Cole's method. This was very encouraging since Cole's method was known to produce valid expressions. The matrix arrangement of this method also gave insight to many of the hidden subtleties of Cole's method.

Once the rules for the synthesis of feedback sequential circuits using state matrices were defined, the method was extended to handle the random input problems. The main difference between the state matrix methods for random input and feedback sequential problems was the input vector used. The feedback sequential input vector contained only the changed input, whereas the random input vector contained the total input state.

The random input form of the state matrix synthesis procedure has since received more attention since it is the more general procedure. This form will also handle the feedback sequential problems in some respects better than the original state matrix method. Hereafter, the random input form of this method will be referred to simply as the "state matrix method", and the method using the changed input vector will be referred to as the "feedback sequential state matrix method."

### Scope and Results of Study

Although the state matrix synthesis procedure is the most important item in this thesis, many other original topics have arisen from this study. The major accomplishments of this study are:

- (1) The development of the feedback sequential state matrix synthesis procedure. (Chapter II)

- (2) The development of the state matrix synthesis procedure for random input circuits.(Chapter III)

- (3) A digital computer program to perform the state matrix synthesis procedure. (Chapter V)

- (4) The development of a simulation technique to check the logical implications of digital equations. (Chapter IV)

- (5) A digital computer program to perform the digital equation simulation and to formulate the implied primitive flow table. (Chapter V)

- (6) The definition of a standard format for the primitive flow table. (Chapter IV)

The state matrix synthesis procedures have the following distinguishing features:

- (1) The basic concepts of circuit synthesis are much easier to grasp than those of other methods.

- (2) The execution of the procedure is straightforward with few or no exceptions to

established rules.

- (3) The resulting digital equations have few of the usual logical complications.

- (4) The procedure takes advantage of device properties to produce circuits with fast response and minimal hardware.

- (5) There is virtually no limitation upon the size or length of the problems which can be handled.

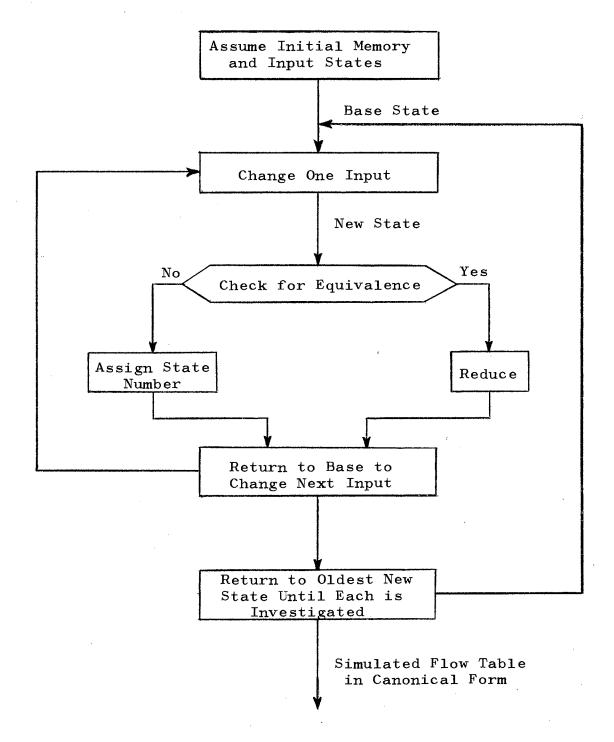

The simulation method presented here provides a check upon the digital equations resulting from a synthesis procedure. Each possible input change is systematically inspected for its effect upon circuit equations and the resulting transitions are recorded in a primitive flow table. This flow table may then be compared to the original flow table which should contain identical information.

In comparing the simulated flow table to its original primitive flow table, it is convenient, if not necessary, to establish a standard flow table format. For this reason, a method similar to the simulation method is used to define the canonical flow table format.

The computer programs included in Appendix B perform the mechanics of synthesis or simulation rapidly and accurately. These programs encompass all of the defined rules and methods for the analysis of digital logic systems and can be utilized to good advantage in design work.

### CHAPTER II

# THE FEEDBACK SEQUENTIAL STATE MATRIX SYNTHESIS PROCEDURE

Although feedback sequential circuits are comparatively simple, they have found a large field of application in modern automation. Consequently, the synthesis of such circuits is of major importance to industrial designers.

Feedback sequential circuits are characterized by their use of a signal indicating the completion of one event to initiate the next event in a prescribed sequence. Feedback sequential circuits are automatic and, once started, require no further attention to sustain sequential action.

### Formal Matrix Representation

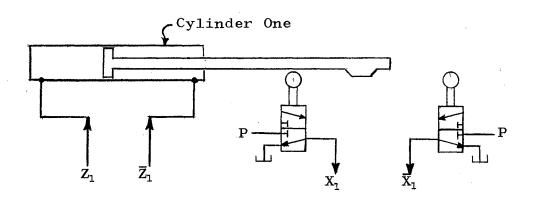

In sequential circuits, each element is associated with one corresponding output from the logic circuit. In a hydraulic circuit this element is typically a hydraulic cylinder and the output is the fluid flow which actuates the cylinder. Since there is usually more than one element in a sequential machine, it is convenient to let  $Z_1$  represent the output which extends cylinder one and  $\overline{Z}_1$  represent the

retract output for the cylinder.<sup>1</sup> The signal  $X_2$  is used as an input to the logic circuit indicating the full extension of cylinder two, and the signal  $\overline{X}_2$  appears when cylinder two is fully retracted. Figure 1 illustrates a physical realization of these variables. The reader who is unfamiliar with hydraulic circuit notation should refer to the literature.

Figure 1. Hydraulic Circuit Illustrating Notation

Using this notation, a sequence involving two cylinders

<sup>&</sup>lt;sup>1</sup>This notation is somewhat unfortunate since  $Z_1$  is used in this chapter to specify only the <u>change</u> of cylinder one, not its continuous state. Also,  $Z_1$  and  $\overline{Z_1}$  are not perfect complements since the specification of one does not imply the other. A more appropriate notation would be  $\Delta Z_1$ , etc.; however, the Z,  $\overline{Z}$  notation is used here for simplicity. A similar statement is true for the inputs X and  $\overline{X}$  used in this chapter only.

can be written as  $Z_1$ ,  $Z_2$ ,  $\overline{Z}_1$ ,  $\overline{Z}_2$ . This implies that cylinder one extends, then cylinder two extends, cylinder one retracts, cylinder two retracts, and then the entire sequence is repeated indefinitely. Each event is initiated by the completion of the proceeding event.

The synthesis of a circuit to execute this sequence proceeds from the assumption that the required outputs from the logic circuit are related to the inputs by the matrix equation given below.

$$\begin{bmatrix} Z_{1} \\ \overline{Z}_{1} \\ \vdots \\ Z_{n} \\ \overline{Z}_{n} \end{bmatrix} = \begin{bmatrix} m_{11} & m_{12} & \dots & m_{1n} \\ \vdots & & \ddots & \vdots \\ m_{n1} & \dots & m_{nn} \end{bmatrix} \begin{bmatrix} X_{1} \\ \overline{X}_{1} \\ \vdots \\ X_{n} \\ \overline{X}_{n} \end{bmatrix}$$

(1)

Recall from the rules of matrix multiplication that when multiplying the matrix [M] by the [X] vector, every entry in the j<sup>th</sup> column of [M] is multiplied by the element in the j<sup>th</sup> row of [X]. Thus, each column in [M] is associated only with the corresponding input element of [X].

For the sequence under consideration, the first event is the extension of cylinder one which results from the previous retraction of cylinder two. Thus, the state number 1 is entered in the matrix in the row of the  $Z_1$  output and the column associated with the  $\overline{X}_2$  input (column four). See Table I.

The next event, the extension of cylinder two, is initiated by the full extension of cylinder one. Hence, the state number 2 is entered in the  $Z_2$  row and the  $X_1$ column. Similarly, state 3 is in the  $\overline{Z}_1$  row and the  $X_2$ column. The sequence is completed by state 4 in the  $\overline{Z}_2$  row,  $\overline{X}_1$  column.

### TABLE I

THE DEVELOPING STATE MATRIX RELATION FOR THE SEQUENCE  $Z_1$ ,  $Z_2$ ,  $\overline{Z}_1$ ,  $\overline{Z}_2$

| $z_1$            | - |   |   |        | 1 | x1                                   |

|------------------|---|---|---|--------|---|--------------------------------------|

| $\overline{Z}_1$ |   |   |   | 3      |   | $\overline{\mathbf{x}}_{\mathtt{l}}$ |

| Z₂               | ~ | 2 |   | -<br>- |   | χ <sup>s</sup>                       |

| Ī₂               |   |   | 4 |        |   | Σ <sub>2</sub>                       |

After all state numbers are entered into Table I, the state matrix must be inspected to ensure that each state is unique and does not represent any contradictions. For this extremely simple problem, this is true and further attention is not required. Table I may now be written matrix form by placing a logical "1" for each state and a "0" elsewhere.

$$\begin{bmatrix} Z_{1} \\ \overline{Z}_{1} \\ Z_{2} \\ \overline{Z}_{2} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 \\ 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \end{bmatrix} \begin{bmatrix} X_{1} \\ \overline{X}_{1} \\ X_{2} \\ \overline{X}_{2} \end{bmatrix}$$

(2a)

The matrix in Table I is termed the <u>state matrix</u> since it only shows the states of the sequence. The matrix in Equation (2a) is termed the <u>output matrix</u> because Equation (2a) is merely a set of digital output equations in matrix notation. Writing Equations (2a) in longhand, one has:

$$Z_{1} = X_{2}$$

$$\overline{Z}_{1} = X_{2}$$

$$Z_{2} = X_{1}$$

$$\overline{Z}_{2} = \overline{X}_{1}$$

$$(2b)$$

Note that the variables used in digital equations are Boolean or binary logic variables.

Since this introductory problem is simple and requires no memory, one could almost predict the results without the use of any formal synthesis procedure. However, further problems in this chapter illustrate the general case.

### Persistent States

The problem of persistent states are prevalent in almost every feedback sequential circuit. Persistent states result when signals remain on long enough to form a

contradiction. The exact cause and remedy for this can best be illustrated by an example.

Consider as example 2 the sequence  $Z_1$ ,  $\overline{Z}_1$ ,  $Z_2$ ,  $\overline{Z}_2$ . The state numbers are entered into Table II in exactly the same fashion as the previous example. That is, state 1 is in the  $Z_1$  row,  $\overline{X}_2$  column. State 2 is in the  $\overline{Z}_1$  row,  $X_1$  column. The remaining state numbers are entered similarly and the resulting state matrix is shown in Table II.

#### TABLE II

# THE STATE MATRIX RELATION FOR THE SEQUENCE $Z_1$ , $\overline{Z}_1$ , $Z_2$ , $\overline{Z}_2$

| $\begin{bmatrix} Z_1 \end{bmatrix}$ |   |   |   |   | 1 | X1                                   |

|-------------------------------------|---|---|---|---|---|--------------------------------------|

| $\overline{Z}_1$                    |   | 2 | ÷ |   |   | $\overline{\mathbf{X}}_{\mathtt{l}}$ |

| Ζ₂                                  | ~ |   | 3 |   |   | Xa                                   |

| īz2                                 |   |   |   | 4 |   | Σs                                   |

If this state matrix were now converted into the output matrix by placing a "1" for the states and a "0" elsewhere, the following equations would result:

$$Z_1 = \overline{X}_2$$

$$\overline{Z}_1 = X_1$$

(3)

Reference to these equations and the state sequence in Table II reveals that cylinder one would be extended by  $\overline{X}_2$  and subsequently retracted by  $X_1$ . However, at the time of retraction the extent signal  $\overline{X}_2$  would still be on, because cylinder two has not been changed since its retraction. Hence, there is a contradiction because cylinder one is trying to extend and retract simultaneously. The signal which remains on creating a contradiction is called a <u>persistent state</u>. In this case, the persistent state is the signal  $\overline{X}_2$  from state 1. This problem arises because only the changed input and the changed output are used in the state matrix relation. An event is specified only by the variables that change, not by the present state of all variables.

This condition can be alleviated by entering a shut-off memory element at the persisting state and its complement at the contradiction. The memory element should be in the "set" position prior to the persistent state and should be in the "reset" position either prior to or on the contradicting state. The complemented memory signal is not used in state signal formulation; it is only used as a reminder when it should be off or in the "reset" position.

For the problem under consideration, the persistent state 1 contradicts state 2. Consequently, state 1 must be modified with a shut-off memory element, say  $W_{12}$ . This element can then be used to shut-off the persistent signal thereby avoiding a contradiction. Further examination of

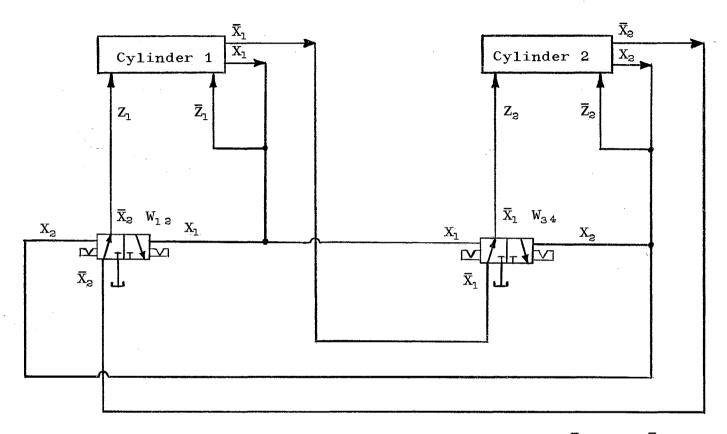

Table 2 reveals that state 3 is persisting at state 4. Hence, the memory element  $W_{34}$  is assigned to state 3. The state matrix for example 2.1 may now be written in output equation form as:

$$\begin{bmatrix} Z_{1} \\ \overline{Z}_{1} \\ Z_{2} \\ \overline{Z}_{2} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & W_{12} \\ 1 & 0 & 0 & 0 \\ 0 & W_{34} & 0 & 0 \\ 0 & 0 & 1 & 0 \end{bmatrix} \begin{bmatrix} X_{1} \\ \overline{X}_{1} \\ X_{2} \\ \overline{X}_{2} \end{bmatrix}$$

(4)

Equations (4) give all of the required output equations to sustain the desired sequential action only if the shutoff memory elements are switched at the proper times.  $W_{12}$ must be in the "set" position in order to formulate the state signal 1; therefore, it may be set prior to its state. In this case,  $W_{12}$  is set by the state signal 4 which is  $X_2$ .  $W_{12}$  must be reset either prior to, or by, state 2. Since the previous state is the persisting state, its signal may not be used to reset itself. Therefore, the contradicting state must be used to shut-off or reset the memory element. Thus, the switching conditions for  $W_{12}$  may be shown as follows:

Set Reset

W<sub>12</sub>

$$X_2$$

$X_1$

State 4 State 2

The notation adopted for subscripting the W elements is quite fortunate since the subscripts of  $W_{l_2}$  (read W one, two) give both the persisting and the contradicting states, respectively. The switching conditions may then be stated by simply observing the subscripts. For example, the memory element  $W_{34}$  is set prior to the persistent state 3 and is reset by the contradicting state 4. Thus, the complete logic specifications for example 2.1 are:

Output Equations:

$$Z_{1} = \overline{X}_{2} \quad W_{12}$$

$$\overline{Z}_{1} = X_{1}$$

$$Z_{2} = \overline{X}_{1} \quad W_{34}$$

$$\overline{Z}_{2} = X_{2}$$

$$(5)$$

Switching Conditions:

SetReset

$$W_{12}$$

$X_2$  $X_1$  $W_{34}$  $X_1$  $X_2$

Before going any further into synthesis procedures, it might be helpful to demonstrate the circuit implementation for this problem. If the circuit shown in Figure 2 is not selfexplanatory, the reader is advised to consult a text on fluid circuits. Refer to Figure 1 for the circuit implied by the boxes representing the cylinders.

Persistent states always occur when two events involving one cylinder are consecutive; however, the same problem arises anytime there is a possibility for a contradiction. This problem may best be illustrated by an example. Consider for example 2.2 the three cylinder sequence  $Z_1$ ,  $Z_2$ ,

$Z_3$ ,  $\overline{Z}_3$ ,  $\overline{Z}_2$ ,  $\overline{Z}_1$ . Following through the sequence, it is found that  $Z_2$  is caused by  $X_1$  in event two. Later, in event five,  $\overline{Z}_2$  is required. However, since cylinder one is not retracted between events two and five, the signal  $X_1$  from event two is still on. Thus, state 2 is a persisting state contradicting event 5. A shut-off memory,  $W_{25}$ , is required to modify state 2. Since states 2 and 5 are not consecutive, the shut-off memory element  $W_{25}$  can be reset just prior to the contradiction, state 5, rather than by the contradiction itself. This is usually more desirable; however, the particular circuit hardware might dictate otherwise.

There are three other persistent states in this sequence. The reader is encouraged to develop the state matrix for this sequence and verify the memory assignment and switching conditions represented by Equations (6). The output matrix for the sequence  $Z_1$ ,  $Z_2$ ,  $Z_3$ ,  $\overline{Z}_3$ ,  $\overline{Z}_2$ ,  $\overline{Z}_1$  is:

| Z                |   | ο               | 1 | 0               | 0               | 0 | ο               | x1                              |     |

|------------------|---|-----------------|---|-----------------|-----------------|---|-----------------|---------------------------------|-----|

| $\overline{Z}_1$ |   | 0               | 0 | 0               | W <sub>61</sub> | 0 | о               | $\bar{\mathbf{x}}_{\mathtt{l}}$ |     |

| Ζa               |   | W <sup>22</sup> | 0 | 0               | Ŏ               | 0 | 0               | x²                              | (6) |

| Ζa               | = | 0               | 0 | O               | 0               | 0 | W <sub>52</sub> | ₹.                              | (0) |

| Z3               |   | 0               | 0 | W <sub>34</sub> | 0               | 0 | 0               | хa                              |     |

| ₹ <sub>3</sub>   |   | 0               | 0 | 0               | 0               | 1 | 0               | ₹.                              |     |

where the switching conditions are:

|                 | Set                                   | Reset                                |

|-----------------|---------------------------------------|--------------------------------------|

| W <sub>25</sub> | $\overline{X}_1$                      | X <sub>3</sub>                       |

| ₩ <sub>34</sub> | X <sub>1</sub> W <sub>25</sub>        | X <sub>3</sub>                       |

| W <sub>61</sub> | X <sub>3</sub> ₩ <sub>52</sub>        | $\overline{\mathbf{X}}_{\mathtt{l}}$ |

| W <sub>52</sub> | X <sub>3</sub>                        | $\overline{\mathbf{x}}_{1}$          |

|                 | · · · · · · · · · · · · · · · · · · · | ·····                                |

When determining persistent states, it is convenient to partition the state matrix according to outputs. The two rows for  $Z_1$  and  $\overline{Z}_1$  represent the output partition one, etc. The two columns for  $X_2$  and  $\overline{X}_2$  are input partition two, etc. With the matrix partitioned in this manner, a systematic method for determining persisting states can be defined. This method requires the individual investigation of each output partition. Starting with the first entry in an output partition, each state is checked by investigating the next entry in the output partition. This next entry is always in the complementary half of the output partition. These two states are always contradictory if they are consecutive and are not within a diagonal partition. A diagonal partition is the four entry square formed by the intersection of an output partition and its corresponding input partition. This square will always be on the diagonal of the matrix. Two consecutive entries in a diagonal partition are not contradictory since the first event turns itself off by the next entry. For the same reason, the event in the output partition following an entry in its diagonal partition is not contradictory. States not covered by the above rule must be examined by applying the following general rule. If the next entry in the output partition is not consecutive and is not within a diagonal partition, then the complementary event of the state immediately preceding the first entry in the output partition must occur before the next entry in the output partition. In other words, the signal that initiated the first entry in the output partition must be negated or turned-off prior to the next entry in the output partition, otherwise the first entry will be a persisting state. The application of these rules is discussed in detail for the example given in the Procedure Summary.

### Memory Assignment

In most sequences, an element is cycled more than once, thus causing an input signal to appear more than once during the sequence. Often, this input signal will initiate a different event each time it appears. In order to determine which event is called for when that input appears, memory of previous events is required.

Consider for example 2.3 the sequence  $Z_1$ ,  $Z_2$ ,  $\overline{Z}_1$ ,  $Z_2$ ,  $Z_1$ ,  $\overline{Z}_1$ . The state matrix shown in Table III is constructed by entering the state numbers as previously discussed. A close examination of this sequence reveals that state 5 is a persistent state. The element  $W_{56}$  is assigned to state 5 to prevent the contradiction at state 6. This element is then

entered into the output matrix for state 5. This is the only persistent state in this sequence.

#### TABLE III

# THE STATE MATRIX RELATION FOR $Z_1$ , $Z_2$ , $\overline{Z}_1$ , $\overline{Z}_2$ , $Z_1$ , $\overline{Z}_1$

| Zı             |     | 1 |   | 5 |                                      |

|----------------|-----|---|---|---|--------------------------------------|

| ĪZı            | 6   |   | 3 |   | $\overline{\mathbf{x}}_{\mathtt{l}}$ |

| Z <sub>2</sub> | . 2 | 1 |   |   | X2                                   |

| Īz             |     | 4 |   |   | X2                                   |

Columns one and two of Table III contain more than one stable state per column. The states 6 and 2 in column one indicate that there are two separate outputs initiated by the input  $X_1$ . One time the input signal  $X_1$  initiates the output  $Z_2$ ; the next time  $X_1$  appears, the output  $\overline{Z}_1$  is desired. In order to distinguish between these states, a memory element is assigned to one of these states and its complement is assigned to the other. For instance, the memory element  $Y_{26}$  is assigned to state 2 and  $\overline{Y}_{26}$  is assigned state 6. In accordance with the W elements, the Y elements are subscripted to denote their associated states. The element  $Y_{26}$  is used to distinguish between states 2 and 6, and is set prior to state 2 and is reset before 6. A similar condition exists between states 1 and 4. The memory element  $Y_{14}$  is used to make each of these states unique.

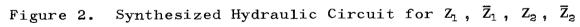

The output matrix is constructed by entering all of the Y elements to distinguish between common input states. The W elements are entered at their persisting states and a "1" is entered for any stable state which does not require memory. A "0" is entered elsewhere. The resulting output matrix for example 2.3 is given by Equation (7).

$$\begin{bmatrix} Z_{1} \\ \bar{Z}_{1} \\ Z_{2} \\ \bar{Z}_{2} \\ \bar{Z}_{2} \end{bmatrix} = \begin{bmatrix} 0 & Y_{14} & 0 & W_{56} \\ \bar{Y}_{26} & 0 & 1 & 0 \\ Y_{26} & 0 & 0 & 0 \\ 0 & \bar{Y}_{14} & 0 & 0 \end{bmatrix} \begin{bmatrix} X_{1} \\ \bar{X}_{1} \\ X_{2} \\ \bar{X}_{2} \end{bmatrix}$$

(7)

Written out, these equations are:

$$Z_{1} = \overline{X}_{1} Y_{14} + \overline{X}_{2} W_{56}$$

$$\overline{Z}_{1} = X_{1} \overline{Y}_{26} + X_{2}$$

$$Z_{2} = X_{1} Y_{26}$$

$$\overline{Z}_{2} = \overline{X}_{1} \overline{Y}_{14}$$

The switching conditions are:

|                 | Set                                  | Reset                    |

|-----------------|--------------------------------------|--------------------------|

| Y <sub>26</sub> | X <sub>1</sub> Y <sub>14</sub>       | X̄₂ ₩ <sub>56</sub>      |

| Y <sub>14</sub> | X1 Y26                               | X2                       |

| W <sub>56</sub> | $\overline{X}_1$ $\overline{Y}_{14}$ | $X_1  \overline{Y}_{26}$ |

Figure 3 is a hydraulic implementation of the logic circuit for this sequence. The passive memory effect is

utilized in this circuit to reduce circuit complexity and hardware. At this point, the reader should refer to Appendix A for a complete discussion of the passive memory effect, assignment, and implementation for hydraulic and fluidic circuits.

### Counting Sequences

Counting sequences are characterized by their repetitious cycling of outputs. For example, a 2,2,1 counter cycles (i.e., extends, retracts) the first element twice, the second twice, and the third once and then repeats the sequence. Counting sequences are handled in exactly the same manner as any other automatic circuit; however, their uniqueness deserves special mention.

In synthesizing this circuit, the usual formal notation is dropped and the simplified approach is introduced. The first simplification is the omission of the output and input vectors. Instead of writing a formal state matrix relation, the rows and columns of the state matrix are labeled corresponding to their associated vectors. With this simplified approach, the state numbers representing the sequence are entered into the matrix as usual. The required memory elements are then assigned adjacent to their state number eliminating the need for rewriting the state matrix into the output matrix form. The output equations are written directly from the completed state matrix.

The first step in synthesizing the equations for

example 2.4 is to enter the state numbers representing the sequence into the state matrix as shown in Table IV. This sequence is written as  $Z_1$ ,  $\overline{Z}_1$ ,  $Z_1$ ,  $\overline{Z}_1$ ,  $Z_2$ ,  $\overline{Z}_2$ ,  $Z_2$ ,  $\overline{Z}_2$ ,  $Z_3$ ,  $\overline{Z}_3$ .

### TABLE IV

$\overline{\mathbf{X}}_{1}$ Χz х<sub>з</sub>  $X_1$  $X_2$ Xa 1 W<sub>12</sub> 3 Y<sub>35</sub>  $Z_1$ 2 Y24  $\overline{\mathbf{Z}}_{1}$  $4 \overline{Y}_{24}$ Y35W56 5 7 Y<sub>79</sub> Ζz 6 Y<sub>68</sub> Ζ₂ 8 ¥6.8 9 Y79 W910  $Z_3$ 10  $\overline{Z}_3$

THE STATE MATRIX FOR A 2,2,1 COUNTER

The next step is the determination of the existence of any persistent states. Applying the rules from page 18 to the matrix under consideration, it is found that states 1 and 2 are contradictory since they are consecutive entries within the same output partition and different input partitions. States 2 and 3 and 3 and 4 are both within diagonal partitions and, thus, are not contradictory. Since state 4 is in a diagonal partition, there is no contradiction between states 4 and 1. Entries like 5 and 6 in the second partition and 9 and 10 in the third partition are contradictory. By similar application of these rules, it can be seen that these are the only three contradictions in this sequence. The shut-off memories (W elements) are now entered into Table IV adjacent to their corresponding persistent states (e.g.,  $W_{12}$  at 1,  $W_{56}$  at 5, and  $W_{910}$  at 9).

The next step of the procedure is the assignment of input memory elements (Y elements). Here, the rule is simple: whenever there is more than one state in a column, a secondary memory state must be assigned to make each state in the column unique. In Table IV there are four such columns requiring memory. The memory elements  $Y_{24}$ ,  $Y_{35}$ ,  $Y_{68}$ ,  $Y_{79}$  are assigned to their corresponding states in accordance to Appendix A.

The last step in the procedure is the specification of the output equations and switching conditions. The output equations are written directly from the state matrix in the same manner as initially discussed. The switching conditions are determined directly from the element subscripts. The complete logical specifications for example 2.4 are given below:

Output equations:

$$Z_{1} = \overline{X}_{1} Y_{35} + \overline{X}_{3} W_{12}$$

$$\overline{Z}_{1} = X_{1} Y_{24} + X_{1} \overline{Y}_{24} = X_{1}$$

$$Z_{2} = \overline{X}_{1} \overline{Y}_{35} W_{56} + \overline{X}_{2} Y_{79}$$

$$\overline{Z}_{2} = X_{2} Y_{68} + X_{2} \overline{Y}_{68} = X_{2}$$

$$Z_{3} = \overline{X}_{2} \overline{Y}_{79} W_{910}$$

$$\overline{Z}_{3} = X_{3}$$

(8)

Switching conditions:

|                  | Set                                                                      | Reset                                       |

|------------------|--------------------------------------------------------------------------|---------------------------------------------|

| Y <sub>24</sub>  | ∏ <sub>3</sub> W₁₂                                                       | Χ <sub>1</sub> Υ <sub>35</sub>              |

| Υ <sub>35</sub>  | $\dot{X}_{1}$ $Y_{24}$                                                   | $X_1  \overline{Y}_{24}$                    |

| Y <sub>68</sub>  | $\overline{\mathrm{X}}_{1}$ $\overline{\mathrm{Y}}_{35}$ W <sub>56</sub> | $\overline{\mathrm{X}}_{2}$ Y <sub>79</sub> |

| Y <sub>79</sub>  | X <sub>2</sub> Y <sub>68</sub>                                           | $X_2$ $\overline{Y}_{68}$                   |

| Ylz              | X <sub>3</sub>                                                           | X <sub>1</sub> Y <sub>24</sub>              |

| W <sub>56</sub>  | $X_1 \overline{Y}_{24}$                                                  | X <sub>2</sub> Y <sub>68</sub>              |

| W <sub>910</sub> | Х <sub>3</sub> Ў <sub>68</sub>                                           | X <sub>3</sub>                              |

Notice that the equations for  $\overline{Z}_1$  and  $\overline{Z}_2$  both reduce, thereby eliminating a memory element. This does not imply that these memory elements are not required. These two signals (states 2 and 4) must be unique since they are used to switch other memories to prepare the proper transition paths.

### Procedure Summary

The procedure for the synthesis of feedback sequential digital control circuits is summarized by the following

four steps:

- Enter State Numbers Write down the specified sequence and number each event in the sequence. Starting with the first event, sequentially enter the state numbers into the state matrix in the row corresponding to the desired output and the column corresponding to the previous event.

- 2. <u>Correct Persistent States</u> Whenever a state signal remains on to form an extend-retract contradiction, the persistent state signal must be modified by a W memory element.

- 3. <u>Assign Memory States</u> Whenever there is more than one state in any column of the state matrix, memory states are required to make each of these states unique.

- 4. <u>Determine Output and Switching Conditions</u> -The digital output equations are obtained from the state matrix by replacing each state number by a logical "1" and all blank entries in the matrix by "0" and then multiplying the matrix. The switching conditions are determined from the memory subscripts.

The following example encompasses all of the defined rules for the synthesis of feedback sequential logic circuits and is worked in detail as a final illustration of this synthesis procedure. The entire problem is presented on page 31 and the procedure is discussed in detail below.

First of all, the sequence is specified and written with state numbers below it, as shown on page 31. This sequence is then entered into the state matrix by placing the state numbers in the row of the desired output and the column of the present input. For example, the state number 1 is entered in the  $Z_1$  row and the  $\bar{X}_3$  column since the first event,  $Z_1$ , is initiated by the previous event which is the retraction of cylinder three. The next event is the retraction of cylinder one; accordingly, state 2 is located in the  $\bar{Z}_1$  row and  $X_1$  column. The remainder of the sequence is entered into the state matrix in the same fashion.

The next step of the procedure requires the investigation of each output partition for the possibility of persistent states. The first partition is investigated by starting with state 1. The next entry in this partition is state 2. Since this is a consecutive entry not within a diagonal partition, states 1 and 2 are contradictory and must be corrected by modifying the persistent state (state 1) with the memory element  $W_{12}$ .  $W_{12}$  is entered in the matrix adjacent to state number 1. The next entry in this partition is state 3. This entry, as well as the next, is within a diagonal partition and is not contradictory. The next entry in partition one after state 4 is state 7. Since state 4 is within a diagonal partition, its initiating signal is negated prior to the next entry (state 7). States 7 and 9 form a contradiction since event 6 has not been

negated before state 9. Accordingly, the memory element  $W_{\gamma 9}$  is entered by state 7. The final entry in partition one is state 1. Since event 8 is not negated before state 1,  $W_{91}$  is placed beside state 9 to correct this contradiction.

The next partition has only two states (5 and 8). It can be seen that these states do not form a contradiction since event 4 is negated by event 7. Similarly, state 8 is not persisting at state 5.

The possible contradiction in partition three (6 and 10) is eliminated since event 5 is negated by event 8. Thus, the signal causing state 6 is turned off before state 10. The state prior to state 10 (state 9) is negated before state 6 eliminating this possible contradiction.

Now that all persistent states have been corrected, the next step in the procedure is the assignment of any required memory states. Column one of the state matrix contains three states (2, 4, and 8). Each of these states must be made unique by modifying the states with the proper memory state. This is done by placing  $Y_{28}$   $Y_{24}$  at state 2,  $Y_{28}$   $\overline{Y}_{24}$  at state 4 and  $\overline{Y}_{28}$  at state 8. (Notice the double subscript notation.) Column two also contains three states, 3, 5, and 10, and the memory elements  $Y_{35}$  and  $Y_{310}$  are assigned accordingly. There are no other columns requiring memory.

The final step of the procedure is the specification of output and switching conditions. The output equations are obtained by mentally replacing each state number by the

logical "1" and multiplying the matrix by the input vector.

The switching conditions for the memory elements are obtained from the element subscripts. For example,  $W_{12}$  is set prior to state 1 by state 10 and is reset by state 2.  $W_{79}$  is set by state 6 and is reset by state 8.  $Y_{24}$  is set by state 1 and reset by state 3, etc.

This problem is worked to completion on the following page.

EXAMPLE PROBLEM

Sequence: 1 1 1  $\overline{2}$  $\mathbf{2}$ State Nos:

|                | X1                                                                                      | $\overline{\mathbf{X}}_{1}$        | X2 | $\overline{\mathrm{X}}_{2}$ | X <sub>3</sub>    | $\overline{X}_{3}$ |

|----------------|-----------------------------------------------------------------------------------------|------------------------------------|----|-----------------------------|-------------------|--------------------|

| Z              |                                                                                         | 3 Y <sub>310</sub> Y <sub>35</sub> |    |                             | 7 W <sub>79</sub> | 1 W <sub>l/2</sub> |

| ₹₁             | $\begin{array}{cccc} 2 & Y_{28} & Y_{24} \\ 4 & Y_{28} & \overline{Y}_{24} \end{array}$ |                                    |    | 9 W <sub>91</sub>           |                   |                    |

| Zə             |                                                                                         | 5 Y <sub>310</sub> Y <sub>35</sub> |    |                             |                   |                    |

| Σ₂             | 8 Y <sub>28</sub>                                                                       |                                    |    |                             |                   |                    |

| Z <sub>3</sub> |                                                                                         |                                    | 6  |                             |                   |                    |

| ₹ <sub>3</sub> |                                                                                         | 10 Y <sub>310</sub>                |    |                             |                   |                    |

Output Equations:

# Switching Conditions:

| Set                                                           | Reset                                                 |

|---------------------------------------------------------------|-------------------------------------------------------|

| $\overline{\mathrm{X}}_{3}$ W <sub>12</sub>                   | $\overline{X}_1$ $Y_{310}$ $Y_{35}$                   |

| $\overline{\mathrm{X}}_{_{3}}$ W <sub>l2</sub>                | X <sub>3</sub> W <sub>79</sub>                        |

| X <sub>1</sub> Y <sub>28</sub> Y <sub>24</sub>                | $X_1 Y_{28} \overline{Y}_{24}$                        |

| X <sub>1</sub> Y <sub>28</sub> Y <sub>24</sub>                | $\overline{X}_{arsigma}$ W <sub>91</sub>              |

| $X_1  \overline{Y}_{28}$                                      | $\overline{X}_1$ $\overline{Y}_{3lo}$                 |

| X <sub>2</sub>                                                | X <sub>1</sub> $\overline{Y}_{28}$                    |

| $ar{\mathrm{X}}_{\texttt{l}}$ $ar{\mathrm{Y}}_{\texttt{3lo}}$ | $X_1 X_{28} Y_{24}$                                   |

|                                                               | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |

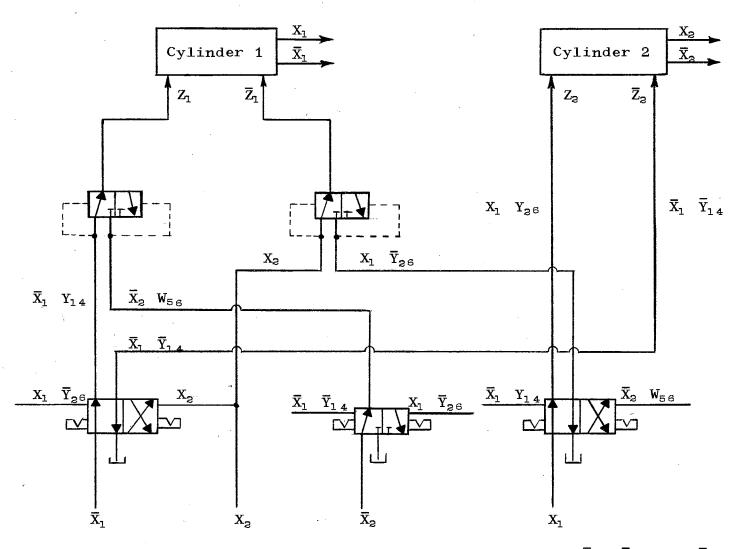

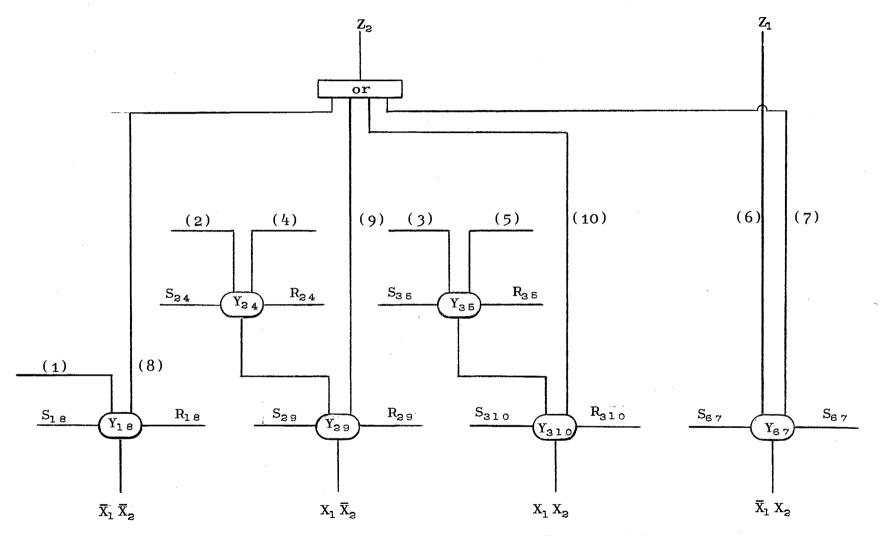

The hydraulic implementation for this circuit is shown in Figure 4. In this circuit, the actual switching signals have been replaced by the notation  $S_{24}$ ,  $R_{35}$ , etc., where  $S_{24}$ denotes the "set" signal for  $Y_{24}$  from the above switching conditions.

ယ ယ

#### CHAPTER III

# THE STATE MATRIX SYNTHESIS PROCEDURE FOR RANDOM INPUT CIRCUITS

Unlike feedback sequential circuits, random input circuits do not anticipate the next input; consequently, every possible input change must be considered. An example of this type of circuit is the secret combination lock in which only one sequence of input changes will result in the proper output (i.e., the opening of the lock). Other sequences might result in different outputs, return to starting position, or many other conceivable situations. In any event, the response to all input change possibilities from any state in the sequence must be specified before a circuit to perform the required logic can be synthesized.

# The Primitive Flow Table

The synthesis of a circuit to perform certain logic sequences must proceed from the word statement of the possible inputs and the desired response to input changes. For every input change, two things must be specified: the resulting output and the desired transition paths from that state. These specifications are most conveniently

represented by the information table termed the <u>Primitive</u> <u>Flow Table</u>.

The primitive flow table contains the complete logic specifications for a problem and is arranged as follows. The columns of the table indicate all of the possible input combinations. These input states are usually labeled above each column according to the Gray code (one variable change between columns). Each row of this table represents the state of the logic system and its corresponding output, Z. Numbers with parentheses around them indicate stable <u>states</u> of the circuit and the unparenthesized numbers show the possible transition paths from one stable state to another.

As example 3.1, consider the primitive flow table shown by Table V. This example has two inputs,  $X_1$  and  $X_2$ , and one output,  $Z_1$ . The table indicates that the logic circuit must provide a path from state (1) to state (2) when the input changes from "00" to "10" as indicated by the transition path numbered 2 in the first row. Also, the circuit must return from (2) to (1) by the path indicated in the second row, first column. Notice that no transition path is shown from input "00", state (1), to input "11", since this would require two inputs to be changed at exactly the same instant, which is highly improbable.

#### TABLE V

PRIMITIVE FLOW TABLE FOR EXAMPLE 3.1

| _ | 00             | 10  | 11  | 01  | Zı |

|---|----------------|-----|-----|-----|----|

|   | (1)            | 2   | _   | 3   | 0  |

|   | 1              | (2) | 4   | -   | 0  |

|   | 1              | -   | 4   | (3) | 0  |

|   | : <del>_</del> | 2   | (4) | 3   | 1  |

In Table V, the output  $Z_1$  results when both inputs are actuated by either the path from state 2 or 3. As is the case with this example, the primitive flow table should specify every possible transition path and should form a closed loop in that there is a path back to the origin or any other state. The above example is extremely simple and requires no memory. When the sequences get larger and inputs are cycled, the need for memory arises as is shown in the next example.

Consider for example 3.2 the primary sequence 00, 10, 11, 01, 11, 10, which results in the output  $Z_1$ . The sequence 00, 01, 11 results in the  $Z_2$  output. All other possible sequences are considered and the transition paths are shown in the completed primitive flow table, Table VI. PRIMITIVE FLOW TABLE FOR EXAMPLE 3.2

| $X_1 X_2$ |     |     |     |    |    |

|-----------|-----|-----|-----|----|----|

| ± 00      | 10  | 11  | 01  | Zl | Za |

| (1)       | 2   | -   | 7   | 0  | 0  |

| 1         | (2) | 3   | -   | 0  | 0  |

| _         | 2   | (3) | 4   | 0  | 0  |

| 1         | -   | 5   | (4) | 0  | 0  |

| -         | 6   | (5) | 4   | 0  | 0  |

| 1         | (6) | 3   | -   | 1  | 0  |

| 1         | -   | 8   | (7) | 0  | 0  |

| -         | 9   | (8) | 7   | 0  | 1  |

| 1 *       | (9) | 3   | -   | 0  | 0  |

Before synthesizing a circuit to perform the indicated logic of Table VI, it is advantageous, although not completely necessary, to administer two additional steps to the primitive flow table. First of all, the primitive flow table should be checked for the possibility of <u>redundant</u> <u>states</u>. Two stable states are said to be redundant if and only if they have the same input state, the same output state, and the same or equivalent transition paths. For example, the states (2) and (9) in Table VI are redundant since they have the same input (they are in the same column), the same output ( $\overline{Z}_1 \ \overline{Z}_2$ ), and the same transition paths (1 and 3). For this reason, the row containing state (9) may be completely removed and all of the transition paths 9 may be replaced with the path indicator 2. There are no more redundancies in this table and the resulting flow table is termed the reduced primitive flow table.

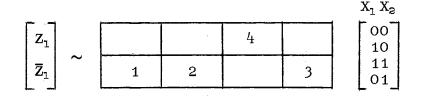

Another advantageous operation on this flow table is the transformation to the <u>canonical flow table</u>. This operation is not completely necessary for the purposes of this chapter, so the definition and detailed discussion of it is deferred until Chapter IV. Briefly though, the basic concept is to <u>order</u> the states according to systematic input changes. The canonical flow table for the problem under consideration (which includes the above mentioned reduction) is shown in Table VII.

#### TABLE VII

#### CANONICAL FLOW TABLE FOR EXAMPLE 3.2

X<sub>1</sub> X<sub>n</sub>

|   | 00  | 10  | 11  | 01  | Zı | Z2 |

|---|-----|-----|-----|-----|----|----|

| ſ | (1) | 2   | -   | 3   | 0  | 0  |

|   | 1   | (2) | 4   | -   | 0  | 0  |

|   | 1   | -   | 5   | (3) | 0  | 0  |

|   | -   | 2   | (4) | 6   | 0  | 0  |

|   | -   | 2   | (5) | 3   | 0  | 1  |

|   | 1   | · — | 7   | (6) | 0  | 0  |

|   | -   | 8   | (7) | 6   | 0  | 0  |

|   | 1   | (8) | • 4 | -   | 1  | 0  |

#### Formal Matrix Representation

Once a problem has been completely specified and the canonical flow table has been derived, the next step is the <u>synthesis</u> of circuit equations to perform the required logic. This synthesis can be reduced to the determination of a unique matrix [M] satisfying the relation.

# $\begin{bmatrix} \mathbf{Z} \end{bmatrix} = \begin{bmatrix} \mathbf{M} \end{bmatrix} \begin{bmatrix} \mathbf{X} \end{bmatrix}$

This is a statement that the outputs  $\begin{bmatrix} Z \end{bmatrix}$  are related to the inputs  $\begin{bmatrix} X \end{bmatrix}$  and previous events. The matrix  $\begin{bmatrix} M \end{bmatrix}$  provides this relationship and contains memory information which defines the present state. The only difference between this matrix relation and the one used for the feedback sequential circuits is the input and output vectors used. In feedback sequential circuit synthesis, the changed input and the changed output vectors are used. For random input circuit synthesis, the input vector contains the total input state (present state of all inputs) and the output vector represents the continuous output state (present state of each output) rather than the change output.

As a first step toward constructing this matrix, the state numbers from the canonical flow table are entered into each of the output partitions. States with an output of  $Z_i$ are entered in the top half of the i<sup>th</sup> output partition and states with the  $\overline{Z}_i$  output are entered in the bottom half. This determines the rows in which states are entered. To determine the proper entry column, recall from the rules of matrix multiplication that each column in the matrix is multiplied only by a corresponding row of the input vector  $\begin{bmatrix} X \end{bmatrix}$ . Thus, a column of the matrix represents events associated with only one input state. Hence, state numbers are entered in the proper row of the output partition and in the column associated with that input state.

To illustrate the state matrix synthesis concept, consider example 3.1 as represented by Table V. This primitive flow table is entered into the state matrix by entering the stable state numbers in the row of the individual output and the column of the present input similar to the way it was done in Chapter II. This matrix is given by Table VIII.

#### TABLE VIII

## THE STATE MATRIX RELATION FOR EXAMPLE 3.1

To obtain the output equation, replace every state number by the logical "1" and place a "0" elsewhere. Multiplying the matrix yields the result:

$$\mathbf{Z}_{1} = \mathbf{X}_{1} \mathbf{X}_{2} \tag{10}$$

The above example illustrates the basic concept of circuit synthesis using state matrices. This problem did not require memory; a more general problem requiring memory is discussed below.

As another example of circuit synthesis, consider example 3.2 represented by the canonical flow table given in Table VIII. The state numbers are entered into the matrix as described above and the result is termed the <u>state matrix</u> relation. See Table IX.

#### TABLE IX

THE STATE MATRIX RELATION FOR EXAMPLE 3.2

### Memory Assignment

As can be seen from Table IX, the only time the output

$Z_1$  appears is state 8. Since state 8 is associated with the input "10", one would be tempted to state that the output  $Z_1$ is equal to  $X_1 \bar{X}_2$ . However, this is not the case since state 2 also has the input "10" but does not have the output  $Z_1$ . Thus, some method to distinguish between states 2 and 8 is required. This is most conveniently done by assigning a memory state at both states. If a memory element was in the "set" position for 2 and in the "reset" position for 8, then these two states would be a unique combination of the input and memory states. This memory element may be represented by placing  $Y_{28}$  adjacent to every 2 in Table IX and its logical complement  $\bar{Y}_{28}$  by states 8. This double subscript notation implies that the memory element  $Y_{28}$  is used to distinguish between states 2 and 8 and is set prior to 2 and is reset prior to 8.

A similar condition exists in column four. Although states 3 and 6 do not have differing outputs, they still required uniqueness since they have different transition paths and their signals are used to switch different memory elements. Therefore, the memory element  $Y_{36}$  is assigned to state 3 and its complement  $\overline{Y}_{36}$  is assigned to state 6. States 4, 5, and 7 in column three also require memory to demand their uniqueness. The memory state  $Y_{47}$   $Y_{45}$  is assigned to state 4,  $Y_{47}$   $\overline{Y}_{45}$  to state 5, and  $\overline{Y}_{47}$  to state 7. Here again, the switching conditions are inferred by the subscripts. At this point, the reader should refer to

Appendix A for further information concerning the passive memory.

The matrix shown in Table X has all of the above memory modifications. Now, each state in this matrix has a unique representation.

### TABLE X

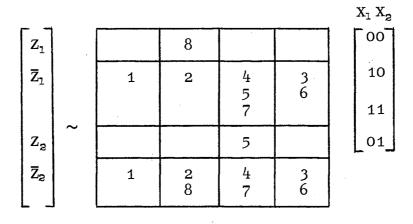

#### THE UNIQUE STATE MATRIX RELATION FOR EXAMPLE 3.2

|                 |   |          |                                        |                                                                                                              |                                         | X <sub>1</sub> 2 | X2 |

|-----------------|---|----------|----------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------|----|

| Z               |   |          | 8 Ī <sub>28</sub>                      |                                                                                                              |                                         | Γο               | 0  |

| <b>Z</b> ₁      |   | 1        | 2 Y <sub>28</sub>                      | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                         | 3 Ү <sub>зб</sub><br>6 Ұ <sub>зб</sub>  | 1                |    |

| Zə              | ~ |          |                                        | 5 $Y_{47}$ $\overline{Y}_{45}$                                                                               |                                         | 0                | 1  |

| _∑ <sup>2</sup> |   | <b>1</b> | 2 Y <sub>28</sub><br>8 <del>Y</del> 28 | $\begin{array}{c} 4  \mathbf{Y}_{4 \ 7}  \mathbf{Y}_{4 \ 5} \\ 7  \overline{\mathbf{Y}}_{4 \ 7} \end{array}$ | 3 Ү <sub>з</sub> е<br>6 <del>Ү</del> зе | _                |    |

ł

## Output and Switching Conditions

The purpose of any synthesis procedure is to give every state a unique signal representation. This signal (or variations upon this signal) is then used either as an output signal or as a switching signal for other memory elements. The above steps produce a state matrix in which every state is represented uniquely by a certain combination of input and memory states. The only remaining step is the specification of the output and switching conditions.

The output equations are obtained from the state matrix relation by replacing every state number designation in the state matrix by the logical "1" and by placing a logical "0" elsewhere. Once this substitution has been made, the resulting matrix is termed the <u>output matrix</u> since it now represents a set of digital equations rather than a state matrix relation. These equations can be rewritten in the individual equation form by multiplying the matrix by the input vector.

The final step in the synthesis procedure is the one which insures the proper circuit operation; this is the specification of when each memory element is to be switched to the proper state. These switching conditions are inferred from the element subscripts and the flow table. For example, the memory element  $Y_{ij}$  is set <u>prior</u> to the state "i" and is reset <u>prior</u> to state "j". This information is obtained from the flow table by observing the possible transition paths to states i and j. The corresponding previous states are to be used for switching signals.

As a specific example, the output and switching conditions for the problem given in Table X are as follows. The output matrix equation is:

|                                   |   |                                      | <u></u>                                                                                           |                                      | X <sub>1</sub> X <sub>2</sub> |

|-----------------------------------|---|--------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------|

|                                   | 0 | Ϋ́ <sub>28</sub>                     | 0 0                                                                                               | 0                                    | 00                            |

| $\overline{Z}_{1}^{\prime\prime}$ | 1 | Y <sub>28</sub>                      | $\begin{array}{cccc} Y_{4\gamma} & Y_{45} & + \\ Y_{4\gamma} & \overline{Y}_{45} & + \end{array}$ | Y <sub>36</sub> +<br>7 <sub>36</sub> | 10                            |

|                                   |   |                                      | $\overline{Y}_{4:\gamma}$                                                                         |                                      | 11                            |

| Z <sub>2</sub>                    | 0 | 0                                    | $Y_{47}$ $\overline{Y}_{45}$                                                                      | 0                                    | 01                            |

| ₹₂                                | 1 | Y <sub>28</sub> +<br>Ŧ <sub>28</sub> | $\begin{array}{cccc} Y_{4\ \gamma} & Y_{4\ 5} & + \\ \overline{Y}_{4\ \gamma} & \end{array}$      | Y <sub>36</sub> +<br>Y <sub>36</sub> |                               |

(11a)

Since the outputs  $Z_1$  and  $\overline{Z}_1$  are perfect complements, only the equations for  $Z_1$  and  $Z_2$  need to be specified. These are:

$$Z_{1} = X_{1} \overline{X}_{2} \overline{Y}_{28}$$

$$Z_{2} = X_{1} X_{2} Y_{47} \overline{Y}_{45}$$

(11b)

The switching conditions as determined from the subscripts and the flow table (Table VII) are:

$$\begin{array}{rll} Y_{4\,5}: & {\rm Set} = {\rm States}\ 2\,+\,8\\ & = & X_1\,\overline{X}_2\\ & {\rm Reset} = {\rm State}\ 3\\ & = & \overline{X}_1\,X_2\ Y_{3\,6}\\ & {\rm Y}_{3\,6}: & {\rm Set} = {\rm States}\ 1\,+\,5\\ & = & \overline{X}_1\,\overline{X}_2\ +\,X_1\,X_2\ Y_{4\,7}\ \overline{Y}_{4\,5}\\ & {\rm Reset} = {\rm States}\ 4\,+\,7\\ & = & X_1\,X_2\ Y_{4\,7}\ Y_{4\,5}\ +\,X_1\,X_2\ \overline{Y}_{4\,7}\end{array}$$

In more compact notation, the switching conditions are:

|                  | Set                                  | Reset                                         |

|------------------|--------------------------------------|-----------------------------------------------|

| Y28              | $00 + 11 Y_{47}$                     | 11 Y <sub>47</sub>                            |

| Y <sub>47</sub>  | 10                                   | 01 $\bar{Y}_{36}$                             |

| Ү <sub>4 Б</sub> | 10                                   | 01 Y <sub>36</sub>                            |

| Y <sub>36</sub>  | 00 + 11 $Y_{47}$ $\overline{Y}_{45}$ | 11 $Y_{47}$ $Y_{45}$ + 11 $\overline{Y}_{47}$ |

Procedure Summary

The state matrix synthesis procedure consists of the following four steps:

- 1. <u>Develop Primitive Flow Table</u> From the word statement of the problem, construct a primitive flow table showing all possible input changes, all possible transitions, and the corresponding outputs. If desired, this flow table may then be transformed into the canonical flow table.

- 2. Form <u>State Matrix</u> Enter the stable state numbers into the state matrix. Each state

number appears in every output partition under the proper column.

- 3. <u>Assign Memory States</u> Whenever there is more than one stable state number in a column, make each state unique by assigning the appropriate memory state.

- 4. <u>Determine Output and Switching Conditions</u> -The output equations are obtained by replacing each state number by "1" and placing a "0" elsewhere and then multiplying the matrix. The output complement need not be specified. The switching conditions are determined from the element subscripts and previous events shown in the flow table.

As a final example of the state matrix synthesis procedure, example 3.3 is worked to completion on page 51, and each step is explained in detail below. The reader may refer to Appendix C for further example problems and their solutions.

Before working the final example, some of the formality of the method can be dropped and the shorthand notation introduced. First of all, the formal matrix representation is omitted and the rows and columns of the matrix itself are merely labeled according to their outputs and inputs. Next, the intermediate step of writing the output matrix is eliminated by mentally multiplying the matrix rather than rewriting it. As a matter of fact, the matrix representation

itself can be eliminated by working directly with the primitive flow table once the reader is familiar with the technique. However, this step is not presented here.

Consider for example 3.3 a secret combination lock in which there is only one proper sequence of output actuations which will open the lock (output  $Z_1$ ). Any deviation from this sequence sounds an alarm (output  $Z_2$ ). The correct sequence is  $X_1$ ,  $X_2$ ,  $\overline{X}_2$ ,  $X_2$ ,  $\overline{X}_1$ ; where X means actuate and hold,  $\overline{X}$  means release. Even though a mistake sounds the alarm, there should be a path provided back to the origin. This primitive flow table is shown on page 51 and is not transformed into the canonical form.

Once the primitive flow table is developed, the next step is the formation of the corresponding state matrix. This is done by entering each state number in the column of the input state and the rows of the individual outputs. For the first output, all state numbers except state 6 are entered in the lower half of output partition one, since all of them have the  $\overline{Z}_1$  output. State 6 is then entered into the  $Z_1$  row of the state matrix. Next, states 1 through 6 are entered in partition two in the  $\overline{Z}_2$  row and states 7 through 10 are entered in the  $Z_2$  row. These two row partitions comprise the state matrix for this example.

The next step is the determination of memory requirements. To do this, each column, representing one combination of the inputs, is treated separately. Reference to the state matrix reveals that every column has multiple states

and requires memory to make each state unique. Column one has two states, 1 and 8, requiring one memory element,  $Y_{18}$ .  $Y_{18}$  is thus entered beside every 1 in the matrix, and its complement  $\overline{Y}_{18}$  is entered adjacent to states 8. Similarily, column two contains three states, 2, 4, and 9. Each of these states is made unique by assigning two memory elements,  $Y_{29}$  and  $Y_{24}$ , in accordance with Appendix A. Column three has three states and column four has two. Memory elements are assigned to these states in the same manner as above.

After the state matrix is formed and the memory requirements are entered adjacent to their respective states, the output equations are obtained by mentally replacing the state numbers with "1's" and then multiplying the matrix by the input vector. The output complements do not have to be specified. The output  $Z_1$  appears at state 6 only. The  $Z_2$ output appears at states 8, 9, 10, and 7.

The final step is the specification of the switching conditions; this step ensures proper circuit operation. If the double subscript notation is used to denote memory elements, the switching conditions are stated from knowledge of the subscripts and the flow table. The subscripts indicate when an element should be in the "set" or "reset" position and the flow table shows the possible transitions to these states. For example,  $Y_{18}$  is set by any state immediately preceding state 1 and is reset by states preceding state 8. From the flow table, it can be seen that the only transition path to only transition path to state 1 is from state 6. There are transition paths to state 8 from states 2, 4, 7, and 9. Thus,  $Y_{18}$  is set by state 6 and is reset by state 2, 4, 7, or 9. The element  $Y_{29}$  is set by state 1 or 8 and is reset by state 5 or 10. The remaining switching conditions are determined in the same fashion and the complete table or switching conditions is given below.

This problem is shown on the next page and the logic circuit schematic is shown in Figure 5.

THE PRIMITIVE FLOW TABLE FOR EXAMPLE 3.3

| x <sub>1</sub> x <sub>2</sub> |     |      |     |                |    |

|-------------------------------|-----|------|-----|----------------|----|

| 00                            | 10  | 11   | 01  | Z <sub>1</sub> | Z2 |

| (1)                           | 2   |      | 7   | 0              | 0  |

| 8                             | (2) | 3    |     | 0              | 0  |

|                               | 4   | (3)  | 7   | 0              | 0  |

| 8                             | (4) | 5    |     | 0              | 0  |

|                               | 9   | (5)  | 6   | 0              | 0  |

| 1                             |     | 10   | (6) | 1              | 0  |

| 8                             |     | 10   | (7) | 0              | 1  |

| (8)                           | 2   |      | 7   | 0              | 1  |

| 8                             | (9) | 10   |     | 0              | 1  |

|                               | 9   | (10) | 7   | 0              | 1  |

The State Matrix:

|    | 00                                     | 10                                                                     | 11                                                                                                                   | 01                |

|----|----------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------|

| Z  |                                        |                                                                        |                                                                                                                      | 6 Y <sub>67</sub> |

| Zı | 1 Y <sub>18</sub><br>8 Ÿ <sub>18</sub> | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                   | $\begin{array}{cccc} 3 & Y_{310} & Y_{35} \\ 5 & Y_{310} & \overline{Y}_{35} \\ 10 & \overline{Y}_{310} \end{array}$ | 7 Ŷ <sub>67</sub> |

| Zg | 8 <b>Y</b> 18                          | 9 ¥29                                                                  | 10 \$\bar{Y}_{310}\$                                                                                                 | 7 Ī <sub>67</sub> |

| ₹₂ | 1 Y <sub>18</sub>                      | 2 Y <sub>29</sub> Y <sub>24</sub><br>4 Y <sub>29</sub> <del>Y</del> 24 | 3 Y <sub>310</sub> Y <sub>35</sub><br>5 Y <sub>310</sub> <del>Y</del> <sub>35</sub>                                  | 6 Y <sub>67</sub> |

Output Equations:

$$Z_{1} = \overline{X}_{1} X_{2} Y_{67}$$

$$Z_{2} = \overline{X}_{1} \overline{X}_{2} \overline{Y}_{18} + X_{1} \overline{X}_{2} \overline{Y}_{29} + X_{1} X_{2} \overline{Y}_{310} + \overline{X}_{1} X_{2} \overline{Y}_{67}$$

(12)

# Switching Conditions:

|                  | Set                                                    | Reset                                                                                  |

|------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------|

| Y <sub>18</sub>  | $\overline{X}_1 X_2 Y_{67}$                            | $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                |

| Y29              | $\overline{\mathbf{X}}_{1}  \overline{\mathbf{X}}_{2}$ | $X_1 X_2 Y_{310} \overline{\overline{Y}}_{35} + X_1 X_2 \overline{\overline{Y}}_{310}$ |

| Y <sub>24</sub>  | $\bar{\mathbf{X}}_{1}  \bar{\mathbf{X}}_{2}$           | $X_1 X_2 Y_{310} Y_{35}$                                                               |

| Y <sub>3lo</sub> | $X_1 \overline{X}_2 Y_{29} Y_{24}$                     | $\overline{X}_1 X_2 + X_1 \overline{X}_2 \overline{Y}_{29}$                            |

| Y <sub>35</sub>  | $X_1 \overline{X}_2 Y_{29} Y_{24}$                     | $X_1 \overline{X}_2  Y_{29} \overline{Y}_{24}$                                         |

| Y <sub>6 7</sub> | $X_1 X_2 Y_{310} \overline{Y}_{35}$                    | $\bar{X}_{1} \bar{X}_{2} + X_{1} X_{2} Y_{310} Y_{35} + X_{1} X_{2} \bar{Y}_{310}$     |

Figure 5. Logic Circuit for Example 3.3

#### CHAPTER IV

# DIGITAL EQUATION SIMULATION AND THE CANONICAL FLOW TABLE

All synthesis procedures will produce valid equations for the representation of the specified logic when the procedure is executed correctly. However, some methods are not easily understood or require personal preference in certain steps. Often, intuitively designed circuits do not function properly or for some reason the circuit action needs to be analyzed. To do this, the implied equations of the circuit can be written.