# COMPUTER AIDED DESIGN OF A DIGITAL FREQUENCY SYNTHESIZER

Bу

BIENVENIDO C. PERALTA Bachelor of Science Oklahoma State University Stillwater, Oklahoma

1953

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of MASTER OF SCIENCE May, 1974

OKLAHOMA STATE UNIVERSITY LIBRARY

SEP 3 1974

# COMPUTER AIDED DESIGN OF A DIGITAL FREQUENCY SYNTHESIZER

## Thesis Approved:

aut Thesis Adviser J Ed L 0

hard L. Cumm Ri

Graduate College the Dean of

## ACKNOWLEDGMENTS

The author wishes to thank the members of his committee, Professors Paul A. McCollum, Richard L. Cummins, and Bennett L. Basore for their guidance and patience.

A note of thanks also to Max Buckles, a colleague at Magnavox, for many helpful programming ideas.

To my wife, Lydia, special thanks for her unquestioning support and encouragement.

# TABLE OF CONTENTS

| Chapter |                                                | Page                         |

|---------|------------------------------------------------|------------------------------|

| Ι.      | INTRODUCTION                                   | . 1                          |

|         | Objectives and Results                         | . 3<br>. 5                   |

| II.     | APPROACH                                       | . 7                          |

| ·       | System Level CAD                               | . 7<br>. 7<br>. 8            |

|         | Sequential Circuits                            | . 91                         |

|         | State Assignment                               | . 17<br>. 18                 |

|         | Output Gating                                  | . 23                         |

| III.    | SYSTEM LEVEL DESIGN                            | . 27                         |

|         | Digital Frequency Synthesizer<br>Specification | . 29<br>. 35                 |

|         | Simulation at the Register Transfer<br>Level   | . 41<br>. 41<br>. 42<br>. 50 |

| IV.     | SYNCHRONOUS LOGIC DESIGN                       | . 53                         |

|         | Input Formats                                  | 53<br>55<br>56               |

Chapter

Page

| I۷  | . ( | (CONTINUED) |  |

|-----|-----|-------------|--|

| 4 1 | •   | 00111110207 |  |

| Counters                                                                                         | 59       |

|--------------------------------------------------------------------------------------------------|----------|

| V. COMPUTER PROGRAM DOCUMENTATION                                                                | 6.5      |

| Synchronous Logic Synthesis Program<br>Asynchronous Logic Synthesis Program                      | 65<br>65 |

| VI. SUMMARY AND CONCLUSIONS                                                                      | 69       |

| Summary                                                                                          | 69<br>70 |

| A SELECTED BIBLIOGRAPHY                                                                          | 71       |

| APPENDIX A - SAMPLE INPUT CODING AND PROGRAM PRINTOUT:<br>SYNCHRONIZATION INDICATOR AND VARIABLE |          |

| MODULO COUNTER                                                                                   | 72       |

| APPENDIX B - SPECIMEN PROGRAM OUTPUTS FROM LOGICMIN                                              | 77       |

| APPENDIX C - COMPUTER LISTING OF SYNCHRONOUS LOGIC<br>DESIGN PROGRAM                             | 82       |

| APPENDIX D - COMPUTER LISTING OF CUBE LOGIC OR<br>ASYNCHRONOUS LOGIC DESIGN PROGRAM              | 95       |

# LIST OF TABLES

| Table |                                                                                                                                       |   | Pa | age |

|-------|---------------------------------------------------------------------------------------------------------------------------------------|---|----|-----|

| I.    | State Transition Table for FFA of<br>Synchronization Indicator                                                                        | • | •  | 14  |

| II.   | Logic Simulator Input Coding for<br>Synchronization Indicator                                                                         | • | •  | 20  |

| III.  | Printout from Logic Simulator Program                                                                                                 | • | •  | 22  |

| IV.   | Printout from FFT Program After Processing<br>Thirty Two Samples of Non-Truncated Data<br>(top) and Seven Bit Data (bottom)           | • | •  | 36  |

| ۷.    | Spectral Analysis Using FFT for Truncated<br>and Non-Truncated Samples. Case I.<br>Synthesizer Set to Lowest Frequency                | • | •  | 37  |

| VI.   | Spectral Analysis Using FFT for Truncated<br>and Non-Truncated Samples. Case II.<br>Synthesizer Set to Five Times Lowest<br>Frequency | • | •  | 38  |

| VII.  | Spectral Analysis Using FFT for Truncated<br>and Non-Truncated Samples. Case III.<br>Synthesizer Set to Six Times Lowest<br>Frequency | • | •  | 39  |

| VIII. | Strength in db of Largest Undesired Frequency<br>Within Pass Band Versus Sample Size                                                  | • | •  | 40  |

| IX.   | Register Transfer Description Used as the<br>System Simulation Program                                                                | • | •  | 44  |

| Χ.    | Sample Output from System Simulation                                                                                                  | • | •  | 47  |

# LIST OF FIGURES

| Figui | re                                                                                                    |   | P | age |

|-------|-------------------------------------------------------------------------------------------------------|---|---|-----|

| 1.    | Timing Diagram for Synchronization Indicator<br>Logic Input = X Output = F1                           | • | • | 12  |

| 2.    | State Diagram of Synchronization Indicator                                                            | • |   | 12  |

| 3.    | Karnaugh Maps for FFA of Synchronization<br>Indicator                                                 | • | • | 14  |

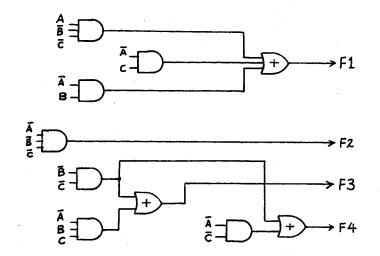

| 4.    | Synchronization Indicator Logic Drawn from<br>Equations Generated by CAD Programs                     | • | • | 16  |

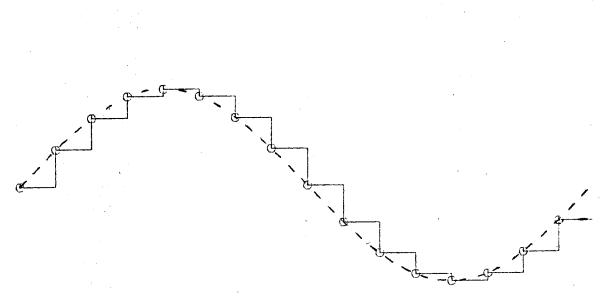

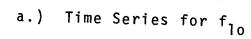

| 5.    | Plot of Time Series of Samples Obtained from<br>Read Only Memory                                      | • | • | 28  |

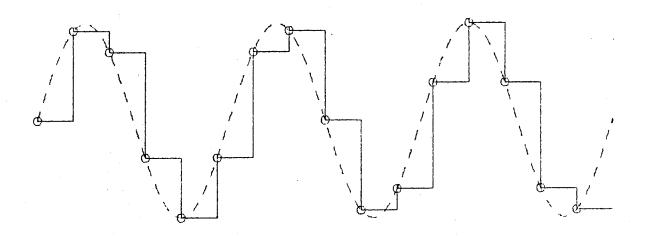

| 6.    | Characteristics of Low Pass Filter                                                                    | • | • | 30  |

| 7.    | Block Diagram of Frequency Synthesizer                                                                | • | • | 31  |

| 8.    | Frequency Synthesizer Timing Chart                                                                    | • | • | 32  |

| 9.    | Timing Diagram for Sweep Mode, Initial f = 32f <sub>lo</sub><br>and Sweep Control Set for 14 Cycles   | • | • | 32  |

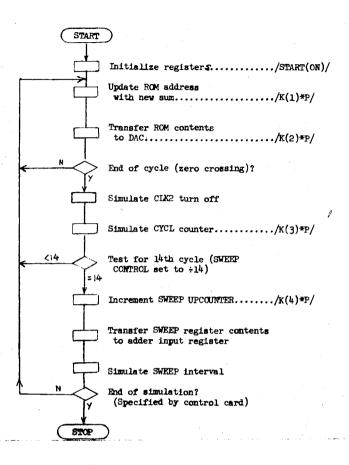

| 10.   | Flow Chart Used to Construct Register Transfer<br>Description                                         | • | • | 43  |

| 11.   | Shift Register for Testing Synchronization<br>Indicator                                               | • | • | 57  |

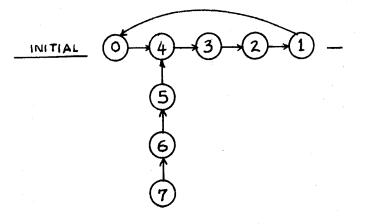

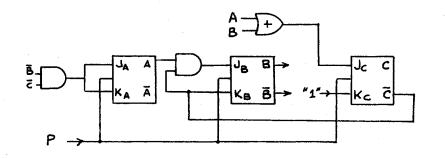

| 12.   | State Diagram Specifying Variable Modulo<br>Counter                                                   | • | • | 58  |

| 13.   | Synchronous Variable Modulo Counter Logic<br>Diagram Drawn from Equations Generated<br>by CAD Program | • | • | 58  |

| 14.   | State Diagram Specifying Divide-by-7 Counter                                                          | • | • | 60  |

| 15.   | Divide-by-7 Counter Obtained from CAD<br>Equations                                                    | • | • | 60  |

| 16.   | State Assignment for Modulo-5 Counter Used<br>in Frequency Sweep Logic                                | • | • | 61  |

| Figu | re                                                                              |   |   |   | Р | age |

|------|---------------------------------------------------------------------------------|---|---|---|---|-----|

| 17.  | Modulo-5 Counter with No Latch Up States                                        | • | • | • | • | 61  |

| 18.  | Frequency Sweep Output Gating Obtained from<br>Multiple Output Prime Implicants | • | • | • | • | 63  |

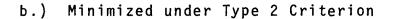

| 19.  | Flow Chart of Synchronous Logic Synthesis<br>Program                            | • | • | • | • | 66  |

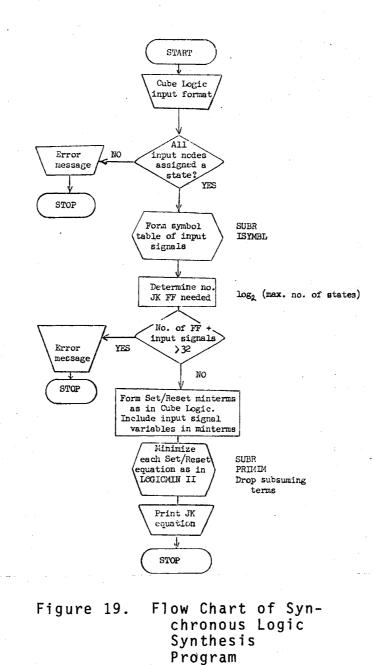

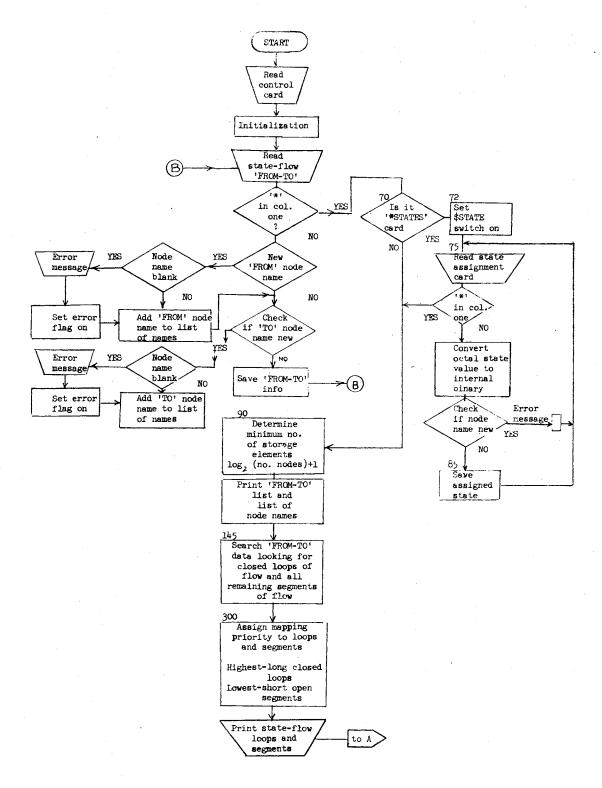

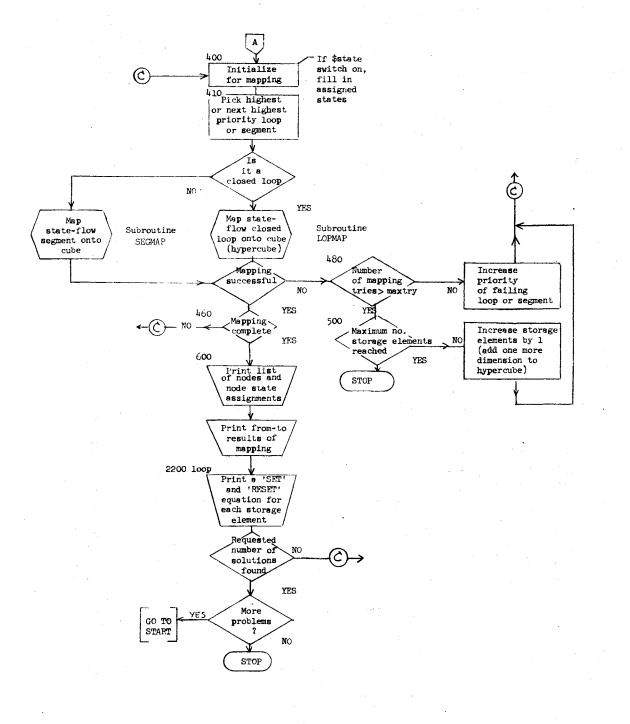

| 20.  | Flow Chart of Asynchronous Logic Synthesis<br>Program                           | • | • | • |   | 67  |

i

## CHAPTER I

#### INTRODUCTION

Computer-aided design, known as CAD in the literature, means many things to many people. The term currently covers all engineering design tasks and certain manufacturing support functions which are assisted by computers.

One of CAD's most successful applications to date is in automating much of the drafting and manual preparation of the "artwork" needed to make printed circuit boards. Programs have been developed which optimize the layout (placement of components) of a circuit board in regard to conductor length and other constraints.

To digital systems engineering, a more significant development occurred when device technologists learned to apply CAD programs similar to those used in circuit board design to their own integrated circuit (IC) artwork generation. Results have been astounding although this started only within the past five years. Improvements in device processing and packaging <u>per se</u> (e.g., passivated silicon junction, epitaxy) had reached a plateau by 1967 or so. However, CAD was able to further reduce the cost of manufacturing IC's while permitting increases in device complexity and performance. Consequently there has been a

growing trend to find new applications of digital circuitry in traditional electronic equipment as well as in automotive, medical, vending machines, and other fields.

CAD of digital components has therefore impacted on the logic design engineer in terms of <u>what</u> work there is to do; it is interesting to note that it is also affecting <u>how</u> to do it. On the matter of "how to do it," device technology today offers components which allow the designer to work at essentially two levels: at the gate/FF level, and at the register transfer or system level. In general, both design levels will be encountered since the former permits synthesis of functions not manufactured as standard IC modules, while the latter uses pre-designed building blocks or standard modules.

Although as noted above CAD has been used profitably in digital device design and production, CAD programs for logic and digital system design and development are not as yet generally available. This may come as a surprise to the reader who knows that <u>analog</u> filter design programs may be purchased, or rented (along with computer time) via remote terminals.

The present situation in regard to <u>digital</u> CAD programs (and particularly sets or systems of inter-related programs) is somewhat similar to the era when a new tool such as the oscilloscope, or perhaps the minicomputer, had just arrived on the scene. Initially they are expensive, and many potential users prefer to wait for a proven, mass produced

model. Others find it more cost-effective to build their own. The author in doing this thesis project has joined with those in the builder category.

Objectives and Results

The goal of this study was to implement a set of programs applicable for the computer-aided design of small digital systems or subsystems.

A survey of expected sources of CAD programs in the areas of logic and digital system design indicated that several synthesis and simulation programs were being used in industry. With the limitations of this study in mind these programs were categorized as available and not avail-The former included low-cost library items such as able. graphical plotting routines, as well as logic simulators and filter design programs which may be accessed via remote terminals. In the not available class were two types of programs: proprietary (for owner company's internal use) and secondly, the few existing CAD software-hardware packages. From this project's viewpoint, the software-hardware systems were unavailable not only because of the five-figure dollar amounts required for their lease but also due to their being primarily data base and documentation systems.

Accordingly, the following objectives were considered:

(1) Develop a computer program for designing synchronous sequential circuits.

(2) To complement item (1) develop a program suitable for system level design.

(3) Search for other programs that are available, in the sense defined previously, for CAD adaptation.

(4) Devise a procedure for applying these programs inCAD of digital systems.

Addressing each of the cited objectives the results of this study are as follows:

(1) A synchronous sequential logic synthesis program was written and "debugged." It accepts as input a simple tabular representation of the state flow diagram of a specification. It outputs all equations needed to construct the circuit synthesized from the state diagram. The schematic may be drawn from the equations using JK flip-flops and IC gates as components.

(2) A register transfer simulation program described in the literature was modified and improved. Although simulation is not synthesis, this simulator can aid the designer by allowing convenient experimentation and evaluation of tentative system configurations. The system structure is described to the program in building block format, while system behavior is simulated in terms of sequences of register transfers and related operations.

(3) Computations for non-digital aspects of the design problem, e.g. spectral analysis and filter design, may be handled with the aid of the fast Fourier transform or FFT

(a library subroutine) and through commercial remote terminals, respectively.

A gate/FF level simulator program was rented after familiarizing with a time-shared version. This program was used for verifying sequential logic designs.

(4) A methodology for computer-assisted design employing the set of programs is reported in this thesis. A case study involving the detailed design of a digital frequency synthesizer is summarized therein.

#### Overview

The five chapters following the Introduction are organized as follows:

Chapter II describes the approaches and algorithms required to implement the programs. A methodology for using these programs for computer-assisted design is also outlined. Topics introduced in Chapter II which may seem tangential include design language, system level and gate level simulation, and non-digital design aspects. Gate level simulation is explained with an example. Programming topics regarding major subroutines of original programs are relegated to Chapter V.

Chapter III considers the design problem at the system level. A new type of frequency synthesizer is presented as a case study in digital system design, hence its functions and specifications are described. Next, the size of the memory word for the synthesizer is determined by analyzing

with the FFT the deterioration of the output waveform as word size is decreased. Feasibility of a proposed system configuration is then studied by simulation. To this end, conversion of block diagrams into register transfer notation is illustrated.

Chapter IV describes the synthesis of synchronous (clocked) sequential circuits. The first example consists of a control function. Subsequent examples deal with shift registers and counters. The remaining examples are concerned with minimization of output gating, and effects of state assignment. All were used in designing the frequency synthesizer.

Programming details, flow charts, listings of the logic synthesis programs, and samples of input coding and resulting printouts (and these comprise "documentation" as used by programmers) are contained in Chapter V and the appendices. For the convenience of the reader, a program which generates asynchronous logic and which served as the prototype for the program employed in Chapter IV is included in Appendix D.

## CHAPTER II

## APPROACH

## System Level CAD

Given today's pre-packaged gate arrays, flip-flops, registers, adders, and other building blocks the task of design starts naturally with the consideration of system level structure and behavior. One may assume that a system can be constructed by (1) selecting a set of building blocks and interconnecting them, and (2) designing non-standard functional blocks, if any are needed, after the system structure has been developed. For this purpose it is convenient to employ a simulator and its programming language.

## Design Language

To simulate a digital system one needs to provide data to a simulator program which describes the system's organization. Additionally the data must convey the details of the system's operations, timing, and control. For ease of preparation and readability, a digital system should be described via a design language.

Duley, et al. [1] and Baray, et al. [2] have proposed languages in which programs containing design specifications may be written, and which serve as inputs for simulation and

synthesis. Chu [3] incorporated the register transfer concept in an Algol-like language that has seen actual use in computer design.

The language adapted in this study is a subset of Chu's Computer Design Language (CDL). As will be shown in Chapter III it can define any register, decoder, memory, and other building blocks. It is easier to learn than Fortran since it is a higher order language. Compared to an equivalent Fortran program, a CDL program would have considerably fewer statements.

## **Register Transfer Simulation**

A CDL description, in conjunction with test data, permits the simulator program to compute a system's behavior or response. The response is characterized primarily as a sequence of values of contents of registers belonging to the system being simulated.

The simulator program used in this study contains two sections: the translator section and simulator proper. The former translates the CDL model of a system (in punched card form) into an internal compiler code and sets up various tables. The latter consists of four routines: Loader, Output, Switch, and Simulate. The Loader accepts the initialization and test data segments of the input card deck and stores them in simulated registers and memories. Results of the simulation are formatted for printing by the Output routine. Printout typically consists of the contents of

certain registers and memory words evaluated at each clock time. Items to be printed are selected by the user. The Switch routine simulates manual switches. The Simulate routine executes the internal compiler code interpretively (i.e. the simulation is performed as though the input program were in machine language).

# Gate Level CAD: Synchronous

## Sequential Circuits

## Manual versus CAD Procedures

A synthesis procedure for synchronous sequential circuits, modelled as Moore machines, consists of five steps:

- (1) Make a flow table from the design specification.

- (2) Reduce the number of rows of the flow table.

- (3) Assign a binary code to each state.

- (4) Determine the flip-flop input equations.

- (5) Design the combinational logic for the output.

We are justified in treating synchronous logic exclusively since its preponderance over asynchronous sequential logic is well known. To a large degree this is due to the fact that the critical race problem does not exist in synchronous sequential circuits and so they are easier to design. When the Moore machine viewpoint is taken, designing the output gating is more straightforward compared with the Mealey model since the output function depends only on the internal state. Further, Friedmann and Menon [4] have

recently shown that this approach lends itself to more systematic production of test patterns (useful in manufacturing and maintenance).

In practice, state assignment is usually done by trial and error. Steps (2) and (4) also contain many tedious operations when more than a few input signals and internal states are required. When done manually step (5) may prove difficult if a large multi-output minimal cost network is desired. Hence the design procedure can benefit from CAD programs.

The CAD programs that were developed assist the designer in performing steps (4) and (5). The name Synchronous Logic Synthesis Program is given to the set since logic equations are generated from which a schematic diagram may be drawn. For reasons to be explained later, methods intended for flow table reduction and state assignment were not programmed.

The suggested CAD procedure follows the manual procedure with two modifications:

(a) The flow table prepared for step (3) is converted into a state diagram.

(b) Only JK flip-flops will be used.

The state diagram of item (a) serves as the input to the synthesis program. Punched cards are easily prepared which convey the node and transition signal data in the form of a from - to table or "wire list." Regarding (b), the JK flip-flop is widely used so that specializing the present

version to a single flip-flop type in order to simplify the program seems justified.

#### CAD Synthesis Algorithms

The following algorithm is commonly used for determining the flip-flop input equations of sequential circuits using JKFF's. (Notations of the form JKFF and FFA denote JK flip-flop and flip-flop A respectively.)

(1) Make a state transition table for each JKFF to be used.

(2) Draw Karnaugh maps for each state transition table.

(3) Derive the minimized JKFF input equations from the maps.

The Synchronous Logic Synthesis Program mechanizes the above procedure. Corresponding to the first step, a "list" data structure is constructed and stored in memory when the data cards are read. Instead of the Karnaugh map, a subroutine processes the list using a version of the Quine-McCluskey minimization algorithm. The minimal expressions  $(J_A \text{ and } K_A \text{ for FFA, etc.})$  are then printed out.

To illustrate the equation generation process, a control logic function will be synthesized by going through steps (1) to (3) manually. The results are then compared with the CAD program's output.

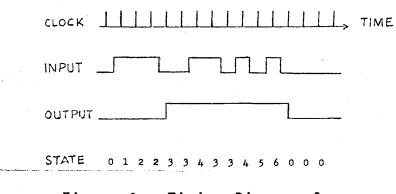

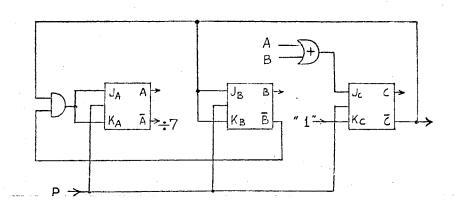

The control logic function (Synchronization Indicator) is specified by the timing diagram shown in Figure 1. The diagram defines the behavior of the function's output for the

Figure 1. Timing Diagram for Synchronization Indicator Logic. Input = X Output = F1

(FI= OUTP UT )

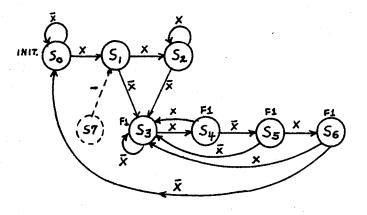

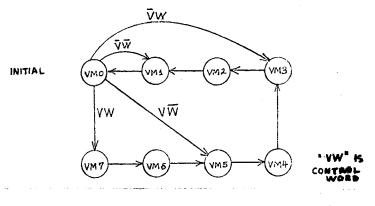

Figure 2. State Diagram of Synchronization Indicator

input signal given. Either a state diagram is drawn from a flow table derived from Figure 1, or made directly without benefit of formal state minimization techniques.

Figure 2 shows a state diagram for the Synchronization Indicator having seven states and an optional state, S7. The label F1 on nodes S3 through S6 indicates that the output is true when the present state is in any of these nodes.

The state transition table for FFA, Table I, was constructed from the state diagram after making the state assignment:

| S0  | S1  | S2  | S 3 | S 4 | S 5 | S6  | S 7 |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 000 | 110 | 101 | 100 | 011 | 010 | 001 | 111 |

In Table I, the entries NC(0) and NC(1) in the Action Desired column mean "no change, state 0" and "no change, state 1" respectively. The table gives the values required for inputs J,K to cause the actions <u>set</u>, <u>reset</u>, <u>NC(0)</u>, and <u>NC(1)</u> to occur during the next clock period. For example in the first row of the table, the next state of FFA is given as <u>1</u> when X = 1. Hence FFA must be set and this requires J = 1 and K = d, where d denotes <u>don't care</u>.

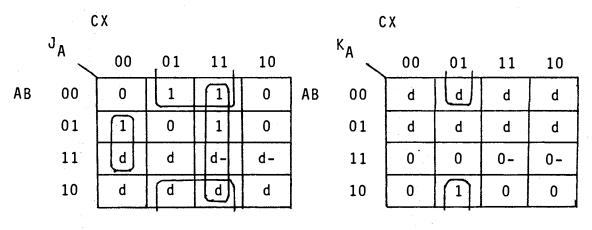

In Figure 3 the Karnaugh maps for  $J_A$  and  $K_A$  are depicted. These maps were constructed by treating Table I as a table of combinations for the present state and input X. For example, cell 0100 of the maps contain the entries 1, d respectively. These were taken from row 3 of Table I with X = 0 columns indicating set A is the desired action.

| Present State | Next Sta     | te (FFA)     | Action                     | Desired*     |

|---------------|--------------|--------------|----------------------------|--------------|

| FFA FFB FFC   | <u>X = 0</u> | <u>X = 1</u> | $\underline{X} = 0$        | <u>X = 1</u> |

| 000           | 0            | 1            | NC(0)                      | Set          |

| 001           | 0            | 1            | NC(0)                      | Set          |

| 010           | 1            | 0            | Set                        | NC(0)        |

| 011           | 0            | 1            | NC(0)                      | Set          |

| 100           | 1            | 0            | NC(1)                      | Reset        |

| 101           | 1            | 1            | NC(1)                      | NÇ(1)        |

| 110           | 1            | 1            | NC(1)                      | NC(1)        |

| 111           | 1            | 1            | NC(1)                      | NC(1)        |

| * Set ⇒       | J = 1, K     | = d          | $NC(0) \Rightarrow J = 0,$ | K = d        |

| Reset ⇒       | J = d, K     | = 1          | $NC(1) \Rightarrow J = d,$ | K = 0        |

## TABLE I

STATE TRANSITION TABLE FOR FFA OF SYNCHRONIZATION INDICATOR

Figure 3. Karnaugh Maps for FFA of Synchronization Indicator

The minimal expressions derived from the loops of the  $J_{\rm A},\ {\rm K}_{\rm A}$  maps are:

$$J_{A} = B\bar{C}\bar{X} + \bar{B}X + CX$$

$$\kappa_{A} = \bar{B}\bar{C}X$$

The CAD program when given the same state diagram and state assignment generates exactly the same equations for  $J_A$  and  $K_A$ . These equations as well as those for the two other FF's required are shown in the computer printouts of Appendix A. Note that the minterms comprising a loop are also displayed.

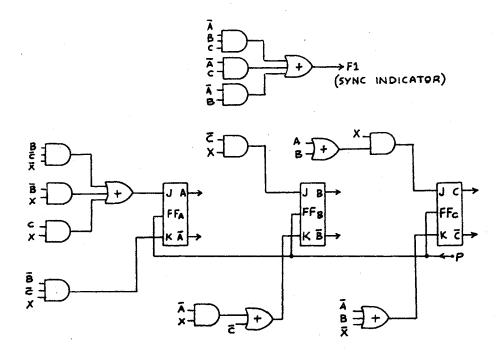

The equations for FFB and FFC are:

$$J_{B} = \bar{c} X$$

$$K_{B} = \bar{A} X + \bar{c}$$

and

$$J_{C} = AX + BX$$

$$K_{C} = \overline{X} + \overline{A} + B$$

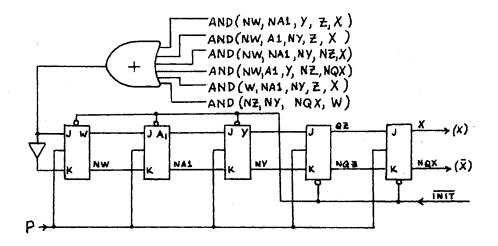

The foregoing equations are depicted in logic schematic form in Figure 4.

The output gating in Figure 4 was obtained by making a truth table of the output function (F1) from the timing diagram and minimizing it with another CAD program. This completed the design of the Synchronizer Indicator.

Referring again to Figure 3, cells 1111 and 1110 of both maps contain dashes, d's, and O's. The dashes are <u>don't care</u> entries which apply when the unspecified state S7 is ignored.

Figure 4. Synchronization Indicator Logic Drawn from Equations Generated by CAD Programs

The d's and O's apply when S7 is assigned binary code 111. Although the expressions generated are the same in either case, they may be different from each other for other state assignments. State assignment and output gating will be discussed further in later sections.

## Flow Table Reduction and State Assignment

Taking into account that the present set of CAD programs do not perform flow table reduction and state assignment, the following guidelines are suggested.

<u>Flow Table Reduction</u>. Manually process a primitive flow table using a method intended for the type of table. Procedures for reducing the number of rows have been detailed by Givone [5] for completely specified, incompletely specified, and input restricted types.

<u>State Assignment</u>. An algorithm is described in a recent paper by Story, Harrison, and Reinhard [6]. This and other methods known to the designer may be used to produce a number of state assignments for each problem. Since it is a simple matter to input these data to the CAD program, all these trials may be submitted in each run. The best solution (fewest number of input terms and/or number of gates) is then selected from the printouts.

Many papers have appeared in the literature proposing schemes for flow table reduction and optimal state assignment. These methods seem to have one or more problems such as incompatibility with don't care conditions, tedious to apply, not appropriate for synchronous logic, and use of a heuristic approach rather than algorithmic.

From the viewpoint of CAD program implementation, it is important that a procedure be definable as an algorithm. Experience has shown that a heuristic method sometimes defies conversion into a program having reasonable memory and running time requirements.

## Verification by Simulation

As an approach to the problem of verification of a logic design, simulation at the gate/FF level is gaining acceptance. Like most CAD tools it is appreciated most when the design to be verified exceeds a few dozen gates and FF's. This is due to the fact that program setup time for the simulation becomes significantly less than the cost of a comparable breadboarding effort. Verifying designs with a good simulator (one which can include effects of gate delays and detect violations of loading rules) permits prototyping with confidence. Hence the need for prototype "kluges" is minimized.

The simulator program employed in this study goes by the trade name of LOGSIM. Literature on its capabilities and an application manual are obtainable from Tymeshare, Inc. [7].

The maximum allowable number of gate-equivalents per simulation is 300, each JKFF being equivalent to 7-10 gates (depending on the particular commercial type). For example, for a network containing 20 JKFF's, 140-200 gates would be allocated for modelling the JKFF's leaving 100-160 gates to be used as gates or inverters. Other simulators have comparable characteristics and may be rated as to availability of gate delay and other modelling features, editing and file saving facilities, and run time and memory requirements.

Table II indicates the coding format and language used for LOGSIM. The circuit modelled by the statements is an 18-gate version of the Synchronization Indicator which resulted from one of several state assignments tried.

The first three lines of Table II describe the flipflops used in the circuit. For example, the significance of the symbols in line 1,

1 JK (2, QA, NA, JA, KA, P, O, O ) taken from left to right is: This statement is from card number 1 of the network's LOGSIM model. A JKFF is specified. There are two outputs, QA and NA. The synchronous inputs are JA, KA, and P. The initial condition for the asynchronous inputs (direct set and direct reset) are O, O, respectively.

Lines 4 through 21 specify AND, OR, and inverter gates and the way they are connected. Line 5 is read "KA is the output of an OR gate whose inputs are A5 and A2." AND gate and inverter declarations are read similarly.

The clock pulse source, P, is declared in line 23. This clock is "connected" to any component where the name P is declared as an input. That is, the node associated with

## TABLE II

# LOGIC SIMULATOR INPUT CODING FOR SYNCHRONIZATION INDICATOR

| and the second | 1. A. |                  |                                       |   |

|------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------|---------------------------------------|---|

| 1 JK(2,QA,NA, JA,KA,P,0,0)                                                                                       |                                           |                  | •                                     |   |

| 2 JK (2, QB, NB, JB, KB, P, 0, 0)                                                                                |                                           |                  |                                       |   |

| 3 JK(2,QC,NC, JC,KC,P,0,0)                                                                                       |                                           |                  |                                       |   |

| 4 JA=OR(AN1,A2,A3,A4)                                                                                            |                                           |                  |                                       |   |

|                                                                                                                  | · · · · · · · · · · · · · · · · · · ·     |                  |                                       |   |

| 5 KA= $OR(A5,A2)$                                                                                                |                                           |                  |                                       |   |

| 6  AN1 = AND(QB, NC, NX)                                                                                         |                                           |                  |                                       |   |

| 7 A2 = AND(NB, X)                                                                                                |                                           |                  |                                       |   |

| 8 A3=AND(NA,QC)                                                                                                  |                                           |                  |                                       |   |

| 9 A4=AND(QC,X)                                                                                                   |                                           | - · ·            | •                                     |   |

| 10 A5=AND(NC,X)                                                                                                  |                                           |                  |                                       |   |

| 11 JB=OR(A6,QA)                                                                                                  |                                           |                  |                                       |   |

| 12 KB=OR(A7,A8)                                                                                                  |                                           |                  |                                       |   |

| 13 AG=AND(OC,X)                                                                                                  |                                           |                  |                                       |   |

| 14 A7=AND(QA,NC,X)                                                                                               |                                           |                  |                                       |   |

| 15 AB=AND(NA, QC, NX)                                                                                            |                                           |                  |                                       |   |

| 16 JC=AND(QA, QB, X)                                                                                             |                                           |                  |                                       |   |

|                                                                                                                  | •                                         |                  |                                       |   |

| 17 KC=OR(A10,A11,A12)                                                                                            |                                           |                  |                                       | • |

| 18 A10=AND(QA,NB,NX)                                                                                             |                                           |                  |                                       |   |

| 19 All=AND( $NA$ , X)                                                                                            |                                           |                  |                                       |   |

| 20  A12=AND (NA,QB)                                                                                              |                                           |                  |                                       |   |

| 21 NX=INVERT(X)                                                                                                  |                                           |                  |                                       |   |

| 23 P=A(PULSE)                                                                                                    |                                           |                  |                                       |   |

| 25 F1=OR(A13,A14,A15)                                                                                            |                                           |                  |                                       |   |

| 26 A13=AND(NA,QC)                                                                                                |                                           |                  |                                       |   |

| 27 A14=AND(QA, QB, NC)                                                                                           |                                           |                  |                                       |   |

| 28 A15=AND(NH,QC)                                                                                                |                                           |                  |                                       |   |

| 29 JK(2,W, NW, JW,KW, P.0.0)                                                                                     |                                           |                  |                                       |   |

| 30 JK(2, A1, NA1, W, NW, P,0,0)                                                                                  |                                           |                  |                                       |   |

| 31 JK(2,0Z,NZ, Y, NY, P,0,0)                                                                                     |                                           |                  |                                       |   |

|                                                                                                                  |                                           |                  |                                       |   |

| 32 JK(2, Y,NY, A1,NA1,P,0,0)                                                                                     |                                           |                  |                                       |   |

| 33 JK(2, X,NQX,QZ,NZ, P,0,0)                                                                                     |                                           |                  |                                       |   |

| 34 KW=INVERT(JW)                                                                                                 |                                           |                  |                                       |   |

| 35 JW=UR (A20, A21, A22, A23, A24, A2                                                                            | 25)                                       |                  |                                       |   |

| 36 A20=AND(NW,NA1,Y,QZ,X)                                                                                        |                                           |                  |                                       |   |

| 37 A21=AND(NW,A1,NY,QZ,X)                                                                                        |                                           |                  |                                       |   |

| 38 A22=AND(NW,NA1,NY,NZ,X)                                                                                       |                                           |                  |                                       |   |

| 39 A23=AND(NW,A1,Y,NZ,NQX)                                                                                       |                                           |                  |                                       |   |

| 40 A24= AND(H, NA1, NY, QZ, X)                                                                                   |                                           |                  |                                       |   |

| 41 A25=AND1W, NQX, NY, NZ)                                                                                       |                                           |                  |                                       |   |

|                                                                                                                  | ACT OC OD O                               |                  |                                       |   |

|                                                                                                                  | AS194094094                               | A . ASI . JA. KA | • AS 1                                |   |

| OUTPUTS J3,KB,AST,JC,KC,AST,F1                                                                                   | L . A S I                                 |                  |                                       |   |

| OUTPUTS AST, W, AL, Y, QZ, X, AST, AS                                                                            | 51,A20,A21,A                              | 22,A23,A24,      | A25                                   |   |

| END                                                                                                              |                                           |                  |                                       |   |

|                                                                                                                  |                                           |                  |                                       |   |

| - SIMULATION COM                                                                                                 |                                           |                  |                                       |   |

| STRUCATION COMI                                                                                                  | MANDD                                     | A T A P          | AGE 1                                 |   |

|                                                                                                                  |                                           |                  |                                       |   |

|                                                                                                                  |                                           |                  |                                       |   |

|                                                                                                                  |                                           | · · · ·          | · · · · · · · · · · · · · · · · · · · |   |

| 1 CLOCKED 'SYNCHRONIZER' USING .                                                                                 | J-K FFS ICA                               | D SOL N          |                                       |   |

| PULSE 150.0                                                                                                      | •                                         | -                |                                       |   |

|                                                                                                                  |                                           |                  |                                       |   |

| END                                                                                                              |                                           |                  |                                       |   |

a literal is connected to any component declaring it as an input signal, assuming of course that the format rules exemplified by the JKFF example are observed.

Lines 29-41 model a shift register which simulates the X-input sequence needed to test the design. It is not part of the logic function being verified.

"Housekeeping" statements which specify outputs to be printed out, the title heading, and number of clock pulses to be generated comprise the rest of the simulation input program.

When the program of Table II is executed, the printout prepared by the LOGSIM simulator is shown in Table III. The left-most heading, TEST, denotes row or line number. The heading P identifies the column used for the clock pulses. Similarly QC, QB, QA, ..., A25 are for FF's and gates specified by the user. The output values are printed alternately for P = 0 and P = 1 in Table III. The JKFF's are shown to change state after a 1-0 transition.

In the present example, Table III shows that the output F1 followed the timing diagram of Figure 1. Note also that the shift register (see columns W through X) produced the input signal sequence specified in the timing diagram. Thus the simulated circuit (or model) driven by a test pattern generated a printout from which the designer can infer that the logic specification was met.

## TABLE III

# PRINTOUT FROM LOGIC SIMULATOR PROGRAM

|   |          |          | CLOCKED                 | I S YN     | СНЕ      |    | I ZEP  | Į •    | USIN     | IG | J-K           | FFS .                 |

|---|----------|----------|-------------------------|------------|----------|----|--------|--------|----------|----|---------------|-----------------------|

| Ť | EST      | INPUT ID | Ρ                       | QQQ<br>CBA | JK<br>AA |    | -      | F<br>1 | WAY<br>1 |    | 22            | AAAA<br>22222<br>2345 |

|   |          |          |                         |            |          |    |        |        |          |    |               |                       |

|   | 1<br>2   |          | **()**<br>**1**         |            |          |    |        |        |          |    |               |                       |

|   | 3        |          | **()**                  |            |          |    |        |        |          |    |               |                       |

|   | 4        |          | **]**                   | 001        | 11       | 11 | + 00 × | •0*    | *011     | 11 | * <b>*</b> 00 | 00000                 |

|   | 5        | · · · ·  | **0**                   | -          |          |    |        |        |          |    |               |                       |

|   | 6        |          | **1**<br>**0**          | -          |          |    | -      | -      | -        |    |               |                       |

|   | 7<br>8   |          | **0**                   |            |          |    |        |        |          |    |               |                       |

|   | 9        |          | **0**                   |            |          |    |        |        |          |    |               |                       |

|   | 10       |          | **1**                   |            |          |    |        |        |          |    |               |                       |

|   | 11       |          | **0**                   |            |          |    |        |        |          |    |               |                       |

|   | 12       |          | **1**                   |            |          |    |        | -      |          |    |               |                       |

|   | 13<br>14 |          | **()**<br>**1**         |            |          |    |        |        |          |    |               |                       |

|   | 15       |          | **0**                   |            |          |    |        |        |          |    |               |                       |

|   | 16       |          | **1**                   |            |          |    |        |        |          |    |               |                       |

|   | 17       |          | **()≍*                  |            |          | _  | _      |        |          |    |               |                       |

|   | 18       |          | **1=*                   |            |          |    |        |        |          |    |               |                       |

|   | 19       |          | **0**                   |            |          |    |        |        |          |    |               |                       |

|   | 20       |          | ± ≠ 1 <b>*</b> ×        | _          |          |    |        | _      | -        |    |               |                       |

|   | 21<br>22 |          | **()**<br>**1**         |            |          |    |        | -      |          |    |               |                       |

|   | 27       |          | **()**                  |            |          |    | -      | -      |          |    |               |                       |

|   | 24       |          | **1=1                   |            |          |    |        |        |          |    |               |                       |

|   | 25       |          | **()**                  |            |          |    |        | -      |          | -  |               |                       |

|   | 26       |          | **1**                   |            |          |    |        |        |          |    |               |                       |

|   | 27       |          | **0**                   | -          |          |    |        | -      | -        |    |               | -                     |

|   | 28<br>29 |          | ≠≠1≈5<br>≠≠0≈1          |            |          | -  |        |        |          |    |               |                       |

|   | 30       |          | **1**                   |            |          |    |        |        | _        |    |               |                       |

|   | 31       |          | **() <b>*</b> ≭         |            |          |    |        |        |          |    |               | -                     |

|   | 32       |          | **1**                   |            |          |    |        | -      |          |    |               |                       |

|   | 33       |          | ×*()**                  |            |          |    |        |        |          | _  |               |                       |

|   | 34       |          | <b>≠ ≈</b> ] <b>*</b> 4 |            |          |    |        |        |          | -  |               |                       |

|   | 35<br>36 |          | >×()××<br>≈×1×1         |            |          |    |        | -      |          |    |               |                       |

|   | 31       |          | **0**                   |            |          |    |        |        |          | -  |               |                       |

|   | 39       |          | **1**                   |            |          |    |        |        |          |    |               |                       |

|   | 39       |          | **()* <b>*</b>          | 010*       | 01*      | 00 | ×01*   | •0*    | *110     | 01 | **00          | 0000                  |

|   | 40       |          | ×≠1××                   |            | -        |    | -      |        |          | -  |               |                       |

|   | 41       |          | **0**                   |            |          |    |        | -      |          |    |               |                       |

|   | 42<br>43 |          | **1**<br>**()**         |            |          |    |        |        |          |    |               |                       |

|   | 44       |          | ×.≠()×.≠<br>≍.≭].≭¤     |            | -        | -  | -      | -      |          | -  |               |                       |

|   | 45       |          | **()**                  |            |          |    |        |        |          |    |               |                       |

|   |          |          |                         |            | -        | -  |        |        | -        |    |               |                       |

|   |          |          |                         |            |          |    |        |        |          |    |               |                       |

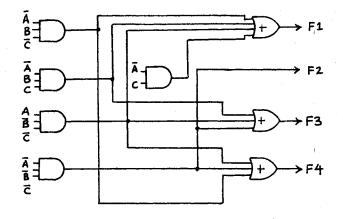

# Gate Level CAD: Minimization of Output Gating

To obtain the minimized expression to be used for an output gating circuit, punched cards representing its truth table are input to LOGICMIN. This program is external to the Synchronous Logic Synthesis Program. These two programs were separated since some modification of the minimization algorithm and different printout formats were desired in each case. LOGICMIN may be used for any combinational switching function provided its truth table has no more than 1024 rows and 32 literals.

#### Single-Output Functions

The algorithm used here is the well known Quine-McCluskey method which initially determines the prime implicants of a given function. The method then finds a set of irredundant expressions from which minimal expressions are formed. A hazard-free minimal sum is also computed for possible use with the asynchronous (direct set/reset) inputs of JKFF's.

## Multiple-Output Functions

For this type of gating an extension of the Quine-McCluskey method described by Givone [8] was used in LOGICMIN. The extension amounts to employing the original algorithm to process tagged product terms and using a mask (AND type) operation on the tags. LOGICMIN computes several candidate solutions for each truth table. One set of solutions tends to optimize cost with respect to the number of input lines and gates. A second set has a different criterion namely that of using smaller (2-input or 3-input) gates rather than larger gates.

To aid the user in drawing the logic schematic from the minimized gating expressions, cross-reference tables, printplots, and binary code labels are included in the printout of results.

#### Non-Digital Aspects

## Spectral Analysis with FFT

The FFT is an efficient method of computing the discrete Fourier transform. Basore [9] has prepared a monograph explaining this computational short-cut.

For CAD programming if the FFT is included in a computer library of subroutines, then it is simply called by the user's program. The version used in this study was written in Fortran and invoked by a statement of the form

CALL COOL (N, ARRAY, -1)

where N specifies the number of samples, ARRAY is the name of an array dimensioned as two rows and N columns, and -1 signifies the direct transform (+1 would specify inverse). ARRAY stores the real and imaginary components computed by the subroutine. The user's program typically provides for the reading in of the sampled data, subsequent conversion of the spectral components into db, and tabulation of results.

## Filter Design

An analog filter synthesis program available through remote terminals was used in designing the low-pass filter specified in Chapter III. The program, designated MATCH by the Applicon Company [10], employs the conjugate gradient approach for optimization.

## Methodology

The CAD procedure suggested for systems consists of seven steps one or more of which may be optional. The choice of which step to by-pass and how many iterations to perform depends on the user's judgement.

(1) Convert the block diagram and timing chart of a system into a register transfer description for input to the simulator program. Reconfigure and simulate again as necessary to refine and simplify the design.

(2) Determine the standard and non-standard building blocks of the system developed in the first step.

For each non-standard block do steps (3) to (7).

(3) Input the state diagram data of a non-standard function to the Synchronous Logic Synthesis Program.

(4) Input to LOGICMIN the truth table of the output gating function.

(5) Draw the schematic for the equations generated in step (3). Label the JKFF terminals to correspond with the state assignment used. Select one of the equations obtained in step (4) and draw its schematic.

(6) Interconnect the output gating from step (5) to the JKFF's.

(7) Verify the complete schematic of the non-standard function by gate level simulation.

Following completion of the above, prototype hardware may be assembled from off-the-shelf items and from the nonstandard functions designed with the procedure.

It is assumed that previous to step (1), non-digital aspects involving filters and related interface circuitry had been dealt with. As noted, CAD programs are commercially available for this portion of the design task.

## CHAPTER III

## SYSTEM LEVEL DESIGN

A new approach which competes favorably with analog techniques in the area of very stable frequency generation is described and used as a design example. The method computes a sequence of sinusoid samples with a simple table look-up scheme followed by interpolation by means of a low pass filter. Table look-up is practical since the number of samples is small, and low-cost read only memory (ROM) used to store the samples is now available. The technique is simpler than digital recursion and produces less noise [11].

The process generates a time series of sine wave samples represented by the expression

$\{\sin 2\pi fnT\}$  n = 0, 1, 2, ...

where f = frequency to be generated, n = time index, and T = sampling interval.

The lowest frequency,  $f_{lo}$  is synthesized when the total number of samples stored in the table, N, are used in each period. This is depicted in Figure 5a with N = 16. For a given T,

$$f_{10} = 1/NT.$$

b.) Time Series for 3f<sub>lo</sub>

Figure 5. Plot of Time Series of Samples Obtained from Read Only Memory

To select a frequency we provide a frequency index k such that

and the time series expression may be written

$\{\sin(2\pi nk/N)\}$   $k \le N/4; n = 0, 1, 2, ...$

The above indicates that the generated frequency can be set by index k. Due to the Nyquist condition, and for ease of filtering, the highest frequency is constrained to  $f = (N/4)f_{10}$ .

Figure 5b shows the sequence of samples corresponding to k = 3. It also shows that after the third cycle the sequence repeats. This implies that as n increases, the product nk is treated modulo N. The generation of time series therefore involves accumulating multiples of k. In terms of the table look-up scheme, accumulated values of k are used as memory addresses and no other computations are needed.

Digital Frequency Synthesizer Specification

Being a case study in system level design pertinent characteristics of the synthesizer are specified as analog and digital. The <u>analog</u> specifications are: (1) number of frequencies = 32; (2) lowest frequency = 1 Hz; (3) maximum in-band noise referred to a generated frequency = -40 db; (4) low pass filter transition band is from 32 to 64 Hz with out-of-band attenuation of 80 db. (See Figure 6). The

Figure 6. Characteristics of Low Pass Filter

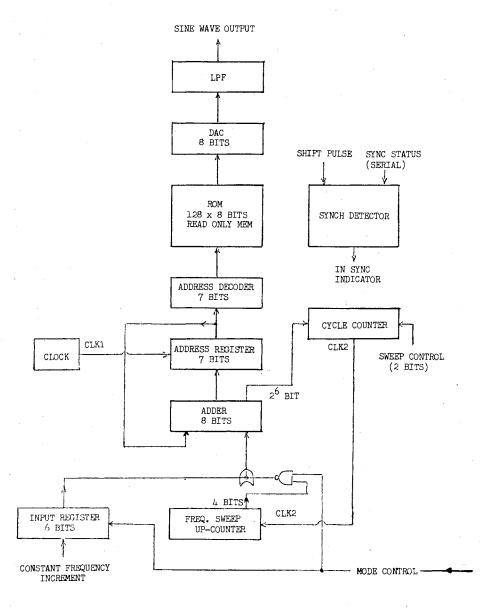

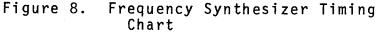

<u>digital</u> portion of the design specification follows. Binary arithmetic is to be used in implementing the block diagram of Figure 7. There are two modes of frequency selection: fixed and sweep. Provide a synchronizer indicator function. The timing charts of Figure 8 and Figure 9 are part of the specification.

In Figure 7 the accumulation process for index k described earlier is done by an accumulator which consists of an address register that feeds back to an adder. The input register holds the value of the control word corresponding to index k for generating a constant frequency. Similarly, the frequency sweep up-counter serves as an

Figure 7. Block Diagram of Frequency Synthesizer

Figure 9.

9. Timing Diagram for Sweep Mode, Initial f = 32f<sub>lo</sub> and Sweep Control set for 14 Cycles

input register except it increments the frequency during the sweep mode.

The table look-up operation is performed by the ROM and accumulator. The digital to analog converter DAC changes the binary coded samples into analog voltages which are then interpolated by the filter LPF. The sampling interval is determined by the clock CLK1 since the address decoder gets the next address after each CLK1 pulse. The box labelled "synch detector" has a logic function which determines if an external pulse train is in synchronism with CLK2.

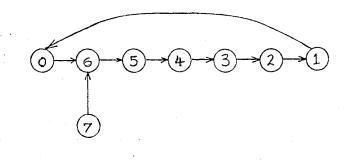

The cycle counter in Figure 7 controls how long a frequency stays fixed during the sweep mode. It contains a  $\div$  7 counter in series with a variable-modulo counter ( $\div$  2, 4, 6, 8 depending on sweep control word). Hence CLK2 pulses are derived from transitions of the 2<sup>6</sup> bit of the adder divided by 14, 28, 42, or 56. In turn, the frequency sweep up-counter supplies k index values 7, 8, 9, 10, 11, 7, .... Since CLK2 drives this counter, the output frequency will be 7f<sub>10</sub>, 8f<sub>10</sub>, .... and will remain fixed for 14, 28, 42, or 56 cycles before changing (sweep mode only).

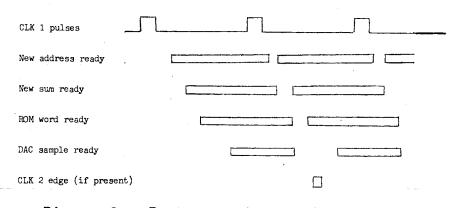

Figure 8 gives the timing relationship between the operations which occur in the Frequency Synthesizer. After each CLK1 pulse enables the address register a new address is loaded into the address decoder. The next sum is ready after a slight delay needed for adding the k index and the

present sum. The time allowed for reading out the ROM and for analog conversion must be short enough so that the analog sample is ready before the next CLK1 pulse.

Some details of fixed and sweep mode operation are depicted in Figure 9. Initially the fixed mode applies, and the selected frequency is assumed to be  $32f_{10}$ . The diagram shows that the 2<sup>6</sup> sum bit indicates overflow after every four samples. The address values are shown to be 0, 32, 64, 96, 0, .... (modulo 128). Because the sweep control is set to permit 14 cycles to be generated, CLK2 is shown to fall after 56 CLK1 pulses. The figure also assumes that the sweep mode was selected at this time, and that the sweep register (or sweep up-counter) was enabled to the adder when it contained the value 7.

The ROM used for storing the sine wave samples is described in Figure 7 as having  $128 \times 8$  bit words. This means that the number of words, N, is double that required by the Nyquist criterion for a maximum frequency of 32 Hz. The 8-bit word size was obtained by taking the worst case error as being equal to the least significant bit. This gives for an 8-bit word (7 bits magnitude plus sign) 20 log 2<sup>-7</sup> or -42 db. This is less than the -40 db specification for in-band noise. The 8-bit word length will be validated later by means of the FFT.

Only 7 bits of the adder in Figure 7 are connected to the address register. That is, the sum bits 2° to 2<sup>6</sup> are used thereby converting the accumulated k index values modulo 128.

# Effects of Truncation and Sampling Errors on Memory Word Length

Determining the correct word length is important since too small a word could result in failing to meet the noise specification due to truncation (round off) effects. Too large a word causes extra power dissipated due to unnecessarily large registers and adders. Further, ROM modules are relatively expensive due to the additional process of "programming" the values to be stored into the module. Hence a change of word size means that a completely new ROM must be programmed.

The effect of word size on spectral purity was studied empirically by using the FFT to compute spectra of samples having different word lengths. For simplicity it was assumed that the synthesizer had a total of 16 samples and that word lengths can be adjusted to 4, 7, and 31 bits.

The results from a 32-point transform are shown in Table IV for 7-bit and 31-bit samples. The 31-bit case was called non-truncated since this is the full word size for single-precision arithmetic. Only the positive 16 samples are shown. The table is for the case when the lowest frequency,  $f_{10}$  was selected.

Table V presents the data of Table IV in db referred to  $f_{10}$ . Additional data for the 4-bit case were included. Similarly, Tables VI and VII give the results for  $5f_{10}$  and  $6f_{10}$  respectively.

# TABLE IV

# PRINTOUT FROM FFT PROGRAM AFTER PROCESSING THIRTY TWO SAMPLES OF NON-TRUNCATED DATA (TOP) AND SEVEN BIT DATA (BOTTOM)

| LINE NO.                                                               | MAGNITUDE                                                                                                                                       | SAMPLED DATA                                                                                                                                                                                     |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                                                                      | 0.4192E-06                                                                                                                                      | 0.0                                                                                                                                                                                              |

| 1                                                                      | 0.4976E 00                                                                                                                                      | 0.0                                                                                                                                                                                              |

| 2<br>3                                                                 | 0.7764E-06                                                                                                                                      | 0.3826830                                                                                                                                                                                        |

|                                                                        | 0.4079E-06                                                                                                                                      | 0.3826830                                                                                                                                                                                        |

| 4                                                                      | 0.3128E-06                                                                                                                                      | 0.7071062                                                                                                                                                                                        |

| 5                                                                      | 0.2016E-06                                                                                                                                      | 0.7071062                                                                                                                                                                                        |

| 6                                                                      | 0.2020E-06                                                                                                                                      | 0.9238790                                                                                                                                                                                        |

| 7                                                                      | 0.4142E-06                                                                                                                                      | 0.9238790                                                                                                                                                                                        |

| · <b>B</b>                                                             | 0.1489E-06                                                                                                                                      | 1.000000                                                                                                                                                                                         |

| 9                                                                      | 0.2300E-06                                                                                                                                      | 1.0000000                                                                                                                                                                                        |

| 10                                                                     | 0.1350E-06                                                                                                                                      | 0.9238603                                                                                                                                                                                        |

| 11                                                                     | 0.1661E-06                                                                                                                                      | 0.9238803                                                                                                                                                                                        |

| 12                                                                     | 0.1296E-06                                                                                                                                      | 0.7071087                                                                                                                                                                                        |

| 13                                                                     | 0.9045E-07                                                                                                                                      | 0.7071087                                                                                                                                                                                        |

| 14                                                                     | 0.1544E-06                                                                                                                                      | 0.3826867                                                                                                                                                                                        |

| 15                                                                     | 0.4901E-01                                                                                                                                      | 0.3826867                                                                                                                                                                                        |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13 | 0.0<br>0.4968E 00<br>0.0<br>0.1795E-02<br>0.0<br>0.1263E-02<br>0.0<br>0.1169E-03<br>0.0<br>0.9601E-04<br>0.0<br>0.6750E-03<br>0.0<br>0.5444E-03 | 0.0<br>0.0<br>0.3828125<br>0.3828125<br>0.7109375<br>0.7109375<br>0.9218750<br>0.9218750<br>0.9921875<br>0.9218750<br>0.9218750<br>0.9218750<br>0.9218750<br>0.9218750<br>0.7109375<br>0.7109375 |

| 14                                                                     | 0.0                                                                                                                                             | 0.3828125                                                                                                                                                                                        |

| 15                                                                     | 0.4894E-01                                                                                                                                      | 0.3828125                                                                                                                                                                                        |

|                                                                        |                                                                                                                                                 |                                                                                                                                                                                                  |

#### TABLE V

# SPECTRAL ANALYSIS USING FFT FOR TRUNCATED AND NON-TRUNCATED SAMPLES CASE I SYNTHESIZER SET TO LOWEST FREQUENCY

| larmonic*       | No Truncation |                                   | 7-bit Samples |                                   | 4-bit Samples |                                   |

|-----------------|---------------|-----------------------------------|---------------|-----------------------------------|---------------|-----------------------------------|

|                 | Magnitude     | H <sub>1</sub> /H <sub>n</sub> db | Magnitude     | H <sub>1</sub> /H <sub>n</sub> db | Magnitude     | H <sub>1</sub> /H <sub>n</sub> db |

| H <sub>1</sub>  | 0.4976        | 0.0                               | 0.4968        | 0.0                               | 0.475         | 0.0                               |

| Н <sub>з</sub>  | 0.4079E-6     | 121.7                             | 0.1795E-2     | 48.8                              | 0.696E-2      | 36.7                              |

| H <sub>5</sub>  | 0.2016E-6     | 127.8                             | 0.1263E-2     | 51.9                              | 0.130E-2      | 51.3                              |

| H <sub>7</sub>  | 0.4142E-6     | 121.6                             | 0.1169E-3     | 72.6                              | 0.694E-3      | 56.7                              |

| Н <sub>е</sub>  | 0.2300E-6     | 126.7                             | 0.9601E-4     | 74.3                              | 0.569E-3      | 58.4                              |

| H <sub>11</sub> | 0.1661E-6     | 129.5                             | 0.6750E-3     | 57.3                              | 0.693E-3      | 56.7                              |

| H <sub>l3</sub> | 0.9045E-7     | 134.8                             | 0.5444E-3     | 59.2                              | 0.211E-2      | 47.0                              |

| H <sub>15</sub> | 0.4901E-1     | 20.1                              | 0.4894E-1     | 20.1                              | 0.467E-1      | 20.1                              |

\*  $H_1 = f_{10}$ .

$f_{10}$  . The zero and even order harmonics vanish for truncated data and less than  $10^{-5}$  for non-truncated data.

ω

# TABLE VI

# SPECTRAL ANALYSIS USING FFT FOR TRUNCATED AND NON-TRUNCATED SAMPLES CASE II SYNTHESIZER SET TO FIVE TIMES LOWEST FREQUENCY

| larmonic*       | No Truncation |                      | 7-bit Samples |                      | 4-bit Samples |                      |

|-----------------|---------------|----------------------|---------------|----------------------|---------------|----------------------|

|                 | Magnitude     | H₅/H <sub>n</sub> db | Magnitude     | H₅/H <sub>n</sub> db | Magnitude     | H₅/H <sub>n</sub> db |

| H <sub>1</sub>  | 0.240E-6      | 125.3                | 0.187E-2      | 47.4                 | 0.724E-2      | 35.3                 |

| H <sub>3</sub>  | 0.532E-6      | 118.4                | 0.145E-3      | 69.6                 | 0.859E-3      | 53.8                 |

| H <sub>5</sub>  | 0.441         | 0.0                  | 0.440         | 0.0                  | 0.421         | 0.0                  |

| H <sub>7</sub>  | 0.272E-6      | 124.2                | 0.111E-2      | 52.0                 | 0.114E-2      | 51.3                 |

| Н <sub>э</sub>  | 0.182E-6      | 127.7                | 0.909E-3      | 53.7                 | 0.933E-3      | 53.1                 |

| H <sub>11</sub> | 0.236         | 5.4                  | 0.235         | 5.4                  | 0.225         | 5.4                  |

| H <sub>13</sub> | 0.183E-7      | 147.6                | 0.439E-4      | 80.0                 | 0.260E-3      | 64.2                 |

| H <sub>15</sub> | 0.417E-7      | 140.5                | 0.184E-3      | 67.6                 | 0.713E-3      | 55.4                 |

$* H = f_{1}$

$f_{10}$  . The zero and even order harmonics vanish for truncated data and less than  $10^{-5}$  for non-truncated data.

# TABLE VII