# SIMULATION AND APL DESCRIPTION OF THE PDP 11/40

Вy

ANAND VARDHAN PANDIT

Bachelor of Engineering

Osmania University

Hyderabad, India

1973

Submitted to the Faculty of the Graduate College

of the Oklahoma State University

in partial fulfillment of the requirements

for the Degree of

MASTER OF SCIENCE

July, 1975

Thesis 1975 P1895 Cop. 2

.

.

.

• •

•

.

OCT 23 1975

# SIMULATION AND APL DESCRIPTION OF THE PDP 11/40

Thesis Approved:

Donald Fisher

Thesis Adviser

Maldu Grace

2. E. Hedrich

Dean of the Graduate College

#### PREFACE

This paper describes the implementation of an assembler-simulator for the PDP 11/40 computer. It is concerned with methods used to implement an assembler, to generate code which is interpretively executed by a simulator. Program-controlled input/output as well as device-initiated input, has been implemented. The assembler-simulator programs are written in PL/1, and are implemented on the IBM 360/65.

I would like to express my gratitude to my major adviser, Dr. Donald D. Fisher, for his advice and guidance during this project.

Also, appreciation is expressed to my other committee members,

Dr. Donald W. Grace and Dr. George E. Hedrick, for their suggestions and assistance in the preparation of this paper. Thanks are also due to Mrs. Debbie Williams for typing the paper.

## TABLE OF CONTENTS

| ${\tt Chapter}$ |                                                                                                                                                                                                                      | Page                                            |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| I.              | INTRODUCTION                                                                                                                                                                                                         | 1                                               |

| II.             | PDP 11/40 ARCHITECTURE                                                                                                                                                                                               | 6                                               |

|                 | System Organization. Unibus Operation.  Memory Organization.  Processor Status Word (PS)  Processor Stack.  Interrupt Structure.  Interrupt Service.  Addressive and Instruction Set.  Input/Output and Peripherals. | 6<br>7<br>9<br>10<br>12<br>14<br>16<br>18<br>22 |

| III.            | THE ASSEMBLER                                                                                                                                                                                                        | 24                                              |

|                 | Scanner. Table Construction and Processing. Pass I. Pass II. Assembler Directives. Error Detection and Handling. Assembler Output. Loader.                                                                           | 25<br>31<br>33<br>35<br>35<br>37<br>37<br>38    |

| IV.             | THE SIMULATOR                                                                                                                                                                                                        | 39                                              |

|                 | Instruction Fetch and Execution                                                                                                                                                                                      | 39<br>41<br>47<br>49<br>50                      |

| ٧.              | APL DESCRIPTION OF THE PDP 11/40                                                                                                                                                                                     | 51                                              |

|                 | The Processor                                                                                                                                                                                                        | 51<br>58<br>60<br>62<br>67                      |

| Chapter                            | Page           |

|------------------------------------|----------------|

| VI. USERS MANUAL                   | 86             |

| The Assembly Language              | 91<br>93<br>93 |

| VII. SUMMARY AND CONCLUSIONS       | 103            |

| BIBLIOGRAPHY                       | 105            |

| APPENDIX A - PROGRAM FLOWCHART     | 107            |

| APPENDIX B - SAMPLE PROGRAM OUTPUT | 114            |

| APPENDIX C - MACHINE OPCODE TABLE  | 128            |

## LIST OF TABLES

| Table |                                                     | Page |

|-------|-----------------------------------------------------|------|

| I.    | Condition Code Bits of the Processor Status Word    | 12   |

| II.   | The State Transition Matrix                         | 27   |

| III.  | Syntactical Categories and Associated States        | 30   |

| IV.   | PDP 11/40 Assembler Directives                      | 36   |

| ٧.    | Device Register and Interrupt Vector Addresses      | 43   |

| VI.   | Function of Reader Control and Status Register Bits | 45   |

| VII.  | Function of Punch Control and Status Register Bits  | 47   |

| VIII. | PROC Program Segments                               | 54   |

| IX.   | Instruction Classes                                 | 56   |

| х.    | The Navigation Matrix                               | 81   |

| XI.   | Error Codes and Messages                            | 99   |

# LIST OF FIGURES

| Figur | re ·                                                       | Page |

|-------|------------------------------------------------------------|------|

| 1.    | PDP 11 Word as Used in the System Manuals                  | . 4  |

| 2.    | A Word as Treated in the APL Description (Chapter V)       | 4    |

| 3.    | Basic System Organization                                  | 7    |

| 4.    | The Unibus System                                          | 8    |

| 5.    | The PDP 11 Word                                            | 10   |

| 6.    | Processor Status Word                                      | 11   |

| 7.    | Processor Stacks                                           | 13   |

| 8.    | Priority Interrupt Structure (11)                          | 15   |

| 9.    | Functional Description of Interrupt Control                | 17   |

| 10.   | Instruction Formats                                        | 19   |

| 11.   | Program Counter Modification in Branch Instructions        | 20   |

| 12.   | Peripheral Device Registers                                | 23   |

| 13.   | State Transition in a FSA                                  | 25   |

| 14.   | Finite State Automaton to Recognize Syntactical Categories | 28   |

| 15.   | Node Format in Operation Code Table                        | 31   |

| 16.   | Node Format in Address-Symbol Table                        | 32   |

| 17.   | Reader Device Registers                                    | 44   |

| 18.   | Punch Device Registers                                     | 46   |

| 19.   | Queue for Device-Initiated Interrupt Simulation            | 49   |

| 20.   | The Processor System Program                               | 52   |

| 21.   | Input/Output Interrupt Generator                           | 59   |

| Figur | re                            | Page |

|-------|-------------------------------|------|

| 22.   | Memory Access Operation       | 61   |

| 23.   | Address Computation Operation | 63   |

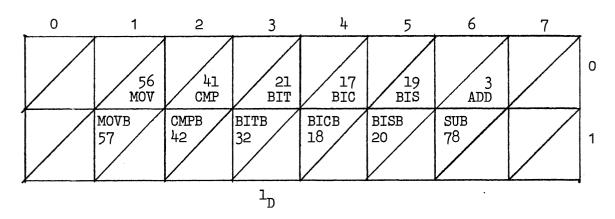

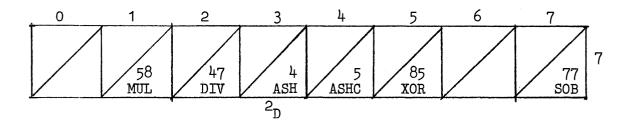

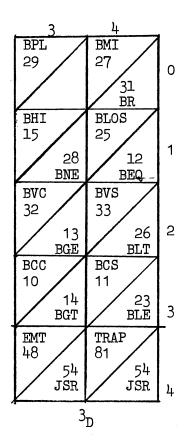

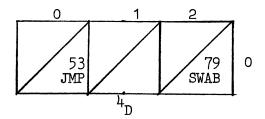

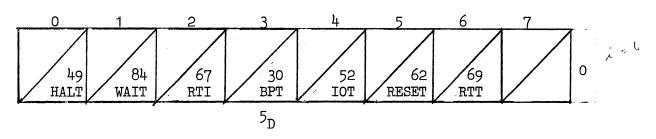

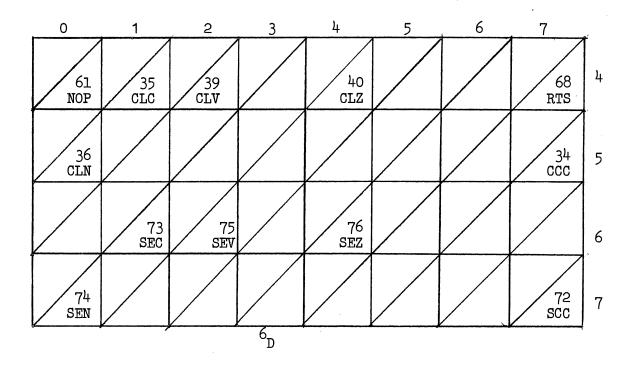

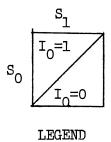

| 24.   | Instruction Decoding Matrices | 64   |

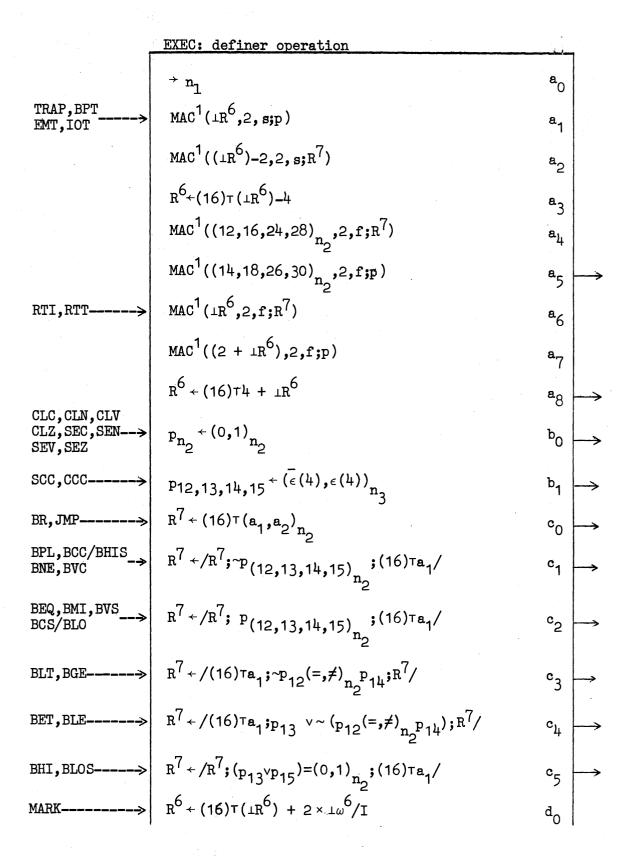

| 25.   | EXEC Routine                  | 68   |

| 26.   | The JOB Card                  | 93   |

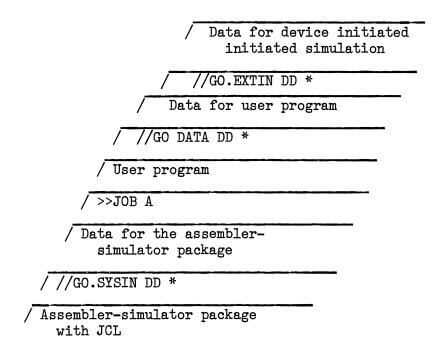

| 27.   | Deck Setup                    | 94   |

| 28.   | Program Setup                 | 95   |

## LIST OF SYMBOLS

| Symbol                          | Dimension          | Function                                |

|---------------------------------|--------------------|-----------------------------------------|

| ADC                             |                    | Address computation defined operation   |

| EXEC                            |                    | Instruction execution defined operation |

| IOIG                            |                    | I/O interrupt generator system program  |

| MAC                             |                    | Memory Access defined operation         |

| PROC                            |                    | Processor unit system program           |

| С                               | 16                 | Device control and status register      |

| c <sub>8</sub>                  |                    | 'Done' bit                              |

| C <sub>9</sub>                  |                    | Interrupt enable bit                    |

| D                               |                    | Decoding matrices                       |

| F                               | 5                  | Instruction fields                      |

| I                               | 16                 | Instruction register                    |

| I <sub>O</sub>                  |                    | Word/byte instruction bit               |

| М                               | 2 <sup>16</sup> ,8 | Main memory                             |

| N                               | 85,10              | Navigation matrix                       |

| R                               | 8,16               | General registers                       |

| R <sub>6</sub>                  |                    | Processor stack pointer                 |

| <sup>R</sup> 7                  |                    | Program counter                         |

| υ                               | 56                 | Unibus lines                            |

| <sup>U</sup> 0−,15              |                    | Data lines                              |

| <sup>U</sup> 16 <del>-</del> 33 |                    | Address lines                           |

| <sup>U</sup> 34,35              |                    | Control lines                           |

| Sy | mbol                    | Dimension | Function                 |

|----|-------------------------|-----------|--------------------------|

|    | υ <sub>40–43</sub>      |           | Bus request lines BR 7:4 |

| a  | F                       | 2         | effective address        |

|    | a <sub>1</sub>          |           | first address            |

|    | <b>a</b> . <sub>2</sub> |           | second address           |

| ъ  |                         |           | local variable           |

| е  |                         | 5         | program exceptions/traps |

|    | e <sub>0</sub>          |           | odd addressing           |

|    | e <sub>1</sub>          |           | reserved instructions    |

|    | e <sub>2</sub>          |           | time out                 |

|    | e <sub>3</sub> .        |           | trap instructions        |

|    | е <sub>Д</sub>          |           | trace trap               |

| g  |                         |           | local variable           |

| h  |                         | 2         | interrupt holder         |

|    | h <sub>O</sub>          |           | exceptions               |

|    | h <sub>1</sub>          |           | I/O interrupt            |

| ı, | j,k                     |           | local variables          |

| m  |                         |           | addressing mode          |

| n  |                         | 10        | navigation vector        |

|    | n <sub>O</sub>          |           | instruction class        |

|    | n <sub>1</sub>          |           | entry line in EXEC       |

|    | n <sub>2,3,4</sub>      |           | branch control in EXEC   |

| р  |                         | 16        | Processor Status word    |

|    | P <sub>0,1</sub>        |           | current operation mode   |

|    | <sup>p</sup> 2,3        |           | previous operation mode  |

|    | <sup>p</sup> 8,9,10     |           | Processor priority       |

|    | 1.3                     |           |                          |

| <u>Symbol</u>        | Dimension | Function              |

|----------------------|-----------|-----------------------|

| $\mathbf{p}_{11}$    |           | Trap (T) bit          |

| <sup>p</sup> 12,13,1 | 4,15      | Condition code        |

| q                    | 5         | memory access queue   |

| r                    | 5         | memory access request |

| ន                    | 2         | selection vector      |

| u.v.w                |           | local vectors         |

#### CHAPTER I

#### INTRODUCTION

The electronic computer affords a very powerful tool for system simulation. It is not by chance, therefore, that the significant increase in system simulations has almost paralleled the growth of electronic computers. The systems that are simulated can be business/economic systems, social systems, environmental systems or even other computer systems. One of the many reasons for simulating systems on a digital computer is the rapidity with which results are obtained. Another reason is the provision it gives to consider the problem to any level of detail.

The reasons for simulating a system can be many fold (9). Among them are the facility of studying a dynamic system in either real time, compressed or expanded time, the ability to study a complicated system by breaking it into component subsystems, the provision it gives to experiment with the system being simulated without actually building a prototype.

Simulation of computer systems can be done either at the "macro" level or at the "micro" level (8). At the macro level, the effects of processing complete jobs are simulated, and each transaction may represent a total job. This level of simulation may be used to study the effects of an increase in the workload of the system, or the quality of service measured in terms of the turn-around time, quality

of service under a projected workload, etc.

Micro level simulation involves extremely fine level of detail.

The effect of each individual machine language instruction is simulated. At this level of simulation, a unit of real time requires many units of simulated time. Therefore, micro level simulation can be expensive, both in terms of programming and running times, and requires a detailed understanding of the system.

During development of software packages for minicomputers, the debugging stage performance may be severely limited by the computer memory size, input-output facilities, or by the lack of translators with diagnostic capabilities. It therefore becomes desirable to simulate the minicomputer on a large host computer, in a higher level language, to get the software packages at least past the debugging stage. Simulation in a higher level language provides ease with which data structures can be manipulated. Even if the simulator does not mimic the simulated machine in its entirety, it may be set up to simulate a sizable subjet of the assembler package. Such a simulation has to be done at the micro level.

In this report a large subset of the PDP 11/40 assembly language has been implemented on an IBM 360/65 host computer in PL/1. The implementation also includes simulation of program controlled input/output from peripheral devices like the teletype and papertape reader/punch. Device-initiated interrupt simulation, using the computer interrupt structure is also incorporated in the implementation.

Chapter II describes the PDP 11/40 computer. Most of the description is based on the Digital Equipment Corporation system manuals of the PDP 11/40 (10, 11, 12). The architecture, instruction formats,

processor operation, interrupt structure, and input-output are covered.

The simulator itself is made up of an assembler and an interpreter. The two pass assembler is described in Chapter III. The scanner, to pick up symbols, symbol table construction during pass I and generation of object code in pass II are covered. Assembly time error detection is also discussed. A good description of the various methods adopted for searching/sorting during table processing can be found in Hellerman (2) and Wegner (14). The factors determining the choice of the method are presented in Gear (1).

The object code generated by the assembler unit forms the input to the interpreter. The object code is loaded into memory before execution can begin. Chapter IV contains a description of instruction fetch and execution, execution-time error checking and debugging facilities, input-output, output formats, etc. The program setup for simulating device-initiated interrupts is also described.

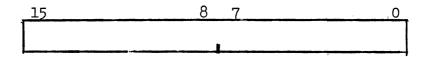

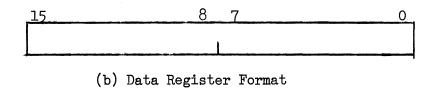

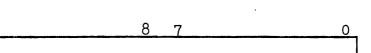

A formal description of the PDP 11/40 is presented in Chapter V. The description is in APL (4) and models the description of the IBM S/360 by Falkoff, Iverson and Sussenguth (5). Programs for processor operation, interrupt handling, address calculation, instruction execution have been described. A word of caution has to be given at this point. Arrays (registers, instruction words, etc.) as handled in the PDP 11/40 system manuals, have the least significant bit position numbered 0, and the most significant bit position numbered 15, as shown in Figure 1.

Figure 1. A PDP 11 Word as Used in the System Manuals

Since the simulator has been modeled on the descriptions in the manuals, words have been treated as shown in Figure 1. However, in the APL description in Chapter V, "words" are treated as shown in Figure 2, to be consistent with the language terminology, with the most significant bit numbered 0, and the least significant bit numbered 15.

Figure 2. A Word as Treated in the APL Description (Chapter V)

Chapter VI is a Users Manual and describes the deck setup and options for using the assembler-simulator. The assembler output format, error messages and codes, are also discussed. A summary and conclusions are presented in Chapter VII. The program flowchart is

given in Appendix A. Appendix B consists of a description of a sample run and the output. The machine operation code symbol table is given in Appendix C.

#### CHAPTER II

## PDP 11/40 ARCHITECTURE

The PDP 11/40 is a 16-bit general purpose, parallel logic computer using two's complement arithmetic. The processor can address directly 32K 16-bit words or 64K 8-bit bytes. All communications among system components are performed on a single high-speed bus, the The processor contains 16 hardware registers, eight of which Unibus. are programmable. The eight nonprogrammable registers are used for storage of a variety of functions including intermediate addresses, source-destination data, console operation data, and the stack pointer for the Memory Management option. The eight programmable general purpose registers RO-R7 can be used as accumulators, pointers to memory locations, or full word index registers, but their most important function is to hold operand and result addresses. Two of these registers R6 and R7 are used as processor stack pointer and program counter, respectively. This means that the contents of R6 and R7 are changed automatically by various instructions and, hence, cannot be used as general purpose registers.

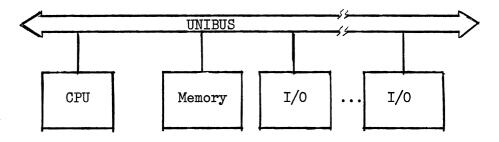

#### System Organization

The whole computer is organized around a single bus called the Unibus. The processor, memory and all peripheral devices share the same high speed bus (Figure 3). Because of the bus concept, all

peripherals are compatible, and device-to-device transfers can be accomplished at a fast rate. The Unibus enables the processor to view peripheral devices as active memory locations and treat peripheral device addresses exactly like (nonrelocatable) memory addresses, in the basic system address space. The processor uses the same set of signals to communicate with memory as with peripheral devices.

Memory locations, processor registers, device status and data registers are each assigned a unique address. All instructions that can be applied to date in core can be applied equally well to peripheral device registers, enabling peripheral devices to be manipulated as flexibly as memory.

Figure 3. Basic System Organization

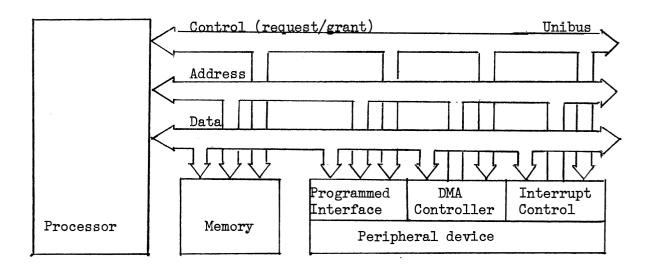

### Unibus Operation

Communication between system components is over the 56 lines of the Unibus, 51 of which are bidirectional and 5 unidirectional. A

bidirectional line permits signal flow in both directions. The five unidirectional bus grant (BG) lines are for priority bus control signals (10, pp. 179). The function of the 56 lines is as follows:

- (1) 16 bidirectional data lines which carry all data transfers.

- (2) 18 address lines. The same addressing scheme is used for programmed I/O, programmed processor/memory transfers, direct memory access (DMA).

- (3) 22 control-logic and parity check lines.

Figure 4 shows the processor, memory and a peripheral device connected to the Unibus. The peripheral device as has been interfaced for programmed instructions, direct memory access and interrupt.

Figure 4. The Unibus System (6)

#### Master/Slave Operation

All bus activity is asynchronous and depends on interlocking of controlled signals. During transfer between two devices, the device controlling the bus is termed the "master," and the other device the "slave." Master-slave relationships are dynamic. Memory is always a slave. The nature of interlocked communication requires that for each control signal issued by the master, the slave issue a response to complete the transfer.

Full 16-bit word or 8-bit byte information can be transferred on the bus between master and slave. Bus operations can be classified into data operations and control operations. The DATI, DATIP data operations transfer data into the master, while the DATO, DATOB data operations transfer data out of the master (10, pp. 182). The bus request (BR) and nonprocessor request (NPR) control signals are used by devices to gain control of the bus. Bus control obtained under a BR is for an interrupt whereas control obtained under an NPR is for a direct memory access (DMA). A device can perform a DMA after acquiring bus control via a BR. Transfer of bus control from one device to another is made by a priority arbitration logic.

#### Memory Organization

PDP 11 memory can be addressed either as 16-bit words or 8-bit bytes. Words always start at even numbered memory locations. A PDP 11 "word" is divided into a high byte and a low byte as shown in Figure 5.

High Byte Low Byte

Figure 5. The PDP 11 Word

Low bytes are stored at even numbered memory locations and high bytes at odd numbered locations. Memory addresses 0-255 are reserved for the system (interrupt vectors, trap vectors, etc.) and the top 4K words are reserved for general purpose registers, peripheral device registers, etc. The user, therefore, has 28K of the 32K directly addressable memory to program.

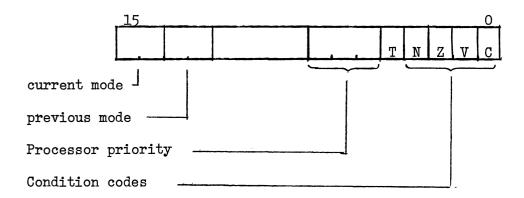

#### Processor Status Word (PS)

The processor status word, Figure 6, contains information about the status of the machine. The status can be described by the processor priority, current and previous operation modes and condition code.

Figure 6. Processor Status Word

The two modes of operation (11, pp. 2-4) Kernel and User modes are available under the Memory Management option.

The processor can operate at any one of the 8 priority levels 0-7. The current priority is maintained in bits 7-5 of the PS.

The 4-bit condition code is set by any of a number of instructions, including many arithmetic instructions. The condition code is set depending on the result of the instruction. Conditions setting the bits are given in Table I.

TABLE I

CONDITION CODE BITS OF THE PROCESSOR STATUS WORD

| PS bit | Bit<br>name | Condition setting the bit           |

|--------|-------------|-------------------------------------|

| 3      | N           | Result is negative                  |

| 2      | Z           | Result is zero                      |

| 1      | V           | Arithmetic overflow                 |

| 0      | С           | Carry from the most significant bit |

The trace trap bit T can be set or cleared under program control. When set, a processor trap will occur through location 14 on completion of instruction execution and a new processor status word will be loaded. The trace trap is a system debugging aid and is transparent to the programmer.

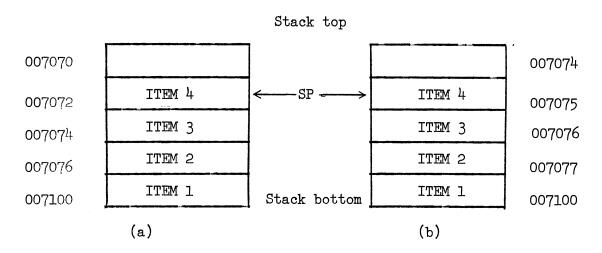

#### Processor Stack

To allow a programmer to make efficient use of frequently accessed data a processor stack is maintained in memory. Register 6 serves as a pointer to the top of the stack. The stack can be maintained anywhere in memory by initializing register 6 in the program. A typical processor stack is built with addresses decreasing from bottom to top as shown in Figure 7.

Figure 7. Processor Stacks (a) Word Stack (b) Byte Stack

Under the Memory Management option, the PDP 11 has two stacks called the Kernel and User stacks. When the processor is operating under the Kernel mode, it uses the Kernal stack and when operating under User mode, the User stack. The stack overflow boundary is at location 256. The Kernel stack boundary is a variable and is set through a stack limit register. Once the Kernel stack exceeds its boundary, the processor traps to location 4 after the current instruction is executed.

The stack permits save and restore of the program counter and status word in conjunction with subroutine calls and interrupts.

This feature allows reentrant codes and nesting of subroutines. Items can be added or removed from the stack by using the autodecrement and autoincrement addressing modes with register 6.

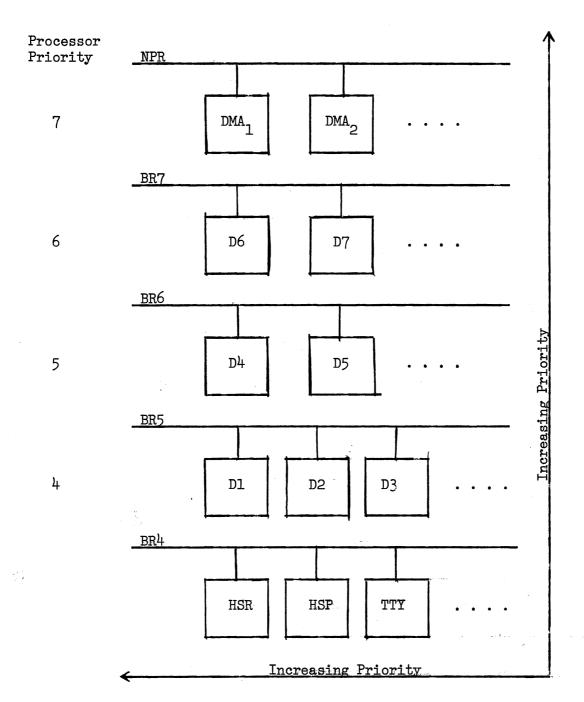

## Interrupt Structure

Since all components use the same Unibus, a certain amount of contention arises when more than one device requests to become bus master. A multilevel automatic priority structure is imposed to overcome this problem.

The Unibus contains 13 lines classified as priority transfer lines. Five of these are the bus request (BR) lines BR (7:4) and NPR and five are the corresponding bus grant (BG) lines BG (7:4) and NPG which the processor uses to respond to a request.

The priority arbitration logic assigns highest priority to NPR direct memory access data transfers. These requests are honored by the processor between bus cycles of an instruction execution. BR7 is the next highest priority and BR4 the lowest. These requests are honored by the processor between instructions. The priority is hardwired into each device except the processor. For example, the teletype and papertape reader/punch have a preassigned priority of BR4.

The processor priority can be set under program control to any one of the levels. This inhibits granting of bus requests on the same or lower levels and provides an effective masking technique. The priority interrupt structure is shown in Figure 8.

Figure 8. Priority Interrupt Structure (11)

Any number of devices can be chain-wired on each level, the device nearer the processor having a higher priority than a device

farther away.

Each device on a particular priority level passes a grant signal to the next device on the line unless it has requested bus control; in this case the requesting device blocks the signal from the following devices and assumes bus control. A device may cause interrupt operation to occur any time it gains bus control on one of the BR lines.

## Interrupt Service

Each device has a unique interrupt vector address in memory. These addresses are transmitted over the bus address lines. Two consecutive words in memory, the starting address of the service routine and the new PS are stored at the interrupt vector address. This unique identification eliminates the necessity of device polling. The operations required to service an interrupt can be described in APL as shown in Figure 9.

The operations involve pushing the Program Status word on the stack, lines 0,1 (Figure 9a), followed by pushing the program counter, lines 2, 3. The new program counter, which is the address of the service routine and the new Program Status word are loaded from the interrupt vector address, lines 4,5. Upon completion of service, a return from interrupt automatically restores the program counter and the old PS.

Legend

a Interrupt vector address

M Memory  $M^{i}$  is byte i

p Program Status word  $R^{6}$  Register 6, the stack pointer  $R^{7}$  Register 7, the Program counter  $\sqrt{R^{6}} \equiv \sqrt{R^{7}} \equiv \sqrt{p} \equiv 16$

Figure 9. Functional Description of Interrupt Control

## Addressing and Instruction Set

Much of the power of the machine is derived from its wide ranging addressing capabilities. Addressing can be done either at the word level or the byte level and is performed through general registers which can be used interchangeably as accumulators, index registers or pointers to memory locations.

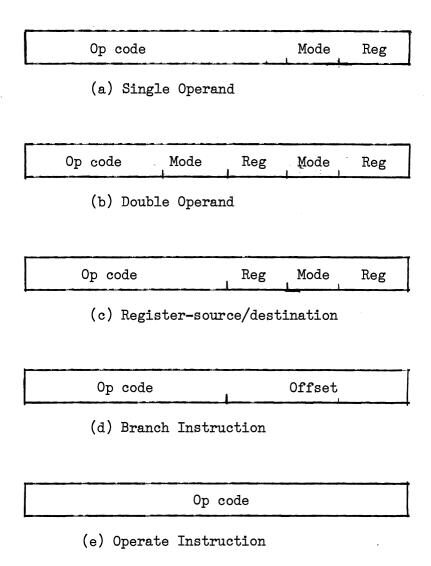

The five different instruction formats are as follows:

- (1) Single operand

- (2) Double operand

- (3) Register-source/destination

- (4) Branch instruction

- (5) Operate instruction

These five formats are shown in Figure 10.

Figure 10. Instruction Formats

Each operand in 1), 2) and 3) is specified by a general purpose register and the mode for using the register. The operand in Branch instructions are specified by an 8-bit word offset; the resetting of the program counter can be functionally represented in APL as shown in Figure 11.

$$\mathbb{R}^{7} \leftarrow (16) \tau (\pm \mathbb{R}^{7}) + 2 \times ((\pm \omega^{7}/I) - I_{8} \times 2^{7}) \qquad 0$$

(a)

Legend

I Instruction register

$$R^7$$

Program counter

$vI \equiv vR^7 \equiv 16$

(b)

Figure 11. Program Counter Modification in Branch Instruction

The offset in a branch instruction is the number of words from the current contents of the PC. The offset, given by the last 7 bits of the instruction register, is treated as a two's complement number. Since the PC expresses a byte address, the offset is multiplied by 2, to express bytes, before it is added to the PC.

The Operate instructions do not require an operand and execution proceeds immediately after instruction fetch.

Any of eight modes of addressing can be used to specify an operand. These are as follows:

(1) Register mode - Mode O: Register specified contains the operand. Assembler syntax: Rn.

- (2) Register deferred mode Mode 1: Register specified contains the operand address. Assembler syntax: @ Rn or (Rn).

- (3) Autoincrement mode Mode 2: Register 5 used as a pointer and then incremented: Assembler syntax: (Rn)+

If register specified is R7, the mode is "immediate" and the operand follows the instruction. Assembler syntax: #n.

- (4) Auto increment deferred Mode 3: Register is used as a pointer to word containing operand address and then incremented. Assembler syntax: @(Rn)+. If register specified is R7, the mode is "absolute," and the absolute address follows the instruction. Assembler syntax: @#A.

- (5) Auto decrement Mode 4: Register is decremented and then used as pointer to operand. Assembler syntax: -(Rn).

- (6) Auto decrement deferred Mode 5: Register is decremented (always by 2 even for byte instructions) and then used as pointer to operand address. Assembler syntax: @-(Rn).

- (7) Indexed Mode 6: Word following the instruction is added to the register contents to give operand address. Assembler syntax: X(Rn). If register specified is R7, the mode is "relative" and the relative address follows the instruction: Assembler syntax: A.

- (8) Index deferred Mode 7: Word following instruction added to register contents gives address of the address of the operand. Assembler syntax: @x(Rn). If the register specified is R7, the mode is "relative deferred." Assembler syntax: @A. In all variations of auto increment and auto decrement modes the

register contents are incremented/decremented by 2 for word instructions and by 1 for byte instructions.

Some of the instructions can address both bytes and words. For byte instructions the leftmost bit of the instruction is 1. An APL description of the instruction set is given in Chapter V.

## Input/Output and Peripherals

The Unibus permits a unified addressing structure in which control, status and data registers for peripheral devices are directly addressed as memory locations. The use of all memory reference instructions on device registers greatly increases the flexibility of input/output programming.

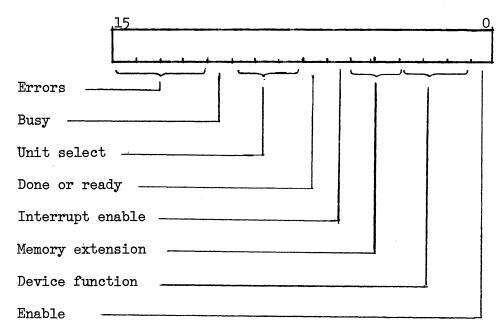

All peripheral devices are specified by two types of registers. These are 1) control and status registers, and 2) data registers and are shown in Figure 12.

Each device has one or more control and status registers that contain all the information necessary to communicate with that device. Many devices require less than sixteen status bits, and some others more than sixteen and, therefore, require additional registers.

The number and type of data registers associated with a device is a function of the device. Papertape reader and punch use single 8-bit data buffer registers, whereas a disk uses 16-bit data buffer registers.

PDP 11 Input/output devices include teleprinters, line printers, teletypes, card readers, alphanumeric displays. Storage devices range from small reel magnetic tape units to mass storage tape and moving or fixed head disk units.

(a) Control and Status Register Format

Figure 12. Peripheral Device Registers

### CHAPTER III

#### THE ASSEMBLER

The first step in the simulation is the conversion of the program source code into machine executable object code. This Chapter contains a discussion of the assembly procedure, code generation, error detection and processing and loading the generated code into memory for execution.

To translate the source assembly language, the assembler must

(1) replace each mnemonic instruction with its equivalent binary

code, and (2) replace each symbolic address with its numerical

address. One way of doing the former is by keeping a list of all

mnemonic instructions in a table and consulting it to find the binary

code, once a mnemonic is read. The latter problem can be approached in

a similar manner by having a table of symbols and their addresses.

The assembly process can be subdivided into the following two phases:

- (1) Scanning of the symbolic input and transforming symbolic names into corresponding codes.

- (2) Assembling the codes for the mnemonics and addresses.

The two phases usually require two scans of the source code. The first scan determines which location is to be assigned to each symbol and on the second scan the assembler produces the binary object code.

Each phase is described in the following paragraph along with the method used for its implementation.

#### Scanner

During each scan of the source code labels, identifiers, numbers, operators, delimiters and assembler directives need to be picked up for the assembly. This function is performed by a scanner. The scanner, generally, is programmed as a subroutine which is called upon by a higher level routine to perform the scanning.

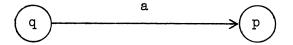

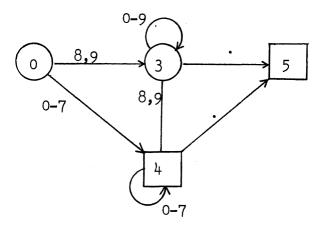

In this report, a finite state automation (FSA) approach is used for the scanner. Hopcroft and Ullman (3) define a finite automaton M over an alphabet  $\Sigma$  as "a system  $(K,\Sigma,\delta,q_0,F)$ , where K is a finite, nonempty set of states;  $\Sigma$  is a finite input alphabet;  $\delta$  is a mapping of K  $\times$   $\Sigma$  into K;  $q_0$  in K is the initial state and  $F \subseteq K$  is the set of final states." The interpretation of  $\delta(q,a) = p$  for q and p in K and a in p is that the FSA goes from state q to state p if the input symbol scanned is q. This transition can be represented graphically as in Figure 13.

Figure 13. State Transition in a FSA

An input symbol y is said to be accepted or recognized by an FSA if  $\delta(q_0,y)=p$  for some p in F.

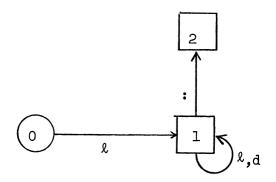

In this report the FSA is set up to recognize identifiers, labels, numbers, operators, assembler directives and delimiters, which form the vocabulary of the PDP 11/40 assembler. As such, a final state is associated with each of these classes of symbols. The alphabet of the FSA is the character set of the PDP 11/40 assembler. The FSA as set up consists of 21 states, 0 through 20, with state 0 being the initial state. States 1, 2, (4,5), (8,10), 11, (12,13,14,15,16,17,18) and 20 are the final states and correspond to the classes of identifiers, labels, numbers, literals, directives, operators, and delimiters respectively. Each character in the alphabet causes a transition from one state to another. All possible transitions are represented by a state transition matrix DELTA (Table II). The rows correspond to the 21 states and the columns (0-21) to characters of the alphabet. Each entry DELTA (I,J) = N in the table represents a transition from state I to State N under input J. For transitions which are not permitted N = -1. After such a transition the FSA goes into state -1. Once the FSA transits to state -1, the scanning is terminated and the symbol which has been recognized is returned to the routine calling the scanning routine.

A graphical representation of the FSA is shown in Figure 14, where each component unit recognizes a particular class of symbols. The final states are shown as squares. Once a symbol is recognized, the scanner routine returns the symbol, the symbol class and the state information of the FSA.

TABLE II

THE STATE TRANSITION MATRIX

| <br>   |       |   |     |            |            |           |     |              |                | VUCAE      | ULARY |           |    |             |     |     |    |     | **** |         |     |     | _ |

|--------|-------|---|-----|------------|------------|-----------|-----|--------------|----------------|------------|-------|-----------|----|-------------|-----|-----|----|-----|------|---------|-----|-----|---|

|        |       |   |     |            |            |           |     |              |                |            |       |           |    |             |     |     |    |     |      |         |     |     |   |

|        | OTHER |   |     |            | /          | +         | દ   | 1            | =              | #          | ·     | ×         | •  | a           | - , | •   | :  | :   | •    | A-Z, \$ | 0-7 | 8,9 |   |

| STATES |       |   |     |            |            |           |     |              |                |            |       |           |    |             |     |     |    |     |      |         |     |     |   |

| o      | -1 C  | ) | . 6 | 7          | 9          | 12        | 12  | 12           | 12             | 12         | 12    | 12        | 13 | 14          | 15  | 20  | 20 | -1  | 11   | 1       | 4   | 3   |   |

| 1      | -1 -1 | ì | -1  | <b>-1</b>  | -1         | <b>-1</b> | -1  | -1           | -1             | -1         | -1    | -1        | -1 | -1          | -1  | -1  | -1 | 2   | -1   | ı       | 1   | 1   |   |

| 2      | -1 -1 | ı | -1  | -1         | -1         | - 1       | -1  | -1           | -1             | -1         | -1    | <b>-1</b> | -1 | -1          | -1  | -1  | -1 | -1  | -1.  | -1      | -1  | -1  |   |

| 3      | -11   | ι | -1  | -1         | -1         | -1        | -1  | -1           | -1             | 1          | - 1   | -1        | -1 | -1          | -1  | -1  | -1 | -1  | 5    | 3       | 3   | 3   |   |

| 4      | -1 -1 | ı | -1  | -1         | - 1        | - 1       | -1  | -1           | -1             | -1         | - 1   | - 1       | -1 | - 1         | -1  | -1  | -1 | - 1 | 5    | 3       | 4   | 3   |   |

| 5      | -1 -1 | ι | -1  | <b>– 1</b> | -1         | - 1       | -1  | -1           | -1             | -1         | - 1   | - 1       | -1 | <b>-1</b>   | -1  | 1   | -1 | - 1 | -1   | -1      | -1  | -1  |   |

| 6      | 8 (   | 8 | 8   | 8          | 6          | 8         | 8   | 8            | 8              | 8          | 8     | 8         | 8  | 8           | 8   | 8   | 8  | 8   | 8    | 8       | 8   | 8   |   |

| 7      | 6     | 6 | 6   | 6          | 6          | 6         | 6   | 6            | 6              | 6          | 6     | . 6       | 6  | 6           | 6   | 6   | 6  | 6   | 6    | 6       | 6   | 6   |   |

| 8      | -1 -  | 1 | -1  | -1         | -1         | -1        | -1  | -1           | -1             | ~ <b>t</b> | -1    | -1        | -1 | -1          | -1  | -1  | -1 | - 1 | -1   | -1      | -1  | -1  |   |

| 9      | 9     | 9 | 9   | 9          | 10         | 9         | 9   | 9            | 9              | 9          | 9     | 9         | 9  | 9           | 9   | 9   | 9  | 9   | 9    | 9       | 9   | 9   |   |

| 10     | -1 -  | 1 | -1  | -1         | -1         | - 1       | -1  | -1           | -1             | -1         | -1    | -1        | -1 | - 1         | - 1 | -1  | -1 | -1  | -1   | -1      | -1  | -1  |   |

| 11     | 1 -   | 1 | -1  | -1         | -1         | - 1       | ~1  | -1           | -1             | -1         | - 1   | -1        | -1 | . <b>-1</b> | -1  | -1  | -1 | -1  | -1   | 11      | -1  | -1  |   |

| 12     | -1 -  | 1 | -1  | -1         | -1         | -1        | -1  | -1           | -1             | -1         | -1    | -1        | -1 | -1          | -1  | -1  | -1 | -1  | -1   | -1      | -1  | -1  |   |

| 13     | -1 -  | 1 | -1  | -1         | -1         | 16        | -1  | , <b>- 1</b> | -1             | -1         | -1    | -1        | -1 | -1          | -1  | -1  | -1 | -1  | - 1  | -1      | -1  | -1  |   |

| 14     | -1 -  | 1 | -1  | -1         | -1         | - 1       | ~1  | -1           | <del>-</del> 1 | 18         | 17    | -1        | -1 | <b>- 1</b>  | 19  | -1  | -1 | -1  | -1   | -1      | -1  | -1  |   |

| 15     | -1 -  | 1 | -1  | -1         | -1         | - 1       | - 1 | - 1          | -1             | -1         | 1.7   | -1        | -1 | -1          | -1  | -1  | -1 | -1  | -1   | -1      | -1  | -1  |   |

| 16     | -1 -  | 1 | -1  | - 1        | <b>– 1</b> | - 1       | - 1 | -1           | -1             | -1         | -1    | -1        | -1 | -1          | -1  | -1  | -1 | -1  | -1   | -1      | -1  | -1  |   |

| 17     | -1 -  | 1 | -1  | -1         | -1         | - 1       | -1  | - 1          | -1             | -1         | - 1   | - 1       | -1 | - 1         | -1  | -1  | -1 | -1  | -1   | -1      | -1  | -1  |   |

| 18     | -1.   | 1 | -1  | -1         | -1         | - 1       | -1  | -1           | -1             | -1         | -1    | -1        | -1 | -1          | -1  | -1  | -1 | -1  | -1   | -1      | -1  | -1  |   |

| 19     | -1 -  | 1 | -1  | <b>- 1</b> | -1         | - l       | -1  | - 1          | -1             | -1         | 17    | -1        | -1 | -1          | -1  | -1  | -1 | -1  | -1   | -1      | -1  | -1  |   |

|        |       |   | _•  | -1         | -1         | - 1       | -1  | -1           | -1             | - 1        | - 1   | -1        | -1 | - 1         | - 1 | - 1 | -1 | - 1 | - 1  | -1      | -1  | -1  |   |

NOTE - REPRESENTS A BLANK

-1 REPRESENTS AN INVALID TRANSITION

(a) unit to recognize labels, identifiers

(b) unit to recognize numbers

(c) units to recognize literals

Figure 14. Finite State Automaton to Recognize Syntactical Categories

(d) unit to recognize assembler directives

(e) unit to recognize operators

(f) unit to recognize delimiters

Legend: alphabet

$$\Sigma = b'''/+\&|=\#(\%)@-,;:.\$ABC...Z\emptyset123...9$$

$\& = \$,A,B,C...Z$   $\varepsilon = \text{any character in }\Sigma$   $d = \emptyset,1,2,...9$

Figure 14. (Continued)

TABLE III

SYNTACTICAL CATEGORIES AND ASSOCIATED STATES

| State | Symbols Recognized |

|-------|--------------------|

| -1    | error state        |

| 1     | identifiers        |

| 2     | labels             |

| 4     | octal numbers      |

|       |                    |

| 5     | decimal numbers    |

| 8,10  | literals           |

| 11    | directives         |

| 12–18 | operators          |

| 20    | delimiters         |

|       | · ·                |

Examples of the symbol recognition process are described below.

## Examples

Numbers in the PDP 11/40 Assembler can either be octal or decimal. Decimal numbers are terminated by the decimal point. 123, 147 are octal numbers whereas 123., 147 are decimal numbers.

Consider the number 123 as the input to the FSA. Figure 14b, the unit to recognize numbers gives the transitions under different inputs. Each character in the input causes a state transition. The initial state of the FSA is state 0. Under the first input character,

"1," the FSA changes its state to 4. The FSA remains in this state for the input characters "2" and "3." Since the input has been exhausted and the FSA is in one of the final states, the number is a valid number. Similarly for the decimal number 123., the FSA will be in state 5 and the number will be recognized. Invalid octal numbers like 184 or 987, which contain 8 and 9 will cause the FSA to transit to intermediate state 3 and, therefore, will not be recognized. The character A in the invalid number 12A3. will cause a transition to state -1 and, therefore, cause an error.

## Table Construction and Processing

The assembler basically has to deal with two types of symbols:

- (1) Operation-code symbols

- (2) Address symbols.

The binary code corresponding to operation-codes is specified by an operation-code symbol table. The binary code for any mnemonic can then be determined by a table look-up. The format of each node in the operation code symbol table used in the implementation is shown in Figure 15. The table itself is given in Appendix C.

|          | Number of |         | Operation | Mnemonic |

|----------|-----------|---------|-----------|----------|

| Mnemonic | operands  | Link    | code      | type     |

| 6 bytes  | 1 byte    | 2 bytes | s 4 bytes | l byte   |

Figure 15. Node Format in Operation Code Table

Address symbols have their codes assigned to them by the assembler. Addresses may be data addresses, assigned according to the storage allocation scheme used for date, or instruction addresses, assigned by determining the address of the instruction having the symbol as its label. An address symbol table is constructed during pass I of the assembly. The format for a node in the address symbol table is shown in Figure 16.

| Symbol  | Link    | Symbol<br>value | Туре  |

|---------|---------|-----------------|-------|

| 6 bytes | 2 bytes | 2 bytes         | l bit |

Figure 16. Node Format in Address-Symbol Table

The scheme adopted for symbol table construction and lookup uses a hashing function. The hashing function partitions the symbols into 16 pseudo-randomly determined classes. The hashing function used is

HASH ADDR

$$\leftarrow 2^4 \mid 5 \downarrow S$$

.

S, the sum of the characters in the symbol taken two at a time from the leftmost position, is shifted 5 bits to the right. The result is divided by 16 and the remainder of the division, a number between 0 and 15, gives the hash address.

The address generated places the symbol into one of 16 buckets

0-15. Synonym generation is handled by placing the symbol into a node in an auxiliary table and linking the node to the bucket to which the symbol is hashed. Each table is, therefore, essentially 16 linked lists. Symbol table lookup involves hashing the symbol to obtain the bucket, and a serial search of the linked list of that bucket.

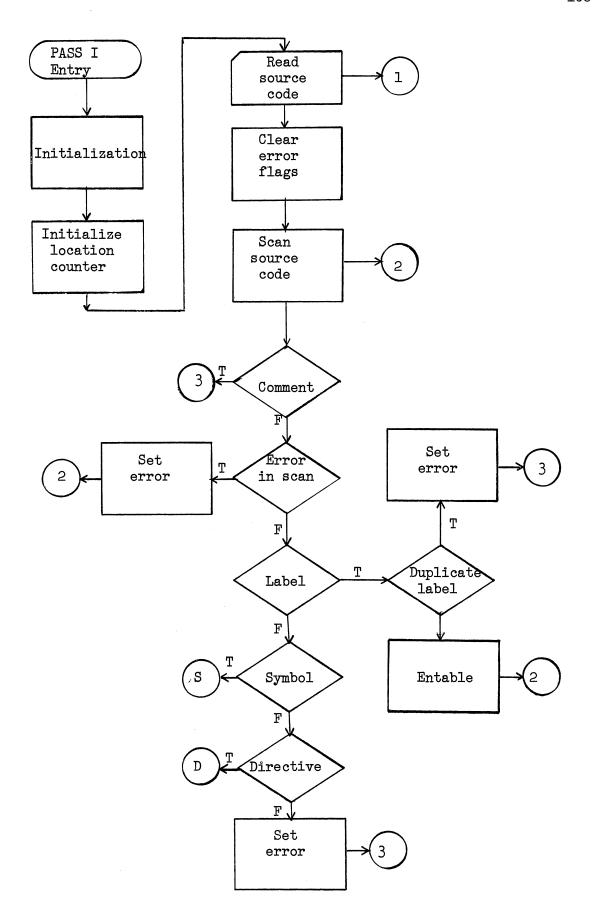

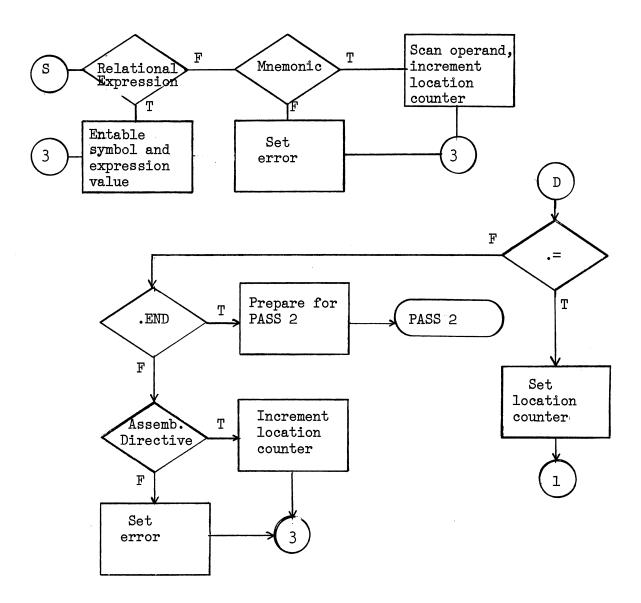

## Pass I

The prime task of the first pass is to construct the address symbol table. A location counter is maintained in both the passes in order to determine the final location of a line of code. After each instruction is translated, the location counter is incremented by the length of the instruction.

The first step is to read a new line of the source for translation. Since the second pass needs to reread the input file, a copy of the input is produced on an auxiliary storage device. Once a source line is read, the assembler extracts various fields from it to form labels, mnemonics, and addresses.

#### Label Field

The symbol found in the label field is placed in the address symbol table along with its address value. Checking for multiple definitions of a label involves a table lookup to see if the label is already present in the table.

# Mnemonic Field

An instruction mnemonic is recognized by the scanner as any other identifier. To see if the mnemonic is valid, an operation code table lookup is performed. If the mnemonic is not present in the table, the error is noted. If present, the address field is scanned.

Assembler directives, recognized by the scanner, are treated as a different class of symbols, distinct from identifiers. During pass I the address field of assembler directives is scanned. The LEND directive terminates pass I.

## Address Field

This field differs from instruction to instruction and may contain a number of subfields separated by commas. Each subfield may contain an expression involving names, numbers, and/or arithmetic operators.

Since the length of a PDP 11/40 instruction is determined by the "mode" of addressing and not by the mnemonic, the address field is scanned to determine the amount by which the location counter is to be incremented. The mode of addressing can be any one of eight different modes (Chapter II). Each operand, addressed by the indexed, relative, immediate or absolute modes requires an extra word. Instructions can, therefore, depending on the mode of addressing, require one, two or at most three words. During pass I the address field is scanned to determine the mode of addressing and hence the instruction length.

# Evaluating Expressions in Address Fields

PDP 11/40 assembler allows only the + and - arithmetic operators in operand expressions. Parentheses are not permitted. Expression evaluation can therefore proceed from left to right. Evaluation may involve conversion of numbers or characters to binary.

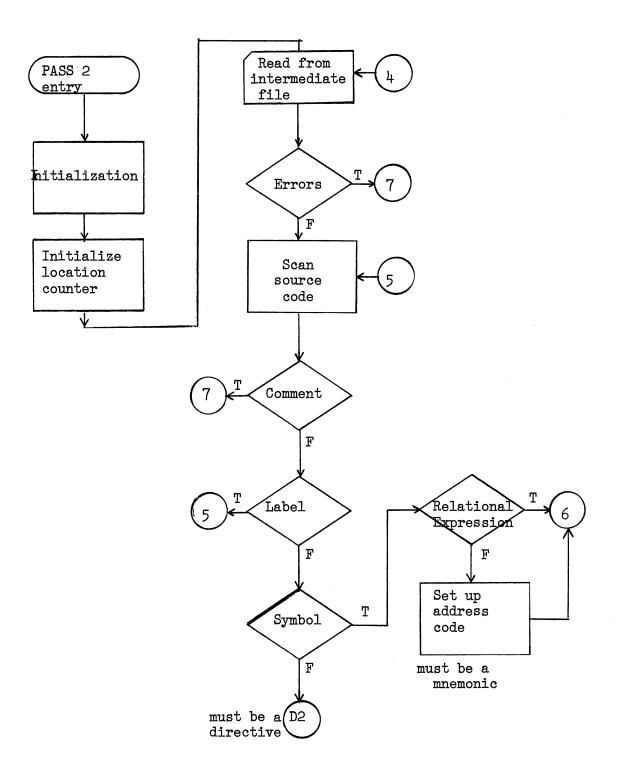

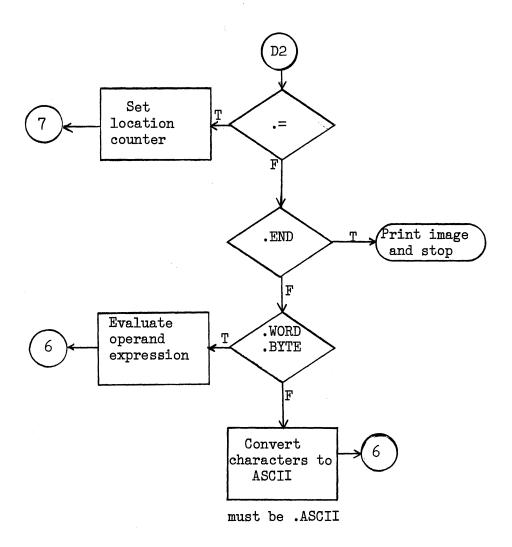

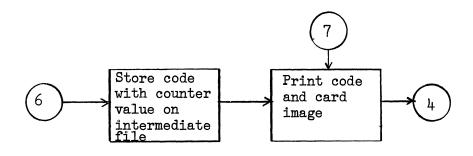

#### Pass II

The purpose of this pass is to translate the source language into binary by using the symbol table constructed in Pass I to convert the addresses, and the operation-code table to convert the mnemonics. A line of code is read in and many of the steps of Pass I repeated. The label field, which is handled completely in Pass I is ignored. The mnemonic field is examined and its binary code fetched by a table lookup. Expressions in the address field are converted to binary. Pass II also is terminated by the .END directive.

## Assembler Directives

Assembler directives fall into four classes. Directives for the PDP 11/40 are listed in Table IV.

TABLE IV

PDP 11/40 ASSEMBLER DIRECTIVES

| Class                    | Directive | Action                                    |

|--------------------------|-----------|-------------------------------------------|

| Data loading             | .WORD     | Load data in decimal or octal             |

| Location counter control | .=        | Set location counter                      |

| Table entry              | =         | Enter name with given definition in table |

| Character conversion     | .ASCII    | Convert character<br>string to ASCII      |

For the data loading directives it is necessary to determine how many words of storage will be occupied by the data in the directive so that the location counter may be incremented during Pass I. For .WORD and .BYTE, this requires the address field be scanned to determine the number of data words provided, by counting commas. Character conversion-loading requires a count of the characters in the string, to increment the location counter.

Location counter control directive sets the location counter to a specific value. This requires evaluation of the expression on the right of the relational operator, and assigns the value to the counter. Table entry directives also require expression evaluation. The symbol name is entered into the table along with the expression value.

During Pass II the address-field expression is converted to binary according to the rules of the directive. Character conversion can be done by a lookup on a table of characters and associated ASCII codes.

## Error Detection and Handling

Error detection is done in both the passes. Invalid symbols are caught by the scanner. Other syntactical errors are caught during operand-field expression evaluation. Error handling is done by placing an error code into an error table along with the statement number. Every type of error has an error code associated with it. The type can be determined from the error detecting mechanism built into the program. As an example, if an invalid mnemonic is picked up in a statement, the error code associated with the error, code 9, along with the statement number, are stored in an error table. The error code is printed in the assembly listing, immediately after the statement causing the error. A list of error codes and associated diagnostic messages is given in Chapter IV.

## Assembler Output

In addition to code generation the assembler usually produces a printed output. The output consists of the object code in octal, statement number and a listing of the source statement. Errors, if any, are indicated on the output by an error code, immediately following the statement in error. The diagnostic message for an

error can be obtained by looking up the code in Table XI, in Chapter VI. Immediately following the source listing, symbols and associated values (in octal) are printed.

## Loader

The binary code generated during assembly is saved on a secondary device to be used by the loader. Once the second pass is terminated, the generated code is loaded into memory for execution. Loading is done only if the assembly is error free. The scheme for loading uses a nonrelocatable loader. Loading begins from location 128 unless the location counter is set to a high value. The first 128 locations, locations (0-127), are reserved for the system. Once loading is complete, the program is ready for execution.

#### CHAPTER IV

#### THE SIMULATOR

The binary code generated by the assembler is loaded into memory for execution. This Chapter contains a description of instruction fetch and execution, program-controlled input/output, device-initiated interrupts, execution time error detection and debugging aids.

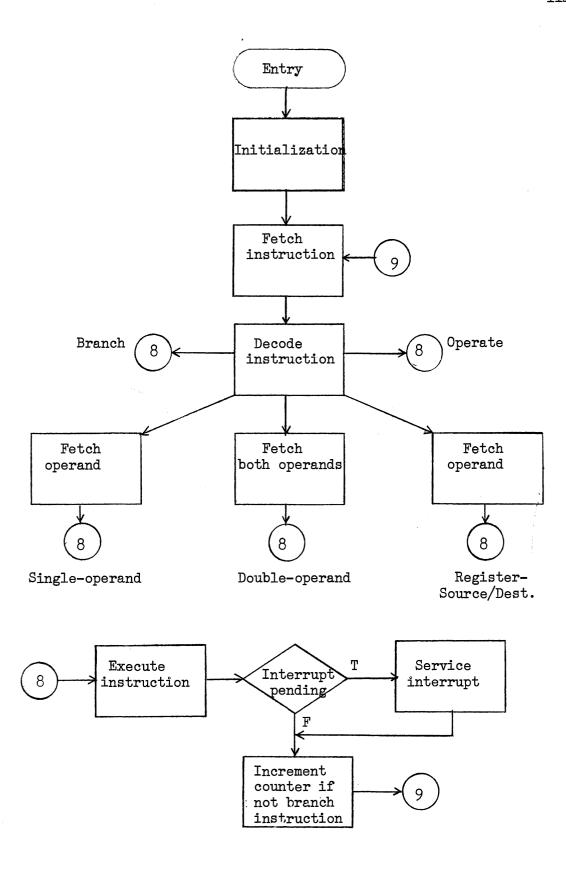

#### Instruction Fetch and Execution

During the loading process the address of the first instruction is placed in the program counter. During instruction fetch, the word in memory at the location given by the contents of the program counter (PC) are placed into the instruction register (IR). The contents of the PC are incremented by 2, to point to the next instruction. The order in which instructions are fetched and executed is determined by the statements of the program.

Having fetched the instruction from memory into the IR, it is necessary to decode the instruction in order to determine its type. The leftmost bit of the IR, specifies if the instruction is to operate on word or byte operands. The remaining 15 bits of the instruction are divided into five 3-bit fields FO-F4. Instruction decoding is done on the basis of these five fields.

For the purpose of instruction decoding and execution, the

instruction set is divided into Single operand instructions, Double operand instructions which include Register-source/destination and Extended Instruction Set (EIS) instructions, Branch instructions and Operate instructions. Once the type is determined by the five fields, instruction execution begins.

The first step during execution is the operand fetch. Each operand in the single and double operand instructions is specified by a register and a mode for using the register. The mode gives the type of addressing used to fetch the operand. For single operand instructions the operand is fetched into the memory buffer register (MBR). For double operand instructions the source and destination operands are fetched into the memory buffer register—source operand (MBR\_S) and MBR.

The second step in the execution phase is to operate on the operands in the MBR and MBR\_S and nodify them as called for by the particular instruction being executed. Thus, instruction ADD, adds the contents of the two registers, whereas CLR clears MBR. The result of the operation is stored at the address specified in the instruction. For single operand instructions this address is the same as the address of the operand, and for double operand instructions this address is the address of the destination operand. Condition code bits are set/cleared if called for by the instruction.

For Branch instructions the operand address is specified as the offset from the current contents of the PC. This offset is added to/subtracted from the contents of the PC to affect the branch.

Branch instructions do not modify the condition code.

Operate instructions do not require operand fetch. Some operate instructions change the condition code.

A detailed APL description of instruction fetch/execution is given in Chapter V.

# Program-Controlled Input/Output

Peripheral device registers are treated by the Unibus as nonrelocatable memory addresses. Therefore, operations on these registers, such as transferring information into or out of them, or manipulating data within them, are performed by normal memory reference instructions.

All devices are specified by a pair of registers. These are

(1) a control and status register that contains all information

necessary to communicate with the device, and (2) a data buffer register which temporarily holds data to be transferred into or out of the memory.

Input/output from teletype, papertape reader and papertape punch has been simulated in this report. All program controlled I/O is done by using the interrupt system of the computer. An interrupt request is made to the processor when information is ready to be input/output. Priorities permitting the processor accepts the request. Control passes to the appropriate interrupt service routine. When  $I/\rho$  is complete, the processor regains control and execution of the interrupted program is resumed.

I/O devices, which have been simulated, are all on the lowest priority level--bus request BR4. Among the devices on this level, highest priority is given to the papertape reader, followed by the

punch and teletype. Interrupt requests are honored by the processor if its operating priority level is less than 4. Once a request is honored for a device on this level, the processor priority is raised to 4, thus, prohibiting any other device on this level to interrupt. After the interrupt has been serviced, the processor priority is lowered to its previous value. The raising/lowering of processor priority, which provides an efficient interrupt mask, is done by loading a new Processor Status word each time the processor is interrupted. The location from which the PS is loaded is unique to the device interrupting. Each device has a unique two-word interrupt vector address. The second word contains the address of the interrupt service routine. When an interrupt request is honored, the old program counter and PS are pushed onto the processor stack and the service routine address and the new PS are loaded.

For the devices simulated in this report, the addresses in memory of the device interrupt vector, control and status register and the device data register are summarized in Table V.

TABLE V

DEVICE REGISTER AND INTERRUPT

VECTOR ADDRESSES (OCTAL)

| Device                                       | 2-Word<br>Interrupt |                          | & Status<br>Ister       | Data<br>Register  |                      |  |

|----------------------------------------------|---------------------|--------------------------|-------------------------|-------------------|----------------------|--|

| Device                                       | Vector<br>Address   | Actual<br><u>Address</u> | Address in<br>Simulator | Actual<br>Address | address in Simulator |  |

| Teletype a) Keyboard/reader b) Printer/punch | 60<br>64            | 177560<br>177564         | 134<br>140              | 177562<br>177566  | 136<br>142           |  |

| Papertape Reader                             | 70                  | 177550                   | 124                     | 177552            | 126                  |  |

| Papertape Punch                              | 74                  | 177554                   | 130                     | 177556            | 132                  |  |

For the purpose of simulation the actual control register and data register addresses were converted to smaller addresses, so that simulation could be done even with a part of the 32K-word addressable memory. The top 128 words of the memory are reserved for the system and contain the interrupt vector addresses and addresses of the device control registers and device data registers.

I/O from the four devices simulated can be broken down into

- (1) Input from teletype keyboard/reader and papertape reader and

- (2) Output to teletype printer/punch and papertape punch.

# Teletype Keyboard/Reader and Papertape Reader

Input from these two devices is similar in most respects. The

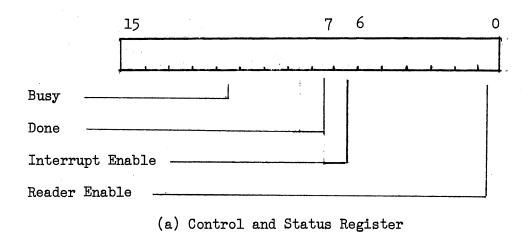

Control and Status register and data buffer register for these devices are shown in Figure 17.

Data

(b) Data Buffer Register

Figure 17. Reader Device Registers

TABLE VI

FUNCTION OF READER CONTROL

AND STATUS REGISTER BITS

| Bit(s) | Name                | Function                                                                                                                                            |

|--------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 11     | Busy                | Set during reception of information bits                                                                                                            |

| 7      | Done                | Set when character available in buffer; cleared when reader enable is set or data buffer referenced; causes interrupt when interrupt enable is set. |

| 6      | Interrupt<br>Enable | Enables interrupt                                                                                                                                   |

| 0      | Reader<br>Enable    | Enables reader (not keyboard) to read read one character                                                                                            |

Input can be initiated by setting the interrupt and reader enable bits in the status register. Setting the reader enable bit causes a character to be read into the buffer. When the character is available, the done bit is set, which causes an interrupt. The interrupt sequence is initiated and control passes to the service routine. When the buffer is referenced in the service routine, to transfer data from it into some location in memory, the done bit is cleared.

# Teletype Printer/Punch and Papertape Punch

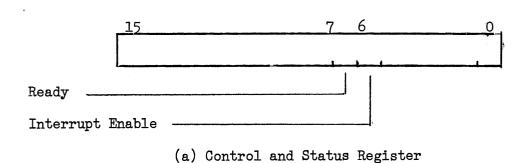

The manner in which output is handled by these devices is similar. The control and status registers and the data register are shown in Figure 18.

Data

(b) Data Buffer Register

Figure 18. Print/Punch Device Registers

The function of the bits of the control and Status register is summarized in Table VII.

TABLE VII

FUNCTION OF PUNCH CONTROL

AND STATUS REGISTER BITS

| Bit | Name                | Function                                                                 |

|-----|---------------------|--------------------------------------------------------------------------|

| 7   | Ready               | Punch available; cleared when buffer loaded; set when punching complete. |

| 6   | Interrupt<br>Enable | Enables "Ready" to cause interrupt                                       |

During simulation the ready bit of the status register is set as part of the initialization process so that the printer/punch is available. To start output, the interrupt enable bit is set. This causes an interrupt and the interrupt sequence is initiated resulting in a branch to the service routine. When the buffer is loaded by the service routine, the ready bit is cleared and punching initiated.

When punching is complete, the ready bit is set again.

# Device-Initiated Inputs

In contrast to program controlled I/O, device-initiated interrupts are treated as nonprocessor request (NPR) type interrupts and, therefore, given the highest priority. NPR requests are honored by the Unibus between bus cycles and are generally for direct memory

accesses. This is generally done by a cycle-steal process. Since cycle stealing in no way disturbs the program sequence, there is no need to save register contents and other information as with program interrupts. As simulated in this report, device-initiated interrupts are used only to input data into the computer from the interrupting devices. Device-initiated interrupts and non-processor requests are used synonymously.

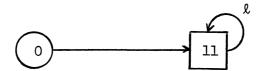

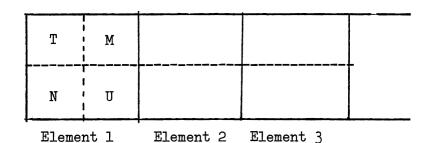

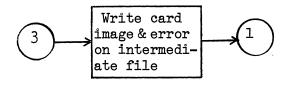

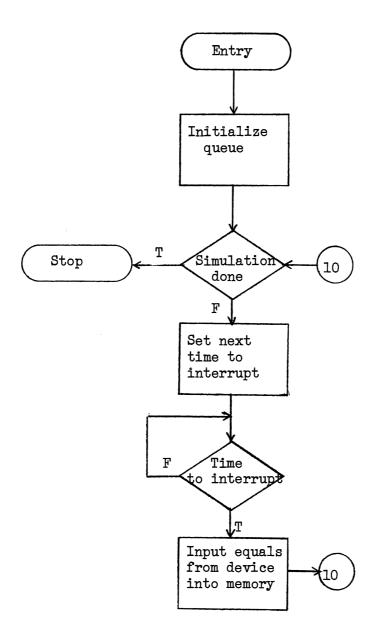

The setup to simulate device-initiated inputs included a queue. Each element of the queue represents one NPR. The elements of the queue are initialized before the simulation begins. Each element consists of the interrupt time in cycles, the location in memory where the data is to be input, the number of characters to be input, and the unit number of the interrupting device for purpose of identification, as shown in Figure 19. The elements in the queue are arranged in increasing order of their interrupt times. A cycle counter is maintained as well as a next time to interrupt (NTTI).

NTTI is the minimum of all interrupt times in the queue elements.

Since the queue elements are arranged in increasing order of their interrupt times, NTTI is the interrupt time of the elements beginning from the first and proceeding to the rear of the queue.

T: time to interrupt

M: memory address where data is to be input

N: number of characters to be input

U: unit identification number

Figure 19. Queue for Device-Initiated Interrupt Simulation

When the cycle counter, which is incremented by one after each cycle, equals NTTI, the signals from the device interrupting, are input via a cycle-steal. For this simulation study the external signals are supplied from a file called EXTIN. After one NPR is honored, NTTI is set to the interrupt time of the next element in the queue. Values of T, M, N. U for each element in the queue are user supplied. The format and deck setup are given in Chapter VI.

## Error Detection

Execution time errors are caught by the simulator and appropriate messages output. These errors may be due to addressing

a word on a byte boundary, overflow/underflow, usage of registers/

modes not permitted in some instructions, etc. Most of the execution

time errors are terminal errors and execution is suspended in those

cases.

# Debugging Aids

To facilitate debugging of programs, debugging aids have been provided in the simulator. Apart from the assembly time and execution time error detection, these aids help detect nonsyntactical execution time errors. Post-execution register and memory dumps are provided. An instruction trace facility is also provided. The instructions SET and CLT, set and clear the trace at (T) in the Processor Status word. When set, the instruction which is executed is traced. Tracing includes a dump of the general purpose registers, program counter, processor stack pointer, preceded registers and the processor Status word. Setting and clearing the T-bit can be done under program control and provides a powerful debugging tool.

#### CHAPTER V

# APL DESCRIPTION OF PDP 11/40

An APL description of the PDP 11/40 is presented in this Chapter. The computer system is described as seen by a programmer, and the description is independent of any particular hardware implementation. Iverson (4) gives a complete definition of the notation used. The description is based on the PDP 11/40 System Manual (11) and the Processor Handbook (10), and consists of a set of programs and tables.

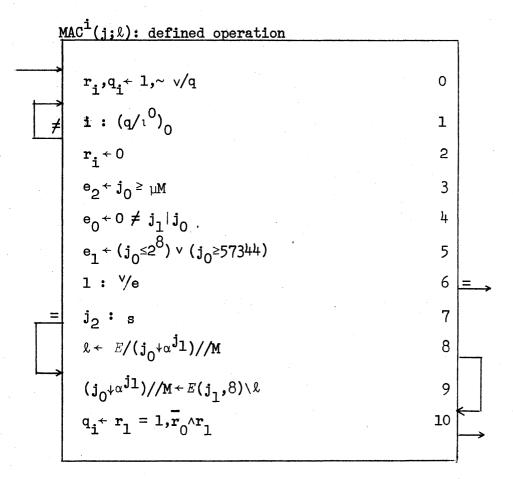

The programs are either system programs or defined operations. All system programs operate concurrently and continuously, with one line active in each program. The defined operation program operates only when invoked by another program. In the description presented, PROC and IOIG are system programs, whereas ADC, EXEC, and MAC are defined operations. The description covers only those aspects of the system operation, which have been implemented in the assembler-simulator, and therefore, does not describe the PDP 11/40 completely.

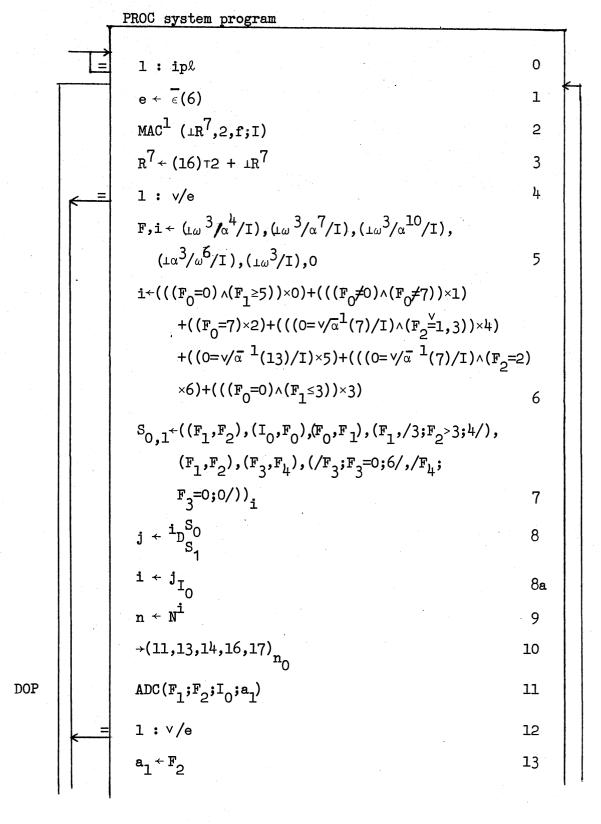

#### The Processor

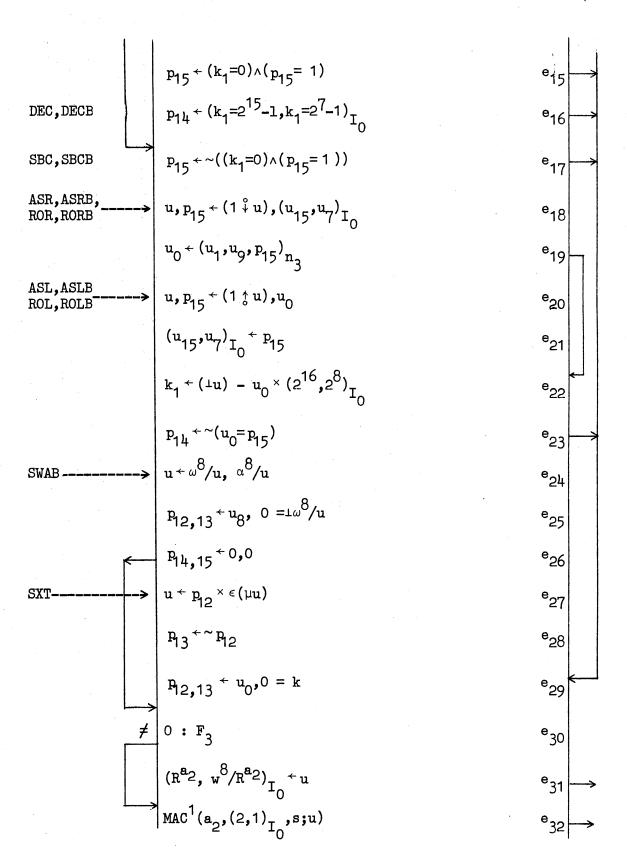

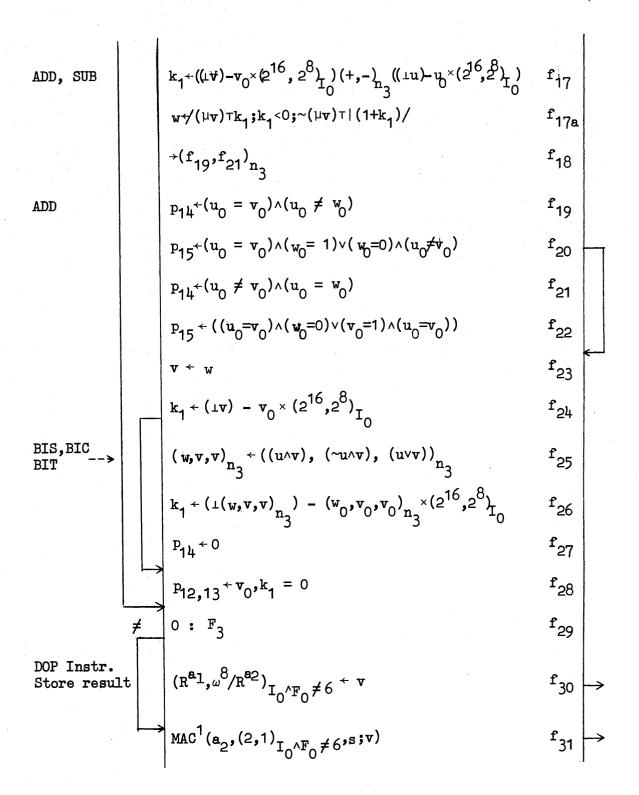

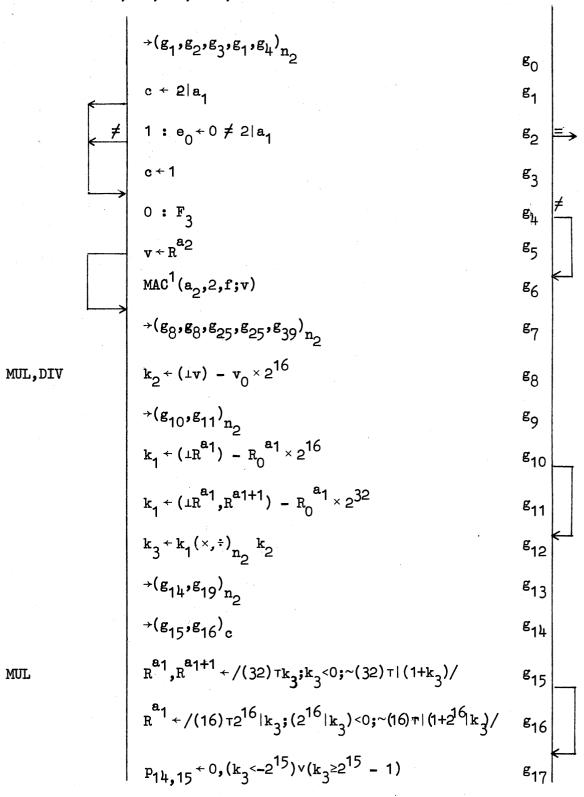

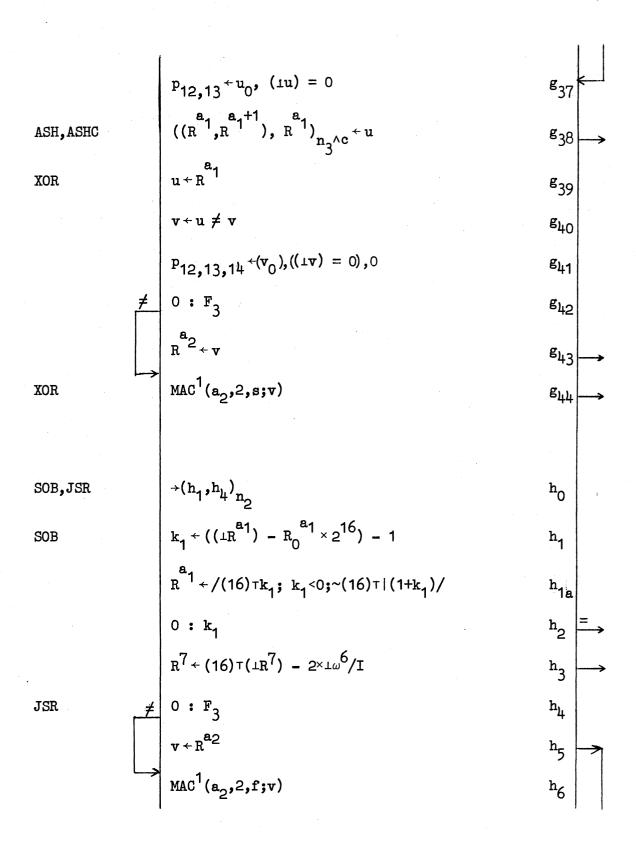

The PROC program, Figure 20, describes the sequencing and execution of instructions and the servicing of interrupts. The program segments, their functions and the state of the processor during each function are summarized in Table VIII.

Figure 20. The Processor System Program

Figure 20. (Continued)

TABLE VIII

"PROC" PROGRAM SEGMENTS

| Lines        | Function                      |   | Major State           |

|--------------|-------------------------------|---|-----------------------|

| 1- 4         | Instruction fetch             | } | FETCH                 |

| 5 <b>-</b> 9 | Instruction interpretation    | J | 1 11 011              |

| 10-16        | Effective address computation |   | SOURCE<br>DESTINATION |

| 17-18        | Instruction execution         |   | EXECUTE               |

| 19-24        | Trap interrupt service        |   | SERVICE               |

The processor can be described in terms of five major states. In the FETCH major state the instruction is fetched from memory. SOURCE and DESTINATION states obtain the source and destination operands, respectively. In the EXECUTE state the machine performs the action specified by the instruction, and the in SERVICE state, interrupts and traps are handled. In every major state the machine performs several minor operations, and a minor state is associated with each operation. For example, the FETCH major state consists of the minor operations: (1) retrieve the instruction from memory; (2) update the program counter; (3) load the instruction register; and (4) decode the instruction.

## Instruction Fetch

The first step in program execution is to fetch the instruction from memory. In order to prepare for instruction fetch, the exceptions vector is initialized to zero (line 1). The 2-byte instruction is fetched from memory at the address given by the program counter, and placed in the instruction register (line 2). The program counter is incremented by 2 (line 3) and in case of any exceptions during instruction fetch, control branches to line 19. Exceptions during fetch may be due to errors in addressing.

## Instruction Interpretation

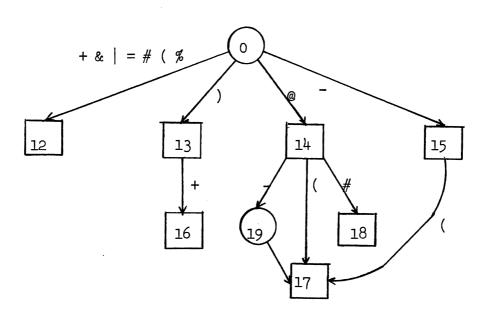

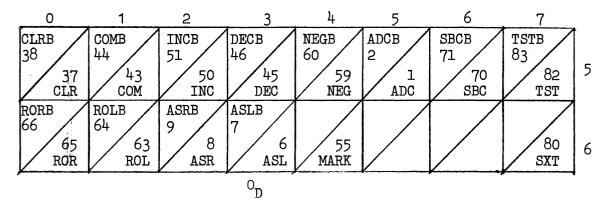

To determine the operation specified by the instruction, the instruction is decoded next. The instruction is divided into five fields, specified by the five components of the vector F (line 5). Instruction interpretation is done on the basis of these fields. The instructions are divided into five different classes, and i takes the value of the class of the current instruction (line 6). Table IX summarizes the five classes.

TABLE IX

INSTRUCTION CLASSES

|   |   | Class                       | i   |

|---|---|-----------------------------|-----|

| s | : | Single operand              | 0,4 |

| D | : | Double operand              | 1   |

| R | : | Register-source/destination | 2   |

| В | : | Branch                      | 3   |

| 0 | : | Operate                     | 5,6 |

|   |   |                             |     |

The components of the selection vector, S, take on values of the fields depending on i (line 7). Lines 8,9 interpret the instruction by selecting a row N<sup>1</sup> from the navigation matrix N, (Table X), to specify the vector n used in subsequent control of the instruction execution. The row of N selected, is determined by an element of a particular decoding matrix D, Figure 24, specified by the instruction class i, and the selection vector S. For example, if the instruction is 020314, the five fields  $F_0$ - $F_4$  have the values 2,0,3,1,4 respectively. Therefore, at line 6, i is assigned the value 1. Consequently,  $S_0$ ,  $S_1$  take on the values of  $I_0$  and  $F_0$  at line 7. The lower diagonal entry ( $I_0$ =0) in the second column ( $S_1$ =2) of the zeroth row ( $I_0$ =0) in the  $I_0$  decoding matrix gives the instruction, CMP. The entry in the element of the matrix, 41 in this case, gives

the row in the navigation matrix N.

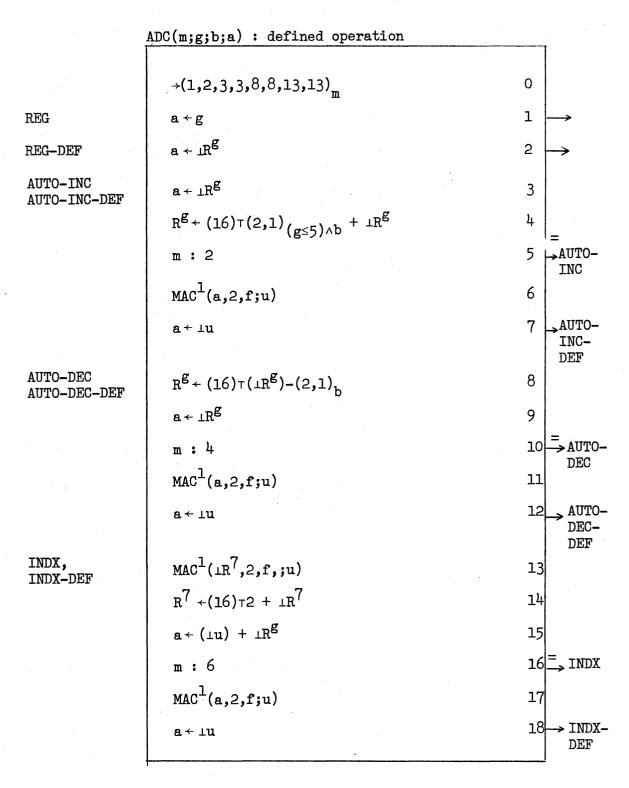

## Effective-address Computation

Address computation is done by the defined operation ADC. Computation depends on the instruction class. For double operand instructions, the address of the source operand (line 11) and the address of the destination operand (line 14) need to be calculated. For single operand instructions, only the address of the destination (line 14) is required. For the Register-Source/destination class of instructions, the register used (line 13) and the destination operand address (line 14) need to be computed. In the branch instruction, address calculation is done in line 16. Operate instructions do not need an operand and are executed immediately after instruction decode. Any exceptions during address computation abort execution (line 15).

#### Instruction Execution

Execution is done by the EXEC defined operation. The entry point in EXEC for any instruction depends on the component  $n_1$ , This is indicated informally by giving the instruction mnemonics on the left hand margin of the EXEC routine. Execution also may involve setting of the condition code. If the trap bit is set after execution, the exception is entered in e (line 18).

# Interrupt Service

Servicing of exceptions is given priority over I/O interrupt service. In case of any exception the bit (O for exceptions, 1 for I/O interrupt) in the interrupt holder h is set (line 20). The interrupt service sequence is initiated, if at least one interrupt is pending (line 21). The sequence consists of pushing the processor status word (PS) and the program counter (PC) onto the processor stack (line 22), and loading the new PS and PC from the interrupt vector address (line 23). The interrupt vector address is selected from one of the six fixed locations in memory. The interrupt vector address of the peripheral device, is obtained from the address lines of the Unibus, when the processor accepts the request. The element of h, which caused the interrupt is reset.

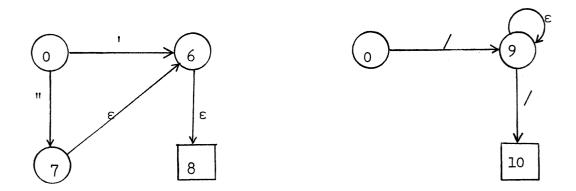

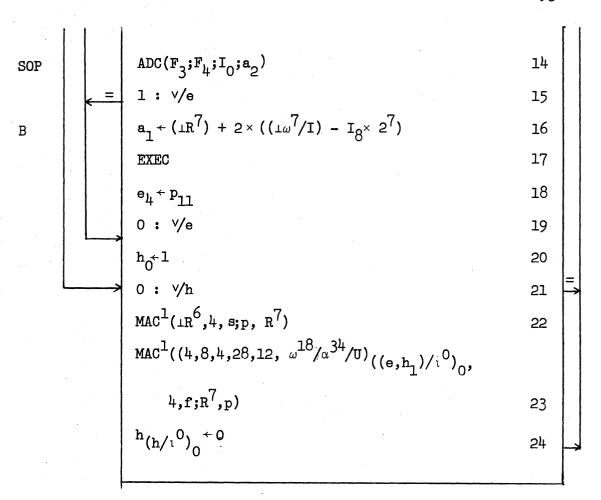

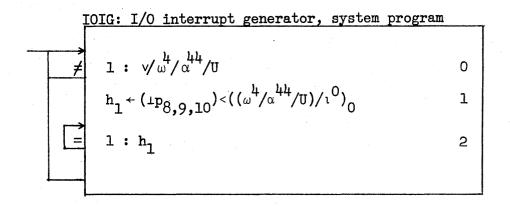

## Input/Output Interrupts

The IOIG system program, Figure 21, determines presence of interrupt requests by peripheral devices, and sets the bit in the interrupt holder, h, accordingly, line 1. The dwell at line 0 checks for interrupts on the Unibus bus request line BR(7:4). When an interrupt request is detected, the processor priority is compared against the request level, line 1. If the processor priority is less than the request level, the bit in the interrupt holder is set. This prohibits further interrupts until a new program counter and a processor status word is loaded and the interrupt holder bit reset (PROC lines 22-24).

Figure 21. Input/Output Interrupt Generator

#### Memory Access Program

The MAC operation, Figure 22, fetches or stores a specified number of bytes from the memory at a given address. The general form of the operation is  $\text{MAC}^{i}(j; \ell)$ , where i specified the device requesting access; j is a three component vector specifying the address in memory  $(j_0)$ , number of bytes to be accessed  $(j_1)$  and type of operation (store:  $j_2$ =s; fetch:  $j_2$ =f), respectively;  $\ell$  specifies the vector into/from which the accessed data is to be stored/fetched.

All data transfer operations are carried on the 56 lines of the Unibus. The addresses,  $j_0$ , are communicated over the 18 address lines, the data, contents of  $\ell$ , are placed on the 16 data lines and the type of operation is determined by the signal on the two Unibus control lines. Since memory is always a slave, a store operation,  $j_2$ =s, transfers data from master to slave and corresponds to the DATO operation. Conversely, a fetch,  $j_2$ =f, requests data from a slave and corresponds to the DATI operation. A description of these operations and Unibus transactions is given in the Peripherals and Interfacing Handbook (10).

Access to memory can be for a nonprocessor request (NPR) by one of the peripheral devices (i=0) or by the CPU (i=1). The request for service is entered in the bus request vector, r, and in the queue if it is empty (line 0). The queue discipline is on a priority basis with the NPR having greater priority than the CPU. The program dwells at line 1 until i is recognized as the first nonzero entry in the queue Requests that are not entered at line 0 are entered in

Figure 22. Memory Access Operation