# MICROPROCESSOR FEASIBILITY STUDY AND PRELIMINARY DESIGN FOR AN ARTILLERY FIRE CONTROL APPLICATION

By

# DAVID ERNEST WEST

# Bachelor of Science in Electrical Engineering

# University of Oklahoma

### Norman, Oklahoma

### 1974

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of MASTER OF SCIENCE May, 1976

÷

ter and the second s • •

OKLAHOMA STATE UNIVERSITY LIBRARY

AUG 26 1976

$\mathfrak{R}(t_i, s_i) = (1, \dots, 1)$

MICROPROCESSOR FEASIBILITY STUDY AND PRELIMINARY DESIGN FOR AN ARTILLERY FIRE CONTROL APPLICATION

Thesis Approved:

Thesis Adviser V

Dean of the Graduate College

### PREFACE

A project is underway at Oklahoma State University to develop an artillery fire control system. A preliminary study has been concluded which demonstrated the feasibility of the proposed system approach by computer simulations. This is a similar preliminary study as to the feasibility of using a microprocessor as the basis of the hardware implementation as an alternative to completely discrete components.

I wish to express my thanks to Dr. Edward Shreve, my thesis adviser, for his valuable guidance. Also, I would like to thank the remaining committee members, Professor Craig S. Sims and Dr. McCollom, for their assistance in the preparation of the final manuscript.

Finally, I would like to express my gratitude to Mrs. Janice Cronch for her excellent typing of the many drafts and the final copy.

# TABLE OF CONTENTS

| Chapter | Pa                                                                                                            | age                                    |

|---------|---------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Ι.      | INTRODUCTION                                                                                                  | 1                                      |

|         | 1.1Background1.2System Description1.3Objectives1.4Analysis Procedure                                          | 1<br>1<br>5<br>6                       |

| II.     | DETERMINATION OF MICROPROCESSOR REQUIREMENTS                                                                  | 8                                      |

|         | <pre>2.1 Throughput</pre>                                                                                     | 9<br>17<br>18                          |

| III.    | OVERVIEW OF MICROPROCESSORS                                                                                   | 20                                     |

|         | <pre>3.1 Introduction</pre>                                                                                   | 20<br>20<br>23                         |

|         | 3.2.2 Monolithic Processor3.3 Integrated Circuit Technologies3.3.1 MOS Technologies3.3.2 Bipolar Technologies | 25<br>25<br>26<br>27                   |

|         | 3.3.3 Technology Comparison                                                                                   | 28<br>31                               |

|         | Military Applications                                                                                         | 35<br>38<br>39                         |

| IV.     | FINAL SELECTION FROM A SURVEY OF AVAILABLE<br>MICROPROCESSORS                                                 | 40                                     |

|         | <ul> <li>4.1 Microprocessor Analysis</li></ul>                                                                | 46<br>49<br>53<br>54<br>58<br>60<br>64 |

|         | 4.4.5 Comparison                                                                                              | 65                                     |

# TABLE OF CONTENTS (Continued)

Page

Chapter

| ۷.         | APPL       | ICATION                                                                 | 0F                                     | THE                                          | Am29                                             | 00 !                                    | SER                     | IES                   | •                        | •          | •        | •        | •         |     | •  | •  | •                | •   | •  | 71                                           |

|------------|------------|-------------------------------------------------------------------------|----------------------------------------|----------------------------------------------|--------------------------------------------------|-----------------------------------------|-------------------------|-----------------------|--------------------------|------------|----------|----------|-----------|-----|----|----|------------------|-----|----|----------------------------------------------|

|            | 5.1<br>5.2 | Introdu<br>System<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6 | Spe<br>Mem<br>Bra<br>Fir<br>Pip<br>Shi | ecif<br>nory<br>nch<br>mwan<br>pelin<br>ft a | icati<br>Syst<br>Cont<br>re Re<br>ne Re<br>and R | on a<br>em<br>crol<br>gis<br>gis<br>ota | and<br>ter<br>ter<br>te | De<br>Co<br>Op<br>Fun | sig<br>ntr<br>era<br>cti | on         | on       | •        | •         | · · |    |    | •<br>•<br>•<br>• |     |    | 71<br>71<br>74<br>81<br>85<br>87<br>91<br>93 |

|            | 5.3        | 5.2.7                                                                   | Mac<br>mat                             | roco<br>e In                                 | ode a<br>nstru                                   | nd I<br>Ictio                           | Mic<br>on               | roc<br>Exe            | ode<br>cut               | e S<br>tio | ium<br>n | ma<br>Ti | ry<br>nes | s a | nd | Pa | ack              | kag | je | 96<br>99                                     |

| VI.        | CONCL      | USIONS                                                                  | AND                                    | RE                                           | Comme                                            | NDA                                     | TIO                     | NS                    | •                        | •          | • *      | •        | •         |     |    | •  | •                | •   | •  | 104                                          |

|            | 6.1<br>6.2 | Summary<br>Project                                                      |                                        |                                              |                                                  |                                         |                         |                       |                          |            |          |          |           |     |    |    |                  |     |    | 104<br>105                                   |

| BIBLIOGRAF | РНҮ.       |                                                                         | •                                      |                                              | •••                                              |                                         | •                       |                       | •                        | • ,        | •        | •        | •         |     |    | •  | •                | •   | •  | 108                                          |

| APPENDIX A | 4 - IN     | MP-16 IN                                                                | ISTR                                   | UCT                                          | ION S                                            | ET                                      | •                       |                       |                          | •          | •        | •        | •         |     | •  | •  | •                |     | •  | 111                                          |

| APPENDIX E | 3 – MI     | CROPROG                                                                 | RAM                                    | IED I                                        | 1ICR0                                            | PRO                                     | CES                     | SOR                   | IN                       | IST        | RU       | СТ       | 101       | ۱S  | ΕT | S  |                  | •   |    | 116                                          |

# LIST OF TABLES

| Table  | Page                                                                   |

|--------|------------------------------------------------------------------------|

| Ι.     | Instruction Mix for Extended Kalman Filter Implementation 12           |

| II.    | Required Constants for Implementation of Special Functions 16          |

| III.   | Technology Comparison                                                  |

| IV.    | Summary of the Differences Between the Two Types of<br>Microprocessors |

| ۷.     | Instruction Mix for Avionics Fire Control                              |

| VI.    | Available Microprocessor Performance                                   |

| VII.   | Am25SO5 Configurations                                                 |

| VIII.  | 16-Bit Microprocessors                                                 |

| IX.    | Hardware Support                                                       |

| Х.     | Software Support                                                       |

| XI.    | Microprocessor Functional Summary                                      |

| XII.   | Microprocessor Comparison                                              |

| XIII.  | System Elements ,                                                      |

| XIV.   | Input/Output Operations                                                |

| XV.    | Descriptive Symbols                                                    |

| XVI.   | Firmware Execution with Pipeline Register                              |

| XVII.  | Execution of Conditional Branch Instructions 91                        |

| XVIII. | Shift Control Code                                                     |

| XIX.   | Instruction Execution Time Summary 100                                 |

| XX.    | Package Count                                                          |

# LIST OF TABLES (Continued)

| Table   |                                                                  | Page  |

|---------|------------------------------------------------------------------|-------|

| XXI.    | Memory Reference Instructions                                    | . 112 |

| XXII.   | Register Reference Instructions                                  | . 113 |

| XXIII.  | Input/Output, Flag and Halt Instructions                         | . 114 |

| XXIV.   | Transfer of Control Instructions                                 | . 114 |

| XXV.    | Extended Instruction Set                                         | . 115 |

| XXVI.   | Intel 3001                                                       | . 117 |

| XXVII.  | Intel 3002                                                       | . 118 |

| XXVIII. | Explanation of Symbols                                           | . 120 |

| XXIX.   | Instruction Set for the 9404 $\ldots$ $\ldots$ $\ldots$ $\ldots$ | . 121 |

| XXX.    | I-Field Assignment                                               | . 123 |

| XXXI.   | Instruction Set for the 9406                                     | . 124 |

| XXXII.  | Instruction Set for the 9407 $\ldots$ $\ldots$ $\ldots$ $\ldots$ | . 125 |

| XXXIII. | 2901 Microcode                                                   | . 126 |

| XXXIV.  | MC10800 ALU Function Set                                         | . 127 |

\*

# LIST OF FIGURES

| Figure                                         |              |   | P | age |

|------------------------------------------------|--------------|---|---|-----|

| 1. Fire Control System                         | •            |   |   | 1   |

| 2. Fire Control Program Structure              |              |   |   | 3   |

| 3. Extended Kalman Filter Implementation       | , <b>.</b>   |   |   | 10  |

| 4. Flowchart of Extended Kalman Filter         | •            |   |   | 11  |

| 5. Decimal Cordic Computer                     | •            | • |   | 15  |

| 6. Basic Computer                              | •            |   | • | 21  |

| 7. Elements Common to Most Microprocessors     | , <b>,</b> • |   |   | 22  |

| 8. 16-Bit Microprocessor                       | •            | • | • | 24  |

| 9. 8-Bit Microprocessor                        | •            |   |   | 24  |

| 10. Speed/Power/Complexity Comparison          | •            | • |   | 29  |

| 11. Basic Microprogrammable System             | •            | • |   | 32  |

| 12. Parallelogram Configuration                | •            | • | • | 45  |

| 13. IMP-16C Card Assembly Block Diagram        |              | • |   | 50  |

| 14. RALU Block Diagram                         |              | • |   | 51  |

| 15. Block Diagram of a Typical System          | •            |   |   | 55  |

| 16. Intel 3002 Block Diagram                   | •            | • |   | 58  |

| 17. Am2901 Block Diagram                       | •            | • |   | 61  |

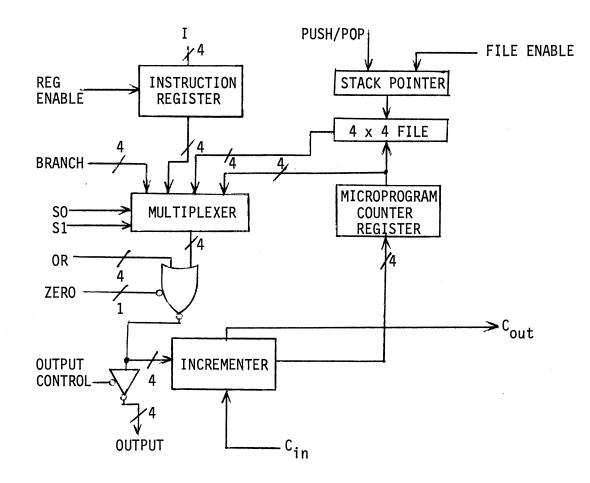

| 18. Am2909 Block Diagram                       | •            |   |   | 62  |

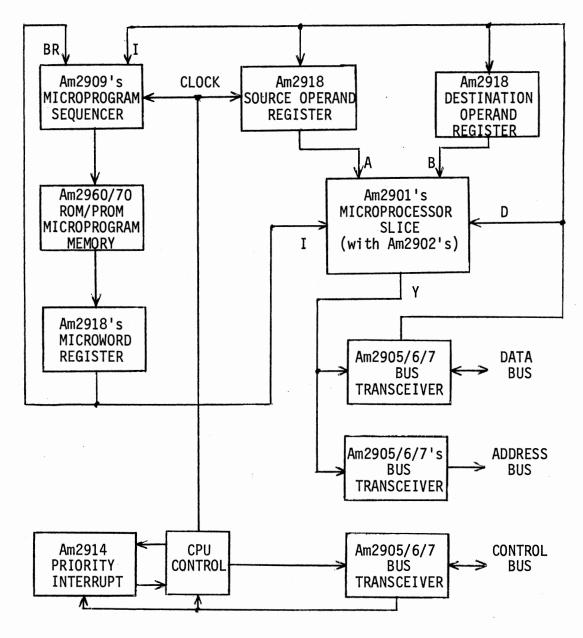

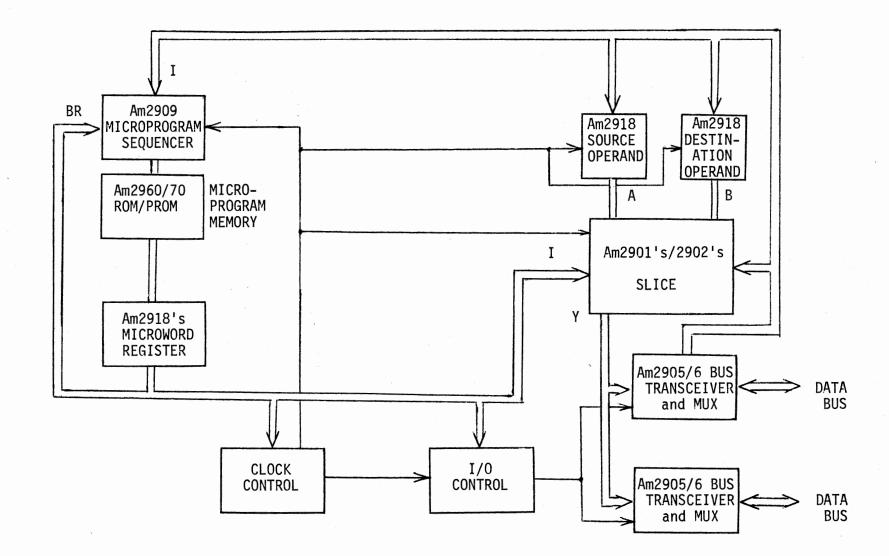

| 19. Typical System Using 2900 Family Elements  | •            |   |   | 63  |

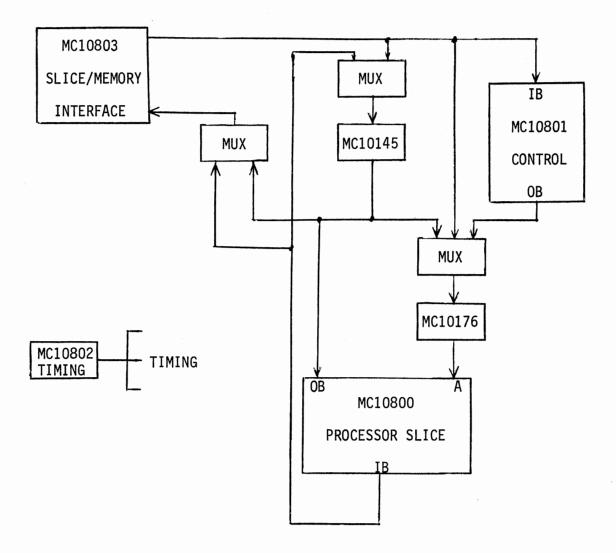

| 20. M10800 Family - Pipeline Processor Example | •            | • |   | 65  |

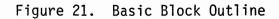

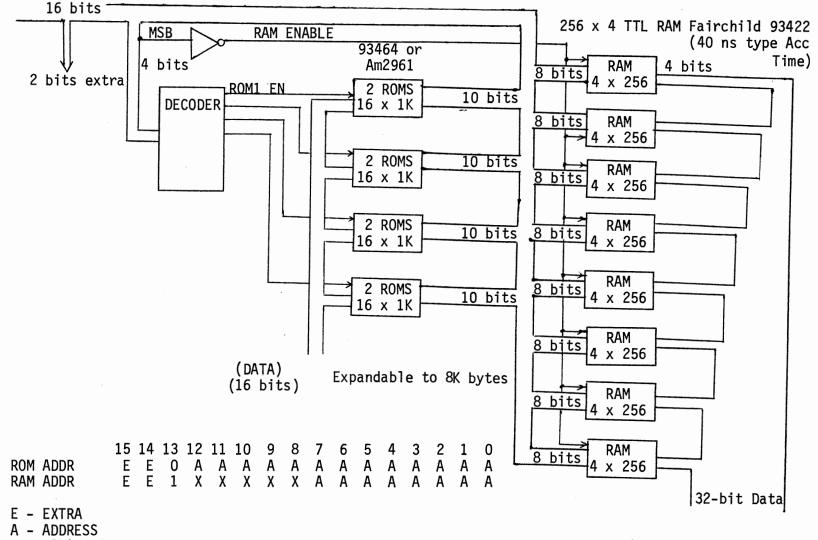

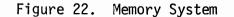

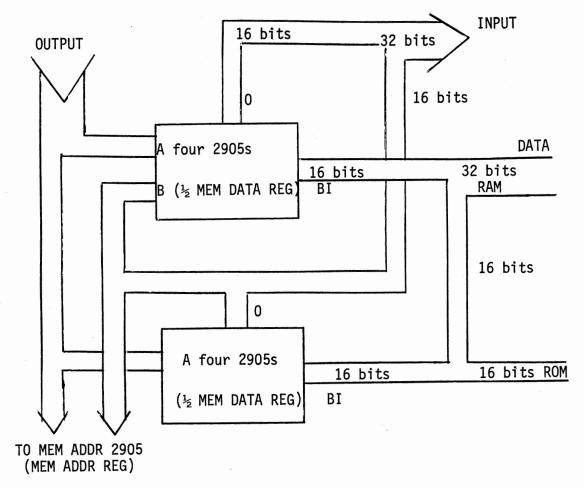

| 21. Basic Block Outline                        | •            |   |   | 73  |

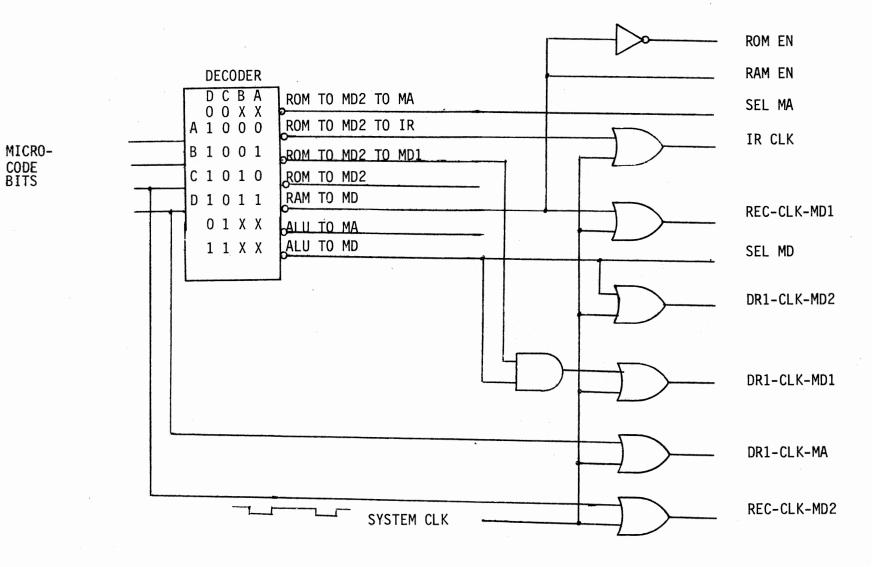

| 22. Memory System                              | •            |   |   | 75  |

# LIST OF FIGURES (Continued)

| Figure Pa                                             | ge |

|-------------------------------------------------------|----|

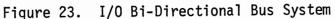

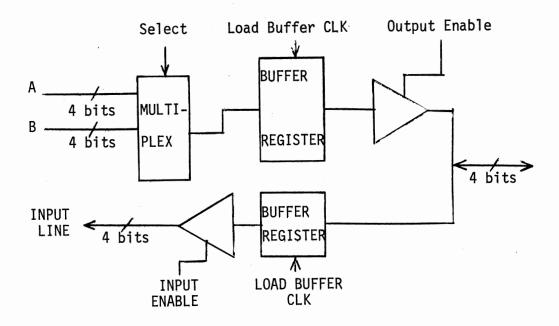

| 23. I/O Bi-Directional Bus System                     | 77 |

| 24. Am2905 Block Diagram                              | 77 |

| 25. Input/Output Control Circuit                      | 80 |

| 26. Input/Output Bus Circuit                          | 82 |

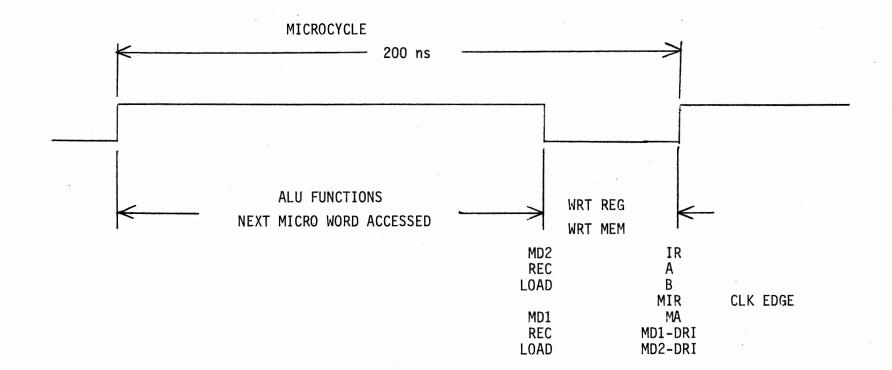

| 27. Microcycle Timing                                 | 83 |

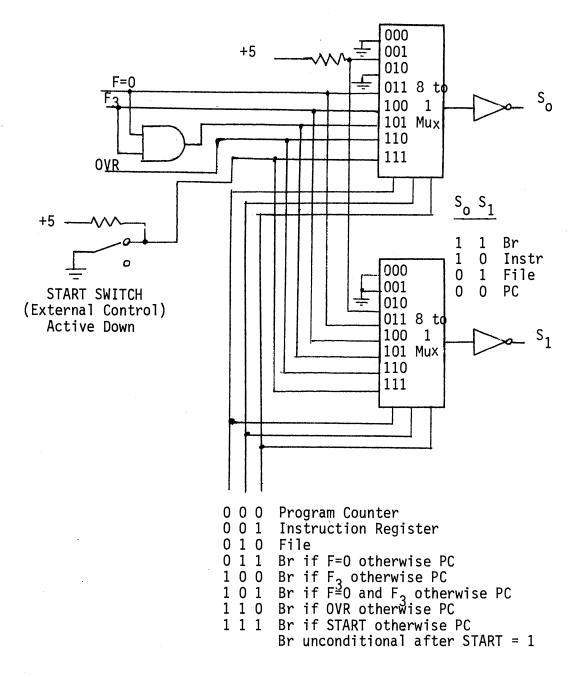

| 28. Branch Control Circuit                            | 84 |

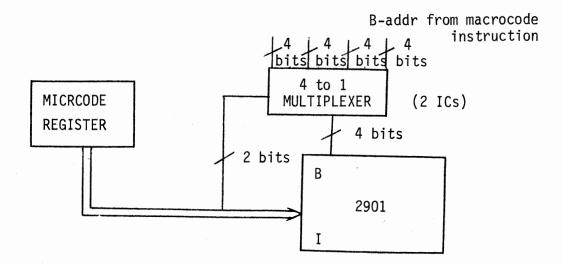

| 29. Firmware Control Using Two Bits of Microcode      | 86 |

| 30. Firmware Control Using Three Bits of Microcode    | 86 |

| 31. Clock Timing During Conditional Branch            | 90 |

| 32. Hardware for Clock Control for Conditional Branch | 90 |

| 33. Shift Control Circuit                             | 92 |

| 34. Multiplication Hardware Modification              | 95 |

| 35. Macrocode Summary                                 | 97 |

| 36. Microcode Summary                                 | 97 |

| 37. Program Development Chart                         | 07 |

### CHAPTER I

#### INTRODUCTION

#### 1.1 Background

This document involves the application of microprocessors to a tactical artillery fire control system. It is part of an overall program to develop a field portable fire control system. Feasibility was established by previous work done by the Electrical Engineering Department of Oklahoma State University. A simulation of the system has been implemented on the IBM 360/65 with encouraging results. Further work is required in software development, so that a flexible hardware implementation is desirable. Thus, microprocessors shall be studied in the hope that they can produce a reasonable alternative to completely hardwired logic.

### 1.2 System Description

The fire control system must predict the point of impact and then calculate necessary corrections to the firing azimuth and elevation to achieve the desired impact position. These functions must be performed in real time so that additional rounds may be fired if necessary before the sensor round has impacted. The advantage of the system is that the meteorological effects from temperature, density and winds do not have to be precisely known before firing to enable compensation. The projectile itself serves as a sensor which enables automatic compensation

without individual attention to each parameter.

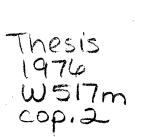

The overall system can best be described using Figure 1. The radar tracks the projectile to provide position and range rate data. This data is fed into the fire control system at a rate of 20 samples/second. The fire control system then uses this data to estimate the position and velocity of the projectile. These are used to predict the impact point and adjust the firing parameters of the artillery for predicted impact errors.

Figure 1. Fire Control System

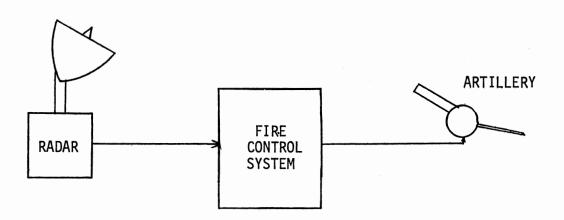

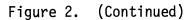

The general program structure which implements the fire control system is shown in Figure 2. Required operations for this process include coordinate transformations, input data filtering, integration of the state transition matrix and control.

This report will look exclusively at the problem of implementing the Kalman filter and coordinate transformations for the following reasons: the microprocessor analysis must begin by carefully determining

Figure 2. Fire Control Program Structure

the system specifications, which include power requirements, speed, input/output (I/O) and software. Before these can be determined, the overall system must first be studied to find the subsystem which presents the greatest requirements. The Kalman filter processor has been deemed the most critical not only for numerical accuracy, but also for required speed. The Kalman filter determines the system's accuracy and it must complete calculations within the 20 sample/second data rate. Thus, the microprocessor requirements such as speed and required instructions will be derived from analysis of the Kalman filter and coordinate transformation algorithms.

#### 1.3 Objectives

The major objectives of this analysis are first to make a selection of the required microprocessor and second to begin the application of this processor to the fire control system. This report is part of a preliminary project; therefore, the selection process will be well documented and written on such a level as to enable re-evaluation of the material in the event of system requirement changes. Also, material as to what is termed next generation processors will be included due to the uncertain time schedule of the project. In the event of a significant time delay in the system design, this material may become useful since faster systems are being designed which may become available commercially.

The applications material will be written using a single best choice if one exists. In the event that a clear choice does not exist, application of each will be done to give an idea as to their distinct advantages. A further objective of the application material is to give an

estimate of the required manpower and resources involved to complete the project. Manpower requirements are seen as an important aspect of this problem.

### 1.4 Analysis Procedure

The study organization has been broken into seven logical steps as shown below:

1. System description,

- 2. Determination of microprocessor requirements from the system description,

- 3. Overview of available microprocessors,

- 4. Reduction of microprocessor spectrum for analysis,

- 5. Study of available microprocessors within reduced spectrum of analysis,

- 6. Detailed comparison and selection and

- 7. Microprocessor application.

The study will begin with the determination of the microprocessor requirements to implement the Kalman filter and coordinate transformation algorithms. This will include determining the required number of bits of accuracy, the time limit for execution and the instruction set. Included in the software requirements will be the necessary subroutine functions.

With the system requirements in mind, an overview of available microprocessors will be presented including an introduction to microprocessors and integrated circuit technologies. From this overview one can reduce the spectrum of microprocessors to those with the most potential for this application. A study of particular processors on the market, which from preliminary analysis satisfy the basic requirements, will be made. After the detailed study of individual processors, a comparison and selection process can begin. Finally after the selection is made, Chapter V will be dedicated to the application of the chosen microprocessor. Application material will include hardware system alternatives, hardware multiplication and subroutine implementation if necessary, software organization, instruction definition and programming examples. Manufacturer-supplied software support will be described along with required software support which must be developed.

#### CHAPTER II

# DETERMINATION OF MICROPROCESSOR REQUIREMENTS

Before a search for the best microprocessor can begin one must first investigate the system requirements and working environment of the processor. This chapter will try to document the basic requirements and any special constraints which the chosen microprocessor must meet. Also a look at the problem in detail will give better understanding of the required firmware functions. Preliminary work has been done at Oklahoma State University in the area of software simulations. The basic Kalman filter equations have been studied and some different algorithms for implementing required functions have been documented. These studies will be used to determine the microprocessor requirements.

This chapter will basically draw from previous work to determine specific requirements and will not try to specify the fire controller functions. Specification of the fire control system is presently being done and is not yet in a concrete form. A complete specification of the fire controller is not necessary at this point since one of the basic reasons for selecting a microprocessor system is the added flexibility of firmware.

The system characteristics will be studied to determine three major areas of interest: throughput, input/output (I/O) parameters and special constraints. Throughput requirements are based on the number and type

of functions which the processor must execute in a given amount of time. The I/O parameters specify such requirements as the type of data, required bit-accuracy of various operations and external control or communication requirements outside of the controller system. Finally the special constraints will be specific characteristics which will necessarily constrain selection of the microprocessor.

### 2.1 Throughput

The firmware implementation of the fire control system has not been completed. The basic variable seems to be in the type of data filter needed to smooth the radar tracking data. Two different methods have been simulated, a polynomial filter and a Taylor series filter, with encouraging results. It is thought that a third method, the extended Kalman filter, would give even better results (38). Thus the extended Kalman filter method, which was the subject of an independent study will be used to determine the throughput requirements.

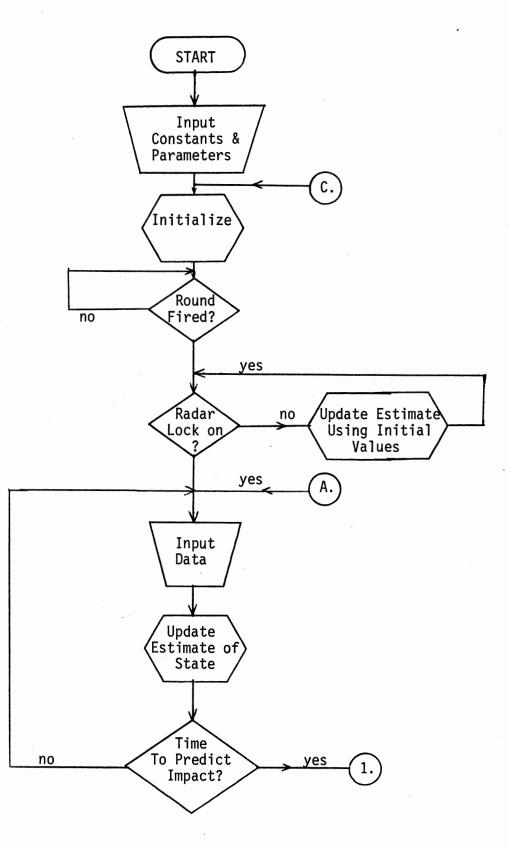

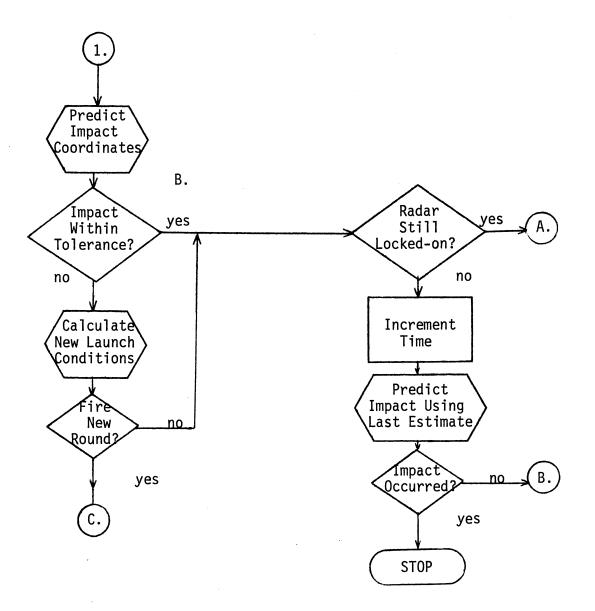

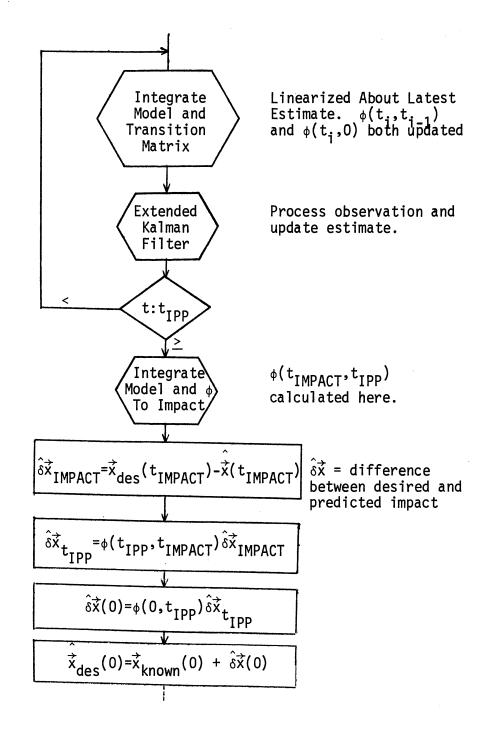

The time limitation for the execution of this state estimation loop is 0.05 second. This is the time to when the next radar data will be available. Thus the extended Kalman filter calculations must have been concluded so that real time estimation can be obtained of the test projectile path. Figure 3 is a block diagram of the extended Kalman filter prospective implementation. In this diagram the loop of interest includes the integration of the model and transition matrix and the extended Kalman filter. Although the integration routine is shown separately it is actually part of the extended Kalman filter as shown in Figure 4. Figure 4 shows the extended Kalman filter in detail where block two, COMPUTE THE PREDICTED STATE, includes the Runge-Kutta integration routine.

Figure 3. Extended Kalman Filter Implementation

Figure 4. Flowchart of Extended Kalman Filter (28)

.

The required functions for the execution of the extended Kalman filter system including the Runge-Kutta integration routine are shown in Table I. This instruction mix was part of the results obtained by a separate study (28). Table I was derived by looking at the functions which must be implemented in the extended Kalman filter loop. These are the functions which must be executed during the 0.05 second sample time. The primary purpose of this instruction mix will be to compute the execution time of the critical Kalman filter loop for prospective microprocessors. The number of required executions of each function shown in Table I does not include the use of one function to execute another function.

#### TABLE I

| Function                                    | Number Required   |

|---------------------------------------------|-------------------|

| Add-subtract<br>Multiply<br>Divide<br>Sin 7 | 900<br>1100<br>14 |

| Cos<br>Tan<br>Square root                   | 7<br>10           |

| Exponential<br>Miscellaneous                | 1<br>4000         |

#### INSTRUCTION MIX FOR EXTENDED KALMAN FILTER IMPLEMENTATION

The functions of Table I are only the major functions which must be

available as either an instruction or a subroutine. They do not include the many memory reference instructions, register manipulation instructions and jump instructions which will also be required. As a rough estimate 4000 miscellaneous instructions of these types will be included in the instruction mix. This is about twice the number of the special functions. These types of instruction have roughly the same execution times especially when compared to the more complex special functions. As a measure of the basic throughput requirements, the execution time of the extended Kalman filter loop will be calculated based on the instruction mix of Table I. This type of throughput calculation is very rough and only intended as a first approximation. A more accurate instruction mix would require programming the application on each processor being considered. In many cases the execution times of the functions will even have to be estimated. These estimates will be based on the performance of a similar microprocessor with the same function.

One has the alternative of using hardware or firmware for the implementation of these special functions. The only functions of the ones shown in Table I which are generally offered by most microprocessors are the add and subtract functions. The multiply and divide functions are sometimes offered but they are no more than internal firmware implemented requiring long execution times. The remaining functions must be implemented either in hardware or as subroutines. The minimization of hardware would lead to the software implementation of these functions depending on the speed of the chosen microprocessor. It is doubtful that a total firmware solution would have the required throughput. Thus a tradeoff between hardware and firmware implementations will probably be necessary. Although the determination of this tradeoff is part of the

system design, two alternatives will be discussed here.

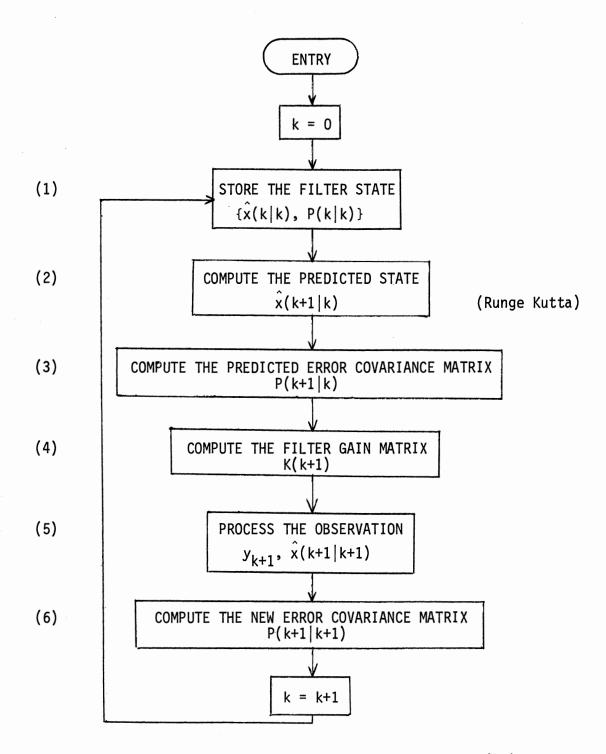

The first alternative is to use Cordic in the implementation of these functions. Cordic algorithms are implemented using both firmware and hardware. A general decimal Cordic computer is shown in Figure 5. The basis of Cordic is the use of a look-up table in read only memory (ROM) for certain constants which are then used by hardware in the calculation of the required function. The process requires a great deal of control and timing hardware, but it is a fast method of implementation (37).

The other alternative is to allocate the hardware resources to a single function which can be used together with firmware control to implement the remaining functions. All the special functions could be implemented with the addition and subtraction instructions as a base. But a better solution is to increase the number of base functions by hardware implementing the multiply, the most used function. Not only is multiplication a heavily used instruction in the system, but it is also required in the firmware implementation of the remaining functions. Furthermore firmware implemented multiplication would require at least thirty times the execution time of those instructions under the miscellaneous heading in Table I. This means the multiplication function would account for roughly 85 percent of the execution time while only accounting for 18 percent of the total number of instructions. Thus, hardware implementation of the multiply instruction could be used to increase the speed of the firmware implemented functions and increase the overall throughput. The final decision as to which method to use is dependent upon the microprocessor selected.

If the multiply is implemented in hardware, the remaining functions

Figure 5. Decimal Cordic Computer (37)

(sin, cos, tan, exponential and squareroot) can be implemented in firmware using rational approximations. These algorithms were investigated independently (28). The implementation of the rational approximation requires a series of multiplies and adds of the argument and certain constants. Thus another required instruction to implement the rational approximations would be a load immediate function or the ability to input constants from program memory. The number of constants required by each function is shown in Table II. The additional number of multiplies is really not significant when compared to the program requirements of 1100 multiplies. For example, only eight multiplies are required for the sin algorithm execution.

#### TABLE II

| Function    | Required Constants | Accuracy (Decimal digits) |

|-------------|--------------------|---------------------------|

| Sin         | 4                  | 10                        |

| Cos         | 6                  | 10                        |

| Tan         | 0                  | 10                        |

| Exp<br>Sqrt | 10                 | 12                        |

| Sqrt        | 5                  | 25                        |

### REQUIRED CONSTANTS FOR IMPLEMENTATION OF SPECIAL FUNCTIONS

The number of constants will have little effect on memory requirements. Each constant must be stored in memory, but either program memory or working memory may be used for storage. The constants must be

accounted for when the memory requirements are finalized.

Thus the throughput of the controller is very dependent upon the multiply instruction execution and will be important in the microprocessor selection. The previous discussion shows that the fire control system will require more general computing power than actual controller type functions.

#### 2.2 Input/Output Parameters

The microprocessor must interface with an external memory and some type of radar data channel. The only periodic input data will be the radar data which are range, range rate, azimuth and elevation. From preliminary simulations done at Oklahoma State University, a data accuracy of at least 32 bits is desirable. The 32-bit accuracy may be obtained by double precision operation of a 16-bit processor but at the cost of reduced throughput. The tradeoff between the increased hardware required for parallel 32-bit operation and the slower but decreased hardware of a 16-bit double precision system must be explored and determined during the microprocessor selection period.

The program memory will be somewhere between 4 kilo (K) and 8K bytes as seen from the previous discussion of the instruction mix. Also the firmware will have many matrix operations requiring external data storage. The matrix operations may involve as large as a six by six matrix (37). The exact working memory requirements are hard to determine but about 128 to 256 bytes of memory will probably be necessary, each byte being 32-bits. These requirements can be determined more accurately when the software has been better defined and the microprocessor system outlined.

#### 2.3 Special Constraints

The major system constraints come from the working environment. The final system is intended to be a field portable artillary fire control processor. Thus, the microprocessor must function over the military temperature range for field use and be relatively small in size to be portable. The power requirements will also necessarily be minimized for portability. These constraints will be observed as nearly as possible, but the operating requirements must first be met. The high speed or large throughput requirement may require a large amount of power.

The basic system will actually have the characteristics of a minicomputer, a large throughput system requiring medium-size-processor numerical ability. It will not have the characteristics of what is usually termed a controller. A powerful interrupt ability is not required. A direct memory access ability is not required since large data block transfers are not involved.

A final consideration which may become a constraint is the necessary manpower to develop a working system. This includes hardware and system design and software support. After the system has been designed, it must be transformed into the code of the microprocessor, which requires coding time and an assembler. If an assembler is not available for the chosen microprocessor, this must also be written. Debug software and special debug hardware will also be required. Thus, the project will require effort which goes beyond the implementation of the controller system. The choice of the microprocessor greatly effects the amount of manpower required for completion of the project.

General system requirements have been discussed so that an orderly microprocessor selection may begin. Actual system design would require

greater detail, but our concern is an overall picture of necessary functions and objectives.

## CHAPTER III

#### OVERVIEW OF MICROPROCESSORS

#### 3.1 Introduction

This chapter will introduce terminology and basic ideas relating to microprocessors. Its purpose is to characterize the different types of available microprocessors and to narrow down the spectrum which will be useful for the fire control application. Once the spectrum of useful microprocessors has been determined, the study and analysis of those which have the most potential may begin. Chapter IV will be dedicated to specific microprocessors presently on the market which meet the present needs.

#### 3.2 Basic Definitions

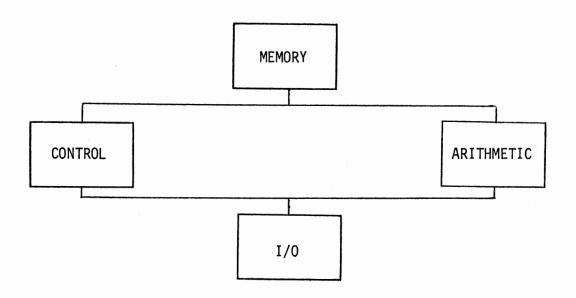

A processor may be defined as a device which fetches and executes instructions. Figure 6 is a block diagram showing the primary sections of a basic computer. The four computer sections are identified as follows:

- 1. Memory For storage of programs

- Arithmetic For performance of calculations on data and instructions

- Input/Output For exchange of data with external world and

- Control For primary control of the arithmetic section with minimal control of the other two sections.

Those sections which fetch and execute the instructions are the arithmetic and control sections, and thus constitute the processing unit.

Figure 6. Basic Computer

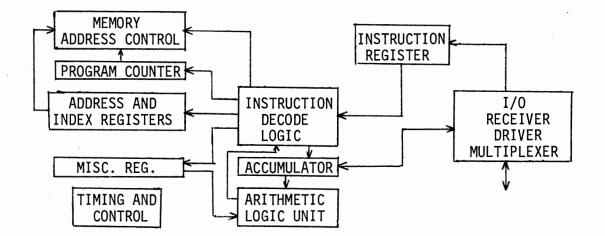

A microprocessor is a set of circuits necessary and sufficient to perform the functions of a general purpose processor. The number of circuits is relatively small and the packaging density of most of the circuits within this set is in the category of large scale integration (LSI). A detailed block diagram of the elements common to most microprocessors is shown in Figure 7. First a means must be provided to address the memory. Once the instruction has been sent from memory to the processor, it is loaded in the instruction register. Also, instruction decode circuitry must be provided to determine what the instruction is

and to generate the signals required to implement the instructions. Some instructions require an arithmetic or logical operation on data. Thus, the processor must contain an arithmetic logic unit (ALU). Since other instructions may involve temporary storage of intermediate results, various service registers are also provided. Furthermore, a method must be provided to sequence addresses through memory, which means that a program counter is necessary. Finally, address modification, such as indexing or subroutine location, requires various address registers or a register stack. All these elements, together with a timing and control section including I/O drivers and receivers, make up the major blocks of a microprocessor.

Figure 7. Elements Common to Most Microprocessors

Thus, a microprocessor is a very small and inexpensive processor contained in a single integrated circuit chip or a set of integrated

circuits. The set of integrated circuits refers to the microprocessor slice configuration in which 2-bit or 4-bit "slices" are paralleled to form larger data path systems. The single chip is called a monolithic microprocessor and it has a fixed width data path.

#### 3.2.1 Microprocessor Slice

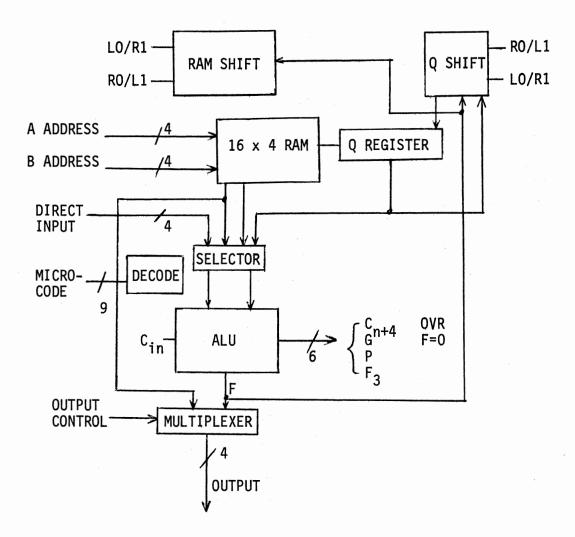

The microprocessors which have been designed to allow a modularity of data paths and whose control sections can support this modularity are considered to be in the "slice" configuration (14). The basic set of chips which together produce a processor include:

- Processor Slice Arithmetic unit which may be used in parallel to achieve the necessary data path width (ALU).

- Look-Ahead Carry Generator Capability of multilevel look-ahead for high-speed arithmetic operations over large word lengths.

- Microprogram Sequence or Control Unit -Control unit containing the instruction register, program counter, etc. depending on the particular manufacturer's system arrangement.

- 4. Read Only Memory (ROM) Memory where the microprogram is stored.

These chip sets may also include such extras as timing function chip, slice/memory interface (34), cyclic redundancy check (CRC) generator/ checker, serial/parallel first in-first out (FIFO) buffer, data path switch (DPS), p-stack, data access register (DAR) (25), multi-mode latch buffer, priority interrupt control unit, and inverting bi-directional bus driver (30).

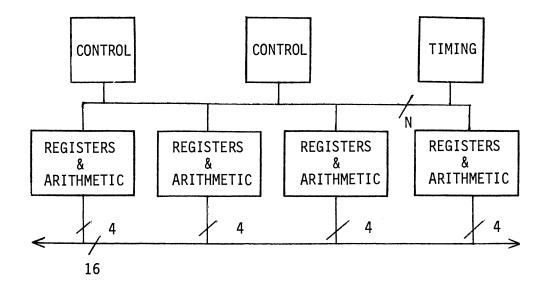

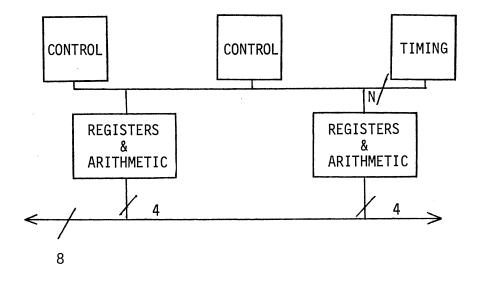

Figures 8 and 9 show 16-bit and 8-bit microprocessor chip level architecture where both microprocessors utilize the same chip set

Figure 8. 16-Bit Microprocessor (Each Block Represents a Chip)

Figure 9. 8-Bit Microprocessor (Each Block Represents a Chip)

.

with minor modifications to the control circuits. These systems are implemented with 4-bit microprocessor slices and each block represents a chip. The diagrams show that the slice microprocessor can be expanded to different data path lengths but at the expense of more chips and complexity.

#### 3.2.2 Monolithic Processor

The other category of microprocessors is where the design of chips has been optimized for a fixed data path of either 4, 8, 12 or 16 bits. These microprocessors usually combine both control and arithmetic functions into a single chip processor. Although these fixed data path processors have all the processor functions in one chip, they still may have peripheral chips such as read only memories, random access memories, interface adapters and communication interface adapters. On the other hand the single chip may be as complete as to have all control, arithmetic, memory and interface circuitry internal. Thus, in general this class of microprocessors will be called a monolithic processor although it may be part of a set of chips which together produce a working system.

These two categories, monolithic and slice, developed due to the different integrated circuit (IC) technologies. To understand the advantages and disadvantages between these two types of microprocessors, one must first understand the different IC technologies being used to manufacture microprocessors.

3.3 Integrated Circuit Technologies

At this point it is not necessary to discuss in detail the different

manufacturing techniques but instead to point out the distinguishing characteristics of the major technologies. MOS and bipolar are the two major groups under which the major technologies can be placed. MOS technology is based on the Metal-Oxide-Silicone-Field-Effect Transistor (MOSFET), while bipolar technology is based on the familiar epitaxial transistor.

#### 3.3.1 MOS Technologies

The most mature MOS process is PMOS or p-channel MOS. Most first generation microprocessors were PMOS. These were monolithic processors with slow speed capabilities. The major advantage of PMOS is high packing density, which is very important for LSI microprocessor development. These devices also have relatively low power consumption but require multiple power sources. PMOS thresholds, the highest of all existing technologies, often require level translation from transistor-transistor logic (TTL) (bipolar) levels to guarantee that minimum thresholds are achieved (7).

N-channel MOS or NMOS has the potential for significantly higher speed than PMOS microprocessors. N-channel devices require a positive gate-to-source voltage and have a threshold of 1-volt or less. Thus, they are more easily driven by TTL drivers which are pulled-up by resistors (15). Also n-channel outputs are easily made TTL compatible and n-channel silicon-gate MOS can run on a single 5-V power supply if required. These advantages are at the cost of increased fabrication complexity but with high packing density. There are many present generation NMOS monolithic microprocessors (9).

One of the latest MOS technologies is CMOS or complementary MOS.

CMOS uses n-channel devices as drivers and p-channel devices for the load. In this configuration only one transistor is on in the quiescent state producing low standby power dissipation. The advantages of CMOS include high noise immunity, wide tolerance to power supply variation, low temperature sensitivity and low power dissipation (2). The CMOS process also requires isolation between n-channel and p-channel devices which again increases the process complexity and cost. The lower packing density, the major disadvantage, has for the most part kept CMOS out of the LSI microprocessor applications, but next generation CMOS microprocessors are being developed by RCA and Intersil (16). Finally, SOS or silicon-on-sapphire is again an improvement in speed but at the cost of process complexity and cost. An SOS process type microprocessor is being developed by Inselek (16).

In general, the present MOS technologies are <u>relatively slow with</u> <u>high packing density</u> useful for single chip processors. The second major technology is bipolar, which can only be utilized in the slice configuration.

#### 3.3.2 Bipolar Technologies

The general characteristics of bipolar ICs are high speed, low packing density and higher cost. The higher cost results from the fact that the manufacture of bipolar circuits of all types involves five to seven masking steps to print the circuit patterns, as opposed to three for MOS (15). TTL is the most popular and most used bipolar logic family. The major advantages of TTL are the high speed, TTL compatibility, and a single +5-volt power supply. The major disadvantages are the high power consumption and the low packing density (7). The latest

improvement in TTL bipolar devices is the use of a Schottky diode clamp between the base and collector to keep the transistor from saturating. This has produced even better speed performance. Also, low power Schottky devices have been introduced which have about one-fifth the power consumption of regular TTL logic. Present generation slice microprocessors are generally low-power Schottky/TTL (16).

Next generation bipolar technologies include ECL and  $I^{L}$ . ECL or emitter coupled logic has ultra high speed, more power consumption, temperature sensitivity, nonstandard power supply voltages and complex interconnection requirements (7). However, high-transient switching currents are avoided reducing peak current requirements over similar TTL chips and thereby making power distribution problems somewhat easier. Motorola is presently developing an ECL 4-bit slice microprocessor (34).  $I^2L$  or integrated injection logic is seen as the process with the potential of giving the best of bipolar and MOS with good speed and high packing density (10).  $I^2L$  attacks the isolation requirement of bipolar devices by careful partitioning and judicious removal of unnecessary resistors. Using this technique, gates can be fabricated which require no isolation within the gate structure (7). At present,  $I^2L$  is not as fast as Schottky TTL and does not have the density to produce a monolithic processor. Texas Instruments is presently developing a 4-bit,  $I^2L$  slice microprocessor (16).

#### 3.3.3 Technology Comparison

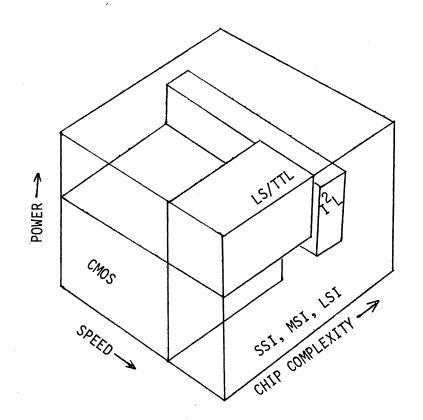

At this point it is possible to compare the different technologies being used to manufacture microprocessors. Figure 10 shows how CMOS,  $I^2L$  and LS/TTL fit into the speed/power/complexity picture. CMOS

standard family logic dominates the low-power corner while low-power Schottky TTL takes over when speed requirement goes into the megahertz (MHz) region (2). The new  $I^2L$  is expected to be only applicable at the LSI level of complexity, fitting somewhere between CMOS and LS/TTL with respect to speed/power.

Figure 10. Speed/Power/Complexity Comparison Source: (2), p. 26.

Finally, an overall technology comparison is made in Table III where each technology is rated from one to ten in each of the categories. Bipolar devices are seen as the best performance devices for

speed but have high power consumption and low packing density. The MOS devices have the opposite characteristics of low power consumption, low speed and high packing densities. This analysis has included the latest technologies being used in microprocessors but one must remember that final recommendations must be made using present generation processors or those in production with reasonable hardware and software document-ation. Many problems can arise from trying to use a processor before final specifications are documented, documentation errors are eliminated and software development has been completed to some degree. Thus, final recommendations as to which microprocessor to use in the fire control system will also be based on the extent of development of the chip set.

#### TABLE III

| Technology<br>Characteristic | PMOS | MOS<br>NMOS | CMOS | TTL E | BIPOLAI<br>ECL | <sup>R</sup> 1 <sup>2</sup> L |  |

|------------------------------|------|-------------|------|-------|----------------|-------------------------------|--|

| Speed                        | 4    | 7           | 5    | 8     | 9              | 6                             |  |

| Reliability                  | 6    | 9           | 8    | 5     | 4              | 5                             |  |

| Power Consumption            | 7    | 8           | 9    | 2     | 1              | 8                             |  |

| Density                      | 8    | 9           | 5    | 6     | 2              | 8                             |  |

| Complexity                   | 6    | 8           | 8    | 9     | 4              | 8                             |  |

| Process Maturity             | 9    | 7           | 6    | 9     | 8              | 6                             |  |

| Multiple Sourcing            | 9    | 8           | 2    | 8     | 2              | 1                             |  |

#### TECHNOLOGY COMPARISON

Source: (7), pp. 64-65.

From the preceding discussion we can see how the two types of microprocessors emerged. The monolithic processor was produced using MOS, but in order to obtain the better performance of the TTL technology, designers had to fragment the microprocessor chip into a slice due to the lower packing density of TTL. The slice configuration not only enables the use of less dense technologies but it also has important system differences. The ability to use faster technologies and the increased fexlibility of the slice configuration has led to the incredibly fast development of bipolar slice microprocessors.

#### 3.4 Monolithic and Slice Comparison

The slice microprocessor has introduced more versatility and greater speed than monolithic or fixed data path processors. The features which make it versatile are its expandable data path and microprogrammable capacity. The microprogram is a flexible firmware system which can be specifically designed to execute a special purpose macro-instruction set. A special purpose instruction set which is tailored to a specific application can be designed.

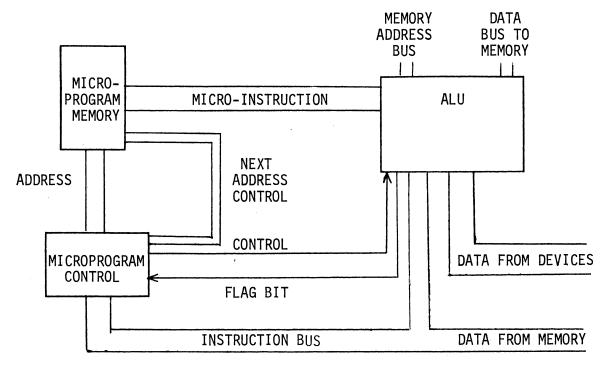

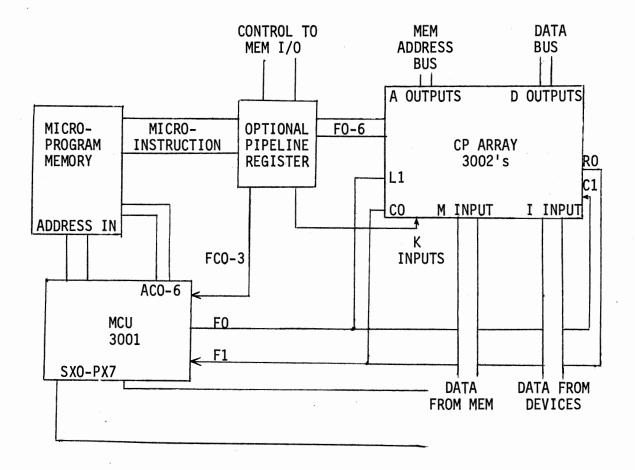

To better understand the microprogrammable system, a block outline of such a system is shown in Figure 11. Basically, the microprogram ROM and microprogram control unit replace the instruction decode logic shown in Figure 7. The macro-instruction is placed on the data bus from the memory. The micro-instruction address is determined by the macro-instruction and the previous micro-instruction. The microprogram then executes the macro-instruction. Conditional jump commands may be executed from the micro-instruction and feedback flag lines from the CP array. The macro-instruction execution ends with a micro-instruction

which returns microprogram address control to the macro-instruction bus which is the data bus from memory. During instruction execution the micro-instruction controls the central processing array.

Figure 11 describes the Intel 3000 series microprocessor slice which uses standard architecture except for the micro-instruction addressing scheme. The Intel set actually executes a jump the the next instruction where the more standard approach is to use a microprogram counter to sequentially execute the microprogram. In this manner, the macro-instruction or main program counter determines the beginning microinstruction address which is then incremented for the next address of microprogram.

Figure 11. Basic Microprogrammable System

The microprogram is usually stored in a read only memory (ROM) or a programmable read only memory (PROM). The micro-instruction program is usually not changed after it has been designed to execute a given instruction set and thus is stored in a nonvolatile memory. ROMs and PROMs also have much better access times and data storage density than random access memories or read/write memories. Macro-instruction programs can be stored in either RAM or ROM depending on the system. Some systems use a loader program stored in a ROM to automatically load the operating macroprogram into RAM. This is useful when the system has several software options or functions it can perform without hardware modification.

It is not manditory for slice microprocessor systems to have a macro-instruction set. The entire software system may be programed on the microlevel but this adds more complexity to the software design. In this application the micro-instructions provide an even faster system.

The slice configuration has been shown to be the higher performance system but it has two important disadvantages. First, it requires a much more complex hardware system with a higher package count, and second, it requires much greater software development effort. The manufacturers are unable to provide the same software support, such as assemblers and simulators, when the instruction set is variable. Also, the programming on the microlevel is on a lower level and thus more difficult than with assembler language.

Assemblers for slice microprocessors are being developed with a great deal of flexibility designed into them to handle the variable micro-instruction sets (28). This type of support for slice micropro-

cessors is new and will not be available for present use except for only one manufacturer, Intel. Naturally, there are no assemblers available for the macro-instructions since they are user defined.

The major system characteristics for slice and monolithic microprocessors are summarized in Table IV. There are exceptions to the characteristics given in Table IV. There are combinations of these two major groups, such as monolithic processors which are microprogrammable and slice processors which use MOS technology, but presently bipolar technology is confined to slice configurations. This table is a reflection of the present microprocessor trends. Future development will be trying to produce faster systems with both flexibility and simplicity. These systems will probably use bipolar technology with improved speed and packing density.

#### TABLE IV

#### SUMMARY OF THE DIFFERENCES BETWEEN THE TWO TYPES OF MICROPROCESSORS

#### Monolithic Processors

- Main processor functions in a single chip a) b) Fixed instruction set Better software support c) MOS technology - slower cycle times d) Simpler system design - smaller chip count e) f) Fixed data path - requires use of software for expansion Slice Microprocessors Chip set centered around processor slice a) Microprogrammable - variable macrolanguage b) Less software support c) Bipolar technology - fastest cycle times, more power d)

- Complex system design high chip count e)

- More versatile expandable data path f)

## 3.5 Previous Work in Evaluation of Microprocessors for Military Applications

A paper by Gregory Fox (6) considers the evaluation and comparison of the performance of commercial microprocessors and a discussion of potential military system applications. The paper begins by showing the exponential growth rate of available microprocessors and then points out the difficulty of selecting the best microprocessor for a given application. The difficulty arises when trying to evaluate scaled down, integrated versions of general purpose computer CPUs with documentation consisting of 20 to 30 pages of specifications. Microprocessors cannot be effectively evaluated on a data sheet basis.

Fox states that the performance of a microprocessor is a function of three factors: (1) cycle time, (2) number of cycles for each instruction and (3) the power of the instruction set. As a measure of these three factors, the author used throughput to compare different types of microprocessors. In order to obtain an estimate of a processor's throughput from the instructions' execution times, an instruction mix must be assumed. Table V shows the instruction mix assumed by the author. The instruction mix is a function of the microprocessor application and this mix is for an avionics fire control system. The mix is determined from the percentage use of a certain instruction and that instruction's execution time. It must be noted that this is not the same type of fire control system but is still an interesting evaluation.

Results from a comparison of an 8-bit, single chip, NMOS and a 16-bit, PMOS, slice microprocessor show that better throughput was obtained from the 16-bit slice. Although the 8-bit processor had a

faster cycle time, the use of double precision arithmetic reduced the throughput below that of a slower 16-bit machine designed with slice processors. One important advantage of the slice machine was having both multiply and divide instructions where the 8-bit processor did not. The author points out that the 16-bit processor's multiply requires fifty percent longer than the time indicated in the specification sheet. A further advantage of the 16-bit machine was the shift instruction useful for scaling incoming data. The 8-bit machine only had a rotate instruction which wraps the shifted bit around to the other end. Thus, processors with higher hardware bit accuracy which have the required instructions can overcome smaller but faster machines.

#### TABLE V

| 29.2<br>18.1                                          |

|-------------------------------------------------------|

| 14.1<br>9.4<br>8.8<br>5.4<br>5.2<br>4.0<br>2.5<br>1.3 |

|                                                       |

#### INSTRUCTION MIX FOR AVIONICS FIRE CONTROL

Source: (6), p.7.

The author cautions potential users about analyzing only instruction times or throughput. These studies are crude and only give rough ideas of a processor's usefulness for a particular application. Further study is required of memory addressing options, number and flexibility of the registers, and the variety of branch conditions available. These are factors which require either actual programming or a great deal of computer experience to evaluate.

Finally, the author does a comparison between different types of processors which is shown in Table VI. He shows that the bipolar slice machine has a considerably better throughput than any other processor configuration. The author also estimates the required throughput for a ground based fire control system as about 10 to 100 KOPS (thousand operations per second).

#### TABLE VI

| Microprocessor           | Word Length<br>(bits) | Throughput*<br>(KOPS) |

|--------------------------|-----------------------|-----------------------|

| 8-bit NMOS               | 8                     | 35                    |

| 8-bit NMOS<br>Byte Slice | 16**<br>16            | 17                    |

| Byte Slice Bipolar       | 16                    | 400-500               |

|                          |                       |                       |

#### AVAILABLE MICROPROCESSOR PERFORMANCE

\* Using Instruction Mix in Table V

\*\* Double Precision Arithmetic

Source: (6), p. 8.

# 3.6 Reduction of Microprocessor Spectrum for Analysis

The slice configuration processors give the best speed performance due to system and technology advantages, which is the major system requirement. The major disadvantages are higher power consumption, lack of software support, increased system complexity, and a large chip count. The only one of these disadvantages which will not affect the present problem significantly is the power consumption. However, a monolithic microprocessor would be considerably slower with a maximum of a 16-bit data path configuration. With a slice microprocessor it is conceivable to use eight 4-bit slices or sixteen 2-bit slices to form a 32-bit hardware data path system. This size system may be approaching a minicomputer in hardware and software design complexity. Thus, the best solution seems to be to use the faster slice configuration with at least a 32-bit data path.

An analysis of the available slice type microprocessors is now required. Because of the expected complexity of a slice configuration of 32 bits, an analysis of a 16-bit monolithic processor will also be done. The limited manpower and resources of this project may become the determining factor. So, one must determine if the slice configuration speed advantage can warrant the increased design effort, or if the monolithic microprocessor system is even a working alternative due to its lack of speed. Chapter IV will be a study of the available microprocessors including the newest of the slice microprocessors and one or two 16-bit monolithic processors. The emphasis is on the slice processors for they seem to be the best hope for a microprocessor system solution to the fire control problem.

#### 3.7 Conclusion

In conclusion, we have introduced the basic concepts of microprocessors showing the effect integrated circuit technologies have had in producing two different types of microprocessors. These two types have been compared and a selection of an expandable data path slice microprocessor has been made based primarily on its speed advantages over monolithic processors. Chapter IV has been allocated to a complete study of the most recent slice microprocessors. Secondly, a monolithic 16-bit processor will be included for purposes of determining if a monolithic microprocessor is a viable alternative in case a large slice system demands excessive manpower.

#### CHAPTER IV

## FINAL SELECTION FROM A SURVEY OF AVAILABLE MICROPROCESSORS

#### 4.1 Microprocessor Analysis

Analysis to determine the best microprocessor for a given application is very difficult unless the system is restricted by some special characteristics such as size or power consumption. The present major consideration is speed, the most difficult of all parameters to precisely measure for a microprocessor unless the exact application is programmed on each processor being considered through benchmark programs. This difficulty arises in trying to evaluate the many parameters which determine speed. A microprocessor's speed is a function of how it is used, software arrangement and chip architecture. One cannot determine the fastest microprocessor directly, but can, through the evaluation of its architecture, determine the processors with the most potential.

The factors which are going to be considered in the determination of a processor's potential include the number of registers or length of stack, the instruction set, cycle time, instruction average execution times, subroutine linkage facilities, external flags and general architectural characteristics. These factors will help determine if the processor can handle the required throughput. Other important factors include chip set complexity, system level of implementation and support software. These all determine manpower requirements. The system level

of implementation refers to whether one designs with large system blocks or with less functional but more flexible small system blocks. Also, the importance of software support cannot be over stressed. This type of software includes assemblers, editors, simulators, and loader programs. Assemblers are required in all phases of firmware development and simulators enable the parallel development of hardware and firmware. Support software when not supplied by the manufacturer becomes a necessary burden upon the designers during system implementation.

Extensive throughput analysis will not be done for the selection process of the slice microprocessor. This type of analysis requires the knowledge of each instruction's execution time and the instruction mix. To obtain instruction execution times would require the microprogramming of a predesigned macro-instruction set. The results derived giving throughput of each processor would be related to its cycle time and the previously discussed characteristics. Thus the conclusions reached from the throughput analysis would probably be the same as the more general analysis of the architecture. Other factors such as developmental manpower requirements are just as important and make the slightly more accurate throughput analysis unnecessary.

Also the selection analysis will not be a process of finding the processor which just meets the speed requirements. The firmware development will be simplified as the percent utilization of the processor's available speed is decreased. A processor with 50 percent utilization requires less programming effort and memory than one with 80-90 percent utilization. Slower processors will be considered only when other unique advantages are obtained from their use.

Previous analysis has led to the selection of a 32-bit bipolar

slice system. This decision is based on the improved speed of the 32bit hardware versus a 16-bit double precision arithmetic system and the decreased cycle time of bipolar technology. The advantages of the monolithic systems, with better software support and smaller chip counts leading to less manpower requirements, have been discussed. The slower speed of these processors reduced the probability of their use, but the necessity of further study was shown. Thus this chapter will include a feasibility study of the use of a monolithic processor and a study of available slice microprocessors leading to the selection of the best slice processor.

Also, from the results of Chapter II, the extensive use of a multiply instruction was seen. Because of the long execution time of a firmware multiply instruction, the use of a hardware multiplication system has been deemed useful to reduce the system speed requirements. The first section of this chapter will deal with hardware multiplication so that the following analysis of microprocessors may use these results for execution time estimates.

#### 4.2 Multiplication with Peripheral Hardware

There are many methods to achieve hardware multiplication which give different ratios of the hardware versus speed tradeoff. Systems which use readily available large scale integration (LSI) and medium scale integration (MSI) circuits to improve the existing processor's arithmetic logic unit (ALU) multiplication ability give the lower speed improvement with a small cost in hardware. At the other end of the spectrum is the specialized multiplication chip which requires little or no ALU functions to give very fast execution times but with increased

hardware cost. The alternative to hardware multiplication is the microprogram multiply which requires  $170 \text{ microseconds } (\mu s)$  for the IMP-16C and 30 µs for the Intel 3000 series for two 16-bit operands. These are the execution times which must be significantly reduced to justify the use of a hardware multiply.

Schmid (17) discusses hardware multiplication systems and in particular a system for the IMP-16C. His application requires no special purpose chips and improves the multiplication time to 23  $\mu$ s with a 6.5 megahertz (MHz) clock operation. The analysis and application of his system is given in detail. The added circuit blocks, multiplication register and control signal generator, are described along with the software and interface problems. Although Schmid's system has a good balance between hardware and speed improvement, it is more complex and slower than specialized chip multiplication.

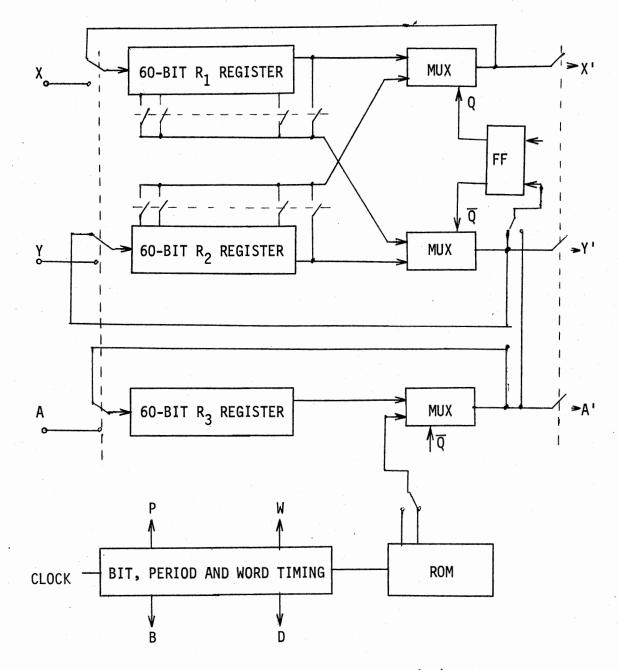

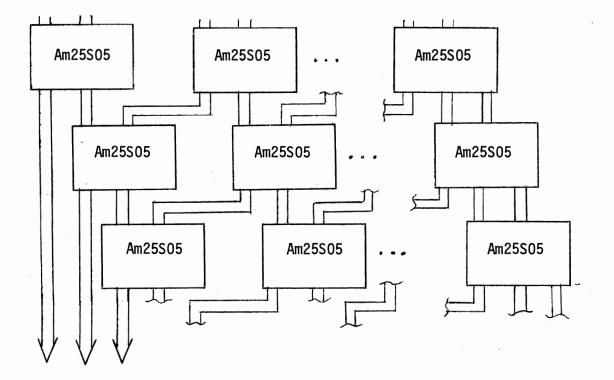

An example of specialized chip multiplication is the Advanced Micro Devices' (AMD) Am25S05 four-by-two two's complement multiplier. It is especially useful for the present application since it is expandable to any array size, available in the military temperature range and is very high speed. Flexibility in the hardware-speed tradeoff is also given by use of different chip configurations. Speed can be increased by use of look-ahead carry chips as shown in Table VII.

Other configurations which are not given in Table VII and which are time sequenced arrangements are discussed by Schmid (17) or by Ghest (8) in an AMD application note. Time sequenced arrangements are slower and more complicated but require less hardware.

The hardware increase is sizeable when compared to a microprocessor which may consist of 30-60 packages without the multiplication hardware.

Also the package count in the table does not include any holding registers that may be required or any clock control circuitry for stopping the clock during multiplication if the cycle time is less than the multiplication delay time. On the other hand, the speed of the slowest configuration is  $0.315 \ \mu$ s, almost 100 times faster than the Intel microprogrammed soltuion which was for a 16-bit operand.

#### TABLE VII

#### Am25S05 CONFIGURATIONS

|    | Configuration                                                                                                  | Array Size<br>(bits) | Total Time (μs)<br>for Multiplication | Package<br>25S05 |    |

|----|----------------------------------------------------------------------------------------------------------------|----------------------|---------------------------------------|------------------|----|

| 1. | Parallelogram<br>carries stay in<br>same row                                                                   | 32 x 32              | .315                                  | 128              | 5  |

| 2. | Parallelogram -<br>carries from lower<br>order multiplica-<br>tion skip to<br>alternate rows<br>where possible | 32 x 32              | .187                                  | 128              | 15 |

| 3. | Split into two<br>parts which are<br>added with high-<br>speed carry look-<br>ahead adder                      | 32 x 32              | .152                                  | 128              | 32 |

Caution must be used when comparing the 0.315  $\mu$ s time to other execution times. This time does not include the time required to input the operands and output the result. This time will vary according to

the microprocessor being used. This chip does produce a significant increase in speed without added system complexity and with little software requirements from the ALU other than set-up type instructions. The application of the Am25S05 is uncomplicated but the hardware increase is significant.

The parallelogram configuration, the first configuration of Table VII, is shown in Figure 12. This configuration requires the lowest number of additional chips of the non-sequenced configurations and is simpler to apply than the sequenced configurations. For these reasons it is probably the best choice of the multiplication hardware systems if the 128 additional required packages are acceptable.

Figure 12. Parallelogram Configuration

#### 4.3 Fixed Data Path Microprocessors

Three representatives of 16-bit fixed data path microprocessors are compared in Tables VIII, IX and X. Table VIII gives an architecture and general characteristics comparison while Tables IX and X give the hardware and software support comparisons, respectively. This is not a complete listing of all 16-bit fixed data path microprocessors but only a representation. The total number of 16-bit processors is not large since the greatest number of fixed data path microprocessors are of the 8-bit structure. The National Semiconductor's IMP-16 is actually designed around a 4-bit slice microprogrammable chip set. Offered as the IMP-16, it is a 16-bit fixed data path, fixed instruction set processor and is thus put into this category.

This comparison again shows the advantage of the lower development manpower requirements due to the hardware and software support. All three microprocessors have resident and cross assemblers, debug, diagnostic, and edit programs and are available on a predesigned card. This type of support is almost necessary for small quantity development programs.

The IMP-16 processor also shows what most experts believe is going to be the growing trend in processor development. This is the predesign of slice microprocessor boards with fixed instruction sets enabling the manufacturers to develop the required support products. As certain MOS chips become established, manufacturers could offer transistor-transistor logic (TTL) slice equivalent systems where improved speed is desired. Engineers could utilize previous experience with the well established chip and save the cost and time of a new learning process. Certain

#### TABLE VIII

#### Manufacturer National National General Model Semiconductor Instrument Semiconductor IPC-16 (PACE) CP-16007 IMP-16 Genera1 16-bit CPU 16-bit CPU 4-bit slice structure Technology PMOS NMOS PMOS No. of devices 1 1 per CPU CPU size (pins) 40 40 24 -3, 5, 12 -12, 5 Supply voltage -12, 5 CPU pwr. 700 750 dissipation (mW) Data word size 8 or 16 16 16 (bits) Instruction word 10, 20, 30 16 16 size (bits) Directly addres-65K 65K 65K sable instruction words (no.) Clock frequency 2 MHz/205 MHz/20 700 KHz/40 (Hz/phases required) Register to 8 2.4 4.6 register add time $(\mu s/data word)$ No. of registers Arithmetic 0 0 4 Index 0 0 0 4 General 8 0 purpose Return stack 10 x 16 External RAM 16 x No. of bits (no. x bits) Interrupts Standard Standard Standard Type Vectored, Vectored. 1/2/2 Level 6 Level multilevel Direct memory Optional Standard **Optional** access BCD arithmetic Standard No No (hardware) Microprogrammable No Yes No -55°C to 85°C Extended temperature range available Delivery start 3 Qtr. 75 3 Qtr. 74 1 Qtr. 73 (qtr. year)

#### **16-BIT MICROPROCESSORS**

|  | TAB | LE | IΧ |

|--|-----|----|----|

|--|-----|----|----|

| HARDWARE | SUPPORT |

|----------|---------|

|----------|---------|

| Manufacturer<br>Model                                                | National<br>Semiconductor<br>IPC-16 (PACE) | General<br>Instrument<br>CP-1600 | National<br>Semiconductor<br>IMP-16 |

|----------------------------------------------------------------------|--------------------------------------------|----------------------------------|-------------------------------------|

| Processor cards (CPU                                                 | Yes                                        | Yes                              | Yes                                 |

| system on a card)<br>Prototyping system<br>(hardware and software    | Yes                                        | Yes                              | Yes                                 |

| development system)<br>In-system emulator<br>(tests system in place) | No                                         | No                               | No                                  |

## TABLE X

### SOFTWARE SUPPORT

| Manufacturer<br>Model                                                                            | National<br>Semiconductor<br>IPC-16 (PACE) | General<br>Instrument<br>CP-1600      | National<br>Semiconductor<br>IMP-16 |

|--------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------------------------|-------------------------------------|

| Resident assembler<br>Cross assembler<br>Simulator<br>High level language<br>Programs (firmware) | Yes<br>FORTRAN IV<br>No<br>SM/PL           | Yes<br>FORTRAN IV<br>FORTRAN IV<br>No | Yes<br>FORTRAN IV<br>No<br>SM/PL    |

| Debug<br>Diagnostic<br>Edit                                                                      | Yes<br>Yes<br>Yes                          | Yes<br>Yes<br>Yes                     | Yes<br>Yes<br>Yes                   |

options can be made available such as extended instruction sets through additional boards or chips. Even special purpose microprogrammed instructions would be available by working with the manufacturer. These are precisely the advantages which prompted the selection of the IMP-16 for the feasibility study of the use of a 16-bit fixed data path microprocessor in the fire control system. The IMP-16 has an optional extended instruction set which includes multiply, divide, and double precision add and subtract. A total of 43 basic instructions are offered with an optional 17 instructions. See Appendix A. The IMP-16 is also a well established system initially being offered in the first quarter of 1973.

#### 4.3.1 Feasibility of Using the IMP-16C

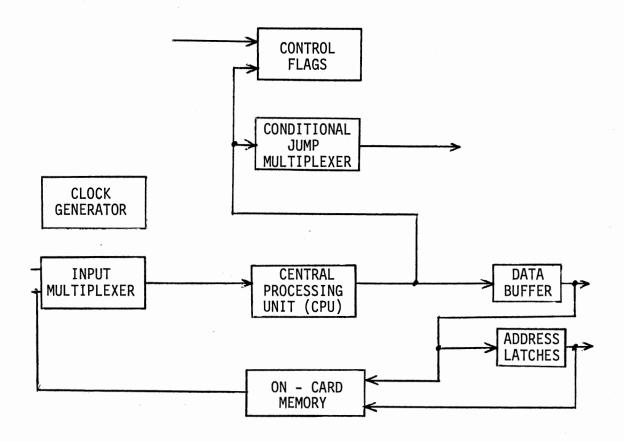

The IMP-16C is a microprocessor card assembly with the functional blocks as shown in Figure 13. The card assembly is a self-contained 16-bit parallel processor with 256 16-bit words of read/write memory. The off-card memory may be expanded in increments of 4,096 16-bit words to provide a total memory of 65,536 words. Two new versions of the IMP-16C are being offered, the IMP-16C/200 and the IMP-16C/300. The new versions have one extra control read only memory (CROM) for purposes of expanding the basic instruction set. The IMP-16C/200 leaves the socket empty so the user may microprogram desired instructions while the IMP-16C/300 comes with a pre-programed CROM for the extended instruction set. The IMP-16P is also available which is a complete microcomputer.

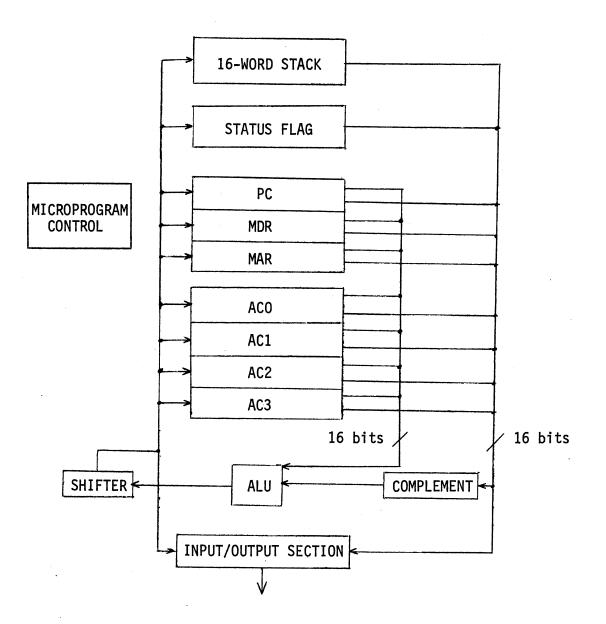

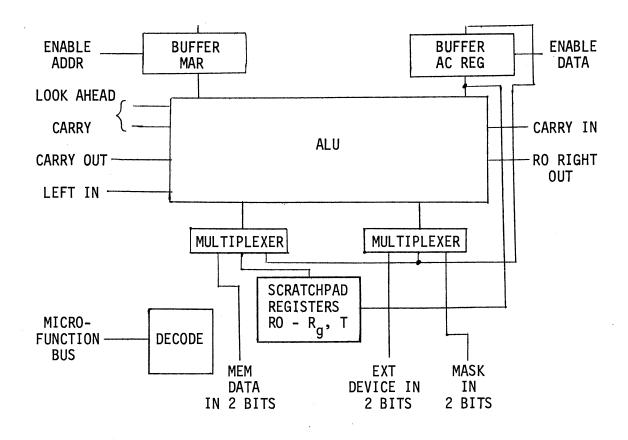

The architecture of the register and arithmetic logic unit (RALU) is straightforward as shown in Figure 14. There are four working reg-

isters (AC), AC1, AC2, AC3), a status flag register, a program counter (PC), memory data register (MDR), a memory address register (MAR) and a 16-word register stack for subroutine and interrupt return addresses. Two of the accumulator registers (AC2 and AC3) are used as index registers. The status flag register is updated by hardware and includes a link bit, overflow bit, carry bit and 13 general-purpose flag bits. The PC, MDR and MAR serve hardware functions and are not directly available to the programmer.

Figure 13. IMP-16C Card Assembly Block Diagram

Figure 14. RALU Block Diagram

There are three addressing modes: direct, relative and index. One may address direct to only the base page (0 to 255). To address above 255 one uses either relative, which adds or subtracts from the PC, or index, which adds the contents of the desired index register to the PC. The above system is implemented with a 2-bit mode field and a displacement field.

The basic and extended instruction sets are shown in Appendix A. The execution times are calculated for purposes of throughput analysis. These calculations are based on a 1.4  $\mu$ s micro-instruction cycle time and a 1.75  $\mu$ s read/write memory cycle time. The execution time is thus calculated using

$$t_{ex} = (1.4) \times (Number of execution cycles) + (1.75 - 1.4) \times (Number of read/write cycles) \mu s(1)$$

or

$$t_{ex} = (1.4) \times (\underset{execution cycles}{^{\text{Number of}}}) + 0.35 \times (\underset{read/write cycles}{^{\text{Number of}}}) \mu s \qquad (2)$$

Using the instruction mix derived in Chapter II, the critical worst case execution time is calculated below for two cases. These calculations are a very rough first approximation effort.

#### Case 1 Firmware Multiply Instruction

| 16-bit multiply: (172 $\mu$ s) x 1100 multiplies/cycle         | = | 189  | ms* | (3)        |

|----------------------------------------------------------------|---|------|-----|------------|

| Double precision add-subtract: $(18.2 \ \mu s) \times 900$     | _ | 10   |     | (1)        |

| instr./cycle                                                   |   | 16   | ms  | (4)        |

| Firmware 16-bit DIV: $(223.65 \ \mu s) \times 14$ instr./cycle | = | 3    | ms  | (4)<br>(5) |

| Trigonometric instr. (Cordic): $(87 \ \mu s) \times 7$         |   |      |     |            |

| instr./cycle                                                   |   | .609 | ms  | (6)<br>(7) |

| Memory access instr.: $(8 \ \mu s) \times 4000$ instr./cycle   | Ξ | 32   | ms  | (7)        |

| Total                                                          |   | 241  | ms  |            |

\* ms = millisecond

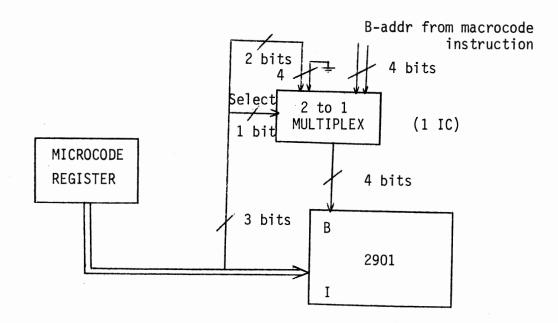

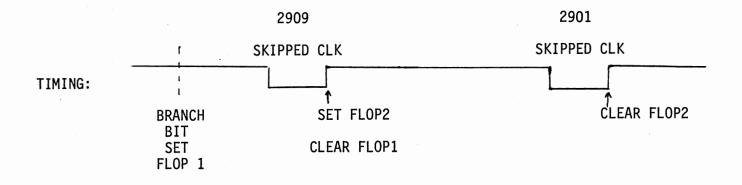

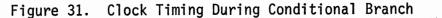

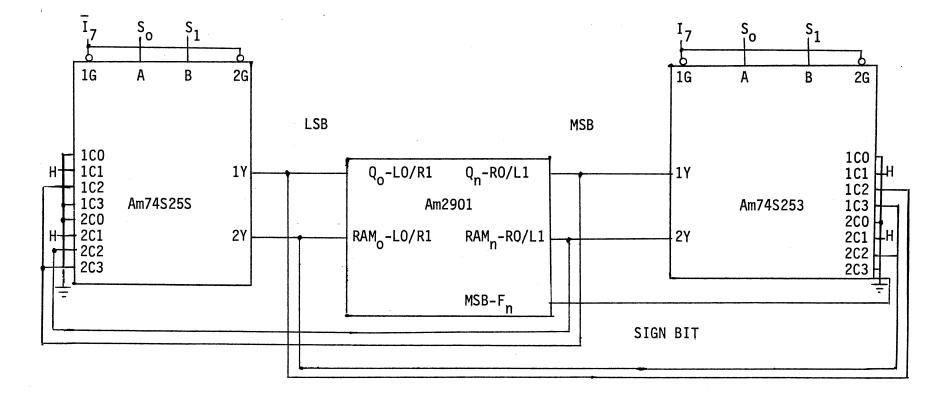

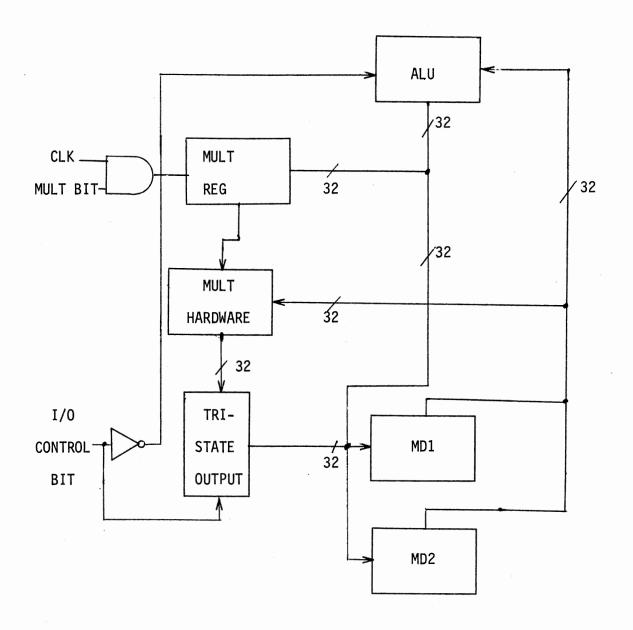

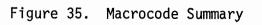

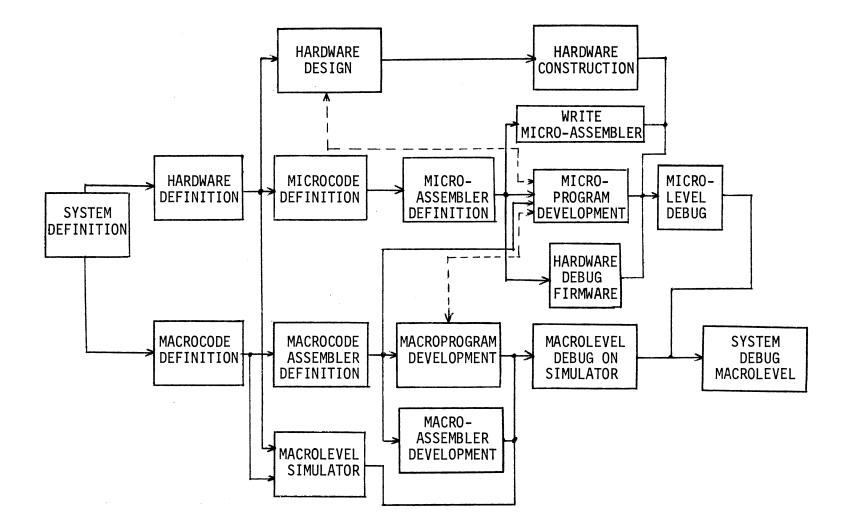

#### Case 2 Hardware 32-bit Multiply