A MICROPROGRAMMED SIMULATION SYSTEM FOR GENERAL PURPOSE REGISTER AND FIXED PURPOSE REGISTER MINICOMPUTERS

By

GLENN RAY THOMPSON

Bachelor of Science

Oklahoma State University

Stillwater, Oklahoma

1974

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of MASTER OF SCIENCE May, 1976

Thesis 1976 T 471m 1. I and the second С¢ 1 • nan an Star a∳<sup>2</sup>r i si 1 • • • , ÷ 2 S 4 . . . .

OKLAHOMA STATE UNIVERSITY LIBRARY

AUG 26 1976

A MICROPROGRAMMED SIMULATION SYSTEM FOR GENERAL PURPOSE REGISTER AND FIXED PURPOSE REGISTER MINICOMPUTERS

Thesis Approved:

Thesis Adviser Dean of Graduate College the

.

#### PREFACE

This thesis is a description of a microprogrammed simulation system for general purpose register and fixed purpose register minicomputers. Such systems aid in the efficiency in which assembler programs are developed for certain classes of minicomputers. The description is designed to instruct the reader in microprogramming techniques and how these techniques might be implemented.

The author wishes to express his appreciation to his major advisor, Dr. Donald D. Fisher, for his guidance and assistance throughout this study. Appreciation is also expressed to other committee members, Dr. George E. Hedrick and Dr. James R. Van Doren, for their invaluable assistance in the preparation of the thesis.

Finally, special gratitude is expressed to my wife, Vicki, for her understanding and encouragement.

# TABLE OF CONTENTS

| Chapter |                                           |   |   |   |     |   | Page |

|---------|-------------------------------------------|---|---|---|-----|---|------|

| Ι.      | INTRODUCTION                              | • |   | • |     | • | 1    |

| ±•      |                                           | • | • | • |     | • | -    |

| II.     | MICROPROGRAMMING                          | • | • | • | ••  | • | 6    |

|         | Introduction                              |   |   | • |     |   | 6    |

|         | Fixed Instruction Computers               |   |   |   |     |   | 7    |

|         | Microprogrammed Computers                 |   |   |   |     |   | . 9  |

|         |                                           | • |   | • | ••• | • | •    |

| III.    | THE CROSS ASSEMBLER                       | • | • | • | • • | • | 16   |

|         | Scanner                                   | • |   | • |     | • | 17   |

|         | Symbol Table Construction and Processing. |   | • |   |     | • | 18   |

|         |                                           |   |   |   |     |   | 20   |

|         | Label Field                               |   |   |   |     |   | 20   |

|         | Mnemonic Op Code Field                    |   |   |   |     |   | 21   |

|         | Operand Field.                            |   |   |   |     |   | 21   |

|         |                                           |   |   |   |     |   | 21   |

|         | Error Detection                           |   |   |   |     |   | 26   |

|         | Assembler Output                          |   |   |   |     |   | 27   |

|         | Loader                                    |   |   |   |     |   | 27   |

|         |                                           |   |   |   |     |   |      |

| IV.     | THE INTERPRETER                           | • | • | • | ••  | • | 28   |

|         | Instruction Fetch and Execution           |   | _ |   |     | _ | 28   |

|         | Machine Instruction Decoding              |   |   |   |     |   | 32   |

|         | Error Detection                           |   |   |   |     |   | 42   |

|         | Debugging Aids                            |   |   |   |     |   | 42   |

|         | Other Simulation Systems                  |   |   |   |     |   | 43   |

|         |                                           |   | • | • |     | • |      |

| V.      | USERS MANUAL                              | • | • | • | ••  | • | 44   |

|         | Tritial Machine Decemintian               |   |   |   |     |   | 44   |

|         | Initial Machine Description               |   |   |   |     |   | 48   |

|         | The Cross Assembly Language               |   |   |   |     |   | 48   |

|         |                                           |   |   |   |     |   | 48   |

|         | Addressing Specifications                 |   |   |   |     |   | 40   |

|         | Operands                                  | ٠ | • | • | • • | ٠ | 51   |

|         | Pseudo Operations                         |   |   |   |     |   | 52   |

|         | Assembly Error Messages                   |   |   |   |     |   | 52   |

| 1       | Control Cards and JCL                     |   |   |   |     |   | 54   |

|         | Deck Setup                                | • | • | • | • • | ٠ | 74   |

| VT.     | SUMMARY AND FURTHER STUDY                 |   |   |   |     | - | 56   |

# Chapter

| Chapter             |             |        |       |       |       |       |         |       | Page |

|---------------------|-------------|--------|-------|-------|-------|-------|---------|-------|------|

| A SELECTED BIBLIOGH | RAPHY       | • • •  | • • • | •     | • • • | • • • | •       | • •   | 58   |

| APPENDICES          | • • • • •   | • • •  | • • • | • •   | • • • |       |         | • •   | 60   |

| APPENDIX A - LIST ( | OF SYMBOLS  | • • •  | • • • | • • • | • • • | • • • | •       | • •   | 61   |

| APPENDIX B - LOGIC  | BLOCK DIAG  | RAM .  | • • • | • •   | • • • |       |         | • •   | 64   |

| APPENDIX C - SAMPLE | E RUNS AND  | OUTPUT |       | • •   | • • • | • • • | • • • • | • • • | 70   |

| APPENDIX D - SYSTEM | IS PROGRAMM | ERS GU | IDE . | • •   | • • • | • • • |         | •     | 103  |

# LIST OF TABLES

| Table |                                                                                   | Page |

|-------|-----------------------------------------------------------------------------------|------|

| I.    | Description of State Transitions for Figure 1                                     | 5    |

| II.   | Control Lines for Figure 4                                                        | 12   |

| III.  | Operand Field Syntax for General Purpose Register<br>Systems                      | 22   |

| IV.   | Operand Field Syntax for Fixed Purpose Register<br>Systems                        | 23   |

| ۷.    | Conditional Statements for General and Fixed Purpose<br>Register Systems          | 35   |

| VI.   | Input Bus Scheme for General Purpose Register Systems                             | 36   |

| VII.  | Special I/O, Debug and Operate Functions for General<br>Purpose Register Systems  | 37   |

| VIII. | Input Bus Connections for General and Fixed<br>Purpose Register Systems           | 37   |

| IX.   | Output Bus Connections for General Purpose Register<br>Systems                    | 38   |

| Χ.    | Input Bus Scheme for Fixed Purpose Register Systems                               | 39   |

| XI.   | Special I/O, Debug and Operate Functions for Fixed<br>Purpose Register Systems    | 40   |

| XII.  | Output Bus Connections for Fixed Purpose Register<br>Systems                      | 41   |

| XIII. | Implementation of Add Register to Register and<br>Branch on Zero                  | 41   |

| XIV.  | Implementation of Load Accumulator From Index<br>Register and Branch on Negative  | 42   |

| XV.   | Input Card Formats for Machine Description of<br>General Purpose Register Systems | 45   |

Table Page Input Card Formats for Machine Description of Fixed XVI. 46 XVII. Addressing Modes for Fixed Purpose Register Systems . . . 49 XVIII. Field Boundaries for Assembler Language Statements 50 XIX. Field Boundaries for Assembler Language Statements 50 Assembler Language Operand Specifications . . . . . . . . XX. 51 XXI. Assembly Error Messages . . . . . . . . . . 53 . . . .

# LIST OF FIGURES

| Figur | e                                                                                          | Page |

|-------|--------------------------------------------------------------------------------------------|------|

| 1.    | State Transitions of the Simulation Process                                                | 4    |

| 2.    | Simplified Block Diagram for Fixed Instruction Stored<br>Program General Purpose Computers | 8    |

| 3.    | Simplified Block Diagram for Microprogrammed Computers                                     | 10   |

| 4.    | A Simple Fixed Purpose Register Machine                                                    | 11   |

| 5.    | A Simple Simulator                                                                         | 15   |

| 6.    | FSA for Recognizing Label Identifiers                                                      | 17   |

| 7.    | The Identifier Symbol Table                                                                | 19   |

| 8.    | Node Formats for Symbol Table                                                              | 20   |

| 9.    | Grammar for Parsing Operand Fields of General Purpose<br>Register Systems                  | 24   |

| 10.   | Grammar for Parsing Non-operate Operand Fields of<br>Fixed Purpose Register Systems        | 25   |

| 11.   | Grammar for Parsing Register Operate Operand Fields<br>of Fixed Purpose Register Systems   | 26   |

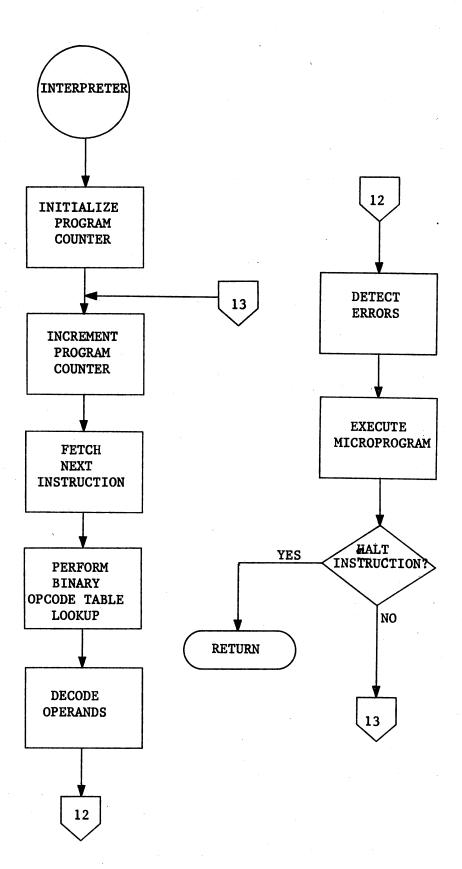

| 12.   | Instruction Fetch and Execution Cycle                                                      | 29   |

| 13.   | Machine Instruction Formats for General Purpose<br>Register Systems                        | 31   |

| 14.   | Machine Instruction Formats for Fixed Purpose<br>Register Systems                          | 32   |

| 15.   | The Microinstructions for the Microprogrammable<br>Pseudo-machine                          | 33   |

| 16.   | Register and Bus Configuration for the Microprogrammable<br>Pseudo-machine                 | 34   |

| 17.   | Sample Program Setup                                                                       | 54   |

Figure

Page

#### CHAPTER I

#### INTRODUCTION

This thesis is a presentation of a method for developing a microprogrammed simulation system for minicomputers chosen under two classifications (14): general purpose register systems and fixed purpose register systems. Of the classes of minicomputers, these two represent the largest number of minicomputers available on the market today. They are also more closely related than any other two classes of minicomputers.

The first classification consists of minicomputers with a General Purpose Register (GPR) structure. The hardware registers of this type of machine serve many functions. Two functions the registers serve are (1) index registers and (2) general purpose accumulators. In one section of an assembler program, a register may be used as an index register to obtain the effective address of an operand, which is to be used in computations of some form; and in that same section of the program the register may be used to contain the operand itself. Examples of machines with this hardware register configuration are the MODCOMP II and III (15) and the INTERDATA 7/16 (10). A subset of the instructions for the INTERDATA 7/16 has been defined for simulation purposes and is contained in Appendix C along with a sample assembler program run.

Minicomputers in the second classification have a Fixed Purpose

Register (FFR) structure. There are several different types of hardware registers used in such systems. Accumulators are designed to hold intermediate results of computations and serve a significant role in the Arithmetic Logic Unit (ALU). Index registers are used to determine the effective address of some operands and serve as an important tool in the use of data arrays as a primary data structure at the machine level. Extension registers, usually of one bit, serve as overflow or carry indicators for the accumulators. Depending upon the particular system, there may be many more registers that serve various purposes. Examples of machines with this hardware register configuration are the HEWLETT-PACKARD 2114A, 2115A, and 2116B (1), the VARIAN 520/1 (20) and the INTERDATA Model 1 (9). A subset of the set of instructions for the HEWLETT-PACKARD 2114A has been defined for simulation purposes and is contained in Appendix C along with a sample assembler program run.

Simulators can be written for a large number of minicomputers in high level languages, such as FORTRAN or PL/I, on large host computers. This facilitates the incorporation of more sophisticated diagnostics into the simulation system, thereby decreasing the amount of debugging time required for any particular assembler language program. One reason this sophistication is usually not built into most minicomputer translation systems is the relatively small amount of main core storage available to the system. With this restriction, the producers of systems software must keep the size of the translators down to a minimum.

Minicomputers are playing an increasingly more important role in the computing industry. This is one reason for the development of

more generalized simulation systems. Minicomputers are used for such purposes as laboratory machines to monitor experiments, interface devices in computer networks and interface devices between large computer systems and peripheral devices. In some cases they are even used for automobile care and maintenance. Their versatility is mainly due to the fact that most minicomputers are bus oriented machines. A data bus allows information from external devices or internal registers to be transferred to logic units and back again along a single data path. This helps to lower hardware costs and make the system more flexible. It is not unusual for as many as 256 external devices to be connected to a single data bus.

An introduction to the subject of microprogramming is given in Chapter II. Background information and an illustration of a small microprogrammed system are discussed. An explanation of some of the differences between fixed instruction computers and microprogrammed computers is also given.

The simulation system itself is composed of a cross assembler and an interpreter. The two pass assembler is described in Chapter III. The scanner for detecting labels and operation codes, pass I symbol table construction and object (machine) code generation in pass II are discussed. Assembly time error detection and diagnostics are also discussed.

The object code generated by the assembler is input to the interpreter. The interpreter is actually a microprogrammable pseudo-machine for which microprograms are designed to simulate instruction execution for a desired system. Pass II of the assembler loads the simulated memory with the generated object code and it is from this simulated

memory that the interpreter obtains the machine instructions. Chapter IV contains a description of instruction fetch and execution, executiontime error detection, and input/output formats. Microinstruction formats and the development of microprograms for the simulated instructions are also discussed. It is not the purpose of this thesis to treat the subjects of input/output and interrupt servicing in great detail. Therefore, these subjects are only briefly discussed in terms of the microinstructions required to perform their basic functions.

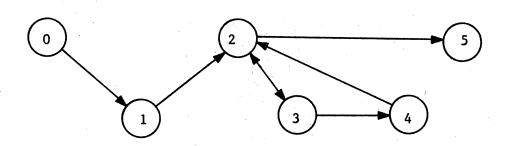

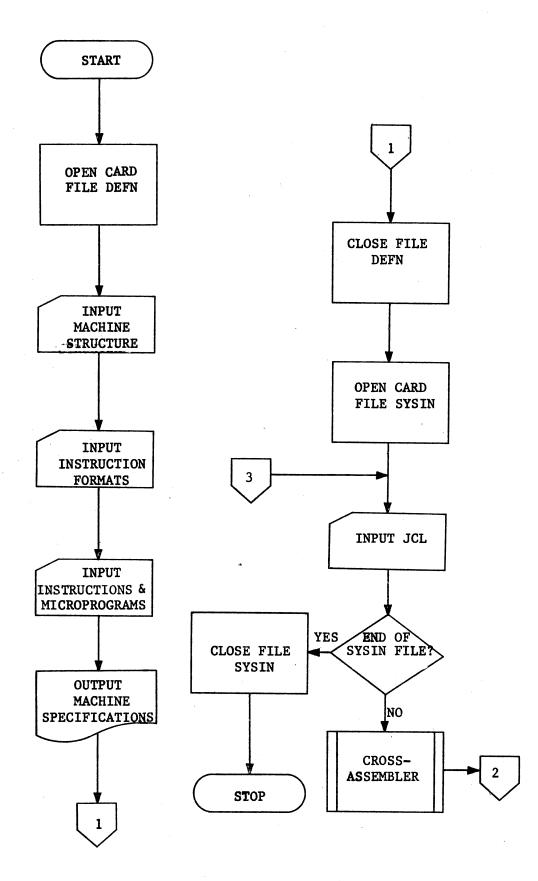

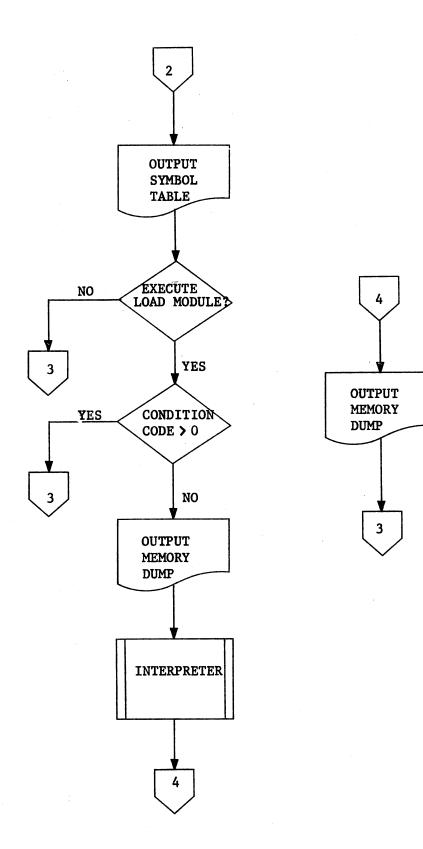

The simulation process can be thought of as a sequence of state transitions. Figure 1 and Table I illustrate the state transitions involved in the simulation process.

Figure 1. State Transitions of the Simulation Process.

Chapter V is a Users Manual and describes the deck setup and options for using the assembler-interpreter. The assembler output format and error messages are also discussed. A summary and further study is presented in Chapter VI. Appendix A contains a list of symbols used in

the description of the simulation system. A logic block diagram of the system is given in Appendix B and Appendix C contains sample assembler program runs and the output. Appendix D is a systems programmers guide to modifications of the simulation system.

# TABLE I

| State           | Description                   |

|-----------------|-------------------------------|

| 0 (Start state) | Hardware register definition  |

| 1               | Instruction set definition    |

| 2               | Job control recognition       |

| 3               | Assembly of source program    |

| 4               | Object program interpretation |

| 5 (Final state) | Termination of job stream     |

# DESCRIPTION OF STATE TRANSITIONS FOR FIGURE 1

The basis for the method of construction of the simulator presented in this thesis was developed by Hill and Peterson (7) in their description of a microprogrammed Small Instructional Computer (SIC). This computer has a fixed purpose register structure with two accumulators, two index registers and one extension register. The instruction set is sufficiently large to illustrate most points about a microprogrammed system. The design of the microinstruction set was influenced by Husson (8) in his description of the microprogramming techniques for large scale computers.

# CHAPTER II

#### MICROPROGRAMMING

#### Introduction

The term microprogramming was first coined by Professor M. V. Wilkes of the Cambridge University Mathematical Laboratory in 1951 (21, 22). In his thesis he stated that one can envision the control portion of a computer as effecting a number of register-to-register transfers of information in order to carry out the execution of a single machine instruction. Each of these steps can itself be thought of as the execution of an instruction for some machine (whose existence is unknown to the programmer). The steps used to effect a single instruction in the user machine can be thought of as constituting a program, usually called a microprogram. Microprograms can also be used for other necessary operations which are in some sense invisible to the programer, for example, fetching the next instruction or computing effective addresses.

There are at least two approaches to microprogrammed control, and they differ significantly from one another. One, called "vertical or sequential microprogramming" (18), relies on the more traditional concept of programming in which an instruction contains an operation code, secondary modifiers and one or more address fields. In this case three addressable storage areas are associated with the host machine: (1) main store, (2) control store and (3) local store.

Local store consists of registers and can be conceived of as being a general purpose storage area for use by the microprograms.

The other approach, called "horizontal microprogramming" (18), uses the microinstructions as control words whose individual bits are used to select specific data paths within the machine. In this case there are no addresses other than those implicitly specified by the bits of the control words. Although this scheme is less general than vertical microprogramming, it is possible to make more efficient use of the hardware of machines organized in this way. A modified version of the horizontal microprogramming scheme is used in the interpreter which is described in detail in Chapter IV.

In either case, the microinstructions generally are held in a control store, usually faster than main store, for which there must be some form of accessing mechanism. The majority of such systems use a non-destructive read-only store (ROS or RCM) for reasons of speed and economy. The read-only nature of these devices also insures the integrity of the simulated machine.

Alternatively, a few machines are now equipped with writable control stores implemented in core arrays. Such core arrays generally are built so that they have the properties of fast reading and slow writing (16). Fast reading is necessary for performance and slow writing can help in cost reduction.

#### Fixed Instruction Computers

In order to contrast some of the aspects of fixed instruction computers and microprogrammed computers, a description of some of the major characteristics of fixed instruction computers follows.

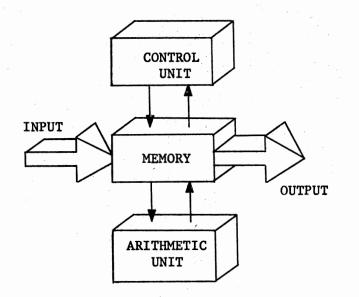

The hardware of fixed instruction computers generally is divided into four units (Figure 2): (1) an input/output unit, (2) memory (or storage), (3) an arithmetic-logic unit, and (4) a control unit. In general, the input/output unit consists of more than one physical device but input and output are often considered together.

Figure 2. Simplified Block Diagram for Fixed Instruction Stored Program General Purpose Computers [From Microprogramming Handbook (14)]

Memory is considered in its conventional way, a series of memory cells and registers used to store the instructions of a program while in execution. Addresses are associated with each memory cell and with all registers. The control unit of the computer can refer to a storage

register by its number (or address). This is called the address property of the storage register (6). Storage registers have two other properties: (1) non-destructive read-out and (2) destructive write-in. Non-destructive read-out refers to the property of accessing the contents of a register without destroying it. Destructive write-in refers to the property of destroying the previous contents of a register when information is stored into the register.

All arithmetic is performed in the arithmetic-logic unit. There is at least one accumulator or general purpose register in the ALU of any computer. The structure of the machine is such that the contents of the accumulator or general purpose register can be tested to determine the characteristics of the value. Usually, this simply means to determine if the value is less than, equal to, or greater than zero. This is the basis for all logical and conditional operations that may be performed by the system.

The control unit coordinates the interaction of all the other units. When a program is in execution, the control unit retrieves instructions from memory in the proper order and also initiates the execution of each instruction. In the simplified case, the control unit has two special registers: (1) the instruction register (IR) and (2) the program counter (PC) or program status word. The PC contains the address of the next instruction to be executed. The IR contains the machine instruction currently being executed. Generally, the ALU and the control unit are together called the Central Processing Unit (CPU).

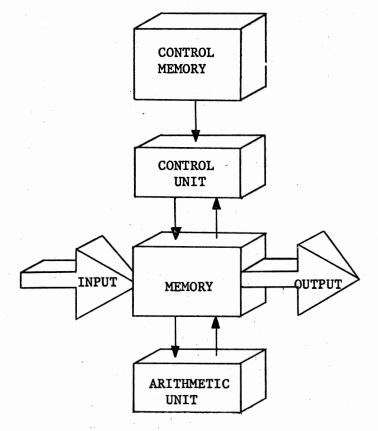

# Microprogrammed Computers

Microprogrammed computers are very similar to fixed instruction

computers, but there is one significant difference: the control memory (Figure 3). Control memory is divided into sections. Each section contains the microinstructions that perform the operations of a particular machine instruction. Each time a machine instruction is fetched, it goes through a decoding process that breaks the instruction up into its appropriate fields and then control is transferred to the microprogram associated with the particular instruction. In the most general sense, microprograms can have some degree of modularity with the use of branching instructions and microprogram subroutines.

Figure 3. Simplified Block Diagram for Microprogrammed Computers [From Microprogramming Handbook (13)]

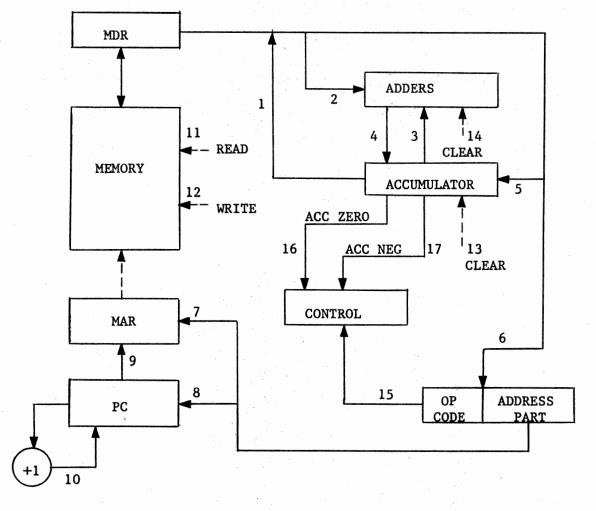

Microprogramming represents a systemic approach to control. Figure 4 depicts a ficticious vertical microprogrammed machine and its control functions. The characteristics of this machine can be summarized as: stored program, word organized, single address (18).

Figure 4. A Simple Fixed Purpose Register Machine [From Rosin (18)]

The register and storage structure is not unlike many modern fixed purpose register computers. But, in general, many modern computers have a series of accumulators, multiple address instructions, and a multipurpose Program Status Word (PSW). The machine in Figure 4 does not use the bus concept of data transfer, for ease of illustration.

The execution or interpretation of an instruction can be considered as a series of register-to-register transfers. A few other primitive functions have been added, such as clearing a register and initiating main memory reads and writes. Table II summarizes the valid operations of the machine in terms of these primitives (18).

### TABLE II

CONTROL LINES FOR FIGURE 4

|   | 1   |                                          | MDR ← ACC                             |  |

|---|-----|------------------------------------------|---------------------------------------|--|

|   | 2   |                                          | ADDERS - MDR                          |  |

|   | 3   |                                          | ADDERS ← ACC                          |  |

|   | 4   |                                          | ACC ← ADDERS                          |  |

|   | 5   |                                          | $ACC \leftarrow MDR$                  |  |

|   | 6   |                                          | $IR \leftarrow MDR$                   |  |

|   | 7   |                                          | MAR 		 ADDRESS PART                   |  |

|   | 8   |                                          | $PC \leftarrow ADDRESS PART$          |  |

|   | 9   |                                          | $MAR \leftarrow PC$                   |  |

|   | 10  |                                          | $PC \leftarrow PC + 1$                |  |

|   | 11  |                                          | MS READ                               |  |

|   | 12  |                                          | MS WRITE                              |  |

|   | 13  |                                          | CLEAR ACC                             |  |

|   | 14  |                                          | CLEAR ADDERS                          |  |

|   |     | an a |                                       |  |

|   | 1.5 |                                          | BRANCH INSTRUCTION                    |  |

|   | 15  | · · ·                                    | $CONTROL \leftarrow OPCODE$           |  |

| , | 16  |                                          | $CONTROL \leftarrow AC = 0$           |  |

|   | 17  |                                          | $CONTROL \leftarrow AC NEG$           |  |

|   | 18  |                                          | UNCONDITIONAL                         |  |

|   | r   |                                          | · · · · · · · · · · · · · · · · · · · |  |

For this particular machine the ACC is used strictly for computational purposes and for conditional (negative or zero) branching. The ADDERS work together with the ACC to perform the necessary arithmetic. The machine instructions consist of an operation code and an operand field and the IR is used in decoding the instructions. The MDR and MAR are used in conjunction to perform the memory access functions. The MDR contains the data word and the MAR contains the address of the data word. The PC is used as a pointer to the current instruction for instruction fetch and may only be incremented to point to the next memory word. The functions of the CONTROL unit, in this case, are few in number: fetch and decode the next instruction and handle any necessary branching.

To implement a simple ADD instruction (addition of the contents of the MDR to the contents of the ACC) this sequence of microinstructions may be specified.

14 CLEAR ADDERS

- 2 ADDERS  $\leftarrow$  ACC

- 3 ADDERS  $\leftarrow$  MDR

- 1 ACC  $\leftarrow$  ADDERS

Except for the fact that these four instructions contain no address parts, the sequence resembles a short conventional program.

As in any other automatic computer, microprograms require the capability to execute branches of control, both conditional and unconditional. In this simplified machine, conditional branches may be based on a zero or negative value in the ACC or the opcode itself. In the latter case, the value of the opcode determines the destination of the branch. For instructions 16, 17, and 18, a single address part must be specified.

Figure 5 contains a set of microprograms which simulates a simple machine using the organization of Figure 4. Address modification is not used and, in this case, it is not possible to modify the microprogram store. IFETCH1 simply updates the PC to point to the next instruction. IFETCH2 loads the next machine instruction into the IR and transfers the control of the program to the control unit. Note that the PC must be initialized at some point before the execution of the first machine instruction. ADD fetches a data word from memory and adds the data word to the contents of ACC. The result is placed into the ACC. CLEAR ADD simply fetches a data word from memory and loads it into the ACC. STORE ACC stores the contents of the ACC into the memory word designated by the address part of the IR. TRA loads the address part of the instruction into the PC and branches to IFETCH2 (a conventional branch or jump). TRA IF ACC NEG tests the ACC for a negative value. If the value is negative, then a branch is made to TRA, otherwise the next sequential instruction is fetched. STORE ZERO uses the ACC to store a zero value in a memory data word.

Figure 5 illustrates how the instruction set of a simple machine may be represented by a set of microprograms. The same concepts apply to the instruction sets of more sophisticated machines. Chapter IV discusses a more general approach to the development of the instruction sets for GPR and FPR minicomputers than the approach discussed in this chapter.

| 10      |         |     |                | $PC \leftarrow PC + 1$                                                        |

|---------|---------|-----|----------------|-------------------------------------------------------------------------------|

| 9       |         |     | IFETCH2:       |                                                                               |

| 11      |         |     |                | $\begin{array}{l} \text{READ} \\ \text{IR} \leftarrow \text{MDR} \end{array}$ |

| 6<br>15 |         |     |                | $CONTROL \leftarrow OPCODE$                                                   |

| 15      |         |     |                | CONTROL COPCODE                                                               |

| 7       |         |     | ADD :          | MAR 		 ADDRESS PART                                                           |

| 11      |         |     |                | READ                                                                          |

| 14      |         |     |                | CLEAR ADDERS                                                                  |

| 2       |         |     |                | ADDERS                                                                        |

| 3       |         |     |                | ADDERS $\leftarrow$ MDR                                                       |

| 4       |         |     |                | ACC $\leftarrow$ ADDERS                                                       |

| 18 (I   | FETCH1) |     |                | GO TO IFETCH1                                                                 |

|         |         |     |                | · · · ·                                                                       |

| 7       |         |     | CLEAR ADD:     | $MAR \leftarrow ADDRESS PART$                                                 |

| 11      |         |     |                | READ                                                                          |

| 5       |         |     |                | $ACC \leftarrow MDR$                                                          |

| 18 (I   | FETCH1) |     |                | GO TO IFETCH1                                                                 |

| -       |         |     |                |                                                                               |

| 7       |         |     | STORE ADD:     |                                                                               |

| 1<br>12 |         |     |                | MDR                                                                           |

|         | FETCH1) |     |                | GO TO IFETCH2                                                                 |

| 10 (1   | FEIGHI) |     |                | GO IO IFEICHZ                                                                 |

| 8       |         |     | TRA:           | PC ← ADDRESS PART                                                             |

| -       | FETCH2) |     |                | GO TO IFETCH2                                                                 |

| (       |         |     |                |                                                                               |

| 17      |         | TRA | IF ACC NEG:    | IF ACC < 0 GO TO TRA                                                          |

| 18 (I   | FETCH1) |     | •              | GO TO IFETCH1                                                                 |

|         |         |     |                |                                                                               |

| 14      |         |     | STORE ZERO:    |                                                                               |

| 3       |         |     |                | ADDERS - ACC                                                                  |

| 13      |         |     | 1. S. S. S. S. | CLEAR ACC                                                                     |

| 1       |         |     |                | $MDR \leftarrow ACC$                                                          |

| 7       |         |     |                | $MAR \leftarrow ADDRESS PART$                                                 |

| 12      |         |     |                | WRITE                                                                         |

| 4       |         |     |                | ACC - ADDERS                                                                  |

| 18 (I   | FETCH1) |     |                | GO TO IFETCH1                                                                 |

|         |         |     |                | -                                                                             |

# Figure 5. A Simple Simulator [From Rosin (18)]

# CHAPTER III

#### THE CROSS ASSEMBLER

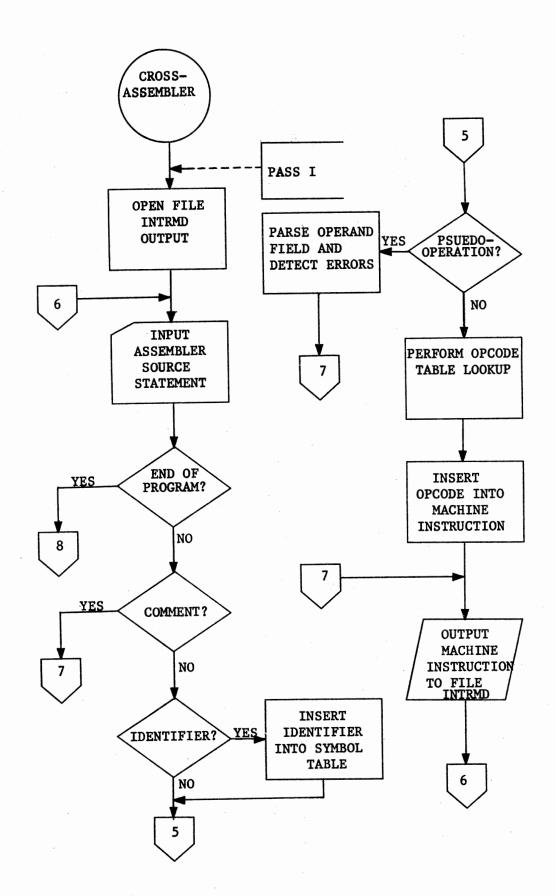

The first step in the simulation process is the conversion of assembler language source code into machine executable object code. This chapter contains a discussion of how this objective is achieved. Included is the assembly process, code generation, error detection and processing and loading the generated code into the simulated memory for execution.

To translate the source assembly program, the assembler must (1) replace each mnemonic op code with its equivalent binary code, and (2) replace each symbolic address with its corresponding location in memory. To achieve the former a table is kept with all the mnemonic op codes and corresponding binary code along with other vital information for the assembly process. Each time an assembler source statement is encountered, a table lookup is performed in order to determine the binary code equivalent. The op code table is generated in an earlier phase of the simulation process. This topic is discussed in Chapter V. In order to achieve (2) it is necessary to keep another table, called a symbol table. Each time a symbolic reference is made, a table lookup is performed in order to determine the corresponding absolute machine address.

Two scans of the source code are required to complete the assembly process for the cross assembler. It is possible to make only one

scan and achieve the same end, but the process is much more complicated and requires additional "housekeeping". The first scan determines which location in memory is to be assigned to each symbol and during the second scan the assembler produces the binary object code. Each phase of the assembly process is described in the following paragraphs along with the method used for its implementation.

#### Scanner

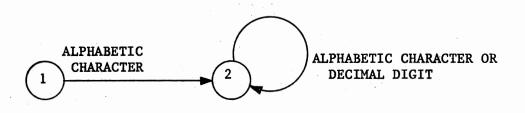

The scan phase serves two purposes: (1) allows the label identifier to be separated from the source statement so it may be placed into the symbol table, and (2) allows the op code to be separated from the source statement so that a search may be made of the op code table to find the equivalent binary code. The process of isolating the identifier can be handled in several ways. One way to accomplish this is by the development of a Finite State Automaton (FSA) to recognize the identifiers. Figure 6 represents a possible FSA for recognizing identifiers.

Figure 6. FSA for Recognizing Label Identifiers

State 1 is the "start" and a transition to the "final" state,

state 2, may only be made under an alphabetic character. A transition from state 2 to state 2 may be made under an alphabetic character or a decimal digit. As each transition is made, the character recognized is catenated onto the current symbol to form the complete identifier. Notice that a count must be kept of the length of the symbol so that the symbol will not become larger than the space available for the identifier in the symbol table.

Another method for isolating the identifier, which is similar to the first method, is the simple catenation of valid characters in the label field onto the current symbol. The catenation process is continued until a blank character or the end of the field is encountered. The latter mathod is the one used in the cross assembler described later in this chapter.

The scan phase for recognizing the mnemonic op codes can be constructed in exactly the same way as the phase for recognizing the label identifiers. The only difference being in the mnemonic op code table lookup performed after the field has been scanned.

#### Symbol Table Construction and Processing

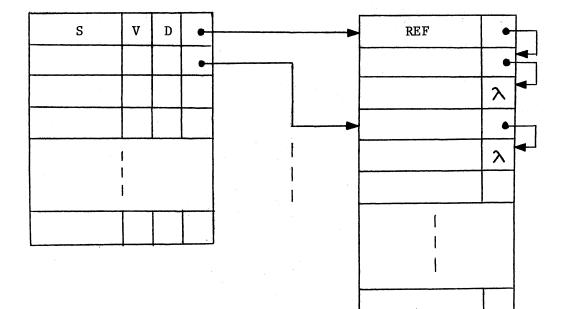

The operation code symbol table is constructed prior to the assembly process so it will not be treated in this section. It is discussed in detail in Chapter V. The table discussed in this section is the identifier symbol table and its general structure is shown in Figure 7. Notice that the symbol table is actually composed of two tables: (1) the symbol definition table, and (2) the symbol reference table. Table (1) contains the identifier, its value, the statement number in which it was defined and a pointer to the reference

table (Figure 8a). Table (2) contains the statement numbers where the identifier is referenced. The reference for each identifier are linked by means of pointers to the subsequent references. The reference table is kept so that a cross-reference listing may be printed after a program has been assembled. Figure 8b shows the node structure for each entry in the symbol reference table.

# Symbol Definition Table

### Symbol Reference Table

Figure 7. The Identifier Symbol Table

The symbol table is constructed in a sequential manner and table lookup also is done sequentially. This method may be somewhat slower than other methods, such as "hashing" techniques or binary searching, when the table becomes very large, but it is straight forward and does not require function evaluations and/or pointer updating when a symbol is defined or referenced.

| •          |       | Statement | Pointer to the  |

|------------|-------|-----------|-----------------|

| Identifier | Value | declared  | reference table |

(a) node format for symbol definition table

| Statement  | Pointer to     |

|------------|----------------|

| referenced | next reference |

(b) node format for symbol reference table

Figure 8. Node Formats for Symbol Table

### Pass I

Pass I has two primary tasks: (1) to construct the identifier symbol table, and (2) to determine the binary code representation for the mnemonic op code and substitute it into the machine instruction. A location counter (or program counter) is kept in both pass I and pass II in order to determine the exact location in the simulated memory to place the instruction. After each instruction is interpreted, the program counter is incremented by the length of the instruction.

The first step is to read a new line of the source assembly program. Since pass II will need to reread the input source program, a copy of the input is produced on an auxiliary storage device.

#### Label Field

An identifier found in the label field is placed into the symbol

table along with the current value of the program counter. Before an identifier is placed into the table, a search is made to ensure that the symbol has not been previously defined.

#### Mnemonic Op Code Field

After a mnemonic op code has been recognized, an operation code table lookup is performed. If the mnemonic is not present, a record of the error is kept. If present, the binary code equivalent is placed into the machine instruction.

# Operand Field

There are five instructions for which the operand field is parsed during pass I: (1) EQU, (2) ORG, (3) DC, (4) DS and (5) END. For these instructions it is possible to interpret the contents of the operand field the first time the instruction is encountered. Note that this places a restriction upon the use of the EQU, DC, and DS instructions. It must be possible to resolve all symbolic references at the time the instructions are first encountered. These instructions are provided by the simulation system and need not be defined by the user. The formats for these instructions are given in Chapter V.

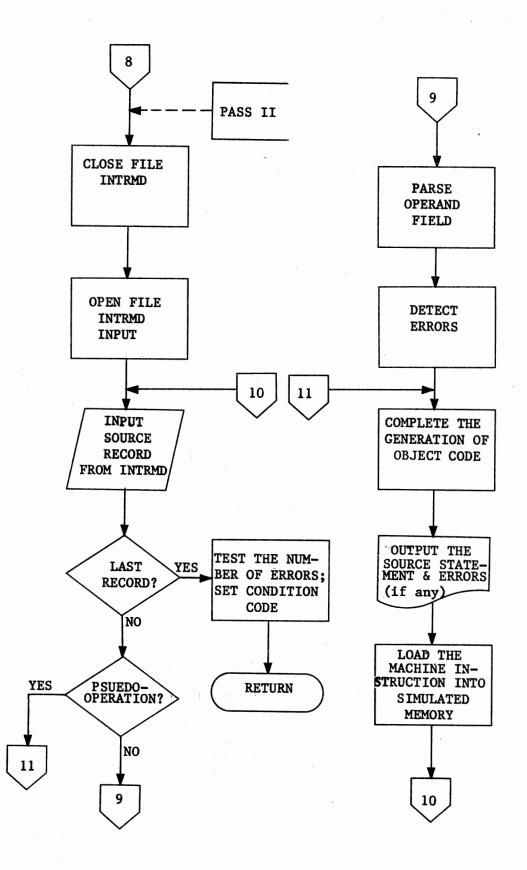

### Pass II

The purpose of pass II is to complete the machine instructions by using the symbol table constructed in pass I and to resolve all symbolic references. The operand field may be divided into as many as five separate fields, depending upon the type of machine being simulated. Commas are used as delimiters in the operand field. The relative position of a value in the operand field dictates its position in the machine instruction. The assembler language operand field syntax for GPR systems is given in Table III and the operand field syntax for FPR systems is given in Table IV.

# TABLE III

ére ti

# OPERAND FIELD SYNTAX FOR GENERAL PURPOSE REGISTER SYSTEMS

| Туре | Syntax      |

|------|-------------|

| 1    | X1          |

| 2    | Dl          |

| 3    | R1,R2       |

| 4    | B1,D1       |

| 5    | R1,K1       |

| 6    | R1,D1       |

| 7    | R1,X1       |

| 8    | SI          |

| 9    | R1,51       |

| 10   | R1,R2,S1    |

| 11   | R1,X1,S1    |

| 12   | R1,D1,S1    |

| 13   | B1,D1,S1    |

| 14   | R1,11       |

| 15   | R1,B1,D1    |

| 16   | S1,S2       |

| 17   | S1,I1       |

| 18   | D1,S1       |

| 19   | R1,D1,D2    |

| 20   | R1,R2,D1    |

| 21   | blank field |

|      |             |

The instruction type dominates the valid combinations of operands in the operand field. The meaning of the symbols used in the operand field definitions of the two classes of machines is given in Appendix A. Examples of the types of operands that can be specified for GPR machines, taken from Table III, follow. The syntax of the operand specifications closely resemble that of the simulated test machine, the INTERDATA 7/16.

| 2  | +12          |

|----|--------------|

| 8  | SYM-2400     |

| 11 | 0,15,*+48    |

| 13 | 12,-64,*     |

| 16 | SYM1, SYM2+4 |

| 17 | SYM,=A(*-28) |

| 20 | 9,10,+8      |

Examples of the types of operands that can be specified for FPR machines, taken from Table IV, follow. The syntax of the operand specifications closely resemble that of the simulated test machine, the HEWLETT-PACKARD 2114A.

| 1 | ALPHA+4          |

|---|------------------|

| 2 | =X'OOFF'         |

| 3 | OPR1, OPR2, OPR3 |

| 5 | 12               |

#### TABLE IV

# OPERAND FIELD SYNTAX FOR FIXED PURPOSE REGISTER SYSTEMS

| Туре | Syntax                                 |

|------|----------------------------------------|

| 1    | S1                                     |

| 2    | <b>I</b> 1                             |

| 3    | operate function 1,,operate function 5 |

| 4    | blank field                            |

| 5    | K1                                     |

Grammars are constructed to aid in the translation of the operand field. Since PL/I supports recursive procedures, the grammars are coded directly into the PL/I source language. Figure 9 illustrates the grammar used to parse the operand fields of the assembler statements for GPR systems. Figure 10 illustrates the grammar used to parse the operand fields of non-operate instructions for FPR systems and the grammar used for operate instructions is given in Figure 11.

ARFLD: DECL; DSTOR; RSPEC; ASPEC; ASPEC, ASPEC; ASPEC, ASPEC, ASPEC. DECL: B QDIGITS; F QDIGITS; X QDIGITS; A LADDR. ' SDIGITS '. QDIGITS: SDIGITS: + DIGITS; - DIGITS; DIGITS. DIGITS: DIGIT DIGITS; DIGIT. DSTOR: PDV DECL. LADDR: (ASPEC). RSPEC: SERPDV; ASPEC, = DECL; PDV; ASTARTH , ASPEC; ASTARTH. SERPDV: PDV ADITSPEC. ADITSPEC: COMPDV; COMASPEC. COMPDV: CTERMPDV COMASPEC; CTERMPDV. CTERMPDV: , PDV; , ASTARTH. COMASPEC: , ASPEC; , ASTARTH. PDV: DECINT. DECINT: INT DECINT; INT. ASPEC: \* ASTARTH; \*; SYMADDR; PDV. ASTARTH: + PDV; - PDV. SYMADDR: SYMI ASTARTH; SYMI. SYMI: LET SYMJ; LET. SYMJ: LET SYMJ; INT SYMJ; LET; INT. INT: 0; 1; 2; 3; 4; 5; 6; 7; 8; 9. LET: A; B; C; D; E; F; G; H; I; J; K; L; M; N; O; P; Q; R; S; T; U; V; W; X; Y; Z; &; \$; %; #; @. DIGIT: 0; 1; 2; 3; 4; 5; 6; 7; 8; 9; A; B; C; D; E; F.

Figure 9. Grammar for Parsing Operand Fields of General Purpose Register Systems

The grammars illustrated in Figures 9, 10 and 11 use certain conventions for distinguishing metasymbols, nonterminal symbols and terminal symbols (5). The nonterminal symbols on the left hand side of a rule are always followed by the metasymbol, colon (:). The right hand side alternatives of the rules immediately follow the colon and are separated by a semi-colon (;). The last alternative of a rule is followed by a period (.). All symbols not appearing on the left hand side of a rule are terminal symbols and all other symbols which are not metasymbols are nonterminal symbols.

ARFLD: DECL; DSTOR; ASPEC; = DECL. DECL: B QDIGITS; F QDIGITS; X QDIGITS; A LADDR. QDIGITS: ' SDIGITS '. SDIGITS: + DIGITS; - DIGITS; DIGITS. DIGITS: DIGIT DIGITS; DIGIT. DSTOR: PDV DECL. LADDR: (ASPEC). PDV: DECINT. DECINT: INT DECINT; INT. ASPEC: \* ASTARTH; \* ; SYMADDR; PDV. ASTARTH: + PDV: - PDV. SYMADDR: SYMI ASTARTH; SYMI. SYMI: LET SYMJ: LET. SYMJ: LET SYMJ; INT SYMJ; LET; INT. INT: 0; 1; 2; 3; 4; 5; 6; 7; 8; 9. LET: A: B; C; D; E; F; G; H; I; J; K; L; M; N; O; P; Q; R; S; T; U; V; W; X; Y; Z; &; \$; %; #; @. DIGIT: 0; 1; 2; 3; 4; 5; 6; 7; 8; 9; A; B; C; D; E; F.

Figure 10. Grammar for Parsing Non-Operate Operand Fields of Fixed Purpose Register Systems.

Grammars give a systematic method for parsing the operand fields of the assembler statements. Using a grammar allows the operand field to be separated into sub-fields and the semantic meaning of each sub-field determined. For example, if an identifier is encountered, a sequential search through the symbol table can be made to find the

value of the identifier. Once the value has been determined, parsing of the field may continue in order to evaluate any modifiers of the symbol value.

OPRSPEC: OPRLIST. OPRLIST: OPR, OPRLIST; OPR. OPR: ALPHA ACHAR; ALPHA. ACHAR: ALPHA ACHAR; NUM ACHAR; ALPHA; NUM. ALPHA: A; B; C; D; E; F; G; H; I; J; K; L; M; N; O; P; Q; R; S; T; U; V; W; X; Y; Z; &; \$; %; #; @. NUM: 0; 1; 2; 3; 4; 5; 6; 7; 8; 9.

Figure 11. Grammar for Parsing Register Operate Operand Fields of Fixed Purpose Register Systems

#### Error Detection

Error detection is accomplished in both passes of the assembler. Invalid symbols and mnemonics are detected by the scanner in pass I. Syntactical errors are detected during the evaluation of the expressions in the operand fields. The use of grammars aids in the error detection facility. The grammars define the form that must be followed in specifying operands. An error occurs any time the form is not followed. As each error is detected, the code for the error is placed into the identification record for the assembler statement. When the source listing is printed in pass II, the errors detected in each statement are printed immediately following the statement. A list of all assembly errors is given in Chapter V.

### Assembler Output

In addition to code generation, the assembler normally produces a printed output. The output consists of the location of each instruction (in hex), the object code (in hex), the statement number and a listing of each source statement. Errors, if any, are indicated immediately following the statement in error. Following the source listing is the symbol table and cross-reference dictionary which contains the symbols, their associated values (in hex) and a list of the statements in which the symbol is referenced. An indication as to the number of assembly errors is also given.

### Loader

The machine instructions generated throughout the assembly process are loaded into the simulated memory for execution. For a GPR system, loading begins at memory location zero. But for FPR systems, loading begins at the first location in page one of the simulated memory. In this context, a page refers to a physical memory page used by most fixed purpose register minicomputers in address/page mapping schemes. Page zero is used by the assembler for patching direct and indirect addresses that cannot be accessed in the current page. The user is not permitted to access any memory location in page zero, other than location zero. This helps to keep all indirect references intact. Once loading is completed the program is ready for execution.

#### CHAPTER IV

### THE INTERPRETER

The binary object code generated by the assembler is loaded into the simulated memory for execution. The machine instructions must be interpreted to carry out the processes of the simulated machine. This chapter describes how the machine instructions are fetched from memory and decoded, how the microinstructions are used in the decoding process, error detection and debugging aids.

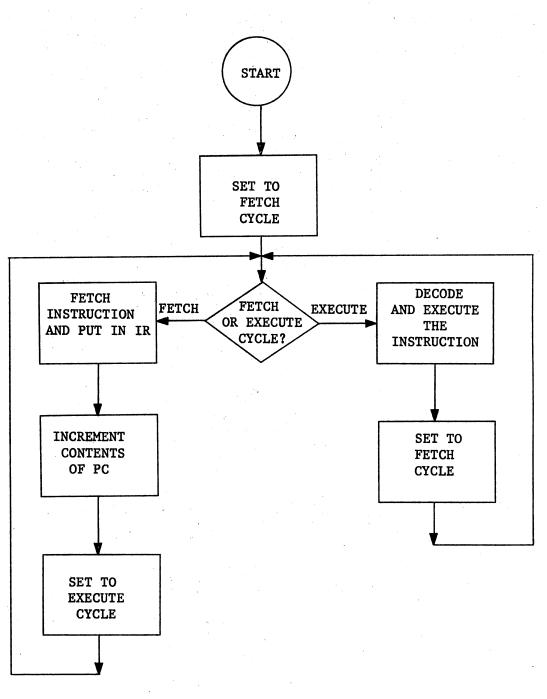

### Instruction Fetch and Execution

Execution begins with the first instruction of the machine language program. The address of this instruction, along with other vital information is known to the interpreter through the use of "global" variables. Once the address is determined in the assembly phase of the simulation process, the global variable is assigned the address of the first executable instruction. The information contained in the global variable is passed to the PC and primes the instruction fetch cycle. The complete instruction fetch and execution cycle, as shown by Hedrick (6), is illustrated in Figure 12. This is an overview of the subject matter discussed in the remaining portion of the chapter. The actual implementation of the fetch-execute process is much more complicated than is shown. The PC and IR are the most important registers used in the fetch-execute cycle. Once the

address of the next instruction is determined, the instruction is extracted from memory and loaded into the IR.

# Figure 12. Instruction Fetch and Execution Cycle

At this point the PC is updated and the instruction is subjected to the decoding process. The decoding process consists of determining the registers and/or addresses specified in the instruction, performing a table lookup of the binary operation code and executing the corresponding microprogram. The machine instruction formats for GPR and FPR systems are displayed in Figures 13 and 14, respectively. (See Appendix A for the symbols used in the two figures.) Notice that the operation code must appear in the same field of every instruction. The interpreter must know where the operation code resides within the machine instruction even before the instruction format is known. This and other related information is part of the initial machine definition and is discussed in Chapter V.

The implementation of a simulation system for the INTERDATA 7/16 required the use of eight of the instruction formats displayed in Figure 13: 1, 3, 5, 8, 9, 11, 14, and 21. Fifty-four of the instructions for the INTERDATA 7/16 have been simulated and a number of them tested in a sample program (See Appendix C).

The implementation of the HEWLETT-PACKARD 2114A required the use of three of the instruction formats of Figure 14: 1, 3, and 4. Appendix C displays the program used to test the simulation system for the HEWLETT-PACKARD 2114A. Machine instruction format 3, Figure 14, is used to specify the register operate instructions. Operate instructions manipulate the contents of internal hardware registers and exercise certain control functions without referencing the random access simulated memory.

| 1.  | OP CODE |    | X1       |    |    |

|-----|---------|----|----------|----|----|

| 2.  | OP CODE |    | D1       |    |    |

| 3.  | OP CODE | R1 |          | R2 |    |

| 4.  | OP CODE | B1 |          | D1 |    |

| 5.  | OP CODE | R1 |          | К1 |    |

| 6.  | OP CODE | R1 |          | D1 |    |

| 7.  | OP CODE | R1 |          | X1 |    |

| 8.  | OP CODE |    | S1       | ·  |    |

| 9.  | OP CODE | R1 | <u> </u> | S1 |    |

| 10. | OP CODE | R1 | R2       |    | S1 |

| 11. | OP CODE | R1 | X1       |    | S1 |

| 12. | OP CODE | R1 | D1       |    | S1 |

| 13. | OP CODE | B1 | D1       |    | S1 |

| 14. | OP CODE | R1 |          | X1 |    |

| 15. | OP CODE | R1 | B1       |    | D1 |

| 16. | OP CODE | S1 |          | S2 |    |

| 17. | OP CODE | S1 |          | I1 |    |

| 18. | OP CODE | D1 |          | S1 |    |

| 19. | OP CODE | R1 | D1       |    | D2 |

| 20. | OP CODE | R1 | R2       |    | D1 |

| 21. | OP CODE |    | 0        |    |    |

Figure 13. Machine Instruction Formats for General Purpose Register Systems

| 1. | OP | CODE | ADDRESSING MODE    |                   | S1 |              |

|----|----|------|--------------------|-------------------|----|--------------|

| 2. | OP | CODE |                    | 11                |    | <br>-<br>-   |

| 3. | OP | CODE | REGISTER OPERATE N | AICROINSTRUCTIONS |    | <br><u> </u> |

| 4. | OP | CODE |                    | 0                 |    |              |

| 5. | OP | CODE |                    | K1                |    | <br>         |

Figure 14. Machine Instruction Formats for Fixed Purpose Register Systems

### Machine Instruction Decoding

As part of the execution phase of the simulation system, the decoding process consists of three main operations: (1) performing a table lookup of the binary operation code, (2) determining the registers and memory locations involved in the execution of the instruction, and (3) executing the microprogram that corresponds to the instruction.

The first operation is relatively simple. The operation code is extracted from the instruction and placed into a temporary location. The op code table is then searched sequentially until the op code is found. Once the operation code is located, all information (instruction format, instruction length, number of operands, etc.) concerning the instruction becomes available.

The function of the instruction format is to show how the operand fields of the instruction are to be used. It specifies when an operand field of a machine instruction represents a register or when it represents an absolute memory address. For example, if instruction format 1 (Figure 13) is used, field 2 of the instruction specifies an index register. The information contained in the operand fields of the machine instructions is used in the execution of the microprogram. This explains the function of operation (2).

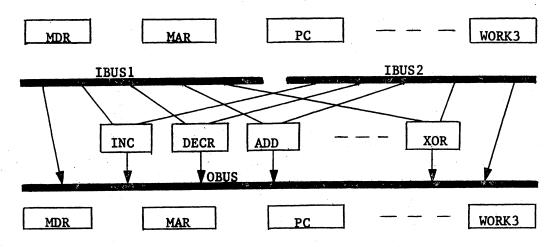

The third operation, executing the microprogram, is the most complex of the three operations. Each eleven digit microinstruction is placed into the Micro Instruction Register (MIR) (see Figure 15) and is subjected to a decoding process of its own. The MIR is a decimal register and the sequence of decimal digits specify the microoperations to be performed. Figure 16 displays the register and bus configuration for valid micro-operation specifications for the microprogrammable pseudo-machine. The user need only concern himself with the microinstructions necessary to accomplish the simulation of a desired instruction set. Instruction fetch and program counter update are taken care of automatically by the interpreter. The microoperations are defined in terms of data paths to and from input/output buses and specific hardware registers. In some cases, data paths are provided to work areas for the microprograms and also to areas containing the operand fields of machine instructions.

| 0 1 2                    | 3 4 | 5 6 | 7 8                                    | 9 | 10          |

|--------------------------|-----|-----|----------------------------------------|---|-------------|

| Conditional<br>Operation | • • |     | Input Input<br>Bus 2 Bus<br>Connection |   | Bus<br>tion |

Figure 15. The Microinstructions for the Microprogrammable Pseudo-machine

Figure 16. Register and Bus Configuration for the Microprogrammable Pseudo-machine

Positions 0-2 of the MIR are used to specify conditional operations. The contents of work area registers may be tested and program control determined from the results. Table V shows how the conditional operations may be specified.

If position 0 of the MIR is set to 1, positions 1 and 2 are decoded and the test operation performed. All other positions of the microinstruction are ignored. If the result of the test is "true", the remaining microinstructions are decoded and executed. If the result is "false", the remaining microinstructions are not executed and control is transferred to the next sequential machine instruction.

If position 0 of the MIR is set to 0, positions 3-10 are decoded as are the remaining microinstructions.

The entries in Table V are used to specify conditional operations for both GPR and FPR systems.

#### TABLE V

| MIR<br>1 2    |   | CONDITION                   |

|---------------|---|-----------------------------|

|               |   |                             |

| 0 0           |   | Filler                      |

| 0 1           |   | Compare T1 and T2           |

| 02            |   | Compare T1 and T2 immediate |

| 03            |   | T1 = T2                     |

| 04            |   | T1 <b>≠</b> T2              |

| 05            |   | T1 < T2                     |

| 06            |   | T1 > T2                     |

| 07            | • | T1 < = T2                   |

| 08            |   | T1 > = T2                   |

| 09            |   | T1 < 0                      |

| 10            |   | T1 > 0                      |

| 11            |   | T1 = 0                      |

| 12            |   | T1 = 1                      |

| 1 3           |   | T1 = -1                     |

| 14            |   | Tl even                     |

| 15            |   | Tl odd                      |

| 16            |   | Tl all l's                  |

| 1 7           |   | T2 < 0                      |

| <li>1.8.</li> |   | $\mathbb{T}2 > 0$           |

| 19            |   | T2 = 0                      |

| 20            |   | T2 = 1                      |

| 21            |   | T2 = -1                     |

| 22            |   | T2 even                     |

| 2 3           |   | T2 odd                      |

| 24            |   | T2 all 1'2                  |

### CONDITIONAL STATEMENTS FOR GENERAL AND FIXED PURPOSE REGISTER SYSTEMS

Table VI illustrates the input bus scheme for the microinstructions designed for GPR systems. Position 3 and 4 of the MIR specify the register or work area data path for input bus 1 and positions 5 and 6 specify the same for input bus 2.

Table VII shows that positions 3 and 4 of the MIR also serve to specify special 1/0, debug and operate functions for GPR systems. When an interrupt is signalled by the user (26 in positions 3 and 4 of the MIR), positions 5-10 of the MIR are used to specify the type of interrupt that has occurred.

#### TABLE VI

### INPUT BUS SCHEME FOR GENERAL PURPOSE REGISTER SYSTEMS

| MIR | <u> </u>      | MIR |               |

|-----|---------------|-----|---------------|

| 34  | IBUS1 INPUTS  | 56  | IBUS2 INPUTS  |

| 0 0 | Filler        | 0 0 | Filler        |

| 0 1 | MDR           | 0 1 | MDR           |

| 0 2 | MAR           | 0 2 | MAR           |

| 03  | PC            | 03  | PC            |

| 04  |               | 04  | e             |

| 05  | e             | 0 5 | ē             |

| 06  | R1            | 06  | R1            |

| 07  | R2            | 07  | R2            |

| 08  | Bl (explicit) | 0 8 | Bl (explicit) |

| 09  | B (implicit)  | 09  | B (implicit)  |

| 1 0 | D1            | 1 0 | D1            |

| 1 1 | D2            | 1 1 | D2            |

| 12  | S1            | 1 2 | S1            |

| 1 3 | <b>S2</b>     | 1 3 | S2            |

| 14  | <b>X1</b>     | 14  | <b>X1</b>     |

| 15  | <b>I1</b>     | 15  | <b>I1</b>     |

| 16  | WORK1         | 16  | WORK 1        |

| 17  | WORK2         | 17  | WORK2         |

| 18  | WORK 3        | 18  | WORK 3        |

Table VIII consists of the valid input bus connections. Some connections involve both input buses some involve only one. A list the functions used is given in Appendix A. Position 7 and 8 of the MIR specify the input bus connections for both GPR and FPR systems.

. . . .

## TABLE VII

# SPECIAL 1/0, DEBUG AND OPERATE FUNCTIONS FOR GENERAL PURPOSE REGISTER SYSTEMS

| MIR | · |                                   |

|-----|---|-----------------------------------|

| 34  |   | FUNCTION                          |

| 19  |   | Input data block (list directed)  |

| 20  | · | Output data block (list directed) |

| 2 1 |   | Memory dump                       |

| 2 2 |   | Register trace "on"               |

| 23  |   | Register trace "off"              |

| 24  |   | Halt                              |

| 25  |   | No operation                      |

| 26  |   | Signal interrupt                  |

### TABLE VIII

### INPUT BUS CONNECTIONS FOR GENERAL AND FIXED PURPOSE REGISTER SYSTEMS

| MIR |   |                         |

|-----|---|-------------------------|

| 7   | 8 | CONNECTION              |

| _   |   |                         |

| . 0 | - | Filler                  |

| 0   | - | IBUS1                   |

| 0   | 2 | IBUS1                   |

| 0   | 3 | IBUS2                   |

| 0   | 4 | IBUS2                   |

| 0   | 5 | INC (IBUS1)             |

| 0   | 6 | INC (IBUS2)             |

| 0   | 7 | DECR (IBUS1)            |

| 0   | 8 | DECR (IBUS2)            |

| 0   | - | ADD (IBUS1, IBUS2)      |

| t.  | 0 | SUB (IBUS1, IBUS2)      |

| 1   | 1 | MUL (IBUS1, IBUS2)      |

| . 1 | 2 | DIV (IBUS1, IBUS2)      |

| 1   | 3 | MOD (IBUS1, IBUS2)      |

| - ī | 4 |                         |

| 1   | 5 | ABS (IBUS1)             |

| 1   | 6 | ABS (IBUS2)             |

| 1   | 7 | NEG (IBUS1)             |

| 1   | • | NEG (IBUS2)             |

| 1   | 8 | AND (IBUS1, IBUS2)      |

| 1   | 9 | OR (IBUS1, IBUS2)       |

| ,   | 0 | XOR (IBUS1, IBUS2)      |

| 2   | 1 | $MDR \leftarrow M(MDR)$ |

| 2   | 2 | $M(MAR) \leftarrow MDR$ |

Table IX contains the valid output bus connections for GPR systems. Once the input bus connection has been made, the data is transferred to the output bus and from there to an appropriate register. Positions 9 and 10 of the MIR delegate to what register or work area the output bus connection is made.

### TABLE IX

| MIR |    |         |         |                                    |  |

|-----|----|---------|---------|------------------------------------|--|

| 9   | 10 |         |         | CONNECTION                         |  |

| 0   | 0  |         |         | Filler                             |  |

| 0   | 1  |         |         |                                    |  |

| •   | 2  |         |         | MDR 		 OBUS                        |  |

| 0   |    |         |         | $MAR \leftarrow OBUS$              |  |

| 0   | 3  |         |         | PC - OBUS                          |  |

| . 0 | 4  |         |         | $R1 \leftarrow OBUS$               |  |

| 0   | 5  |         |         | $R2 \leftarrow OBUS$               |  |

| 0   | 6  |         |         | T1 🗲 OBUS                          |  |

| 0   | 7  |         |         | T2 🗲 OBUS                          |  |

| 0   | 8  |         | · · · · | WORK1 		 OBUS                      |  |

| 0   | 9  |         |         | WORK2                              |  |

| 1   | ó  |         |         | WORK3 		OBUS                       |  |

| 1   | 1  |         |         |                                    |  |

| 1   | 1  |         |         | $B1 \leftarrow OBUS$               |  |

| 1   | 2  |         |         | B 🗲 OBUS                           |  |

| 1   | 3  |         |         | $X1 \leftarrow OBUS$               |  |

| 1   | 4  |         |         | (R1 + 1) ← OBUS                    |  |

| 1   | 5  |         |         | $(R2 + 1) \leftarrow OBUS$         |  |

| 1   | 6  |         |         | R1 ← K1 ↑ OBUS                     |  |

| 1   | 7  |         |         | $R1 \leftarrow K1 \downarrow OBUS$ |  |

| 1   | 8  |         |         | $R1 \leftarrow K1$ CBUS            |  |

| 1   |    |         |         |                                    |  |

| 1   | 9  | · · · · |         | $R1 \leftarrow K1$ CBUS            |  |

### OUTPUT BUS CONNECTIONS FOR GENERAL PURPOSE REGISTER SYSTEMS

The input bus scheme for FPR systems is shown in Table X. Notice that some of the same registers are used for FPR systems as GPR sysstems. Such operations as branching and data transfers are common to both systems. Positions 3 and 4 of the MIR specify the register or work area data path for input bus 1 and positions 5 and 6 specify the same for input bus 2.

### TABLE X

| R   |              | MIR        |         |              |

|-----|--------------|------------|---------|--------------|

| 3 4 | IBUS1 INPUTS | 5 <b>6</b> | 1.      | IBUS2 INPUTS |

| 0 0 | Filler       | 0 0        | r.<br>F | Filler       |

| 01  | MDR          | 0 1        |         | MDR          |

| 02  | MAR          | 02         |         | MAR          |

| 03  | PC           | 03         | `       | PC           |

| 04  | e            | 04         |         | e            |

| 05  | ē            | 0 5        |         | ਦ            |

| 06  | 1            | 0 6        |         | 1            |

| 07  | ACC A        | 07         |         | ACC A        |

| 08  | ACC B        | 08         |         | ACC B        |

| 09  | XR1          | 09         |         | XR1          |

| 10  | XR2          | 10         |         | XR2          |

| 11  | <b>I1</b>    | 1 1        |         | I1           |

| 12  | <b>S1</b>    | 1 2        |         | S1           |

| 1 3 | L            | 1 3        |         | L            |

| 14  | WORK1        | 1 4        |         | WORK 1       |

| 15  | WORK2        | 15         |         | WORK2        |

| 16  | WORK 3       | 16         |         | WORK 3       |

### INPUT BUS SCHEME FOR FIXED PURPOSE REGISTER SYSTEMS

As with the GPR systems, Table XI shows that positions 3 and 4 of the MIR also serve to specify special I/O, debug and operate functions for FPR systems. When an interrupt is signalled by the user (24 in positions 3 and 4 of the MIR), positions 5-10 of the MIR are used to specify the type of interrupt that has occurred.

Table XII contains the valid output bus connections for FPR sys-

tems. Once the input bus connection has been made, the data is transferred to the output bus and from there to the appropriate register. Positions 9 and 10 of the MIR delegate to what register or work area the output bus connection is made.

### TABLE XI

### SPECIAL I/O DEBUG AND OPERATE FUNCTIONS FOR FIXED PURPOSE REGISTER SYSTEMS

| MIR |   |                                   |

|-----|---|-----------------------------------|

| 3 4 |   | FUNCTION                          |

|     |   |                                   |

| 17  | s | Input data block (list directed)  |

| 18  |   | Output data block (list directed) |

| 19  |   | Memory dump                       |

| 20  |   | Register trace "on"               |

| 2 1 |   | Register trace "off"              |

| 22  |   | Halt                              |

| 23  |   | No operation                      |

| 24  |   | Signal interrupt                  |

|     |   |                                   |

Table XIII illustrates the microinstructions necessary to add the the contents of two general purpose registers (of a GPR system) and branch if the contents of the destination register is zero. For this operation, instruction format 10 (Figure 13) must be specified. Table XIV illustrates the microinstructions necessary to load the contents of index register 1 into the accumulator (of an FPR system) and branch if the contents of the accumulator is negative. Instruction format 1 (Figure 14) must be specified for this operation.

## TABLE XII

| MIR |    |                       |          |

|-----|----|-----------------------|----------|

| 9   | 10 | CONNECTION            | N        |

| 0   | 0  | Filler                |          |

| Ó   | 1  | MDR 		OBU             | 8        |

| 0   |    | MAR 		OBU             |          |

| 0   |    | $PC \leftarrow OBUS$  |          |

| 0   | -  | $XR1 \leftarrow OBUS$ | 8        |

| 0   |    | $XR2 \leftarrow OBU$  | -        |

| 0   |    | $T1 \leftarrow OBUS$  | 5        |

| 0   |    | $T2 \leftarrow OBUS$  |          |

|     | -  |                       | DIIC     |

| 0   |    | WORK1 $\leftarrow$ 01 |          |

| 0   |    | WORK2 $\leftarrow$ 01 |          |

| 1   | 0  | WORK3 ← OI            |          |

| 1   | 1  | ACC $A \leftarrow 0$  |          |

| 1   | 2  | ACC $B \leftarrow OI$ | BUS      |

| 1   | 3  | L ← OBUS              |          |

| 1   | 4  | $K1 \leftarrow OBUS$  |          |

| 1   | 5  | ACC $A \leftarrow K$  | -        |

| 1   | 6  | ACC $A \leftarrow K$  |          |

| 1   | 7  | ACC $A \leftarrow K$  | 1 CBUS   |

| 1   | 8  | ACC A 		 K            | 1 🗘 OBUS |

| 1   | 9  | ACC $B \leftarrow K$  | 1↑ OBUS  |

| 2   | 0  | ACC $B \leftarrow K$  | 1↓ OBUS  |

| 2   | 1  | ACC $B \leftarrow K$  | 1 CBUS   |

| 2   | 2  | ACC $B \leftarrow K$  |          |

### OUTPUT BUS CONNECTIONS FIXED PURPOSE FOR REGISTER SYSTEMS

### TABLE XIII

### IMPLEMENTATION OF ADD REGISTER TO REGISTER AND BRANCH ON ZERO

| INSTRUCTION<br>NUMBER | MIR         | DESCRIPTION                                                           |

|-----------------------|-------------|-----------------------------------------------------------------------|

| 1.                    | 00006070905 | R1 ← R1 + R2                                                          |

| 2.                    | 00007000106 | $T1 \leftarrow R1$                                                    |

| 3.                    | 1110000000  | If T1 = 0 then go to next;<br>else decode next machine<br>instruction |

| 4.                    | 00012000103 | next: $PC \leftarrow S1$                                              |

`

### TABLE XIV

### IMPLEMENTATION OF LOAD ACCUMULATOR FROM INDEX REGISTER AND BRANCH ON NEGATIVE

| INSTRUCTION<br>NUMBER | MIR         | DESCRIPTION                                                           |

|-----------------------|-------------|-----------------------------------------------------------------------|

| 1.                    | 00009000111 | ACC $A \leftarrow XR1$                                                |

| 2.                    | 00007000106 | $T1 \leftarrow ACC A$                                                 |

| 3.                    | 1090000000  | If T1 < 0 then go to next;<br>else decode next machine<br>instruction |

| 4.                    | 00012000103 | next: $PC \leftarrow S1$                                              |

### Error Detection

Errors occurring during execution time are detected by the interpreter and appropriate messages are printed. Errors such as addressing and operation exceptions are detected during normal execution. In all cases the occurence of an execution time error causes termination of the program. This is due to the fact that there are no error correction capabilities built into the simulation system. The cause of the error must be determined and corrected and the program resubmitted for execution.

#### Debugging Aids

Instructions used as tools for debugging may be defined with the micro-operations provided. Two such instructions are the instruction trace and memory dump operations. The instruction trace may be turned "on" and "off" as desired and causes the contents of all hardware registers to be printed (in decimal) after the execution of any subsequent instructions. The dump instruction provides a means of determining the contents of memory within a certain region. Pre-execution and post-execution memory dumps are provided without specification.

### Other Simulation Systems

Other types of hardware simulation languages have been developed. Two of these are APL (the interactive terminal languate) (3) and PMSL (12). Both APL and PMSL require strict knowledge of the simulated computer system but treat the simulation process on different levels.

APL makes use of a special character set, which includes both an upper and lower case alphabet, to achieve parallelism with AHPL (A Hardware Programming Language), the hardware "description" language. At the APL level of simulation, register transfer, memory access, I/O buffering, etc. can be specified in detail not unlike that of the simulated system. Thus, detailed knowledge of the interaction of registers, memory and peripherals is necessary.

PMSL, as designed by Knudsen (12), is a conversational facility for the creation, modification, storage, retrieval and analysis of descriptions of computer hardware at the top system level, where work is performed on processors, memories, controllers, channels and peripherals. PMSL provides a powerful tool to the design engineers of computer systems. Performance, cost and device utilization can be monitored to give the designer a look at critical aspects of new system designs. The language is based on the PMS (Processors, Memories and Switches) notations in Bell and Newell (2).

### CHAPTER V

### USERS MANUAL

This chapter describes how to use the simulation system. The machine description phase, assembly language statements and options, deck setup and output, and control cards are discussed. At certain points, the current restrictions of the simulation system are also discussed.

### Initial Machine Description

The first phase of the simulation process is the machine description. The user is required to supply necessary information about the simulated machine in the form of input cards. The details of the card formats for the input information are given in Tables XV and XVI. Information about the hardware of the machine such as the types of registers used, the size of the registers, and the memory word size must be specified. Other details about the instruction set and formats must also be specified. If at any time a specification is requested that does not apply to the particular machine, a negative or zero value should be placed in the corresponding field of the input card. The input formats for the machine definition must be followed exactly to ensure correct results in later phases of simulation. Note that all character and bit values must be left justified in the appropriate fields and all numeric values must be right justified in the

# TABLE XV

### INPUT CARD FORMATS FOR MACHINE DESCRIPTION OF GENERAL PURPOSE REGISTER SYSTEMS

| CARD        | CARD    | FIELD   |                                                                                         |

|-------------|---------|---------|-----------------------------------------------------------------------------------------|

| SET         | COLUMNS | TYPE    | DESCRIPTION                                                                             |

| 1           | 1       | Bit     | Specify 1 if output of machine de-                                                      |

|             |         |         | scription is desired                                                                    |

|             |         |         | Specify 0 for no output                                                                 |