# SEGMENTED-VIRTUAL MEMORY DESIGN FOR

AN ALGOL 68 COMPILER

By

Bachelor of University Studies Oklahoma State University

MARK GOTO

Stillwater, Oklahoma

1975

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of MASTER OF SCIENCE July, 1978

# SEGMENTED-VIRTUAL MEMORY DESIGN FOR

AN ALGCL 68 COMPILER

# THESIS APPROVED:

Thesis Adviser

Dean of Graduate College

#### PREFACE

thesis is a description of a design for This an ALGOL 68 run-time organization. The design relies heavily on a segmented-virtual memory scheme for simulating a large memory store and handling memory management requests. The author would like to thank each of the members of the Computing and Information Sciences Department who have made his study at O.S.U. enjoyable, and especially Dr. G. E. Hedrick who has been more than his advisor. The author would also like to acknowledge the support of the National Science Foundation for sponsoring this research under grant NSF-MCS576-06090.

# TABLE OF CONTENTS

| Chapter |      |      |                |              |     |     |     |           |       |     |       |       |       |      |     |            |       |     |     |    |   | Pa | ige    |

|---------|------|------|----------------|--------------|-----|-----|-----|-----------|-------|-----|-------|-------|-------|------|-----|------------|-------|-----|-----|----|---|----|--------|

| 1.      | INTR | ODUC | TIO            | N .          | •   | •   | •   | •         | •     | •   | •     | ٠     | ٠     | •    | •   | •          | ۲     | ٠   | •   |    | • | •  | 1      |

|         |      |      | )ecti<br>story |              |     |     |     |           |       |     |       |       |       |      |     |            |       |     |     |    | • | ٠  | 1      |

|         |      | 1    | LGOI<br>view   | 6            | 3 с | :on | pi  | .10       | er    |     |       | •     | ۲     |      | •   |            |       |     |     |    | ٠ | •  |        |

|         |      |      | es (           |              |     |     |     |           |       |     |       |       |       |      |     |            |       |     |     |    |   |    | 4<br>7 |

| II.     | PRES | ENT  | RUN-           | -TI          | ME  | EN  | IVI | R         | DNN   | IE) | T     |       | •     | ٠    | •   | ٠          | •     | •   | •   | ٠  | • | •  | 11     |

|         |      |      | trodi<br>n-tii |              |     |     |     |           |       |     |       |       |       |      |     |            |       |     |     |    |   |    | 11     |

|         |      |      | n-ti           |              |     |     |     |           |       |     |       |       |       |      |     |            |       |     |     |    |   |    |        |

|         |      |      | n-ti           |              |     |     |     |           |       |     |       |       |       |      |     |            |       |     |     |    |   |    |        |

|         |      |      | nmary          |              |     |     |     |           |       |     |       |       |       |      |     |            |       |     |     |    |   |    |        |

| III.    | PROF | OSEI | RU             | N <b>-</b> T | IME | E   | NV  | I         | ROI   | M   | ENT   |       | •     | •    | •   | ٠          | ٠     | •   | •   | ٠  | ٠ | •  | 15     |

|         |      | Des  | sign           | De           | sci | ir  | oti | 0         | n     |     |       |       |       |      |     | •          |       |     |     |    |   | •  | 15     |

|         |      |      | Pa             |              |     |     |     |           |       |     |       |       |       |      |     |            |       |     |     |    |   |    |        |

|         |      |      | e Se           |              |     |     |     |           |       |     |       |       |       |      |     |            |       |     |     |    |   |    |        |

|         |      |      | AL             |              |     |     |     |           |       |     |       |       |       |      |     |            |       |     |     |    |   |    |        |

| IV.     | SUMM | ARY  | <b>C</b> 0     | NCL          | USI | [0] | IS, | , 1       | A N I |     | 7U1   | C U I | RE    | WC   | R   | (          | ٠     | ٠   | •   | •  | ٠ | •, |        |

|         |      | Sur  | nmary          | v a          | ħđ  | Co  | na  | :11       | 151   | ior | 15    |       |       | -    |     | -          |       | _   | -   |    |   |    | 33     |

|         |      |      | ture           |              |     |     |     |           |       |     |       |       |       |      |     |            |       |     |     |    |   |    |        |

| REFEREN | ICES | • •  | •              | • •          | -   | •   | •   |           | •     | ٠   | •     | •     | •     | •    | •   | •          | •     | •   | •   | •  | • | ٠  | 37     |

| APPENDI | XA.  | - DI | ESCR           | IPT          | 101 | IS  | OF  | 7         | RUI   | N-1 | []    | łΕ    | D     | AT / | 4 5 | 5 <b>T</b> | RUC   | CTI | JRI | ES | • | •  | 39     |

| APPENDI | XB   | - PI | DL D           | ESC          | RIE | PT1 | [0] | <b>IS</b> | 01    | 7 1 | RUI   | V-1   | r I I | 1E   | RC  | )ប         | r I I | NES | 5   | •  | • | ٠  | 41     |

| APPENDI | X C  | - PI | ROGR           | AM           | DES | 510 | GN  | L         | AN (  | GUI | A G E | 2     |       | ٠    | •   | •          | •     | ٠   | ٠   | •  | • | •  | 52     |

| APPENDI | X D  |      | PERA<br>LGOL   |              |     |     |     |           |       |     |       |       |       |      |     |            |       | os1 |     | •  | • | •  | 54     |

/

# LIST OF TABLES

| Table |                                                  | Page |

|-------|--------------------------------------------------|------|

| I.    | Versions of the OSU ALGOL 68 Compiler            | • 3  |

| II.   | Paging Environment Routines •••••••              | - 20 |

| III.  | Segmented Environment Routines                   | • 25 |

| IV.   | Items Allocated on the Heap                      | - 28 |

| ۷.    | Items Allocated on the Stack • • • • • • • • • • | • 29 |

# LIST OF FIGURES

| Figure | Page                                                           |

|--------|----------------------------------------------------------------|

| 1.     | The Layered Environments • • • • • • • • • • • • • • • • • • • |

| 2.     | Mapping the Virtual Space into the Physical Space 17           |

| 3.     | Location of the PMT                                            |

| 4.     | Correspondence between SMT entries and PMT<br>entries          |

| 5.     | SMT structures                                                 |

| 6.     | Stack and Heap Storage in Segmented Memory 27                  |

| 7.     | Stack Display Layout                                           |

| 8.     | Stack Environment for Parallel Processes • • • • • 35          |

#### CHAPTER I

#### INTRODUCTION

#### Objectives

Since 1973 a project has been underway at Oklahoma State University to write a portable compiler for the ALGOL 68 language (1) (2) (3) (4). This project was started by an implementation of a subset translator and an interpretive executor with the original intent of providing a scientific subset compiler (1). Since that time, many modifications and additions have been incorporated with the long range goal of providing full support of the ALGOL 68 lan-As a result of this work, it has been recognized by quage. people concerned with this project that the run-time environment provided by the current interpretive executor is inadequate for the expanding implementation and on-going work. Therefore, it was decided to revise the present executor so as to increase the flexibility of the storage management functions.

Prior to 1977, the Oklahoma State University ALGOL 68 compiler had only limited storage management beyond the classical stack environment. The main objective of this thesis is to present a run-time environment design that

would simplify implementation of non-LIFO storage allocation such as ALGOL 68 heap generators, flexible multiple values and transput-file information. Other objectives of this design are to handle large ALGOL 68 user storage demands on small computers and to ease implementation of ALGOL 68 parallel processing.

# History of the Oklahoma State

#### University ALGOL 68

#### compiler

In 1973, John Jensen implemented a scientific subset compiler for ALGOL 68 on an IBM 1130 with 8K 16-bit words of storage (1)<sup>1</sup>. This original version (referred to here as Version I) of the Oklahoma State University ALGOL 68 compiler has developed into an implementation that supports a sizable subset of the language.

Major contributions have come from thesis work by Roger Berry (2), Alan Eyler (3), Walter Seay (4) and Alan Robertson (5). This includes development of a subset ALGOL 68 transput package, addition of procedures to the Version I compiler and the enhancement of mode processing. Other contributions have come from several students who volunteered time to work on this project, most notably Larry Hanes, Charles Hanes and Alan Robertson.

\*"1K" is equivalent to 1024.

Berry's (2) implementation of formatted transput resulted in an independent package which supports a subset of transput as defined by the "Report on the Algorithmic Language ALGOL 68" (6). Incorporating this package with the Version I compiler on an IBM 360/65 resulted in the Version II compiler in late 1975.

#### TABLE I

# VERSIONS OF THE OSU ALGOL 68 COMPILER

| Version | Description                                                                                                                                    |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------|

| I       | John Jensen's original implementation on the IBM<br>1130 in 1973                                                                               |

| II      | Version I with Roger Berry's Transput package<br>incorporated on the IBM 360 in 1975                                                           |

| III     | Version I enhanced to support procedures imple-<br>mented on the IBM 1130 in 1975                                                              |

| IV      | Re-integration of Berry's Transput package,<br>Eyler's implementation of procedures and<br>Jensen's original version on the IBM 360<br>in 1976 |

Alan Eyler completed his work (3) on implementation of procedures during late 1975, but on the same machine as John Jensen's original work. This version (Version III) was

later recombined with Version II and satisfactorily completed in early 1976 (Version IV).

In mid 1976, Walter Seay completed his work (4) on mode processing. It is mainly due to his modifications and the work on integrating the Version II and III compilers that the need for improving the run-time environment became crucial.

In 1978, Alan Robertson completed research on Transformational grammars (5), and proposed a system by which ALGOL 68 format denotations may be parsed and interpretively executed at run-time. In designing this addition to the compiler, he required some heap storage mechanizms that are easily provided by the design presented in this thesis. In fact, the consideration of Alan Robertson's design for processing formatted transput and the problems encountered by Walter Seay were the inspiration for this thesis.

The latest work on the Oklahoma State University ALGOL 68 compiler includes re-integration of Walter Seay's work with the Version IV compiler, updating the formatted transput package, testing the compiler on various different machines (TI ASC, IBM 370/158, CDC CYBER 175), and implementation of the design presented here.

# Review of Current Work

The ALGOL 68 language, as defined in the "Revised Report on the Algorithmic language ALGOL 68" (7), is a very

powerful language. Several implementation efforts on the language are currently in progress. Three of the most notable efforts which have come to the attention of the author are: 1) the Cambridge ALGOL 68 compiler, 2) the ALGOL 68 compiler of Paris-Sud University (Orsay) and 3) the Manchester ALGOL 68 compiler.

The Cambridge ALGOL 68 compiler has been implemented and used at 0.S.U. and has proven to be a very efficient and fast compiler. Its drawbacks are the lack of numerical facilities, the lack of formatted transput and the diffiin transporting the culty involved compiler onto non-370-like machines. Despite these drawbacks, it has excellent capabilities for use in writing compilers (ie. almost full implementation of modes and structures). Performance tests on an IBM 370/158 show that equivalent programs execute somewhere between one and a half to three times faster when using the Cambridge compiler as compared to the IBM PL/I optimizer.

The ALGOL 68 compiler of Paris-Sud University (Orsay) is not available at O.S.U. but its implementors claim (8) to have implemented almost all of the language as defined by the "Revised Report" (7). This compiler was implemented in FORTRAN on a Univac 1100-series computer and is a true compiler in the sense that it produces relocatable object code. The use of FORTRAN suggests that portability and readability were objectives in the initial choice of the implementation

language. However, the authors admit that certain machine dependent features of the Univac FORTRAN V compiler were used and that the code generation phase is strongly dependent on the run-time computer.

The Manchester ALGOL 68 compiler was of interest due to the run-time environment design (9) (10), specifically, the use of segments. This presentation consists of a design that uses segments of a slightly different form, with the same goal of flexible storage management. This design uses segments as a means for handling storage management of flexible rowed values and heap generators in a similar manner to the way that the Manchester ALGOL 68 handles problems with these modes.

The above descriptions are a brief overview of current compilers whose design have points of similarity or have influenced this proposal. Other notable implementations of ALGOL 68 include ALGOL 68-R (11) and the Control Data Corporation ALGOL 68 compiler for the 6600 and similar computers.

Besides the current implementation efforts mentioned above, literature on ALGOL 68 and compiler writing topics have contributed to the design presented here. An excellent survey of the ALGOL 68 language is presented in the revised cdition of <u>Ap Informal Introduction to ALGOL 68</u> (12). Much of the information about the Manchester ALGOL 68 compiler appears with discussions of other compiler writing topics in the "Proceedings of the Vth Annual III Conference on Imple-

mentation and Design of Algorithmic Languages" (13). In addition, the author has used material from Gries (14) as a basis for designing parts of the run-time storage organization. Ideas for the remaining portion of the storage management scheme in this thesis came from discussions of operating systems storage management in Madnick and Donovan (15), especially the descriptions of MULTICS<sup>2</sup>.

#### Notes on Terminology

The author's background in compiler writing and operating systems has resulted in the use of terminology from both fields. Terms used in this thesis such as pseudo-code, stack environment and display vector are borrowed from compiler writing, while terms such as layered design, page fault and virtual memory come from an operating systems background<sup>3</sup>. While Gries (14) and Madnick and Donovan (15) provide adequate definitions of several such terms, presentation of a few descriptions here are worthwhile.

Gries (14) describes a stack environment for a block structured language, as a large table of contiguous locations from which storage areas are allocated. These areas,

\*The Multiplexed Information and Computing System (MUL-TICS) is described in a case study by Madnick and Donovan (15).

<sup>3</sup>In particular, the term "layer" as used in this thesis, is not the same as the ALGOL 68 term "layer" in the language definition. which are called stack-frames, are allocated when a program block is entered and are de-allocated when the block is Because the stack-frames are allocated in a exited. last-in-first-out manner, the run-time storage organization is called a stack environment. In addition to the allocation of memory, a vector of table indices or addresses is maintained that indicate the beginning of each stack-frame This vector of addresses is called a display allocation. vector. Because this vector is updated and saved each time a stack-frame is created, a display vector exists for each stack-frame. For the purposes of this thesis, the storage allocated upon entering a block is called a stack-frame, the saved list of addresses that maps the allocations is called a display and a list of addresses that includes the most recent allocation (ie. the active stack-frame) is the display vector.

Gries (14) also described an interpreter as a program that performs two functions: 1) translates a source program into an internal form, and 2) executes (interprets or simulates) the program in this internal form. For the purposes of this thesis, the internal form of the source program is called pseudo-code (especially because it resembles machine code for a hypothetical ALGOL 68 machine) and the portion of the interpreter that performs the second function mentioned above is called an interpretive executor.

Madnick and Donovan (15) describe several operating systems besides MULTICS. MULTICS, however, has special significance in that it uses a segmented-virtual memory management scheme and had a design approach used known as a layered design. This thesis adopts the layered design approach and uses a form of segmented-virtual memory management that resembles that of MULTICS. MULTICS, a section of high In speed primary storage is used as a cache memory to which memory references are made. A virtual memory space is maintained by translating virtual addresses into cache memory addresses. Since the virtual memory size is much larger that the cache memory size, secondary storage is used to store subsections of the cache memory until needed. These subsections of cache memory are called pages in MULTICS and in this thesis. Additionally, a reference to a page that is not currently in cache memory causes a paging operation known as a page swap to occur (a page of cache memory is copied to secondary storage and the desired page of virtual memory is copied into cache memory). All memory that is addressable by a virtual address is considered to be pagable, as opposed to hardware registers or cache memory pages for which no address translation occurs.

Two ALGOL 68 terms of special significance are used throughout this thesis: 1) flexible rowed values and 2) heap values or storage. Rowed values in ALGOL 68 are values which may be accessed via a name and a subscript; ie., they

correspond to Fortran or PL/I arrays. Flexible rowed values are values that may change their bounds after the declaration of the values has been executed. This is somewhat similar to the way PL/I varying strings may change in length. The consequences of this feature are that the storage requirements of a flexible rowed value may change after allocation of the rowed value is complete, which makes this type of storage allocation a special problem that cannot be handled by the stack environment described above.

Heap values also cannot be handled by a stack environment, because by definition, they must remain allocated as long as any references exists to the allocated storage, even after the block where the heap values were allocated has been exited<sup>4</sup>. Heap values may be of any valid ALGOL 68 mode which creates further problems in that data-handling and allocation techniques must exist for both heap and non-heap values.

For the most part, this thesis uses the same terminology as can be found is Gries (14) and Madnick and Donovan (15) unless otherwise stated. The above descriptions hopefully provide some added insight into the terms most frequently used by this thesis which are not commonly known.

4Note that "Heap" refers to specifically ALGOL 68 heap storage which is storage that remains allocated even after a program block is exited and which is garbage collected as the need is perceived.

## CHAPTER II

#### PRESENT FUN-TIME ENVIRONMENT

# Introduction

The OSU ALGOL 68 compiler generates pseudo-code which is interpretively executed. The interpretive execution is performed in a simulated memory with an extended stack model run-time environment. An excellent description of the overall compiler was delivered at the 1975 International Conference on ALGOL 68 (16).

This presentation is concerned with three aspects of the current run-time environment: 1) the run-time symbol table and run-time addressing, 2) the stack organization of memory, and 3) the simulated memory itself. The design presented here should either improve the performance of and/or increase the flexibility of each aspect.

Run-time Symbol Table and Addressing

The run-time symbol table is represented by a vector of active entries, linked lists of inactive entries and a table of character representations. The symbol table entries consist of two items: an absolute address of the storage associated with the variable and an indicator of the

When variable is accessed, mode type. а а compiler-generated identifier number is retrieved from the pseudo-code instruction and used to index the active entry vector of the symbol table. The address of the variable location in memory is then obtained from the symbol table and the value of the variable is either fetched from or stored into the indicated location. If a pseudo-code instruction accesses more than one variable, then the above process is repeated for each variable.

Due to limitations imposed by the IBM 1130, the runtime symbol table was statically limited to 120 entry positions. Although later versions of the compiler were run on an IBM 360/65, expansion of the symbol table proved to be very difficult due to restrictions in the implementation language, namely FORTRAN. At that time, it was decided not to alter the symbol table structure because the enormous amount of re-design effort required was not available.

The design presented in this thesis eliminates the run-time symbol table by using display offset addressing. Each variable is addressed by an offset from a stack display address which is kept in a display vector. This scheme will remove the restriction of 120 active unique variables and can maintain the speed of address by keeping a copy of the active display vector in primary storage.

# Run-time Stack Organization of Memory

The interpretive executor has a very primitive memory management scheme. The allocation of memory is performed according to a single stack organization. Corresponding to each new range of the ALG(I 68 program, a new stack frame is initialized by copying and updating the standard stack model display vector. At the end of each range, the current stack frame is released along with the storage associated with it. This stack organization plus a very simple heap allocation mechanism (with no storage reclamation) constitutes all of the storage management of the interpretive executor.

In order to increase the flexibility of storage management, a segmented-virtual memory scheme is used. Segments are used to allocate memory for two types of requests: 1) requests for memory that cannot be allocated and de-allocated in a stack environment, and 2) requests for memory that may have later requests to increase or decrease the size of the original requests. Examples of these types of requests are ALGOL 68 flexible rowed values, ALGOL 68 heap values, transput-file information and the memory area for sub-allocating a stack environment.

# Run-time Simulated Memory

The simulated memory used by the interpretive executor consists of a disk file of 8000 words with two 80 word pages kept in core memory. Cne page is used to fetch pseudo-code instructions while the other page is used for fet<sup>Ching</sup> and storing data values. Since the original implementation machine was an IBM 1130 with 8k 16-bit words of memory, the above limitations were considered reasonable choices. however, due to the many additions and modifications since the original implementation, the power of the implemented language has increased significantly. The natural result of this growth is that users are attempting to write programs of greater complexity which require more user storage.

The proposed design uses a virtual memory space to allow larger memory requests while using segmentation to control paging. A much larger address space and increased flexibility can be provided without excessive overhead costs.

#### Summary

The major problem prints are: 1) the limitations of a fixed and static size addressing scheme, 2) the lack of flexibility in the storage management features, and 3) the limited size of simulated memory. These problems have caused implementation efforts in extended mode processing and transput-file processing to be extremely complex. In addition, user programs of appreciable size simply are not accepted by the interpretive executor.

#### CHAFTER III

## PROPOSED FUN-TIME ENVIRONMENT

# Design Description

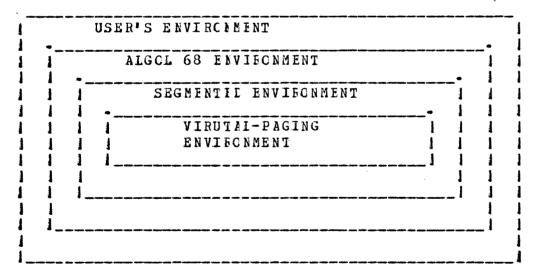

The proposed run-time environment can be broken down into a layered design consisting of four environments as follows: 1) an inner-most paging virtual memory environment, 2) a segmented memory allocation environment, 3) an

Figure 1. The Layered Environments

ALGOL 68 "machine" environment, and 4) the outer-most layer which is the ALGOL 68 user environment. These environments are briefly diagrammed in Figure 1.

# The Paging Environment

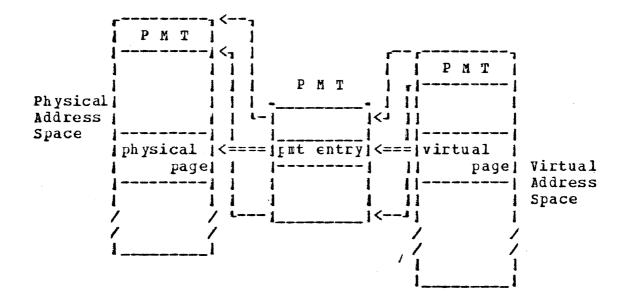

The paging environment uses a contiguous page mapping table that maps virtual gages into physical pages that may be stored on disk (or any other appropriate direct-access medium.) The Page Mapping Table (hereafter abbreviated to PMT) is stored at the beginning of the simulated virtual memory such that direct indexing can be used to map a virtual page into a physical gage. Figure 2 diagrams the virtual memory to physical memory mapping. Note that the PMT (as shown in the exploded center block) is fixed such that the virtual addresses of the PMT are the same as the physical addresses of the PMT.

The paging environment is simulated using a memory block of 1024-words and a Page Fault Table (PFT). The memory block is divided into eight 128-word page slots (numbered 0 to 7) which are used as a cache memory for paging purposes (for the purposes of this thesis, the term "cache" is used to refer to the primary storage block used by this design). In contrast to the PMT which is used to indicate the mappings between virtual and physical storage, the PFT maps virtual memory into cache memory and is used in a manner similar to the usage of hardware associative registers.

Figure 2. Mapping the Virtual Space into the Physical Space

Of the eight cache memory page slots, slot zero always contains physical page zero which always corresponds to virtual page zero; slots one through seven contain physical pages and the corresponding virtual pages as indicated by entries one through seven of the FFI.

Each entry of the PHT contains five logical fields cf information: 1) a virtual page number, 2) a page slot address, 3) the Least-Recently-Used (LRU) reference count, 4) a modification flag, and 5) a physical page number. The virtual page number, page slot address, and physical page number are used to maintain the correspondance between a page slot and a virtual address. The "LRU reference count"

field indicates approximately how long ago the page slot was referenced while the modification bit indicates whether or not the contents of that page slot was modified.

A description of the addressing process, shows how the various PFT entry fields are used and how a virtual address is mapped into a physical disk page. The virtual address is de-composed into a virtual page number and a page offset value so that a search of the Page Fault Table may be made to hopefully locate the page in memory. At the same time that the PFT is searched, two other operations are performed: 1) locating the least-recently-used page and 2) updating the page slot reference counts. If the desired virtual page is in memory, then the reference to the appropriate page slot or slots is performed.

If a desired page is not in the cache memory, then a virtual memory reference is made to the appropriate PMT entry. Since the PMT is also a part of pagable memory the physical page numbers of the PMT area are fixed such that they correspond to the virtual page numbers. This fixed correspondence allows a virtual page of the PMT to be paged-in without address translation. The inquiry into the PMT produces the physical page number of the page to be fetched. Using the location of the least-recently-used page found during the PFT search, a page swap is performed and the virtual memory reference is completed. Examining Figure 3, one can see that the FMT occupies the first several pages

|      |      | Physical<br>Address<br>Space |      | Virtual<br>Address<br>Space |          |  |

|------|------|------------------------------|------|-----------------------------|----------|--|

| Page | No . |                              | Page | No .                        |          |  |

| -    | 0    | IPMT page                    | <    | 0 1                         | PMT page |  |

|      | 1    | IPMT page                    | <    | 1                           | FMT page |  |

|      | 2    | IPMT page                    | <    | 2                           | PMT page |  |

|      | 3    | IPMT page                    | <    | 2                           | FMT page |  |

|      | •    |                              | 1    | •                           |          |  |

|      | •    | 1 •                          |      | •                           | •        |  |

|      | • .  | •                            |      | •                           | •        |  |

Figure 3. location of the PMT

of both the virtual address space and the physical address space.

The paging environment level contains four main modules as shown in Table II<sup>1</sup>. These modules perform the operations involved in virtual memory addressing. Routine VMREF is the external linkage to the paging environment in that all virtual memory references are performed via a call Routine VMPFX determines whether a referto this routine. ence can be satisfied cr if a "page-fault" occurs. Routine VMPFT performs the actual FFT search and routine VMSWP performs page swapping.

<sup>1</sup>An informal PDL description of this module (VMPFT) and the other virtual-paging modules (VMREF, VMPFT, VMSWP) is presented in Appendix E.

#### TAELE II

#### PAGING ENVIRONMENT ROUTINES

| Routine | Description                           |

|---------|---------------------------------------|

| VM R EF | Virtual memory fetch and store module |

| VMPFX   | Virtual memory page fix module        |

| VMP FT  | Page Fault Table search module        |

| VMS WP  | Virtual memory page swar module       |

#### The Segmented Environment

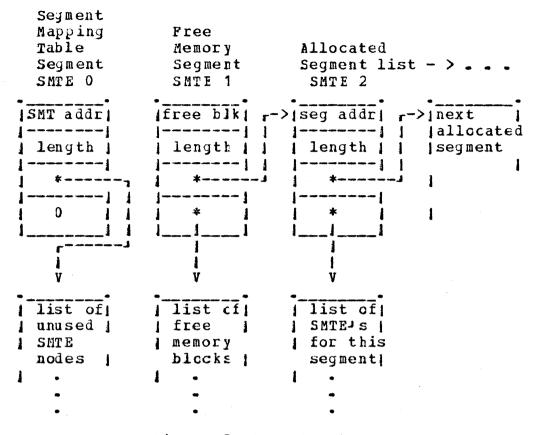

The Segmented environment uses segments as a means of representing memory allocations that are dynamic but are not allocated in any predictable order. A segment allocation creates an entry (or entries) in the Segment Mapping Table (SMT) that reserve a group of FMT entries. The SMT entry consists of four fields: 1) a virtual address origin of the segment, 2) a segment length, 3) an allocated segment list pointer, and 4) a pointer to the next SMT entry (SMTE) node in the segment. The virtual address origin and the segment length indicate the allocated virtual memory, while the allocated segment list pointer are used in memory reclamation. Note that a segment may consist of several SMTE nodes but each SMTE refers to a

contiguous section of virtual memory<sup>2</sup> (these contiguous sections of virtual memory are referred to as "blocks" in the following discussions). Figure 4 shows how a SMTE corresponds to the PMT entries.

| ~ | <br>~ |  |

|---|-------|--|

|   |       |  |

|   |       |  |

PMT

| SMT        |         |        |    |      |       |

|------------|---------|--------|----|------|-------|

| 11         |         |        |    | 1    | i     |

| 1          | couront | origir |    | 1    |       |

| SMT ENTRY  | segment | 01191  |    | PMT  | ENTRY |

|            |         | s      | 11 |      | 1     |

| 1 1        |         | e      | el | JEMT | ENTRY |

| 1 1        |         | g      | nl | 1    |       |

| 1 1        |         | m      | g٧ | PMT  | ENTRY |

| 1 1        |         | е      | t  |      |       |

|            | • .     | n      | h  | /    | 1     |

| 1 1        |         | t      |    | /    | 1     |

| 11         | segaent | origin | 1  |      | 1     |

| ISMT ENTRY |         |        | >  | EMT  | ENTRY |

| 11         |         | S      | 11 | ]    | 1     |

| 1 1        |         | e      | e۷ | PMT  | ENTRY |

| 1 1        |         | g      | n  |      |       |

| 1 1        |         | m      | g  | 1    | 1     |

| 11         |         | е      | t  | 1    | 1     |

|            |         | n      | h  | I    | 1     |

|            |         | t      |    |      |       |

Figure 4. Correspondence between SMT entries and PMT entries

<sup>2</sup>A contiguous section of virtual memory means a section of virtual memory with contiguous virtual addresses; ie., the physical addresses may be non-contiguous. When the Segment Marring Table is initially created, a page of virtual memory is reserved and entries are created as necessary to fill the rage. Two entries are set to nonzero values such that segment 0 (represented by entry 0) describes the origin and length of the SMT itself while segment 1 describes the remainder of unallocated virtual memory. The remaining SMT entries are set to zero and linked together (via the SMTE node list pointer) to form a list of unused SMTE nodes.

The allocated segment list pointer is used to link together the SMTE nodes that are the primary entry of each segment. As shown in Figure 5, the active segment list pointer of entry 0 and entry 1 are used for the purpose of indicating the beginning of the unused node list and the allocated segment list. Each segment of allocated storage is represented by a single SMTE or by a list of SMTE nodes.

The length field of an SMTE indicates the contiguous virtual memory size described by the entry node. Therefore segment 1 represents free or unallocated blocks of memory which can be used to satisfy allocation or expansion requests. An SMT entry node with a zero-value length field does not represent any menory but may be used in creation of a new segment.

The creation of a new segment and allocation of memory requires that searches of the unused SMTE node list and the free memory segment be made looking for an empty node and

Figure 5. SMT structures

for a free space block large enough to satisfy the allocation request. The new SMIE node is appropriately filled-in, removed from the unused entry node list and inserted into the allocated segment list.

Another feature of segmented memory management is the ability of segments to expand or contract in size. To expand a segment, an additional SMT entry (representing additional virtual memory) is chained to the primary SMTE such that the desired total segment size is allocated. To

contract a segment, the SMTE length field is reduced and a new free SMTE is created to represent the freed virtual memory.

The four functions of segmented memory management: 1) memory allocation, 2) memory de-allocation, 3) expansion of a memory allocation, and 4) contraction of a memory allocation, are provided by four of the routines shown in table III<sup>3</sup>. The only other externally called routine is SMREF which performs segmented-memory addressing. The remaining segmented environment routines perform internal house-keeping on the Segment Mapping Table and Page Mapping Table.

Because of the address mapping from virtual to physical pages, allocated segments may be re-arranged into single blocks by re-ordering the FMT. As a part of the memory management facilities, the routine SMSMT re-compresses segments into single blocks. In order to avoid memory fragmentation, this routine is invoked whenever an allocation request can not be satisfied using one block (in other words, the virtual memory described by a single SMTE node). Although the added memory area is forced to be a single block in processing a segment expansion request, it need not be virtually contiguous to the original segment memory area except when the segment being expanded is the SMT itself (ie. entry 0 of the table).

<sup>3</sup>See Appendix B for an informal PDL description of the segmented environment routines.

# TABLE III

## SEGMENTED FNVIRONMENT ROUTINES

| <br>        |                                         |

|-------------|-----------------------------------------|

| <br>Routine | Function Ferformed                      |

| SMREF       | Segmented memory access                 |

| SMA LC      | Allocate a new segment                  |

| SMFRE       | De-allocate a segment                   |

| SMADD       | Expand the size of a segment            |

| SMSUB       | Contract the size of a segment          |

| SMS MT      | Re-compress segments into single blocks |

| SM G ET     | Get a blcck cf free memory              |

| SMPUT       | Put a block back into the free list     |

| SMTAL       | Allocate a SMT entry node               |

| SMT FR      | Un-allocate a SMT entry node            |

| SM P MT     | Set PMT entries segment numbers         |

|             |                                         |

The procedure of addressing segmented memory is performed by the routine SMBEF. This routine accepts segmented addresses which consist of a segment number and a segment offset. The segment number is used to locate a segment block list in the SMN and the segment offset is used to locate the appropriate SMNF. By combining the offset value with the SMTE origin value, a virtual address is obtained and the segmented address translation is complete.

#### The ALGOL 68 Environment

The ALGOL 68 Environment is the "machine-level" of a hypothetical ALGOL 68 machine. For the OSU ALGOL 68 Compiler, this is the level or environment which interpretively executes pseudo-code generated from ALGOL 68 programs. In order to maintain compatibility with earlier versions of the OSU ALGOL 68 compiler, a translation phase must be incorporated which will convert pseudo-code generated by the codeemitter phase of Version IV of the compiler (listed in Appendix D) to pseudo-code suitable for the proposed runtime executor. This translation of the pseudo-code is concerned with two aspects: 1) replacing the addressing with stack-display-offset addressing and 2) modifying the instruction codes to handle explicit stack operations.

# ALGOL\_68 Level Addressing and Heap Storage Management

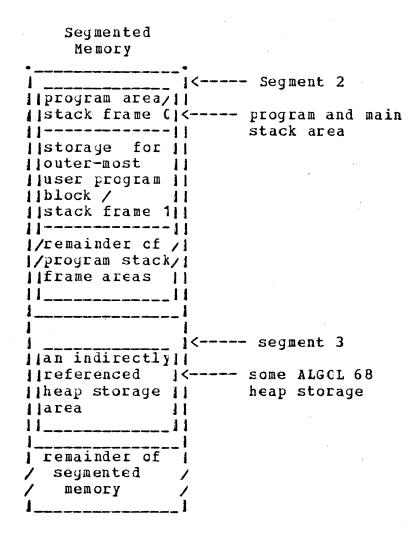

The ALGOL 68 Environment level uses an addressing scheme partially based on a stack environment. All instruction references to memory consist of the pair: stack-frame number, stack-frame offset. The stack-frame number is used to index a vector of stack-frame addresses which is added to the offset value to yield the effective address. In order for references to other instructions to be represented by this same address format, an extra outer display is artifically created (display number 0) that maps the storage area of where the program instruction codes are kept. All non-instruction references to memory (any address not a part of an instruction) take the form of valid segmented addresses. Figure 6 shows how segments are used to allocate memory for ALGCI 68 program stack areas and heap

Figure 6. Stack and Heap Storage in Segmented Memory

storage areas. The active display vector consists of segmented addresses that refer to the beginning of each stack frame (all stack frames in Figure 6 are contained in segment 2). As the stack grows, the segment containing the stack is expanded, which is accomplished through use of the segmented environment.

#### TABLE IV

# ITEMS ALLCCATED ON THE HEAP

| Descr          | iption of Item                                                         | Description of Why                                                                                                                                                                              |

|----------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| decla          | ariables explicitly<br>red to be "HEAP"<br>bles.                       | To maintain the hear vari-<br>ables even after closing<br>the block in which the<br>declaration appeared.                                                                                       |

| a fle<br>(excl | torage allocated to<br>wible rowed value<br>uding the array<br>iptor). | To allow for later expan-<br>sion of a flexible rowed<br>value (if subscript check-<br>ing is performed, then the<br>segmented address could be<br>easily stored with the<br>array descriptor). |

|                | rs and internal work<br>for transput.                                  | Tc maintain global storage<br>for transient I/O status,<br>information and data.                                                                                                                |

#### TABLE V

#### ITEMS ALLCCATED ON THE STACK

| _ |                                                                                                                                                                                                                                                                       |                                                                                                            |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

|   | Description of Item                                                                                                                                                                                                                                                   | Description of Why                                                                                         |

|   | All local variables of<br>primitive modes such as<br>INT, REAL, BOOL, CHAR,<br>etc.                                                                                                                                                                                   | The storage management for<br>these items conforms to<br>the requirements of a<br>stack-model environment. |

|   | All local reference-to<br>variables such as REF INT,<br>REF REF INT, REF REAL, CI<br>even REF REF amode.                                                                                                                                                              |                                                                                                            |

|   | All local structures which<br>do not contain items to be<br>put onto the heap (example<br>- STRUCT (REAL re, REAL im)<br>goes on the stack whereas<br>STRUCT (STRING s) causes<br>the storage of the flexi-<br>ble rowed value "s" to be<br>allocated in a heap area. | its descriptor may be                                                                                      |

|   | All local rowed values<br>that are not flexible                                                                                                                                                                                                                       | The storage management for these items conforms to                                                         |

that are not flexible rowed values.

these items conforms to the requirements of a stack-model environment.

As can be seen in Figure 6, heap storage is maintained in separate memory areas, thereby avoiding allocation conflicts with the stack area. This allows memory management of the stack at the ALG(L 68 level to be straight-forward but requires that references to the heap be made indirectly through a segmented address stored in the stack. There are two conclusions to be drawn from this: 1) it is easy to manipulate the storage of items allocated in heap areas but there is an overhead incurred for referencing them, and 2) the storage of an item allocated in a stack area may be manipulated only under very rigid conditions but such manipulation loes not require indirect addressing as for heap items. These conclusions were carefully considered before deciding what items of an ALGOL 68 program should be allocated in the stack area and what items should go on the heap. Tables IV and V show the results of several decisions as to where an item should be allocated.

# ALGOL 68 Level Local Storage Management

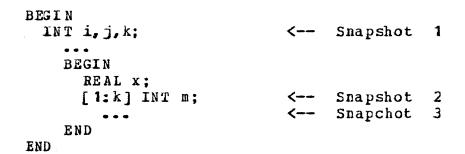

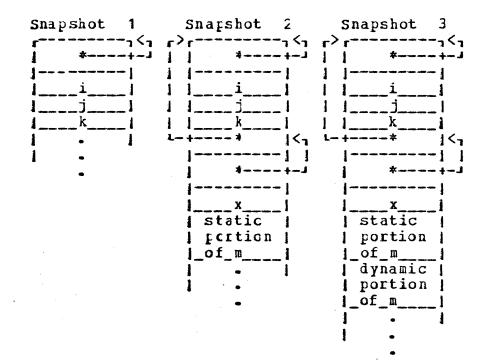

The ALGOL 68 level local storage management consists of a stack environment maintained within a segment. Figure 7 shows some snapshots of the run-time stack for a sample program. For each "BEGIN" in an ALGOL 68 program, a stackframe is created. As stack-frames are created, a list of addresses are maintained and copied into the beginning of the storage allocated for each stack-frame. The first snap shot of Figure 7 diagrams the contents of the stack after the first stack-frame has been created. Snapshot 2 of Figure 7 shows the state of the stack after the second stackframe has been created but before the storage for the rowed value "m" is allocated. Note that the first portion of the

Figure 7. Stack Display Layout

stack is an address that indicates the beginning of the first stack-frame and that further down in Snapshot 2 are two addresses which indicate the beginnings of the first and second stack-frames. As each new stack-frame is created, another address is added to the display maintained in the display vector and an updated copy of this list is stored onto the stack. The local storage management <sup>C</sup>an be summarized as the creation and destruction of stack-frames and parallels the techniques described in Gries (14).

## CHAPTER IV

# SUMMARY, CONCLUSIONS, AND FUTURE WORK

### Summary and Conclusions

In keeping with the goals of the Oklahoma State University ALGOL 68 Compiler project, this design adds flexibility with a limited expense of execution time. This design removes the major problem points of earlier versions of the compiler in three ways:

- 1. by adding flexible storage management facilities;

- by replacing the addressing scheme of earlier versions;

- 3. by expanding the storage capacity of the interpretive executor.

The Oklahoma State University ALGOL 68 Compiler is not only enhanced by the above capabilities, but the design of the run-time system should prove easier to modify for varying machine configurations than earlier versions thus enhancing the portability of the compiler. This can be attributed to the layered-design approach which applies very nicely to the segmented virtual memory features described here.

33

The O.S.U. ALGOL 68 user can benefit greatly from the added heap storage facilities and expanded storage capacities while the layered design approach should reduce the effort required of future implementors to modify or extend the capabilities of the interpretive executor.

#### Future Work

There are several suggested modifications which are based on the capabilities of the implementation machine. On a machine where primary storage is plentiful, two options may be exercised: 1) the size of the page fault table and the cache memory may be increased, or 2) the virtual memory level may be replaced altogether.

The modification of the size of the page fault table and the cache memory may be performed by adjusting the the initial value of the global variable indicating the page fault table size as shown in Appendix A, and by changing the appropriate table sizes used as the page fault table and the cache memory.

To replace the virtual memory level, the routine VMREF should be modified, the page mapping table kept and all other virtual memory level items discarded. Rather than consulting the page fault table, the routine VMREF should directly access a table of contiguous locations as if it were the simulated memory. The page mapping table translation of virtual addresses must be kept so that segmented memory level compression of free memory blocks can be performed, even though the result of the translation is only an index of the simulated memory in primary storage.

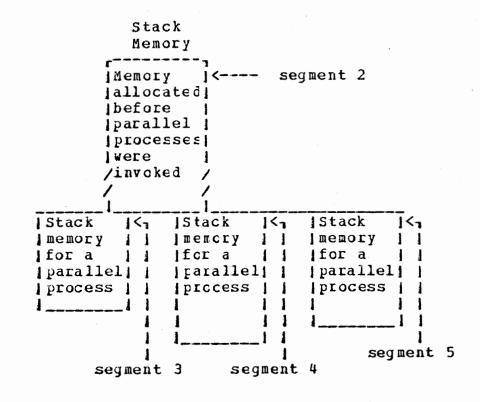

Future extensions to this work include the design of run-time facilities for simulated parallel processing. In ALGOL 68, parallel processing generally takes the form of a set of ALGOL 68 procedures which are to be executed as if they were executing simultaneously. The major problem

35

arises because while executing in parallel, different and distinct additions may be made to the stack environment. In fact, as shown in Figure 8, the portion of the stack allocated prior to the invocation cf the parallel procedures must be shared while distinct portions of the stack must be created for each parallel routine. This problem can be solved by allocating a new segment for the continuation of the stack environment of each parallel process. The address mapping of the stack environment is normally performed by the active display vector. In the case of parallel processing, multiple display vectors are maintained such that each parallel process may access the shared portion of the stack environment and may access its own extension of the stack. Each new display vector will contain a copy of the active display vector up to the point where a parallel procedure is invoked with added stack-frame addresses pointing to its extension of the active stack.

36

#### FEFERENCES

- Jensen, J. C. "Implementation of a Scientific Subset of ALGOL 68." (Unpub. M.S. thesis, Oklahoma State University, 1973.)

- (2) Berry, R. "A Practical Implementation of Formatted Transput in ALGCL 68." (Unpub. M.S. thesis, Oklahoma State University, 1973.)

- (3) Eyler, A. D. "The Implementation of a Subset of Procedures in an ALGCI 68 Compiler." (Unpub. M.S. thesis, Cklahoma State University, 1975.)

- Seay, W. M. "Implementation of a Subset of Modes in an ALGOL 68 Compiler." (Unpub. M.S. thesis, Oklahoma State University, 1976.)

- (5) Robertson, A. L. "Transformational Grammars: Their Applications and Implementation" (Unpub. M.S. thesis, Oklahoma State University, 1978.)

- (6) van Wijngaarden, A. (Ed.), B. J. Mailloux, J. E. L. Peck and C. H. Koster. "Report on the Algorithmic Language ALGCL 68." <u>Numerische</u> <u>Mathematik</u>, Vcl. 14 (1969), pp. 70-218.

- (7) van Wijngarrden, A. (Ed.), B. J. Mailloux, J. E. L.

Peck, C. H. A. Koster, M. Sintzoff, C. H.

Lindsey, L. G. L. T. Meertens, and R. G. Fisker.

"Revised Report on the Algorithmic Language

ALGOL 68." Berlin-Heidelberg: Springer-Verlag, 1976.

- (8) Taupin, D. "The AIGCL 68 Compiler of Paris-Sud University." <u>FICCEEDINGS of the 1975</u> <u>International Conference on ALGCL 68</u>, Stillwater, Cklahoma: (10-12 June 1975), pp. 16-22.

- (9) Barringer, H., and C. H. Lindsey, "The Manchester ALGOL 68 Compiler." <u>Proceedings of the Vth</u> <u>Annual III Conference on Implementation and</u> <u>Design of Algorithmic Languages</u>, Guidel, France: (16-18 May 1977), pp. 145-182.

- (10) Pierce, R. H., "An ALGOL 68 Run-Time Organization." (Unpub. M.S. thesis, Victoria University of Manchester, 1971.)

- (11) Currie, I. F., S. C. Bond, and J. D. Morison. "ALGOL 68-R." <u>ALGCL 68 Implementation</u>. J. E. L. Peck (ed). Amsterdam: North Halland Publishing Co., 1971, pp 21-34.

- (12) Lindsey, C. H, and S. G. van der Meulen <u>Informal</u> <u>Introduction tc ALGOL 68</u>, Revised Edition, Amsterdam: North-Holland Publishing Co., 1977.

- (13) Andre, J., and J. Eanatre (Ed.) <u>Proceedings of the</u> <u>Vth Annual III Conference on Implementation and</u> <u>Design of Algorithmic Languages</u>, Guidel, France: (16-18 May 1977).

- (14) Gries, D. <u>Compiler Construction for Digital</u> <u>Computers</u>, New York: John Wiley & Sons, Inc., 1971, pp. 171-211, 328-335.

- (15) Madnick, S. E., and J. J. Donovan <u>Operating Systems</u> New York: McGraw-Hill Book Co., 1974, pp. 105-208, 534-548.

- (16) Robertson, A., and G. E. Hedrick, "A Portable Compiler For An ALGOL 68 Subset." <u>Proceedings of</u> <u>the 1975 International Conference on ALGOL 68</u>, Stillwater, Cklahoma: (10-12 June 1975), pp. 59-63.

- (17) Van Doren, J. R. "Notes on Software Design Methods (Flowcharts and FDL's)." Presented as course material for Computer Structure & Programming, a graduate level course at Oklahoma State University.

## APPENDIX A

## DESCRIPTIONS OF RUN-TIME

# DATA STRUCTURES

The following descriptions are data structures used throughout the design. Additionally, some descriptions of the variables used in PDL descriptions of the presented design are included. For purposes of the design presentation, global "constants" have been chosen that meet all design requirements (these constants may or may not be optimal for performance considerations).

GLOBAL "Constants"

| page size         | (PSIZE) - page size value<br>(128 words) |   |

|-------------------|------------------------------------------|---|

| PMT size          | (NPMTE) - no. of PMT entries             |   |

| PFT size          | (NPFTE) - no. of PFT entries             |   |

| PMTE size         | (PELEN) - size of PMTE entry             |   |

|                   | (2 words)                                |   |

| SMTE size         | (SELEN) - size of SMTE entry             |   |

|                   | (4 words)                                |   |

|                   | (IORD) - read op-code                    |   |

|                   | (IOWR) - write op-code                   |   |

|                   | (PFILE) - paging disk file               |   |

|                   | (disk record length                      | = |

| •                 | memory page size)                        |   |

| PAGING "Hardware" |                                          |   |

| memory(1024)      | (MEMRY) - cache paging memory            |   |

|                   | (PFT) - Page Fault Table                 |   |

|                   | (APNUM) - active page number             |   |

|                   | (APPOS) - active pft entry               |   |

|                   |                                          |   |

### PFT entries (page fault table)

- 1) virtual page no.

- 2) cache-memory page slot address

- 3) LRU reference count

- 4) Modified bit

(sign position: >0 -- on, <0 -- off), and physical page no.

- **PMT entries** (page mapping table)

- 1) physical page no.

- 2) no. of the segment possessing this page

### SEGMENTED ADDRESS

- 1) segment mapping table entry number

- 2) segment offset address

SMT entries (segment mapping table)

- 1) Segment origin

- 2) Segment length

- 3) Allocated segment list pointer

- 4) Segment block list pointer

SEGMENT--A68 level "Hardware"

ERROR - termination code

SMTAR - SMT address register

- ASNUM active segment number

- ASORG active segment origin address

- ASLEN active segment length

- ASLNK active allocated segment list pointer

- ASPTR active segment block list pointer

- DSPLN display vector length

- DSPVT display vector of active stack frames (maximum of 20 active stack frames)

## APPENDIX B

## PDL DESCRIPTIONS OF RUN-TIME ROUTINES

The following figures are PDL descriptions of the Run-time routines. These descriptions are intended as a rough guide for implementation and therefore omit detailed or error-checking code in the interest of clarity.

## Paging Environment Routines

The four routines VMREF, VMPFX, VMPFT and VMSWP form a core of modules that deal directly with the virtual-memory/real-memory interface. With the exception of a few restricted segmentation level routines, all accesses to the paging level environment are performed indirectly through the routine VMREF. The few exceptions to this mechanism are the segmentation level routines that modify the Page Mapping Table for the purposes of garbage collection. This limited access allows the entire paging environment to be removed with the exception of the Page Mapping Table.

41

## Reference to virtual memory routine

```

vmref:

PROC (virtual address, huffer, start, stop,

I/O flag);

v := virtual address;

i := start - 1:

DO UNTIL i > stop;

CALL vmpfx (v, c, pfte);

¢ c is the returned cache memory address or

zero if the desired page is not in cache

memory ¢

¢ pfte is the rage slot number of

least-recently used page ∉

IF c = 0 THEN

vpage := v / page size ¢ PSIZE ¢;

voffset := v - (vrage * rage size);

CALL vmpfx ((2 * vpage), c, pn );

¢ if c is returned as zero, then there is

no PMT entry for the desired page, ie.

the reference is outside the virtual

address space ¢

IF c = 0 THEN

signal address error and guit;

FI;

ppage := memcry(c);

CALL vmswp (vrage, ppage, pfte );

c := pft(pfte, 2) + voffset;

FI:

i := i + 1;

v := v + 1;

IF write operation THEN

IF pfte > 0 TEEN

page := rage slot 0 which is always

paged-in ¢

set modified-flag of pft(pfte);

FI:

memory(c) := buffer(i);

ELSE

buffer(i) := nemory(c);

FI:

END:

RETURN;

END vmref:

```

### Page Fixing routine

```

wmpfx:

PROC (vaddr, c, p);

page := vaddr / page size;

offset := vaddr - (page * page size);

IF page = 0 THEN

¢ virtual page needed is page 0 ¢

c := offset;

p := 0:

RETURN;

FI:

IF page = active rgno & APNUM & THEN

¢ page needed was the last page accessed ¢

c := cache address cf active pft entry;

p := active pftn \not\in APPOS \not\in;

RETURN:

PI:

CALL vmpft (page, pfte, p);

¢ pfte is the returned pft entry position of

page in cach \epsilon-memory or zero if desired

page is not in memory ¢

IF pfte > 0 THEN

c := pft(pfte,2) + offset;

RETURN;

FI:

IF page \leq (2 * PMT size / page size) THEN

∉ if page requested is a PMT page, then the

physical rage number is known without

consulting the FMT ¢

CALL vmswp (page, page, p);

c := pft(p,2) + offset;

RETURN;

ELSE

c := 0;

RETURN;

FI:

END vmpfx;

```

Page Fault Table search routine

```

vmpft:

PROC (page, pfte, plru);

pfte := 0;

plru := 1;

max ref cnt := pft(plru,3);

DO 1 := 1 TO 7 EY 1;

IF pft(i,3) < 127 THEN

∉ increment reference count up to a

limit cf 127 ¢

pft(i,3) := rft(i,3) + 1

FI;

IF pft(i, 1) = rage THEN

¢ page has been found; return pft position ¢

active pgnc # APNUM # := page;

active pftn & APPOS & := i;

pfte := i;

pft(i,3) := 0;

FI;

IF pft(i,3) > max ref cnt THEN

return position of candidate for page-out #

plru := i;

max ref cnt := pft(i,3);

FI:

END;

RETURN;

END vmpft;

Page Swap routine

vmswp:

PROC (vpage, ppage, p);

IF pft(p, 4) > 0 THEN

perform page-out operation

FI;

perform page-in cretation;

¢ set virtual gage number, reference count,

and physical rage number ¢

pft(p,1) := vpage;

pft(p,3) := 0;

pft(p,4) := -ppage $$ set modified bit off $;

active pyno ¢ AFNUM ¢ := vpage;

active pftn ¢ APPCS ¢ := p;

RETURN;

END vmswp:

```

### Segmented Environment Routines

The segmentation level routines provide all the memory management functions and map all segment-type addresses into In keeping with the goal of modular virtual addresses. design, the segmented environment presents the appearance of being a collection of memory management primitives to all external environment levels. Thus the routines SMALC and are used for memcry allocation and un-allocation SMFRE respectively, and the routine SMREF is used for all segmented-level memory accesses. For expansion or contraction of an allocated memory area, the respective routines SMADD and SMSUB would be called.

Reference to segmented memory routine

smref: PROC (segment number, segment offset, buffer, start, stop, I/O flag ); snum := sequent number; sofst := segment cffset; len := stop - start + 1; i := start; j := i - 1; IF snum ≠ active segment no. ¢ ASNUM ¢ THEN sptr := SMT address \$\$ SMTAR \$\$ + (SMTE node size ∉ SELEN ∉ \* snum); CALL vmref (sptr, smte, 1, SMTE node size, IOFD); active segment no. ¢ ASNUM ¢ := snum; active segment crigin addr. & ASORG & := smte(1); active segment length & ASLEN & := smte(2); active alloc. seq. list ptr.  $\emptyset$  ASLNK  $\emptyset$  := smte(3); active seq. blk. list ptr. & ASPTR & := smte(4); FI: sorg := active sequent origin addr. & ASORG #; slen := active segment length \$\$ ASLEN \$\$; sptr := active seg. blk. list ptr. # ASPTR #; DO WHILE len > 0; DO WHILE sptr  $\neq$  0 & sofst  $\geq$  slen;

```

¢ follow segment chain pointer until entry

is found that contains desired offset

address ¢

sofst := sofst - slen;

CALL vmref (sptr, smte, 1, SMTE node size,

IORD);

sorg := smte(1);

slen := smte(2);

sptr := smte(4);

END:

1 := slen - sofst + 1;

¢ compute remaining length of seg. blcck ¢

IF 1 > len THEN

$ length of desired request is totally

contained in current SMT entry Ø

1 := len;

FI;

addr := sorg + scfst;

sofst := sofst + 1;

len := len - 1;

j:= j + 1;

CALL vmref (addr, buffer, i, j, I/O flag);

i := i + l;

END:

RETURN;

END smref;

```

#### Segment allocation routine

smalc:

| PROC | (segment | lengt | h, segmen | at. | number, 1 | cet | turn | code | ); |

|------|----------|-------|-----------|-----|-----------|-----|------|------|----|

| CAL  | L smtal  | (SMTE | address)  | ¢   | allocate  | a   | new  | SMTE |    |

| n    | ode ¢.   |       |           |     |           |     |      |      |    |

- sglen := segment length & rounded up to the nearest integer multiple of page size \$;

- CALL smget (sglen, SMTE, error code) ¢ search free segment fcr needed space, fill-in fields of SMTE node tc reflect allocated storage area and set error code (on cf three possible conditions: a) a free block of sufficient size was found, b) no free block was adequate but compression cf segments could produce the necessary free block, and c) insufficient total memory to perform allocation). ¢;

- IF error code is above condition "c" THEN set return code to indicate allocation failure; RETURN;

ELSE

set return code to no error condition; FI;

IF error code is above condition "b" THEN

CALL snsmt \$\not\$ congress free memory segments \$\not\$;

CALL snget (sglen, SMTE, error code);

\$ search free segment list again for needed

segment of free memory \$;

IF error code is not condition "a" THEN set return ccde to indicate allocation failure;

RETURN:

FI;

FI;

sptr := SMT address \$\nothermathcal{e}\$ SMTAR \$\nothermathcal{e}\$ + SMTE node size

\$\nothermathcal{e}\$ SELEN \$\nothermathcal{e}\$ + 2 \$\nothermathcal{e}\$ compute address of primary

allocated segment list pointer \$\nothermathcal{e}\$;

CALL vmref (sptr, SMTE(3), 1, 1, IORD);

CALL vmref (sptr, SMTE address, 1, 1, IOWR)

\$\nu\$ insert new segment into allocated segment

list \$\nu\$;

segment number := (SMTE address - SMT address) /

SMTE node size:

CALL vmref(SMTE address, SMTE, 1, SMTE node size, IOWR) & update smt entry #;

CALL smpmt (SMTE(1) & segment crigin &, SMTE(2)

# segment length &, segment number) & set the

segment number fields of the PMT entries that

are in the new segment #;

DEFINITION

RETURN;

END smalc;

## Segment de-allocation routine

```

smfre:

PROC (segment number );

SMTE address := (segment number * SMTE node

size) + SMT address ⊄ SMTAR ⊄;

sptr := SMTE address;

DO WHILE sptr \neq (;

CALL vmref (sptr, SMTE, 1, SMTE node size,

IORD) & fetch each SMTE for segment ¢;

sptr := SMTE(4) $$ save ptr to next SMTE $$;

CALL smpmt (SMTE(1), SMTE(2), 1) & set the

segment number fields of the FMT entries

that are in the current segment \emptyset;

CALL smput (SMIE address) ¢ return memory

block to free list ¢;

SMTE address := sptr;

END:

RETURN:

END smfre;

```

#### Memory block allocation routine

```

smget:

PROC (segment length, new SMTE, error code );

total free size := 0;

sptr := SMT address & SMTAR & +

SMTE node size & SELEN Ø;

last := sptr:

DO UNTIL sptr = C;

addr := sptr;

CALL vmref (sptr, free SMTE, 1, SMTE node

size, IORD) & fetch each SMTE of free

memory segment (segment 1) ¢;

IF free SMTE(2) < sequent length THEN

total free size := total free size +

free SMTE(2) ¢ total the amount of

free memory space \emptyset;

last := sptr;

sptr := free SMIE(4) $$ get pointer to

next SMTE #;

ELSE

sptr := 0;

FI:

END:

IF free SMTE(2) < segment length THEN

IF total free size < segment length THEN

error code := # insufficient total space #:

ELSE

error code := ¢ insufficient contiguous

space ¢;

FI;

ELSE

IF free SMTE(2) > segment length THEN

new SMTE(1) := free SMTE(1) ¢ copy

segment origin ¢;

new SMTE(2) := segment length;

free SMTE(1) := free SMTE(1) +

segment length ¢ update origin of

free memory block ¢;

free SMTE(2) := free SMTE(2) -

segment length ¢ update length of

free memory block ¢;

new SMTE(3), new SMTE(4) := 0;

CALL vmref (last, free SMTE, 1, SMTE

node size, ICWR);

ELSE

new SMTE(1) := free SMTE(1) ¢ copy

sequent crigin #:

new SMTE(2) := free SMTE(2) ¢ copy

segment lergth ¢;

new SMTE(3), new SMTE(4) := 0;

IF last = addr THEN

```

free SMTE(1), free SMTE(2) := 0 ¢ if the SMIE found is entry 1 in the SMT, then reset its origin and length fields to zero ¢; CALL vmref (addr, free SMTE, 1, SMTE node size, IOWR); ELSE last := last + 3 \$\not\$ update pointer to indicate block list ptr field of previous SMTE in free memory block list ¢; CALL vmref (last, free SMTE(4), 1, 1, IOWR) ¢ delete current SMTE from free memcry block list ¢; CALL SMTFE (addr) & un-allocate unused SMIE ¢; FI: FI; FI; RETURN; END smget;

.

```

saput:

PROC (SMTE address );

addr := SMTE address;

CALL vmref (addr, cld SMTE, 1, SMTE node size,

IORD) ¢ fetch cld SMTE ¢;

last := SMT address & SMTAR & +

SMTE node size:

DO UNTIL last = C:

CALL varef (last + 2, sptr, 1, 1, IORD)

¢ fetch each SMTE of allocated segment list ¢;

IF sptr = addr THEN

sptr := old SMIE(3);

CALL vmref (last + 2, sptr, 1, 1, IOWR)

¢ update allocated segment list ¢;

last, old SMTE(3) := 0;

ELSE

last := sptr;

FI;

END;

sptr := SMT address + SMTE node size + 3;

CALL vmref (sptr, cld SMTE(4), 1, 1, IORD)

¢ fetch pointer to free memory block

list p;

CALL vmref (sptr, addr, 1, 1, IOWR) & insert

old SMTE into list #:

CALL vmref (addr, cld SMTE, 1, SMTE node size,

IOWR) ∉ update free memory block list ∉;

RETURN:

END smput;

PMTE segment number update routine

smpmt:

PROC (origin, length, segment number );

addr := PMTE ncde size & PELEN & * (origin /

page size ¢ PSIZE ¢) - 1;

npgs := (length + page size - 1) / page size;

DO i := 1 TO npgs BY 1;

addr := addr + FMTE node size;

CALL vmref (addr, segment number, 1, 1, IOWR)

entries marred by the input segment

origin/length ¢;

END;

RETURN:

```

```

END smpmt;

```

## APPENDIX C

## PROGRAM DESIGN LANGUAGE

The Program Design Language descriptions of the Runtime routines use an informal PDL similar to that used by Oklahoma State University Computing and Information Sciences Department. Specifically the introductory notes shown here are based on notes by Dr. J. R. Van Doren describing an informal PDL used as Computer Science course material (17).

Modules or Procedures format

Module name: PROC optional parameter list;

Sequence of PDL and/or English language statements

RETURN END module name;

#### Module Invocation

CALL module name(optional parameter list);

## Elementary Decision logic

IF condition THEN

Sequence of PDL and/or English language statements ELSE Sequence of PDL and/or English language statements

FI;

or

IF condition THEN

Sequence of PDL and/or English language statements FI;

## Looping Constructs

DO WHILE condition; Sequence of PDL and/or English language statements; END;

DO UNTIL condition;

Sequence of PDL and/or English language statements; END;

DO index = initial value TO final value BY increment; Sequence of PDL and/or English language statements; END;

Comments or Remarks

∉ Comment or Remark statement ∉

# APPENDIX D

# OPERATION CODES OF THE VERSION IV

# OSU ALGOL 68 COMPILER

The Version IV OSU ALGOL 68 Compiler interpretively executes 4-tuple pseudo-code. The meanings of the various 4-tuples are listed below.

## BASIC OPERATION CODES

|     | 00, 00, 00<br>R2, R3 | BLOCK ENTRY<br>BLOCK EXIT             |

|-----|----------------------|---------------------------------------|

| 020 | NZ NJ                | R2 IS THE ELEMENTAL MODE OF THE       |

|     |                      | RETURNED VALUE                        |

|     |                      | R3 IS THE NUMBER OF ROWS FOR R2       |

| 030 | 01, 00, R4           | UNCONDITIONAL JUMP/BRANCH             |

|     |                      | <b>R4 IS THE BRANCH ADDRESS</b>       |

| 030 | 02, R3, R4           | CONDITIONAL JUMP/BRANCH               |

|     |                      | R3 IS THE ID OF THE CONDITIONAL VALUE |

|     |                      | <b>R4 IS THE BRANCH ADDRESS</b>       |

| 030 | 03, R3, R4           | LOAD ADDRESS                          |

|     |                      | R3 IS THE DISPLACEMENT TO BE ADDED TO |

|     |                      | THE RESOLVED ADDRESS                  |

|     |                      | R4 IS THE ID OF THE ADDRESS TO BE PUT |

|     |                      | ONTO THE STACK TOP                    |

| 030 | 04, R3, R4           | BRANCH WITH INDEX                     |

|     |                      | R3 IS THE ID OF THE INDEX VALUE       |

|     |                      | R4 IS THE ADDRESS OF THE BRANCH TABLE |

| C30 | 05, R3, R4           | SET FLAG ON DATA SWITCH               |

|     |                      | R3 IS THE FLAG NUMBER                 |

|     |                      | R4 IS THE DATA SWITCH NUMBER          |

| 040 | R2, 00, R4           | ALLOCATE SYMBOL                       |

|     |                      | R2 IS THE MODE OF THE SYMBOL          |

|     |                      | <b>R4 IS THE IDENTIFIER NUMBER</b>    |

| 050 | R2, R3, R4           | SET STATEMENT NUMBER                  |

|     |                      | <b>R2 IS THE STATEMENT NUMBER</b>     |

|     |                      | R3 IS THE ELEMENTAL MODE OF THE STACK |

|     |                      | TOP VALUE TO BE VOIDED                |

|       |            | R4 IS THE NUMBER OF ROWS                                  |

|-------|------------|-----------------------------------------------------------|

| 061   | R2, R3, R4 | UPDATE SYMBOL TABLE                                       |

|       |            | R2 IS THE MODE OF SYMBOL TABLE ENTRY                      |

|       |            | R3 IS THE ADDRESS                                         |

|       |            | <b>R4 IS THE IDENTIFIER NUMBER</b>                        |

| 062   | R2, R3, R4 | PRINT UNFORMATTED                                         |

|       |            | R2 IS THE ELEMENTAL MODE OF THE VALUE                     |

|       | · .        | TO BE PRINTED                                             |

|       |            | R3 IS THE NUMBER OF ROWS                                  |

|       |            | R4 IS THE ID OF THE VALUE TO BE                           |

| 070   | DD DD D4   | PRINTED                                                   |

| 070   | R2, R3, R4 | BECOMES                                                   |

|       |            | R2 IS THE MODE OF THE VALUE TO BE                         |

|       |            | ASSIGNED<br>R3 IS THE SOURCE ID                           |

|       |            |                                                           |

| 000   | R2, R3, R4 | R4 IS THE DESTINATION ID<br>READ UNFORMATTED              |

| 000   |            | READ UNFORMATIED<br>R2 IS THE ELEMENTAL MODE OF THE VALUE |

|       |            | TO BE READ                                                |

|       |            | R3 IS THE NUMBER OF ROWS                                  |

|       |            | R4 IS THE ID OF THE VALUE TO BE READ                      |

| 090   | R2, R3, R4 | DEFINE LABEL                                              |

| 030   |            | R2 IS THE ADDRESS OF THE LABEL                            |

|       |            | R3 IS THE NEGATIVE OF THE BLOCK                           |

|       |            | NUMBER                                                    |

|       |            | R4 IS THE ID OF THE LABEL                                 |

|       |            |                                                           |

| 50N   | R2, R3, R4 | ALLOCATE DESCRIPTOR FOR ARRAYS                            |

|       |            | N IS THE ELEMENTAL MODE                                   |

|       |            | R2 IS THE ID OF THE ARRAY                                 |

|       |            | R3 IS THE NUMBER OF ROWS IN THE ARRAY                     |

|       |            | <b>R4 IS THE ADDRESS OF THE SKELETON</b>                  |

|       |            | DESCRIPTOR(S)                                             |

| 510   | R2, R3, R4 | LOAD SUBSCRIPTED                                          |

|       |            | R2 IS THE NUMBER OF ROWS IN THE ARRAY                     |

|       |            | R3 IS THE ID OF THE ARRAY                                 |

|       |            | R4 IS THE SYMBOL TABLE POINTER OF THE                     |

|       |            | TEMPORARY SYMBOL TABLE ENTRY                              |

|       |            | GENERATED CONTAINING THE                                  |

|       |            | CALCULATED ADDRESS                                        |

| 52N   | R2, R3, R4 | MOVE ROW OF OPERANDS                                      |

|       |            | N IS THE ELEMENTAL MODE                                   |

|       |            | R2 IS THE NUMBER OF ROWS                                  |

|       |            | R3 IS THE ID OF THE SOURCE OPERAND                        |

|       |            | R4 IS THE ID OF THE DESTINATION                           |

| C 7 4 | nn nn n4   | OPERAND                                                   |

| 230   | R2, R3, R4 | ALLOCATE SLICING DESCRIPTOR                               |

|       |            | R2 IS THE NUMBER OF ROWS                                  |

|       |            | R3 IS THE IS OF THE ARRAY TO BE                           |

|       |            | SLICED<br>DA IS THE ADDRESS OF THE SLICING                |

|       |            | R4 IS THE ADDRESS OF THE SLICING                          |

| 511   | R2, R3, R4 | TEMPLATE<br>Lower Bound                                   |

| J41   | NL NJ NA   | R2 IS THE NUMBER OF ROWS IN THE ARRAY                     |

|       | •          | NY TO THE WONDER OF KONO IN THE AKKAN                     |

.

٢.