# DESIGN AND IMPLEMENTATION OF A LOW POWER T-GATE CELL LIBRARY AND COMPARISON WITH ITS CMOS EQUIVALENT

By

### KANISHKA DE

Bachelor of Technology in Electronics and

**Communication Engineering**

West Bengal University of Technology

Kolkata, West Bengal, India

2010

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of MASTER OF SCIENCE December, 2014

# DESIGN AND IMPLEMENTATION OF A LOW POWER T-GATE CELL LIBRARY AND COMPARISON WITH ITS CMOS EQUIVALENT

Thesis Approved:

Dr. Chris Hutchens

Thesis Adviser

Dr. Louis G. Johnson

Dr. Carl D. Latino

### ACKNOWLEDGEMENTS

I would like to take this opportunity to thank my committee chair and advisor Dr. Chris Hutchens and express my sincere gratitude for his valuable advice, cooperation, patience and understanding. I wish to express my sincere thanks to Dr. L. Johnson and Dr. C. Latino for serving on my graduate committee. I feel proud to have served as a research assistant in the Mixed Signal VLSI Design Lab at Oklahoma State University. It had been a wonderful and exciting journey and learning experience to work at MSVLSI Design Lab. History of electronic design had shown ups and downs following its nature. The advent of new technology heralds the obsoletion of the old one. Down the road in future in another 25-30 years we might see a dramatic change in technology node with CMOS design being no longer into great practice but the knowledge that I received at MSVLSI Lab will always be extendable to new technologies.

I appreciate MSVLSI Lab team members Mr. Rehan Ahmed, Dr. Ran Liao, Dr. An Guanglei, Mr. Cheng Hao and Mr. Aniket Kulkarni for all their cooperation, valuable suggestions and comments along the course of working at MSVLSI Lab. Above all, I am grateful to my parents for their constant moral and financial support that inspired me to carry on my research ignoring all obstacles in my way.

#### Name: KANISHKA DE

#### Date of Degree: DECEMBER, 2014

### Title of Study: DESIGN AND IMPLEMENTATION OF A LOW POWER T-GATE CELL LIBRARY AND COMPARISON WITH ITS CMOS EQUIVALENT Major Field: ELECTRICAL ENGINEERING

Abstract:

This work presents the design methodologies, considerations and practical implementation techniques of a sub-threshold/ moderate inversion variability aware Transmission Gate based digital cell library. The implementation method of a reduced ASIC cell library containing minimum number of logic gates sufficient for further front end and back end processing is described. The proposed library targets a reduced implementation time and effort suitable for academic and industrial environment aiming minimum power consumption in battery less devices, portable electronic gadgets or wireless micro sensor networks where computation speed is not of prime concern. To the authors best knowledge, none of the literature till date demonstrates clearly and in a consolidated manner the applicability of T-Gate logic topology as a candidate for ultralow power applications. Hence, a comparison is presented with equivalent low power CMOS logic gates. Circuit behavior can be significantly impacted due to MOSFET parameter variation. Clear simulation based measurement techniques are presented for measuring concerned parameters like input capacitance, Static Noise Margin(SNM) and I<sub>OFF</sub> of the T-Gate logic cells and compared with its CMOS equivalent at the same PVT corners. It is observed that the T-Gate shows lower normalized input capacitance than CMOS logic gates. A statistical analysis of logic failure is also presented along with its potential solutions for improvement. As compared to the CMOS gates, the T-Gate logic gates are found to demonstrate slightly narrower distribution of the switching threshold point(V<sub>Trip</sub>) when performed 200 point Monte Carlo simulation taking process variation and mismatch into account. The CMOS gates demonstrate better static noise margin and hence more robust than T-Gate logic cell and suitable for lower supply voltage operation. A comparison of I<sub>OFF</sub> is presented to compare the static behavior of the two topologies. The details of device and gate sizing methodology are described along with necessary references. The library is characterized and abstracted to generate necessary files for further processing. A target system is synthesized and a seven stage ring oscillator is simulated in both topologies and is compared to make conclusion based on the observations. T-Gate logic cells demonstrate better static behavior but outperformed by its CMOS logic equivalent in terms of energy consumed per cycle within the range of VDDD from 400mV to 600mV. T-Gate logic gates are slower than its CMOS counterpart at any VDDD of operation and insignificant improvement is achieved with increasing power supply.

### TABLE OF CONTENTS

| Chapter                                                       | Page |

|---------------------------------------------------------------|------|

| I. INTRODUCTION TO SUBTHRESHOLD OPERATION AND APPLICATION     | N1   |

| 1.1 INTRODUCTION                                              | 1    |

| 1.2 GOVERNING EQUATIONS AND REGION OF OPERATIONS              |      |

| 1.3 VTrip OR SWITCHING THRESHOLD POINT OF AN INVERTER         |      |

| 1.4 PREVIOUS WORK AND MOTIVATION                              |      |

| 1.4 THESIS ORGANIZATION                                       | 10   |

|                                                               | 11   |

| II. NORMALIZED INPUT CAPACITANCE COMPARISON                   | 11   |

| 2.1 INTRODUCTION                                              | 11   |

| 2.2 EXPERIMENT SETUP                                          |      |

| 2.3 SIMULATION RESULTS AND DETAILED ANALYSIS                  |      |

| 2.4 CHAPTER SUMMERY.                                          |      |

|                                                               |      |

| III. COMPARISON OF SNM AND FAILURE RATE                       | 17   |

| 3.1 INTRODUCTION                                              | 17   |

| 3.2 OBJECTIVE                                                 |      |

| 3.3 EXPERIMENT SETUP AND PROCEDURE                            |      |

| 3.4 FAILURE AND REDUCTION IN FAILURE BY INCREASING VDDD       |      |

| 3.5 EXTENSION TO T-GATE LOGIC GATES                           |      |

| 3.6 CHAPTER SUMMERY                                           | 34   |

|                                                               |      |

| IV. IOFF COMPARISON BETWEEN T-GATE AND CMOS LOGIC             | 35   |

| 4.4 INTRODUCTION                                              | 35   |

| 4.2 EXPERIMENT SETUP                                          |      |

| 4.3 OBSERVATIONS                                              |      |

| 4.4 I <sub>OFF</sub> COMPARISON BETWEEN CMOS AND T-GATE LOGIC |      |

| 4.5 CHAPTER SUMMERY.                                          |      |

|                                                               |      |

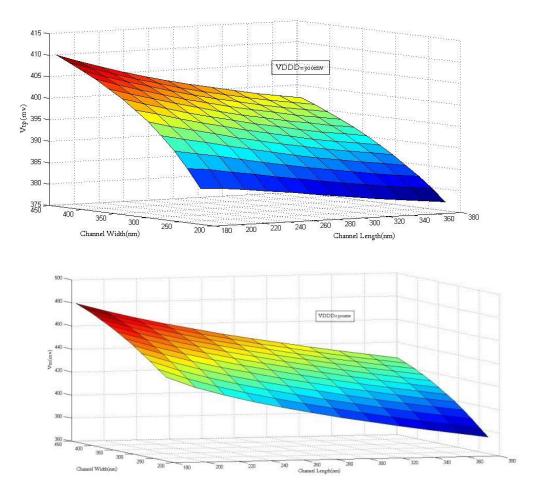

| V. DEVICE SIZING FOR MINIMUM POWER DELAY PRODUCT              | 49   |

| 5.1 INTRODUCTION                                      | 49   |

|-------------------------------------------------------|------|

| 5.2 EXPERIMENT SETUP                                  | 50   |

| 5.3 ALGORITHM FOR PDP VS DEVICE GEOMETRY MEASUREMENT. | 50   |

| 5.4 EXPERIMENT RESULTS AND OBSERVATION                | 51   |

| 5.5 CHAPTER SUMMERY                                   | 56   |

| VI. LOAD BASED DEVICE SIZING                          | 57   |

| 6.1 INTRODUCTION                                      | 57   |

| 6.2 EXPERIMENT SETUP                                  |      |

| 6.3 SIMULATION RESULTS AND OBSERVATION                |      |

| 6.4 CHAPTER SUMMERY.                                  |      |

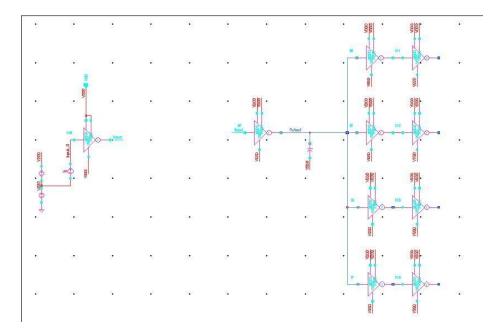

| VII. CONTROLLER FOR MICRONEURAL INTERFACE             | 63   |

| 7.1 ARCHITECTURE DESCRIPTION                          | 63   |

| VIII. REDUCED ASIC CELL LIBRARY DESIGN                | 68   |

| 8.1 INTORDUCTION                                      | 68   |

| 8.2 LIBRARY IMPLEMENTATION METHOD                     | 68   |

| 8.3 CHAPTER SUMMERY                                   | 72   |

| IX. T-GATE SIZING METHODOLOGY                         | 73   |

| 9.1 INTRODUCTION                                      | 73   |

| 9.2 GATE SIZING METHODOLOGY                           |      |

| 9.3 DEVICE SIZING                                     |      |

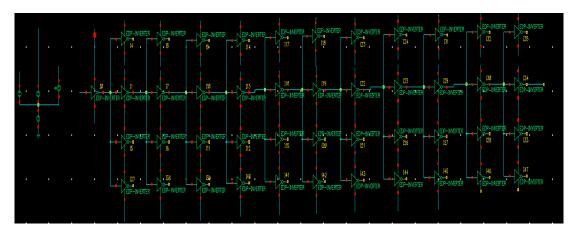

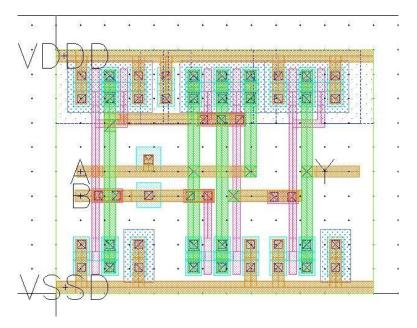

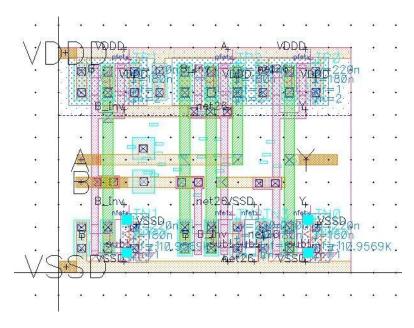

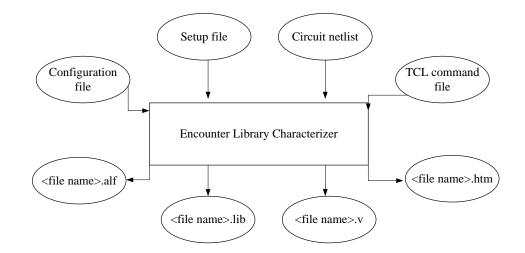

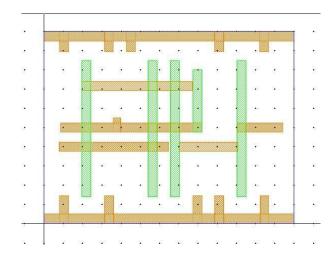

| X. T-GATE CELL LIBRARY IMPLEMENTATION                 | 82   |

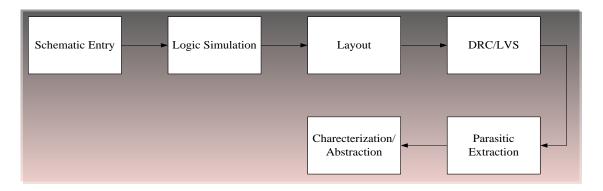

| 10.1 IMPLEMENTATION FLOW REVIEW                       | 82   |

| XI. SYNTHESIS RESULTS COMPARISON AND CONCLUSION       | 86   |

| 11.1 RESULTS COMPARISON                               | 86   |

| 11.2 CONCLUSION                                       | 90   |

| REFERENCES                                            | 91   |

| APPENDICES                                            | 94   |

| APPENDIX A                                            | 94   |

| APPENDIX B                                            | .104 |

### LIST OF TABLES

### Table

## Page

| 1.1 Transistor parameters comparison, VTn =430mV at VDDD=400mV                        | 4  |

|---------------------------------------------------------------------------------------|----|

| 2.1 Normalized Input capacitance comparison between T-Gate and CMOS                   | 13 |

| 2.2 Propagation Delay for different T-Gate logic gates                                | 14 |

| 3.1 V <sub>Trip</sub> of NAND2X1 and NOR2X1 vs Increasing width and Length            | 23 |

| 3.2 Proposed Device sizing for CMOS NAND2X1                                           | 26 |

| 3.3 Proposed Device sizing for CMOS NOR2X1                                            | 26 |

| 3.4 Change in V <sub>Trip</sub> of NAND2X1 with increasing NMOS no of fingers         | 26 |

| 3.5 Change is V <sub>Trip</sub> of NOR2X1 with increasing no of PMOS fingers          | 27 |

| 3.6 NAND2X1 V <sub>Trip</sub> with NOF PMOS=1                                         | 27 |

| 3.8 Device sizing for NAND2X1 and NOR2X1 resulting close to mid-rail $V_{Trip}$       |    |

| 3.9 PDP measurements corresponding to $1^{st}$ and $2^{nd}$ combinations in Table 3.8 |    |

| 3.10 Failure Rate for INVX1 vs increasing VDDD                                        |    |

| 3.11 Failure Rate for NAND2X1 vs increasing VDDD                                      |    |

| 3.12 Failure rate of NOR2X1 vs increasing VDDD                                        |    |

| 3.13 Change in INVX1 Failure Rate with increasing device fingers                      |    |

| 3.14 PDP measurement for INVX1 from Table 3.10 and Table 3.13                         |    |

| 3.15 Failure Rate of INVX1 vs Increasing VDDD                                         |    |

| 3.16 Failure Rate of T-Gate NAND2X1 vs increasing VDDD                                |    |

| 3.17 Failure Rate of T-Gate NOR2X1 vs increasing VDDD                                 |    |

| 3.18 Ring Oscillator frequency vs increasing VDDD                                     |    |

| 4.1 Ion/Ioff at width=300nm and Length=180nm                                          |    |

| 4.2 Comparison of IOFFs between T-Gate and CMOS logic Gates                           |    |

| 4.3 IOFF Comparison for T-gate and CMOS 2:1 MUX                                       |    |

| 6.1 Rise time and Electrical effort                                                   | 60 |

| 8.1 Library cell lists                                                                |    |

| 8.2 Synthesis result for different cell libraries (without HA in reduced set 3)       |    |

| 8.3 Synthesis result for different cell libraries (without HA in reduced set 3)       |    |

| 11.1 static power, dynamic power and energy per cycle comparison                      |    |

| 11.2 Synthesis results for MNI controller                                             |    |

| 11.3 MC simulation for VTrip of T-Gate NAND2X1 at VDDD=400Mv                          | 90 |

|                                                                                       |    |

## LIST OF FIGURES

# Figure

# Page

| <ol> <li>Id vs VDS for sub-threshold and above VGSs for NMOS</li></ol>  | 3<br>4<br>5<br>6<br>6<br>7<br>V7<br>8<br>9<br>12<br>13<br>14<br>15<br>16<br>16<br>20<br>21<br>21<br>22<br>24<br>24<br>25<br>25<br>28<br>28 |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                         |                                                                                                                                            |

| 3.12.b Butterfly for 3rd combination in Table3.8                        | 28                                                                                                                                         |

| 3.13 Butterfly for 4th combination in Table 3.8                         | 29                                                                                                                                         |

| 3.14 Butterflies: best case of CMOS Logic and best case of T-gate Logic |                                                                                                                                            |

| 4.1 Experiment Setup                                                    |                                                                                                                                            |

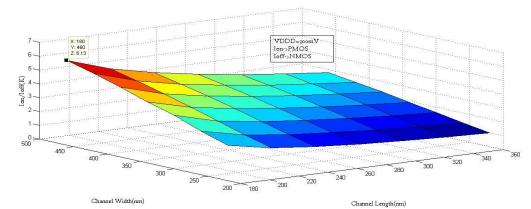

| 4.2 Ion/Ioff, PMOS supplying Ion and NMOS supplying Ioff                |                                                                                                                                            |

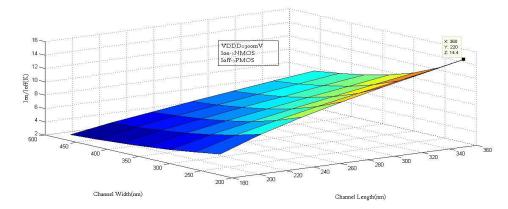

| 4.3 Ion/Ioff, NMOS supplying Ion and PMOS supplying Ioff                |                                                                                                                                            |

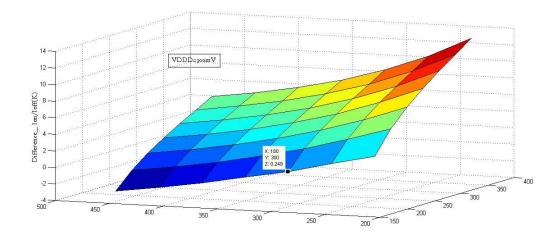

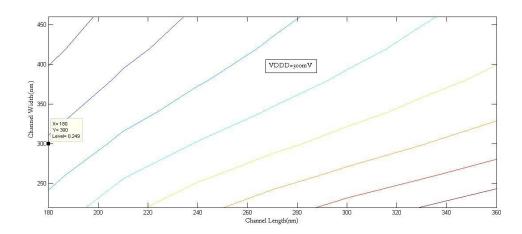

| 4.4 Surface plot for Difference_(Ion/Ioff)                              | 37                                                                                                                                         |

|                                                                         |                                                                                                                                            |

| 4.5 contour plot for Difference_(Ion/Ioff)                                                 | 37  |

|--------------------------------------------------------------------------------------------|-----|

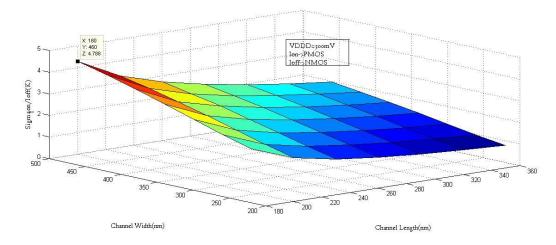

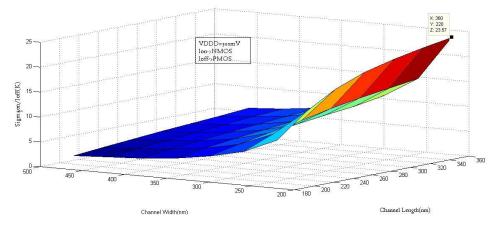

| 4.6 Sigma(Ion/Ioff), Ion->PMOS, Ioff-> NMOS                                                |     |

| 4.7 Sigma(Ion/Ioff), Ion->NMOS, Ioff-> PMOS                                                |     |

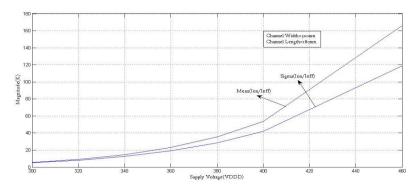

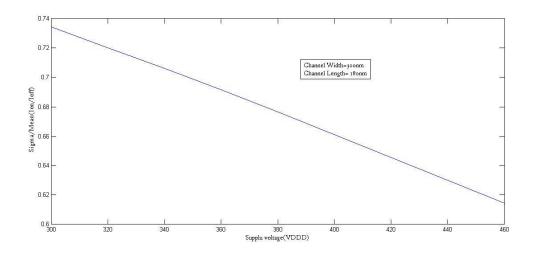

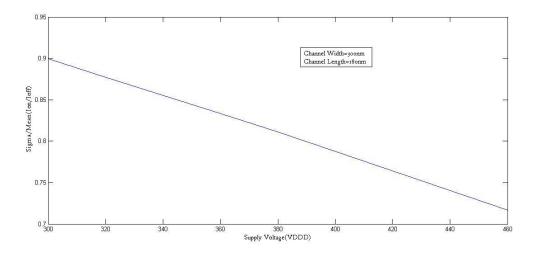

| 4.8 Mean and Sigma of Ion/Ioff, Ion->NMOS, Ioff-> PMOS vs VDDD                             |     |

| 4.9 Sigma (Ion/Ioff) vs VDDD, Ion-> PMOS, Ioff->NMOS                                       |     |

| 4.10 Sigma (Ion/Ioff) vs VDDD, Ion-> NMOS, Ioff->PMOS                                      |     |

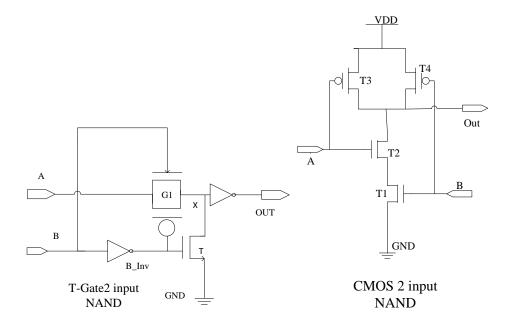

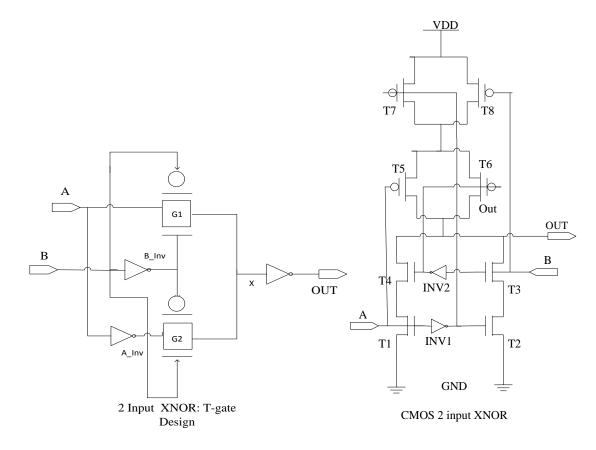

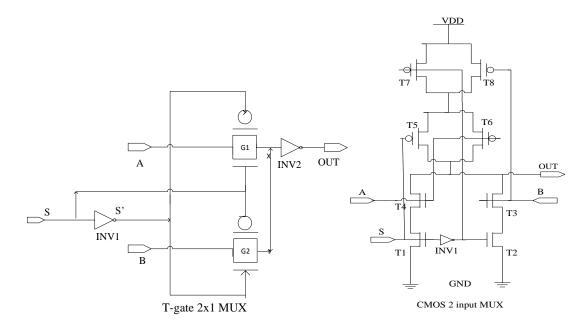

| 4.11 T-gate(left) and CMOS(right) two input NAND                                           |     |

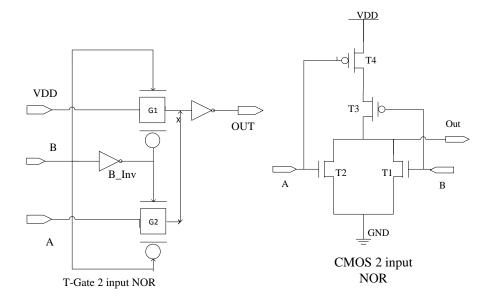

| 4.12 T-gate(left) and CMOS(right) two input NOR                                            |     |

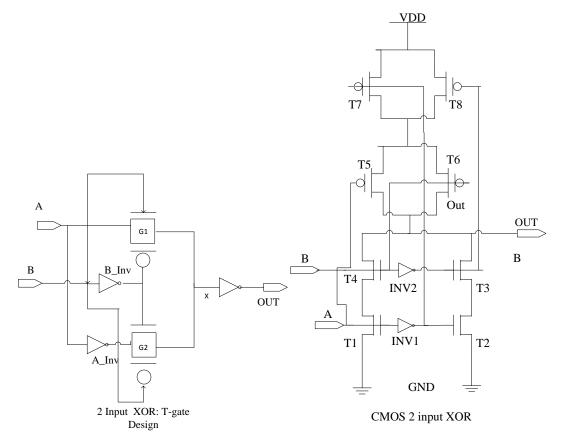

| 4.13 T-gate(left) and CMOS(right) two input XOR                                            |     |

| 4.14 T-gate(left) and CMOS(right) two input XNOR                                           |     |

| 4.15 T-gate(left) and CMOS(right) 2:1 MUX                                                  |     |

| 5.1 FO4 inverter chain as circuit under test                                               |     |

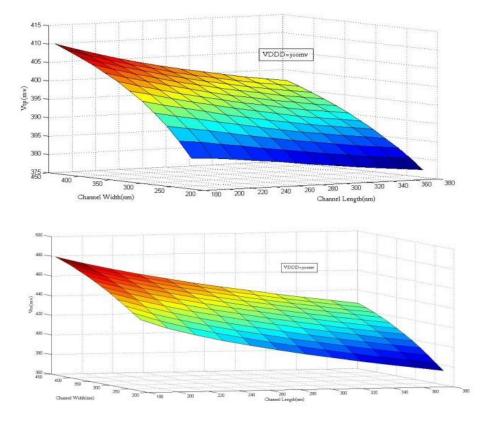

| 5.2 VTp(top) and VTn(bottom) variation with changing finger Width and Length               |     |

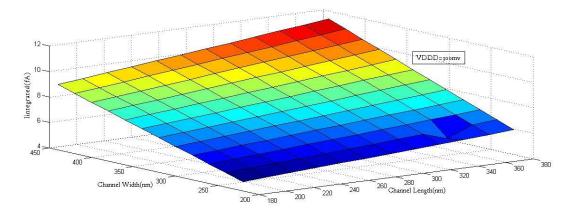

| 5.3 change in Iintegrated current with changing device geometry                            |     |

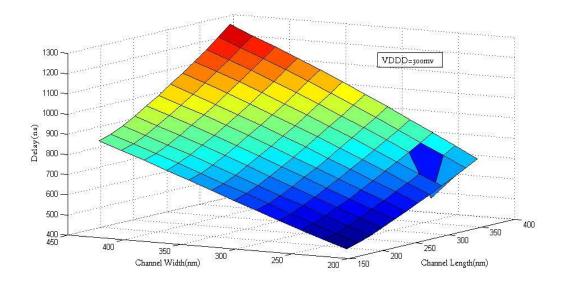

| 5.4 Surface Plot: Impact of device geometry change on delay                                |     |

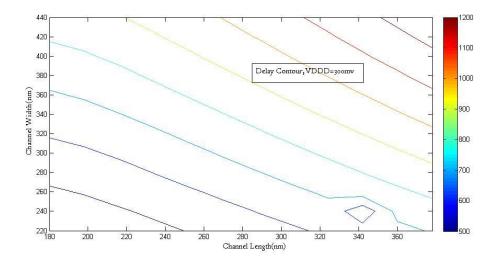

| 5.5 Contour Plot: Impact of device geometry change on delay                                |     |

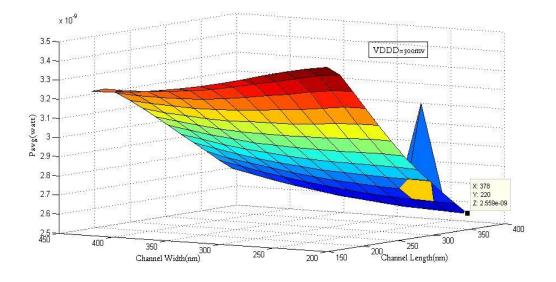

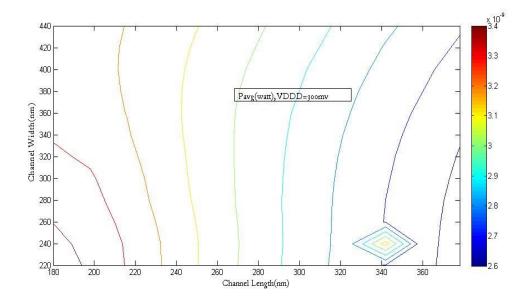

| 5.6 Surface plot: Pavg variation with changing device geometry                             |     |

| 5.7 Contour plot: Pavg variation with changing device geometry                             |     |

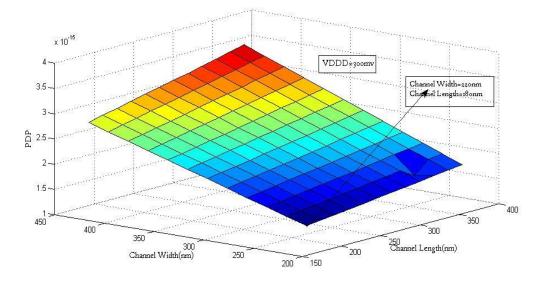

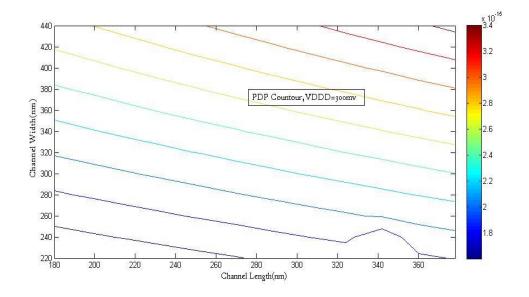

| 5.8 Surface plot: PDP variation with changing geometry                                     |     |

| 5.9 Surface plot: PDP variation with changing geometry                                     |     |

| 6.1 Experiment Setup for calculation of load based device sizing                           |     |

| 6.2 Electrical Effort of INVX1 vs Channel Width                                            | 59  |

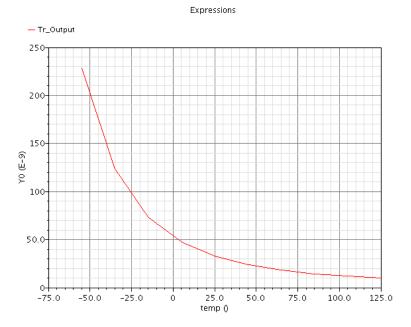

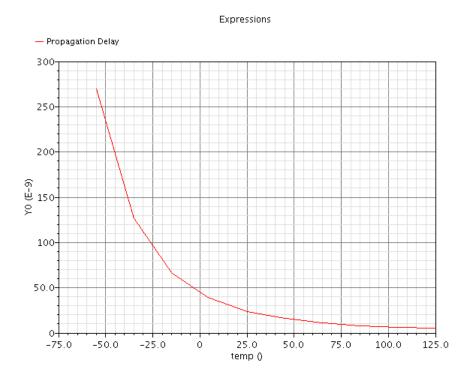

| 6.3 Rise Time vs Temperature (in degree centigrade)                                        | 59  |

| 6.4 Propagation delay vs Temperature(in degree centigrade)                                 | 60  |

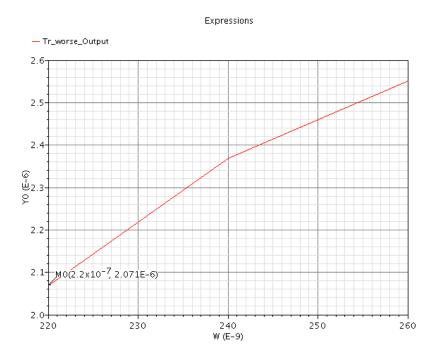

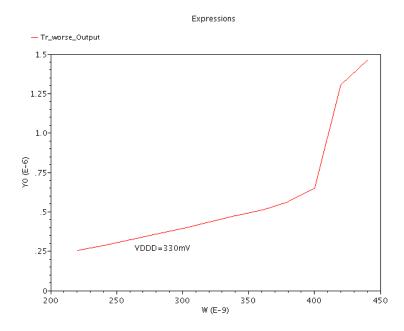

| 6.5 Rise Time vs Channel width, VDDD=270mv, ss corner, T=-55 <sup>0</sup> C                | 61  |

| 6.6 Rise Time vs Channel width for different VDDD= $330$ mV, ss corner, T= $-55^{\circ}$ C | 61  |

| 6.7 Propagation delay vs Channel width at VDDD=330mv.worst case PVT corner.                | .62 |

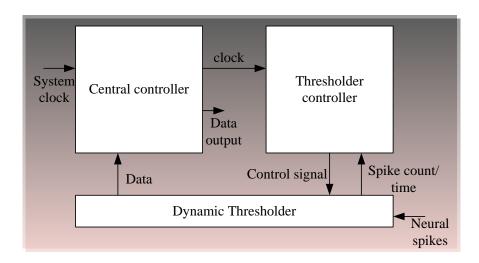

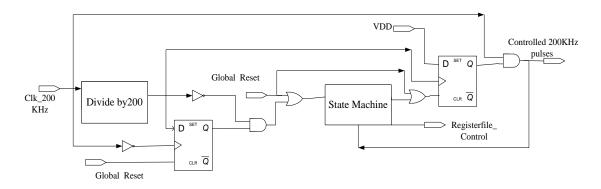

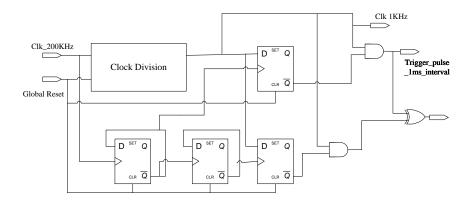

| 7.1 Block diagram of MNI Controller.                                                       |     |

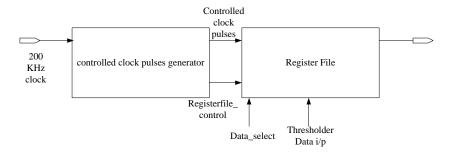

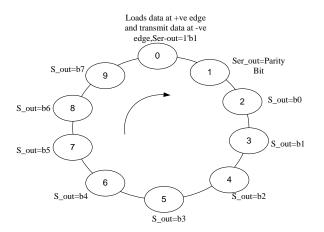

| 7.2 Central controller block diagram                                                       | 64  |

| 7.3 State diagram for central controller                                                   |     |

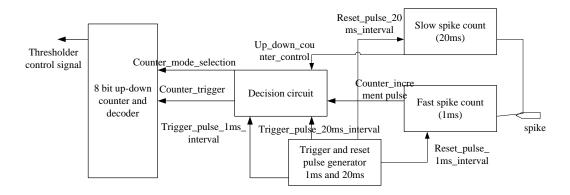

| 7.4 Controlled pulse generator circuit                                                     | 65  |

| 7.5 Thresholder controller block diagram                                                   | 65  |

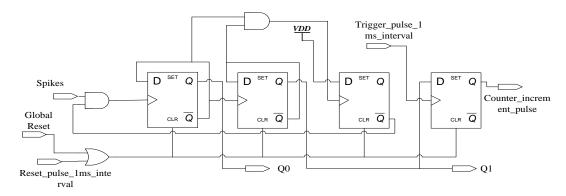

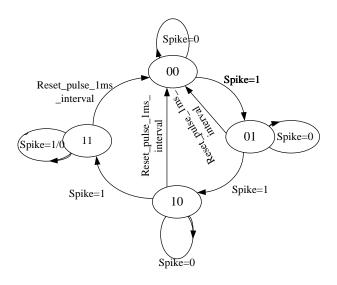

| 7.6 Fast spike detection module                                                            | 65  |

| 7.7 State diagram for fast spike detection module                                          | 66  |

| 7.8 1ms interval Reset and Trigger pulse generator.                                        |     |

| 7.9 RTL simulation for MNI controller.                                                     | 67  |

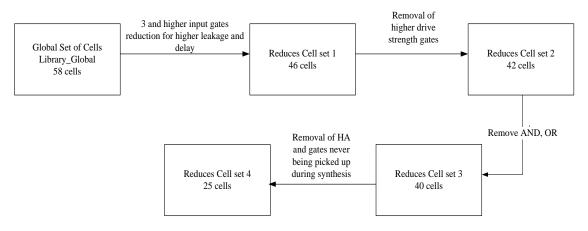

| 8.1 Library reduction flow                                                                 | 69  |

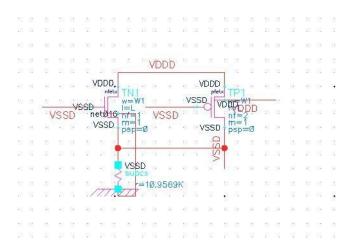

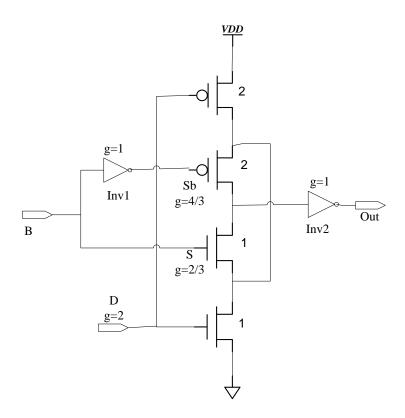

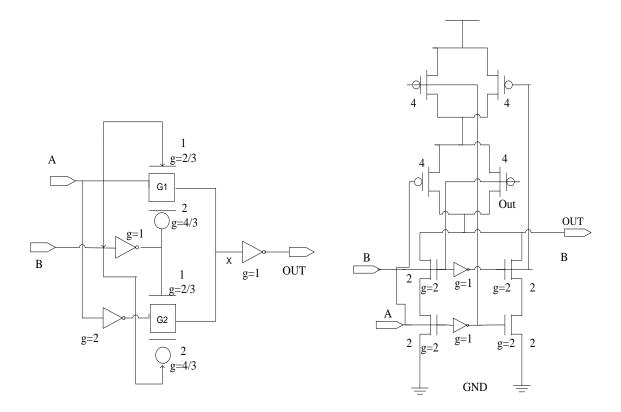

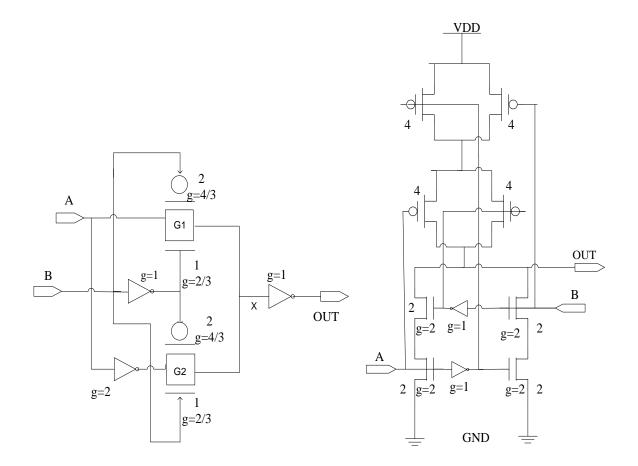

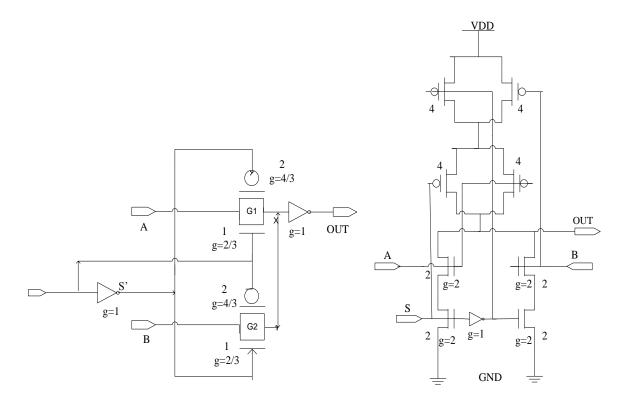

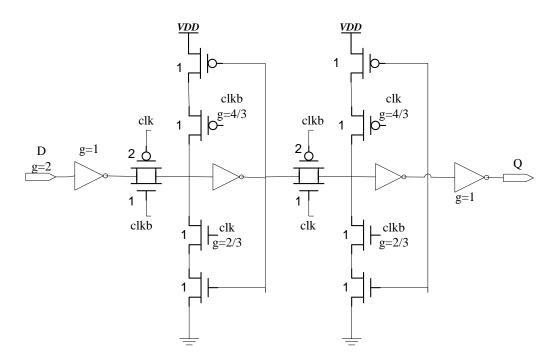

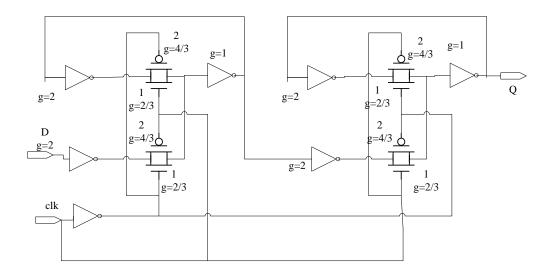

| 9.1 T-Gate NAND2X1                                                                         |     |

| 9.2 INVX1 driving T-Gate                                                                   |     |

| 9.3 NAND2X1 driven by INVX1                                                                |     |

| 9.4 upsized devices and Corresponding Logical Effort                                       |     |

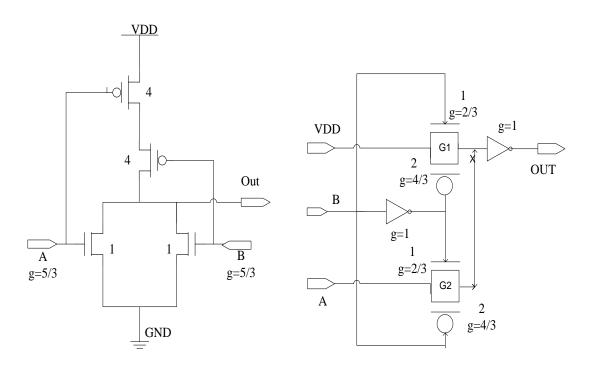

| 9.5 Gate sizing for standard CMOS NAND2X1 (left) and T-Gate NAND2X1 (right                 |     |

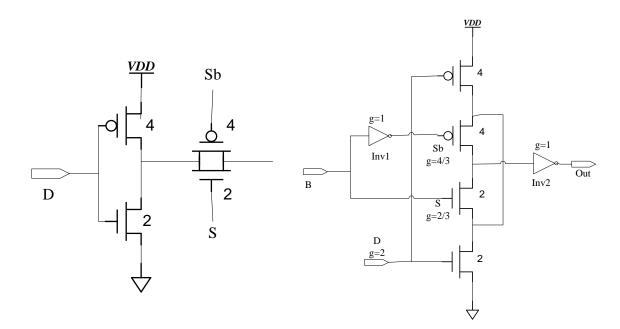

| 9.6 Gate sizing for standard CMOS NOR2X1 (left) and T-Gate NOR2X1 (right)                  |     |

| 9.7 Device sizing for T-Gate XOR2X1 (left) and standard CMOS XOR2X1 (right)                |     |

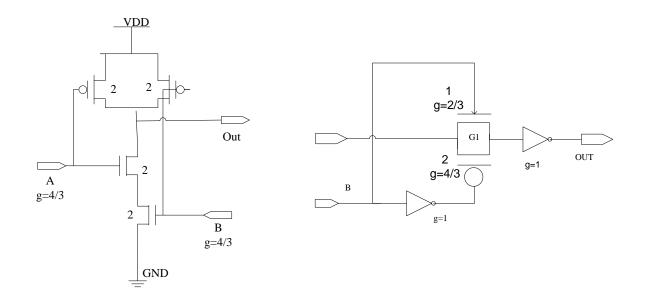

| 9.8 Device sizing for T-Gate XNOR2X1 (left) and standard CMOS XNOR2X1                      | 79  |

| 80 |

|----|

| 81 |

| 81 |

| 82 |

| 83 |

| 83 |

| 84 |

| 84 |

| 85 |

| 87 |

| 88 |

| 89 |

| 89 |

|    |

#### CHAPTER I

#### INTRODUCTION TO SUBTHRESHOLD OPERATION AND APPLICATIONS

#### 1.1 INTRODUCTION

Sub-threshold operation is popular where circuit applications have a tight power budget and computational speed is of lesser interest. The supply voltage is scaled down near or below threshold voltage resulting in reduced energy consumption for both active operations and static or leakage power dominated circuits [26]. Energy constrained applications having lower activity rate and a lower speed requirement [26] often demands longer battery life and can account on wireless power harvesting as a potential alternative. Micro-sensor networks and RFIDs are examples of such applications used for habitat or interment monitoring, i.e. health and structural monitoring and automotive sensing[26]. The extremely low rate of change of information in environment and health monitoring applications accounts for the reduced performance requirements of the circuit as a result\_reduction in power consumption becomes a key factor. The radio frequency identification (RFID) tags and application specific digital signal processor and micro-controlling units for portable devices are other examples of such kind of energy constrained operations. The TI C5xx family of DSPs or the TI MSP430 family **MCUs** has been used for portable measurements successfully. of

#### **1.2 GOVERNING EQUATIONS AND REGION OF OPERATIONS**

The sub-threshold equation[1] of current irrespective of region of operation (saturation or linear) can be expressed as

$$Id = I0.\exp\frac{(VGS - VT)}{nUT}(1 - \exp(\frac{-VDS}{UT}))$$

Where,

$$I0 = \mu 0. Cox \frac{W}{L}(n-1). UT^2$$

n is the sub-threshold slope and given by the equation below  $n = (1 + \frac{Cd}{Cox})$  where, Cd is depletion capacitance and Cox is the oxide capacitance

W and L are channel width and length respectively, VGS and VDS are gate to source and drain to source voltage respectively, UT is the thermal voltage and is approximately 26mV at room temperature. Sub-threshold region of operation could be defined as VGS being less than VT(threshold voltage of the MOSFETs) while VDS(drain to source voltage of the MOSFET) could vary depending on whether the device is operating in linear or saturation region. Theoretically at VDS=(3-5)UT and above, the term  $(1 - \exp(\frac{-VDS}{nT}))$  becomes approximately

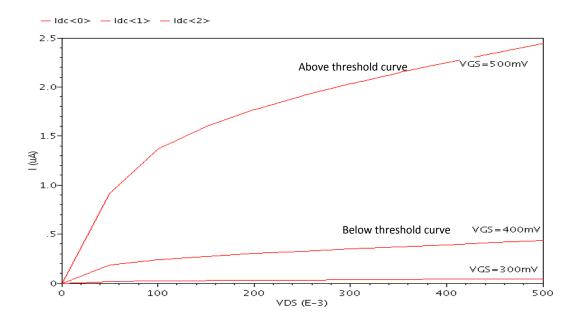

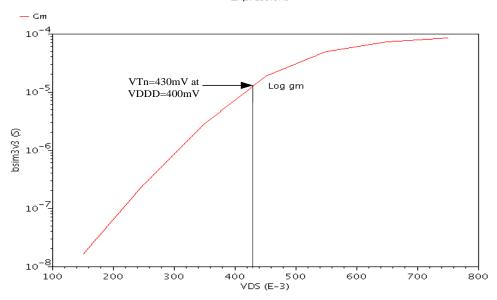

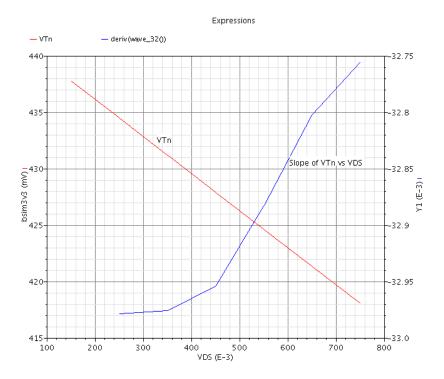

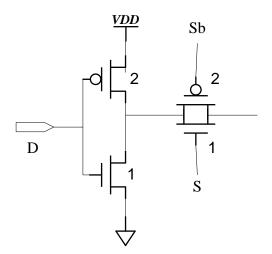

equal to one and the device is called to operate in sub-threshold saturation(sub-threshold linear otherwise). The threshold voltage of a minimum geometry NMOS(W=220nm,L=180nm, NOF=1) in this process is measured to be approximately 430mV (neglecting the effect of DIBL at lower supply voltages. See Figure 1.9). Similar  $I_D$  vs VDS curves can be observed for both for Sub-threshold and super threshold region of operation with the exception that in sub-threshold the current is orders of magnitude less and follows a log-linear behavior with VGS. The  $I_D$  vs VDS curve for sub-threshold and above threshold VGSs are shown in Figure 1.1.

Figure 1.1 Id vs VDS for sub-threshold and above VGSs for NMOS

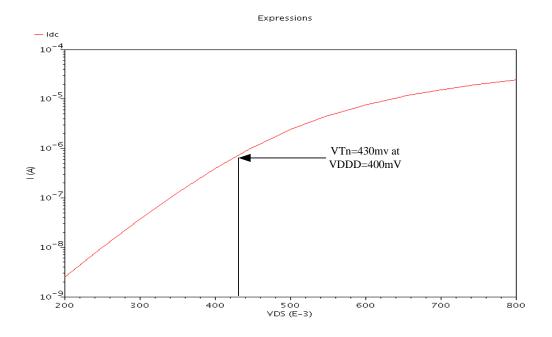

Typical log-linear behavior in sub-threshold may be obtained by tying the gate to drain of the NMOS(minimum geometry) and varying the VGS from 200mV(device being in sub-threshold saturation) to 800mV(device being in velocity saturation).See Figure 1.2.

Figure 1.2 Log-Linear behavior of Id vs VDS, VTn=430mV at VDDD=400mV

| Parameters of Interest          | Sub-Threshold | Moderate Inversion | Strong Inversion |

|---------------------------------|---------------|--------------------|------------------|

| gm Efficiency                   | High          | Moderate           | Low              |

| VDS(Sat)                        | 5xUT          | 130-250mV          | 250mV and Above  |

| Band Width(g <sub>m/Cgg</sub> ) | Low           | Moderate           | High             |

| Noise                           | Low           | Moderate           | High             |

| Self-Gain((g <sub>m/gds</sub> ) | VA/nUT        | 2VA/(VGS-VT)       | VA/(VGS-VT)      |

| Area(WL)                        | High          | Moderate           | Low              |

Table 1.1 Transistor parameters comparison, VTn =430mV at VDDD=400mV

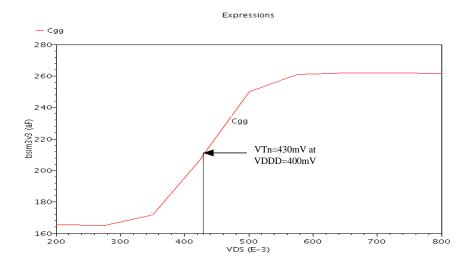

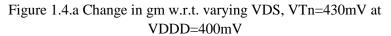

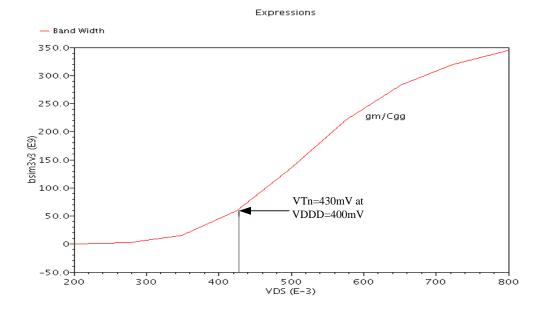

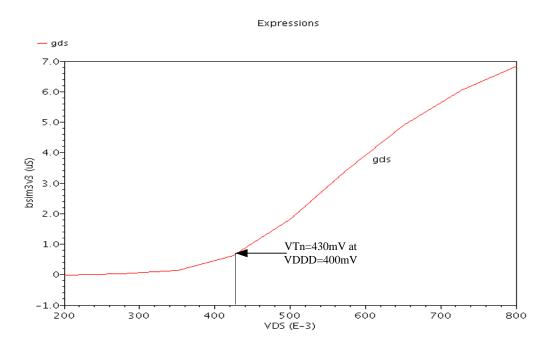

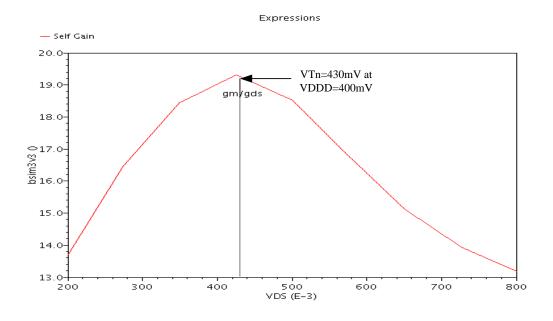

A comparison of the more significant transistor parameters are given in Table 1.1[27]. The change in Cgg, gm and Log(gm) as we move from sub-threshold saturation to velocity saturation is shown in Figure 1.3, Figure 1.4.a, Figure 1.4.b respectively. Both of

Figure 1.3 Change in Cgg w.r.t. varying VDS, VTn=430mV at VDDD=400mV

Expressions

Expressions

Figure 1.4.b Change in Log(gm) w.r.t. varying VDS, VTn=430mV at VDDD=400mV

these parameters increases as we move towards velocity saturation resulting in a net change in band-width i.e. gm/Cgg as shown in Figure 1.5. The change in gds and self-gain i.e. gm/gds has been shown in Figure 1.6 and 1.7 respectively. It is observed that the self-gain first increases but

Figure 1.5 Change in gm/Cgg with increasing VDS, VTn=430mV at VDDD=400mV

Figure 1.6 Change in gds w.r.t. varying VDS, VTn=430mV at VDDD=400mV

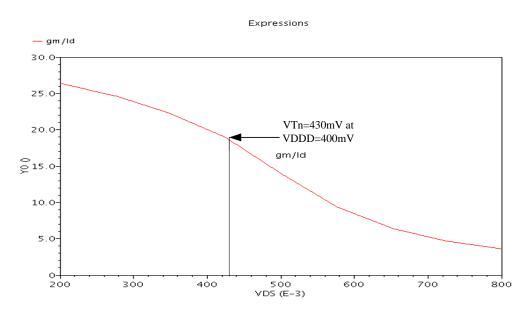

near threshold voltage it reaches its maxima and there after starts falling whereas gds monotonically increases with increasing VDS. The gm efficiency(gm/Id) is shown in Figure 1.8 which is highest in sub-threshold and then falls as VDS increases.

Figure 1.7 gm/gds w.r.t. varying VDS, VTn=430mV at VDDD=400mV

Figure 1.8 gm efficiency (gm/Id) w.r.t. changing VDS, VTn=430mV at VDDD=400mV

Figure 1.9 VTn variation due to DIBL with increasing VDS.

#### 1.3 VTrip OR SWITCHING THRESHOLD POINT OF AN INVERTER

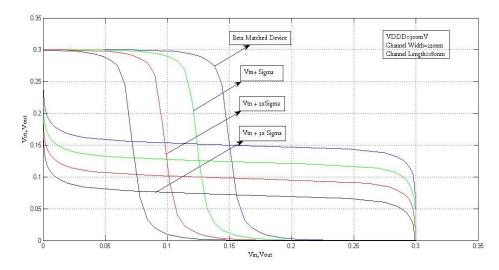

The VTrip point or the switching threshold point of an inverter in velocity saturation can be expressed by the following equation [32]:

$$VTrip = \frac{Gn.VTn + Gp(VDDD - |VTp|)}{Gn + Gp}$$

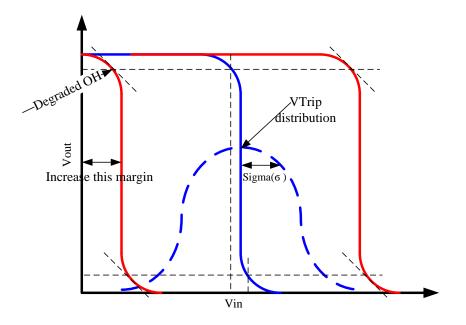

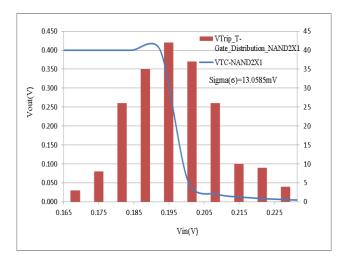

where VTn and VTp are PMOS and NMOS threshold voltages respectively. Gn and Gp are the NMOS and PMOS conductance respectively. MOSFET VT varies due to process variation and mismatch i.e. VTn and VTp are two independent statistical parameters having their own sets of statistical distribution. Consequently VTrip has a statistical distribution associated with it which is dependent on VTp and VTn. Impact of this variation is severe in sub-threshold (i.e. VDDD is scaled down below threshold). For a beta matched inverter (i.e. both NMOS and PMOS carrying same ON current) VTrip equals to VDDD/2. The Voltage Transfer Curve (VTC) of a beta batched inverter is marked in blue in Figure 1.10 with its VTrip distribution. The distribution is considered as a normal distribution i.e. drains current will have a corresponding log normal distribution [1] in sub-threshold. The Sigma(6) of the distribution is also highlighted in the figure. It can be noticed that if the VTC is shifted to the furthest left corner (See Figure 1.10) due to variability the inverter can result in logic failure due to degraded output high(OH) logic level. If the OH of any gate is lower than the input high (IL) logic level requirement of the succeeding gate, it causes logic failure. Similarly on the other side failure may occur because of poor output low (OL) logic level. This failure is a static failure. Even in an ideal and completely noiseless

system this failure may occur as a result of variability. There are two solutions to this particular problem. Either we can increase VDDD to increase margin i.e. shift these entire set of VTC curves along the 'Vin' axis to higher values (i.e. higher Mean( $\mu$ )) or we can increase the device area to narrow down the VTrip distribution ( i.e. reduce Sigma(6)). Probability of failure can be reduced with both of these above mentioned techniques. A detailed discussion on which one is a better option to reduce failure is presented in Chapter III.

Figure 1.10 VTC of a beta matched inverter and the impact of variability.

#### 1.4 PREVIOUS WORK AND MOTIVATION

A detailed discussion on sub-threshold design methodologies could be found in [1] which describes the impact of supply voltage scaling down aiming minimum energy operation. Even though it mentions T-Gate topology as low power architecture the implementation is primarily focused on CMOS logic gates and device sizing for sub-threshold. Tae-Hyoung Kim et al[28] takes into account the impact of reverse short channel effect on device sizing for sub-threshold operation while[29] considers Inverse Narrow Width Effect on sub-threshold device sizing. Ran et al[18] combines this two impacts in moderate inversion device sizing in achieving a robust digital cell library designing for ultra-low power applications. It also explores the impact of varying device sizing in order to manage threshold voltage variation keeping it independent of device geometry to a first order. All of the above work focused on CMOS topology while targeting reduced power consumption. Hence we focus on T-Gate topology to evaluate its merits and demerits as a candidate for low-power architectures and compare with its near VT CMOS logic equivalent to establish its usefulness in sub-threshold.

#### **1.5 THESIS ORGANIZATION**

An introduction to sub-threshold region of operation is presented in Chapter I along with the changes in different concerned MOSFET parameters as we move from sub-threshold to moderate inversion to finally velocity saturation. The capacitance at the input of a logic gate is a factor of concern as higher the input capacitance, the greater is the drive strength requirement to drive that gate. Hence a comparison of normalized input capacitance of T-Gate and CMOS logic gate is summarized in chapter II that shows that T-Gates are having lower normalized total input capacitance. Chapter III deals with prime factor in sub-threshold operation i.e. robustness. The static noise margin is compared between two logic gate topologies under consideration to verify their robustness. The experiments uncover the fact that the CMOS gates are more robust in Subthreshold due to having better noise margin but T-Gate shows better rate of decrease of logic failure with increasing VDDD due to having narrower distribution of switching threshold point( $V_{Trin}$ ) w.r.t. process variation and mismatch. A comparison of  $I_{oFF}$  is presented in Chapter IV between CMOS and T-Gate logic equivalent showing that CMOS should show better I<sub>OFF</sub> performance which is a prime factor for static operation. The device sizing methods to achieve an optimum Power Delay product(PDP) and optimum loading are discussed in Chapter V and Chapter VI which leads to the choice of device finger geometry at specified PVT corner and given specific target system requirement. Target system architecture has been described in Chapter VII to exercise the libraries in this study and a reduced ASIC cell library implementation method has been described in Chapter VIII aiming reduced implementation time and effort. T-Gate based logic gate sizing is described in Chapter IX in details for all concerned gates for the target library whereas the T-Gate library design, implementation, characterization and abstraction flow is described in Chapter X. Finally, the target system is synthesized with the implemented T-Gate library as well as with an existing low power CMOS cell library and the results are compared with each other in Chapter XI. The comparison shows performances at static and dynamic that helps to choose one library over the other one based on requirements and region of operation. Supporting files are provided in appendix A and appendix B.

#### CHAPTER II

#### NORMALIZED INPUT CAPACITANCE COMPARISON

#### 2.1 INTRODUCTION

The normalized input capacitance or Logical effort of any digital logic gate has been designated as the ratio of the total input capacitance to the input capacitance of an inverter that can deliver the same output current [20]. The prerequisites to be eligible for logical effort analysis impose certain restrictions on the designated logic gates as described in [20]. The input of the logic gates has to be connected to the gate of a MOSFET and not to the drain or the source terminal. This makes logical effort analysis more valid for CMOS logic gates. Hence, for T-Gate the more fundamental term will be normalized input capacitance (w.r.t.INVX1) as we are not exactly sure of the drive strength of a T-Gate. Keane et al [21] shows a sub-threshold standard CMOS gate device sizing method that takes into account the DIBL effect and compares the new logical effort with the traditional standard CMOS gate logical effort and reports improvement in performance. Chang et al [22] describes the impact of voltage and temperature variation on delay and proposes a new logical effort formulation that takes into account the above two variation mentioned. Wang et al [23] demonstrates the error incorporated in logical effort calculation due to unequal slope of input and output transition of a gate when a multistage log is tapered to reduce the internal energy and introduces a slope correction model. Morgenshtein et al [24] shows that the delay and effort is dependent on the input combinations of the gate switching due to presence of parasitic intermodal capacitance and varies. A delay analysis using modified logical effort is presented in [25]. However none of the above literature proposes any effective way to calculate the logical effort of a T-gate based logic gate design or compares the logical effort of a T-gate based logic design and a standard cell based logic gate design in order to make firm argument on their performance in terms of delay. The effective computation of logical effort of a T-gate based design can be cumbersome as we deal mostly with the inter nodal parasitic capacitance in a T-Gate for effective input capacitance calculation. Here we propose an simulation based method to calculate the normalized input capacitance of T-Gate based logic gate by simulation and compare the worst case computed effort with the traditional standard CMOS based cell's logical effort(Note Normalized Input capacitance is the logical effort itself in case of CMOS logic). For simplicity we limit our analysis to two input gates.

#### 2.2 EXPERIMENT SETUP

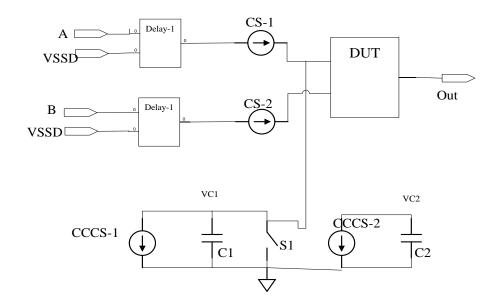

Figure 2.1: Experiment setup for normalized input capacitance calculation

Figure.2.1 shows the experiment setup used for this purpose. DUT represents the Design under test i.e. the two input T-gate logic gates for which we want to calculate the effort. Inclusion of Delay-1 and Delay-2 is optional and does not impact the experiment results. [Cs-1, CCCS-1] and [CS-2,CCCS2] are two current controlled current sources with current gain(k) = -1, used for this setup.C1 and C2 are the capacitors to calculate the input capacitance of port A and B. C1=C2=10fF in this case.

Now, the change in voltage (assuming VC1) across C1 is measured while switching the inputs to cover all possible input combinations and the charge accumulated on C1 is calculated as Q=C1\*( VC1 -0); The input capacitance at port A for any particular combination could be calculated as Cinput-A ,=Q/(VDDD-0) where VDDD is the power supply voltage and 400mv in this case. The input capacitance at port B(i.e. Cinput-B )could be found following a similar methodology. After calculating the worst case capacitance seen looking into both of the input ports it could be normalized w.r.t. the input capacitance of INVX1 to get the normalized input capacitance.

Table 2.1 shows a comparison of normalized input capacitance of T-Gate and CMOS logic gates. Note that the logical effort for the standard CMOS based design [20] does not include the inter nodal parasitic capacitances which will increase the effective Logical Effort.

| Gate<br>Type | Normalized Input capacitance- T-gate Logic |        | Normaliz | Normalized Input Capacitance- CMOS Logic |  |  |

|--------------|--------------------------------------------|--------|----------|------------------------------------------|--|--|

| 51           | Port A                                     | Port B | Port A   | Port B                                   |  |  |

| NAND         | 143.3m                                     | 1.69   | 1.3      | 1.3                                      |  |  |

| NOR          | 134.5m                                     | 2      | 1.6      | 1.6                                      |  |  |

| XOR          | 322.1m                                     | 2.8    | 4        | 4                                        |  |  |

| XNOR         | 231.4m                                     | 2.3    | 4        | 4                                        |  |  |

| MUX          | 993.3m                                     | 254.3m | 2        | 2                                        |  |  |

Table 2.1 Normalized Input capacitance comparison between T-Gate and CMOS

It's notable that the total normalized input capacitance in case of T-gate logic is actually less than that of equivalent CMOS design.

#### 2.3 SIMULATION RESULTS AND DETAILED ANALYSIS

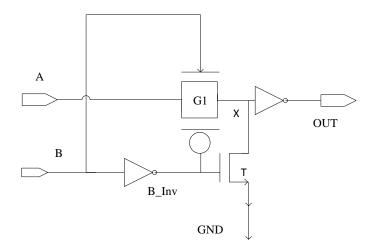

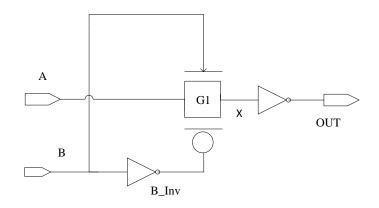

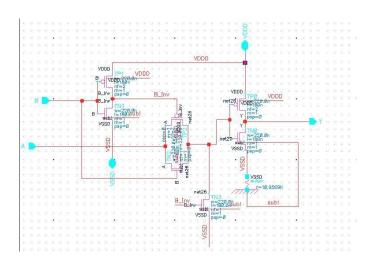

A Transmission gate based NAND2X1 gate is shown in Figure 2.2

Figure 2.2 T-Gate NAND2X1

Operation observation and calculation:

when A=0 and B=1: T-Gate G1 will be selected; B\_Inv=0; Port B drives an 1X inverter and parasitic capacitance as Port A is at 0; Any charge that is stored at node x can flow forward or reverse way.

When A=1,B=0: T-Gate G1 is deselected i.e. off. Port A will drive the parasitic capacitance(as B=0) and will supply the leakage current through G1.B=0 i.e. B\_inv=1 and the NMOS T will be on and pull node x down. The leakage through G1 will find a path to ground through T. From the

simulation, it's verified that at this input combination a lot of leakage current flows through A(waveform IA at A=1,B=0)

When A=1, B=1: T-GateG1 is On. Since A is 1 it will drive the output inverter through G1 and the parasitic cap as B\_Inv=0; Both the NMOS T and the Cgs of output inverter will provide leakage path and Port A will supply all these current

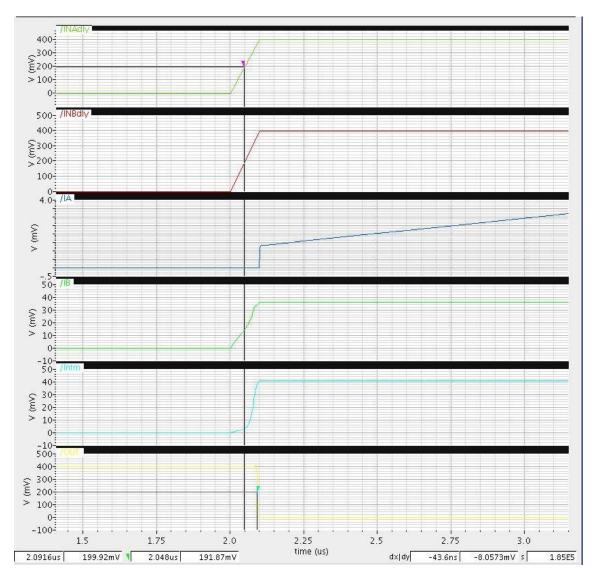

Worst case normalized input capacitance at port A: At A=0, B=1; port A drives the maximum capacitance. Capacitance at the input of A= (Peak voltage(IA)x 10Pf/ (VDD))= 3.39mv x 10Pf/.4 = 87.81a. From the simulation Input capacitance of an INVX1 is Cin\_1X= 612.8a. So normalized input capacitance at port A= 87.81a/612.8a= 0.143

Worst case normalized input capacitance at Port B:When B=1, A=0, Port B drives the maximum capacitance , (One 1X inverter + two parasitic capacitances as A=0 + One NMOS (from G1)).From the simulation, Capacitance at the input of B == (Peak voltage(IB)x 10Pf/ (VDD))=41.45mvx10pf/0.4 =1.036f. Normalized input capacitance at the input of Port B= 1.036f/612.8a=1.69. See Figure 2.3.

|   | Name/Signal/Expr 🔺    | Value  |

|---|-----------------------|--------|

| 1 | CIA                   | 87.81a |

| 2 | CiB                   | 1.036f |

| З | Cin_1X                | 612.8a |

| 4 | Logical_effort_Port_A | 143.3m |

| 5 | Logical_effort_Port_B | 1.691  |

Figure 2.3 Simulation data for T-Gate NAND2X1

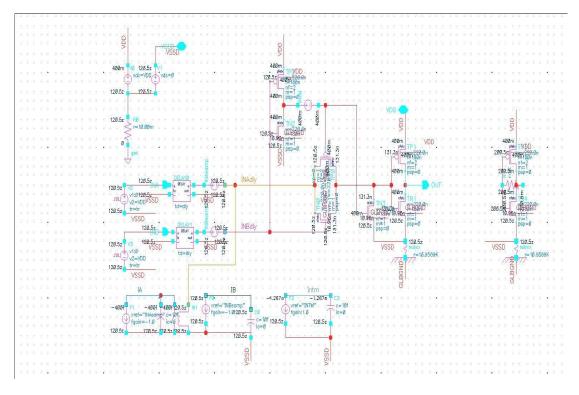

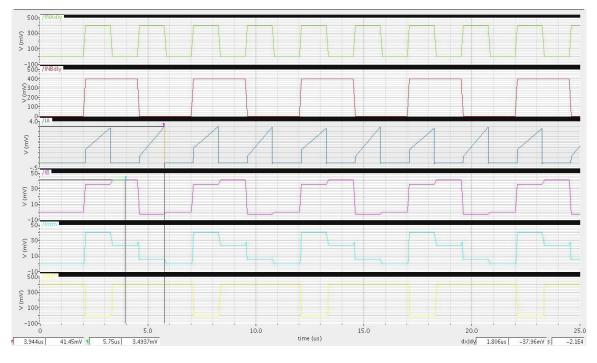

The simulation setup for input capacitance calculation for NAND2X1 is shown in Figure 2.4. Figure 2.5 shows the simulated waveforms for the same. The propagation delay is shown in Figure 2.6 and measured to be 43ns. The input capacitance for the additional logic gates are calculated similarly and are given in Table 2.1. The propagation delays for VDDD equal 400mV(tt corner and room temperature) as measured for the concerned logic gates are summarized in Table 2.2 below.

| ruble 2.2 riopuguton Denay for unreferrit r Suite fogle gutes |                        |  |  |  |  |

|---------------------------------------------------------------|------------------------|--|--|--|--|

| T-Gate Type                                                   | Propagation Delay (ns) |  |  |  |  |

| NAND2X1                                                       | 43                     |  |  |  |  |

| NOR2X1                                                        | 39                     |  |  |  |  |

|                                                               |                        |  |  |  |  |

| XOR2X1                                                        | 35                     |  |  |  |  |

| XNOR2X1                                                       | 32                     |  |  |  |  |

| MUX2X1                                                        | 32                     |  |  |  |  |

Table 2.2 Propagation Delay for different T-Gate logic gates

Figure 2.4 Experiment setup for input capacitance calculation of NAND2X1

Figure 2.5 Simulation waveform for NAND2X1

Figure 2.6 Propagation delay measurement for NAND2X1

#### 2.4 CHAPTER SUMMERY

It is notable from Table 2.1 that the total normalized input capacitance for the T-Gates are less than their corresponding CMOS counterpart. But it does not conclude that the T-Gate cells are having lower logical effort and faster. The CMOS gates, in this case are CONVENTIONALLY sized to produce 1X output drive. That is why, when their input capacitance is normalized w.r.t. to the input capacitance of a INVX1 it shows us the corresponding logical effort in case of CMOS cells. On the contrary, the T-Gates contains two stages with an INVX1 as their output stage and T-Gate network as first stage. Dividing the input capacitance of the T-Gate w.r.t. the total input capacitance of an INVX1 does not produce the logical effort as the output drive strength of the T-Gate here depends on the driving gate along with the T-Gate sizing. The logical effort of a T-Gate can be derived in a different manner and discussed in details in Chapter IX.

#### CHAPTER III

#### COMPARISON OF SNM AND FAILURE RATE

#### **3.1 INTRODUCTION**

Variability is one of the prime concerns as supply voltage scales below 1V and to a much greater extent as VDDD scales near the MOSFET threshold voltage (VT) Circuits operating in moderate inversion or sub-threshold aim to achieve the lower power consumption. Variability in transistor parameters e.g. Threshold voltage (VT) exist irrespective of region of operation but the impact is more severe in sub-threshold as  $I_{ON}$  is comparable to  $I_{OFF}$ . Due to exponential dependency of current on threshold voltage, minor change in threshold voltage can cause major change in  $I_{ON}$ . The current in sub-threshold is given by the following equation below

$$Id = I0.\exp\frac{(VGS - VT)}{nUT}(1 - \exp(\frac{-VDS}{UT}))$$

Where,

$$I0 = \mu 0. Cox \frac{W}{L}(n-1). UT^2$$

\_n is the sub-threshold slope and given by the equation below  $n = (1 + \frac{Cd}{Cox})$  where, Cd is depletion capacitance and Cox is the oxide capacitance.

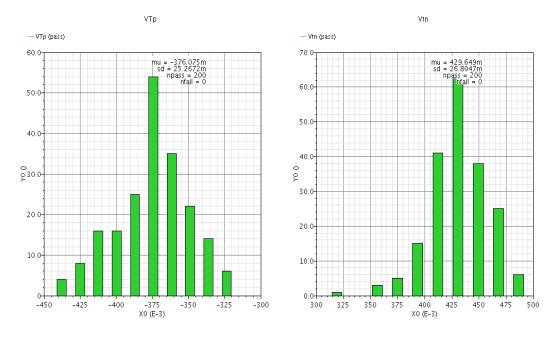

Threshold Voltage(VT) distribution of minimum geometry transistor for the CMOS 180nm process under investigation has been shown in Figure 3.1 as obtained by 200 point Monte Carlo simulation taking both process variation and mismatch into account. The matching properties of MOS transistors and threshold voltage model for MOSFETs are demonstrated in [10] and [11] respectively. This initiates the need for further investigation of digital logic gates and their topologies to fit ultra-low power applications. Static Noise Margin is one of the standard methodologies followed in order to quantify and measure rate of failure in standard cell design[1]. Several authors proposed variability aware device sizing and cell library design techniques for sub-threshold\_operation. Kwong et al [1], [2] considers the skewed P/N process corners (i.e. strong NMOS and week PMOS or the vice versa) as in both case either the circuit

can't drive the output to logic high or logic low to full output swing properly given a clock rate and if the output high (OH) or output low (OL) of one stage is below the trip point (V<sub>Trip</sub>) of the successive gate, logic failure may occur. The above stated impact is most prominent when an NAND is driving a NOR or vice versa. The NAND is having degraded output low (OL) as a result of the stronger pull up network (parallel PMOS) and consequently the worst case input high (IH) requirement. Whereas the NOR shows poor output high(OH) as a result of the stronger pull down network (parallel NMOS) and hereby the worst case input low (IL) requirement. The failure rate of INVX1, NAND2X1 and NOR2X1 w.r.t. upsized device width and VDDD is evaluated in [1] and [2], defining failure as closing of either of the lobes of the butterfly. The failure is measured by the help of 5k point Monte Carlo simulation. Increasing device geometry reduces the Standard Deviation (SD) of the distribution of threshold voltage variation via a large gate area sampling. A narrower distribution indicates reduced variability but not necessarily an improved SNM. An asymmetrical butterfly results in a higher failure as the smaller lobe indicates a higher probability of closing under worst PVT consideration [8]. Formulation for measuring the SNM for above threshold SRAM cells are provided by [3]. A clearer way of analytical measurement of the SNM and butterfly plot is demonstrated in [12]. Dasdan et al [4] focuses on variability aware cell library design on the basis of Statistical Timing Analysis (SSTA) requirements. Liu et al[5] discuss the implementation of fuzzy logic controller for controlling body bias of the transistors while operating in sub-threshold and hereby achieve better energy savings and performance optimization. Gemmeke et al [6] considers INWE and RSCE into account while sizing the devices. Lohstroh et al [7] shows the flip flop approach of measuring the worst case SNM- is equivalent to an infinitely long chain w.r.t. worst case SNM and gives a mathematical equivalence of four different ways of calculation of SNM. Calhoun et al [9] analyzes SNM of SRAM dependencies on sizing, VDDD, temperature and local and global threshold variation and also gives a mathematical model for sub-threshold SNM.

Figure 3.1: Threshold Voltage(VT) distribution for NMOS(right) and PMOS(left)

#### **3.2 OBJECTIVE**

The focus of the following experiment and analysis is to derive an optimum SNM given a particular VDDD where we define optimum SNM to be the gate, having equal noise margins on both lobes of the butterfly plot in order to avoid a higher probability of failure for either of the output logic state under worse case PVT considerations [8]. A NAND2X1 driving a NOR2X1 and vice versa is considered as the worst case circuit under test [1] and 3 input NAND/NOR are disallowed. Different device sizing methodology for the test circuit is explored to obtain the best case SNM and the impact of increasing VDDD and device geometry is analyzed aiming reduction in logic failure rate. Considering the fact that increasing VDDD essentially shifts the V<sub>Trip</sub> Mean ( $\mu$ ) of V<sub>Trip</sub> distribution of the logic gates to higher values with minimal or insignificant change in Sigma(6) of the trip point distribution. Analysis has been done for both CMOS topology and T-Gate based design and their SNM is compared as a measure of robustness. Finally the optimum operating frequency for each of the topologies has been derived by simulating a seven-stage NAND-NOR ring oscillator as VDDD\_is varied from 300mV to 400mV with a step of 20mV.

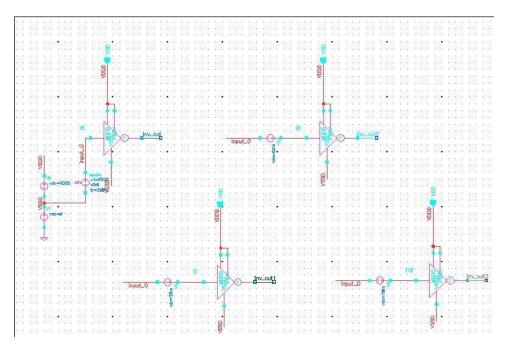

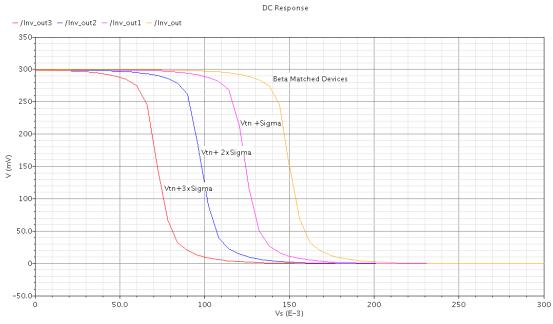

#### 3.3 EXPERIMENT SETUP AND PROCEDURE

The trip point ( $V_{Trip}$ ) of a beta matched inverter at VDDD=300mV is measured. This is as expected to be set at or near VDDD/2. In a skewed P/N process corner the NMOS is typically going to be stronger w.r.t. the PMOS or vice versa. As a result, the trip point is going to move up or down from its ideal balanced state (VDDD/2) resulting in an asymmetric butterfly. Considering process variation and mismatch, the VTn may vary by 1,2 or 3 Sigma(6) etc. where sigma is shown in Figure 3.1. This is modeled as shown by the arrangement in Figure 3.2. The DC sources are set to 0,1,2,3 Sigma voltage values to represent variation of NMOS threshold voltage, where the sigma is obtained by a 200 point Monte Carlo simulation taking process variation and mismatch into account. The VTC curves for each as these cases is obtained by an input dc sweep and are shown in Figure 3.3. It is observed that as the threshold voltage reduces, the inverter is no longer beta matched and the VTC curve shifts towards left which impacts the butterfly causing an asymmetric SNM . The butterfly plots for each of these cases are shown in Figure 3.4.

Figure 3.2 Experiment setup for butterfly plot with varying Sigma VTn

Figure 3.3 VTC curves with changing Sigma VTn

Figure 3.4 Butterfly plot and SNM change with varying VTn

From Figure 3.4 we see that beta matched gates result in an optimum SNM as shown by the symmetric butterfly plots as per our definition and with increasing Sigma(6) VTn, the bottom lobe in the butterfly is becoming smaller resulting in lower SNM for output logic low. The opposite effect is observed as VTp of the PMOS is varied. Beta matched logic results in a symmetric butterfly plot and an optimum SNM for both out logic states with an equal probability of failure of both SNM.

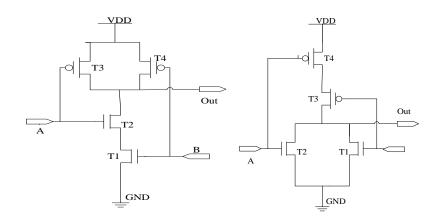

As stated in [1], a chain of NAND and NOR driving each other is consider to be the worst case in terms of SNM. We now seek to optimize noise margins following our definition by focusing on device sizing for the NAND2X1 and NOR2X1 gates. The two parallel NMOSs (T1, T2, Figure 3.5) in NOR2X1 and the two parallel PMOSs (T3,T4, Figure 3.5) degrades the output logic high OH) and low(OL) respectively. This is the main cause of degraded SNM in case of NAND2X1 and NOR2X1 and them driving each other.

Figure 3.5 CMOS NAND2X1 (left) and NOR2X1 (right)

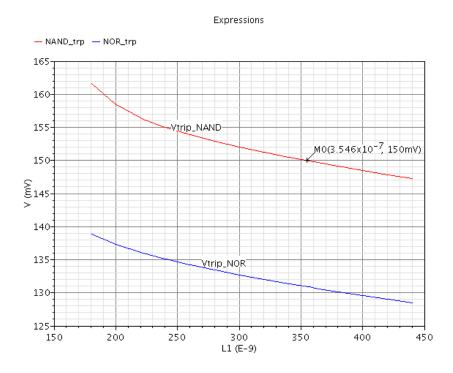

Threshold voltage (VTn and VTp) variation with device geometry in the process under consideration is shown in Figure 3.6.

Figure 3.6 VTn (top) and VTp(bottom) variation w.r.t. device geometry

Figure 3.6 shows that both the threshold voltages (VTn and VTp) increases with increasing device width for any given channel length. On the contrary, both VTn and VTp decreases with increasing channel length for any given device width of choice. This property is exploited in order to derive a symmetric SNM for the logic circuit under test. The following two possibilities are considered.

- a) If we increase PMOS finger width in NAND2X1 and NMOS finger width in NOR2X1, the I<sub>OFF</sub> will reduce due to increase in threshold voltage which might improve SNM and hence balance the trip point at VDDD/2 resulting in symmetric butterfly.

- b) If we increase channel length of NMOS of NAND and PMOS of NOR, Ion will increase due to the resulting reduction in threshold voltage and will improve SNM by more closely balancing the  $V_{Trip}$  at mid-rail resulting in more symmetric butterfly.

We employ the above methodology to verify improvement in SNM. The results are shown in Table 3.1.The 1st 5 data correspond to method (a) stated above and the last 5 data correspond to method (b). In both cases the trip point( $V_{Trip}$ ) distribution of NAND2X1 and NOR2X1 connected as inverter has been measured with their input and output sorted together , along with mean and Sigma of distribution by 200point Monte Carlo simulation(with process variation and mismatch

into account). It is observable that we don't get any significant improvement in trip point in NAND2X1 with increasing device width but the NOR2X1 shows improvement in trip point( $V_{Trip}$ ) which is close to VDDD/2 at a NMOS finger width=440nm at VDDD=300mV.

| Width<br>(nm)    | Length<br>(nm)   | Vtrip_NAND<br>(mV) | Mean_Vtrip_<br>NAND (mV) | Sigma_Vtrip<br>_NAND<br>(mV) | Vtrip_NOR<br>(mV)  | Mean_Vtrip<br>_NOR (mV) | Sigma_Vt<br>rip_NOR<br>(mV) |

|------------------|------------------|--------------------|--------------------------|------------------------------|--------------------|-------------------------|-----------------------------|

| 220              | <mark>180</mark> | 161.7              | 162.2                    | 14.66                        | <mark>138.9</mark> | 137.8                   | 14.06                       |

| <mark>280</mark> | <mark>180</mark> | <mark>161.7</mark> | 161.9                    | 14.29                        | 142.8              | 142.1                   | <mark>13.56</mark>          |

| <mark>340</mark> | <mark>180</mark> | <mark>162</mark>   | 162.2                    | 14.09                        | <mark>145.9</mark> | 145.4                   | 13.3                        |

| <mark>400</mark> | <mark>180</mark> | 162.5              | <mark>162.6</mark>       | 13.95                        | <mark>148.1</mark> | 147.7                   | <mark>13.16</mark>          |

| <mark>440</mark> | 180              | 162.9              | <mark>163</mark>         | 13.87                        | <mark>149.1</mark> | 148.8                   | 13.09                       |

| 220              | 216              | 156.8              | 156.6                    | 15.48                        | 136.4              | 135.4                   | 13.78                       |

| 220              | 252              | 154.3              | 153.9                    | 15.81                        | 134.6              | 133.6                   | 13.65                       |

| 220              | 288              | 152.6              | 152                      | 15.94                        | 133.2              | 132.2                   | 13.57                       |

| 220              | 324              | 151.1              | 150.5                    | 15.98                        | 131.9              | 131                     | 13.51                       |

| 220              | 360              | 149.8              | 149.1                    | 15.99                        | 130.8              | 129.8                   | 13.48                       |

Table 3.1  $V_{Trip}$  of NAND2x and NOR2X1 vs Increasing Width(top 5) and Length(bottom 5)

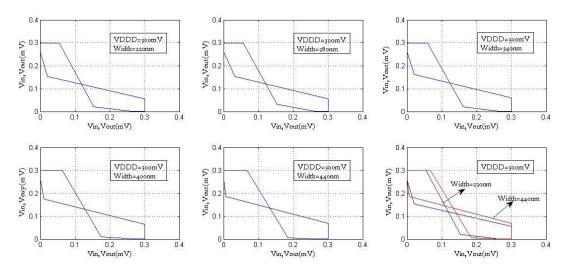

On the other hand increasing channel length shows improvement in NAND trip point at L=360nm but degradation in NOR trip point with increasing channel length. However none of this shows a drastic improvement in Sigma( $\sigma$ ) of trip point(V<sub>Trip</sub>) distribution as sigma varies proportional to 1/SQRT(WL). The butterfly plots against both (a) and (b) has been shown in Figure 3.7 and Figure 3.8 respectively.

Figure 3.7 Butterfly plots w.r.t. increasing Width (method a, top 5 data in Table 3.1)

Figure 3.8: Butterfly plot w.r.t. increasing Channel length (method b, Bottom 5 data in Table 3.1)

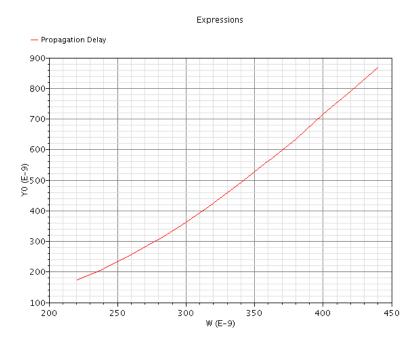

The change in trip point\_ $(V_{Trip})$  of NAND2X1 and NOR2X1 w.r.t. changing Channel Length are shown in Figure 3.9 and change in trip point\_ $(V_{Trip})$  of NOR2X1 w.r.t. channel width is shown in Figure 3.10 respectively.

Figure 3.9: Change in  $V_{Trip}$  with increasing Channel Length (nm) for NAND2X1-NMOS, NOR2X1-PMOS(VDDD=300mV)

Expressions

Figure 3.10: Change in NOR2X1  $V_{Trip}$  w.r.t. increasing NMOS device width(nm)

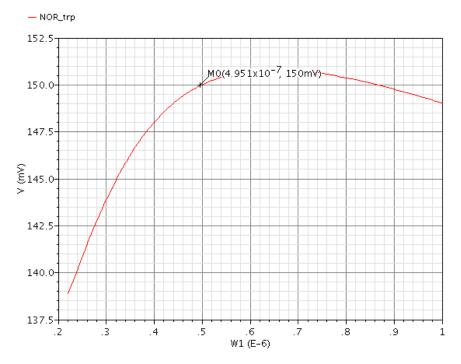

Based on Table 3.1, Figure 3.9 and Figure 3.10, I propose an optimum device (finger) sizing for CMOS NAND2X1 and NOR2X1 for best case SNM and symmetric butterfly shown in Table 3.2 and Table 3.3 respectively.

Table 3.2 Proposed Device sizing for CMOS NAND2X1

| NAND_NMOS_ | NAND_NMOS_ | NAND_NMOS_ | NAND_PMOS_ | NAND_PMOS_ | NAND_PMOS_ |

|------------|------------|------------|------------|------------|------------|

| Width      | Length     | NOF        | Width      | Width      | NOF        |

| 220        | 355        | 2          | 220        | 180        | 2          |

Table 3.3 Proposed Device sizing for CMOS NOR2X1

| NOR_NMOS_ | NOR_NMOS_ | NOR_NMOS_ | NOR_PMOS_ | NOR_PMOS_ | NOR_PMOS_ |

|-----------|-----------|-----------|-----------|-----------|-----------|

| Width     | Length    | NOF       | Width     | Length    | NOF       |

| 495       | 180       | 1         | 220       | 180       |           |

However there are two more possibilities of optimization of SNM. We can add a few extra fingers to the NMOS of NAND2X1 and PMOS of NOR2X1 and that will attempt to balance the trip point at the mid-rail and consequently result in symmetric butterfly and equal SNMs-. The change in trip point of NAND2X1 and NOR2X1 along with the Sigma\_(6) and Mean\_( $\mu$ ) of trip point\_(V<sub>Trip</sub>) distribution has been shown in Table 3.4 and table 3.5 respectively.

Table 3.4 Change in  $V_{Trip}$  of NAND2X1 with increasing NMOS no of fingers

| NAND_NMOS_<br>Width(nm) | NAND_NMOS_<br>Length(nm) | NOF_NMOS | Vtrip_NAND_(nm) | Mean_Vtrip_(mV) | Sigma_Vtrip<br>(mV) |

|-------------------------|--------------------------|----------|-----------------|-----------------|---------------------|

| 220                     | 180                      | 2        | 161.7           | 162.2           | 14.66               |

| 220                     | 180                      | 3        | 154.4           | 154.7           | 14.55               |

| 220                     | 180                      | 4        | 149.3           | 149.6           | 14.49               |

| 220                     | 180                      | 5        | 145.4           | 145.6           | 14.45               |

It can be seen from Table 3.4 and Table 3.5 that the trip point\_ $(V_{Trip})$  of NAND2X1 is closed to VDDD/2 when NOF\_NMOS is 4. The trip point\_ $(V_{Trip})$  of NOR2X1 shows similar behavior at PMOS NOF=7. Also reducing the PMOS NOF in NAND to NOF=1(instead of NOF=2) will balance the trip point to VDDD/2 as shown in Table 3.6.

| NOR_PMOS_<br>Width(nm) | NOR_PMOS_<br>Length(nm) | NOF_PMOS | Vtrip_NOR_(nm) | Mean_Vtrip_(mV) | Sigma_Vtrip<br>(mV) |

|------------------------|-------------------------|----------|----------------|-----------------|---------------------|

| 220                    | 180                     | 4        | 138.9          | 137.8           | 14.06               |

| 220                    | 180                     | 5        | 142.6          | 141.6           | 13.88               |

| 220                    | 180                     | 6        | 145.7          | 144.7           | 13.75               |

| 220                    | 180                     | 7        | 148.2          | 147.3           | 13.66               |

Table 3.5 Change is  $V_{Trip}$  of NOR2X1 with increasing no of PMOS fingers.

Table 3.6 NAND2X1 V<sub>Trip</sub> with NOF PMOS=1

| NAND_NMO | NAND_NMOS | NAND_NMOS | NAND_PMOS | NAND_PMOS | NAND_PMOS | Vtrip_NAN |

|----------|-----------|-----------|-----------|-----------|-----------|-----------|

| S_Width  | _Length   | _NOF      | _Width    | _Length   | _NOF      | D_(mV)    |

| 220      | 180       | 2         | 220       | 180       | 1         | 150       |

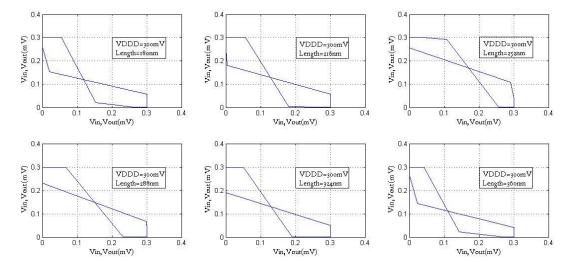

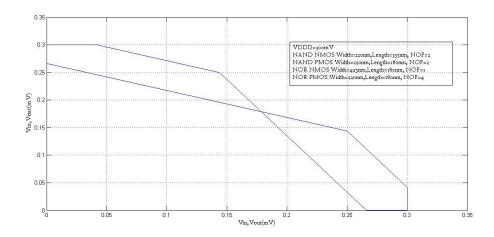

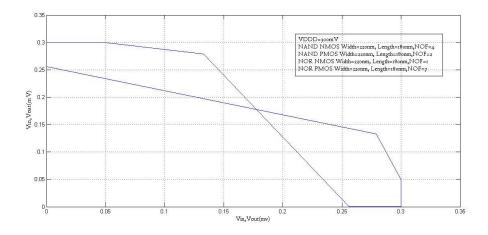

Based on this analysis we have four overall different combinations of device and figure sizing for NAND2X1 and NOR2X1 that gives close to VDDD/2 Vtrip. This is shown in Table 3.7. We need to choose the best case combination out of this. To do so, we plot the butterfly for each of this combination considering a NAND2X1 is driving a NOR2X1 and vice versa. The butterfly plots are shown in Figure 3.11, 3.12.a, 3.12.b, 3.13 respectively corresponding to each combination of NAND2X1 and NOR2X1 in Table 3.8.

Table 3.8 Device sizing for NAND2X1 and NOR2X1 resulting close to mid-rail V<sub>Trip</sub>

| NA  | NAN   | NAN  | NAN   | NAN   | NAN  | NOR   | NOR   | NOR  | NOR   | NOR   | NOR  |       |      |

|-----|-------|------|-------|-------|------|-------|-------|------|-------|-------|------|-------|------|

|     |       |      |       |       |      |       |       |      |       |       |      |       |      |

| ND  | D_N   | D_N  | D_P   | D_P   | D_P  | _NM   | _NM   | _NM  | _PM   | _PM   | _PM  |       |      |

| _N  | MOS   | MOS  | MOS   | MOS   | MOS  | OS_   | OS_L  | OS_N | OS_   | OS_L  | OS_N |       | Vtri |

| MO  | _Leng | _NOF | _Widt | _Leng | _NOF | Width | ength | OF   | Width | ength | OF   | Vtrip | p_N  |

| S_  | th    |      | h     | th    |      |       |       |      |       |       |      | _NA   | OR   |

| Wid |       |      |       |       |      |       |       |      |       |       |      | ND    | (mV  |

| th  |       |      |       |       |      |       |       |      |       |       |      | (mV)  | )    |

|     |       |      |       |       |      |       |       |      |       |       |      |       |      |

| 220 | 355   | 2    | 220   | 180   | 2    | 495   | 180   | 1    | 220   | 180   | 4    | 149.8 | 150  |

|     |       |      |       |       |      |       |       |      |       |       |      |       |      |

| 220 | 180   | 4    | 220   | 180   | 2    | 220   | 180   | 1    | 220   | 180   | 7    |       | 148. |

|     |       |      |       |       |      |       |       |      |       |       |      | 149.3 | 2    |

|     |       |      |       |       |      |       |       |      |       |       |      |       |      |

| 220 | 180   | 2    | 220   | 180   | 1    | 495   | 180   | 1    | 220   | 180   | 4    | 150   | 150  |

|     |       |      |       |       |      |       |       |      |       |       |      |       |      |

| 220 | 180   | 2    | 220   | 180   | 1    | 220   | 180   | 1    | 220   | 180   | 7    |       | 148. |

|     |       |      |       |       |      |       |       |      |       |       |      | 150   | 2    |

|     |       |      |       |       |      |       |       |      |       |       |      |       |      |

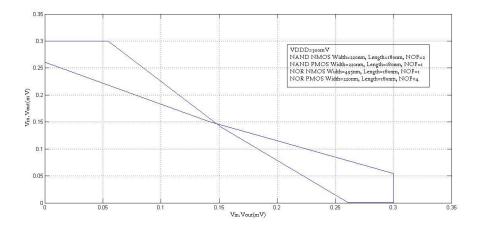

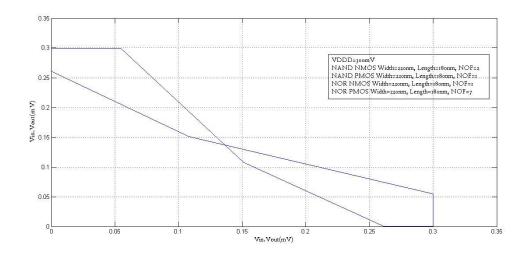

Figure 3.11: Butterfly for 1st combination in Table 3.8

Figure 3.12.a: Butterfly for 2nd combination in Table 3.8

Figure 3.12.b: Butterfly for 3rd combination in Table 3.8

Figure 3.13: Butterfly for 4th combination in Table 3.8

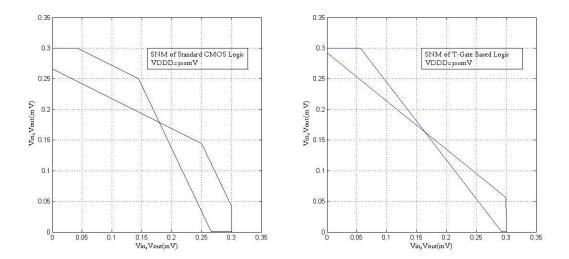

From Figure 3.11, 3.12, 3.13, 3.14 it is clear that the 3rd and 4th combination does not produce enough SNM even though all of them have close to mid-rail  $V_{Trip}$ . So we discard them. Whereas, the 1st two combinations in Table 3.8 produces almost comparable SNM. Now we make a best case choice between 1st and 2nd combinations of Table 3.8. In addition we consider the power delay product(PDP) as the determining or most significant factor. To achieve this we measure the delay, Integrated Current and average current over a cycle[1], Pavg and PDP all at VDDD=300mv using a 7 stage NAND-NOR(configured as an inverter) chain. The results are displayed in Table 3.9 in sequential order for combination 1 and 2 of Table 3.8. This show that the best case NAND2X1 and NOR2X1 will be given by 1st device sizing method of Table 3.8. This is the optimum SNM we achieve by device resizing at a particular VDDD. Beyond this, in order to reduce logic failure or to increase frequency of operation, we must increase VDDD. Increasing VDDD shifts the distribution and the Mean of Vtrip to a higher value. From Table 3.9 the 1<sup>st</sup> combination geometry combination of Table 3.8 turns out to be the best solution at the VDDD under consideration.

| Delay(ns) | Integrated<br>current(fA) | Avg_current(A) | VDD(mV) | Pavg(watt)  | PDP(J)     |

|-----------|---------------------------|----------------|---------|-------------|------------|

| 223       | 5.555                     | 2.49103E-08    | 300     | 7.47309E-09 | 1.6665E-15 |

| 196       | 6.879                     | 3.50969E-08    | 300     | 1.05291E-08 | 2.0637E-15 |

Table 3.9 PDP measurements corresponding to 1<sup>st</sup> and 2<sup>nd</sup> combinations in Table 3.8

### 3.4 FAILURE AND REDUCTION IN FAILURE BY INCREASING VDDD

In digital logic, devices should operate in saturation when in the act of switching in order to retain maximum current and limited gain and band width. In sub-threshold (and weak inversion), when VDS is equal to 3-5 UT i.e. 75-125 mV, the device is considered to be in saturation. To be a little conservative we consider that the devices should at least maintain 125mV(5.UT) of VDS across

them. Hence for an INVX1, we define failure as downward shift of the trip point ( $V_{Trip}$ ) below 125mV and upwards shift beyond (VDDD-125)mV= 175 mV for VDDD=300mV. When considering the trip points for the NAND2X1 and NOR2X1, they are essentially connected as inverters if the inputs are shorted together. Hence, the same analogy could be extended for NAND2X1 and NOR2X1 gates. The failure has been measured by a 200 point Monte Carlo simulation (with process variation and mismatch) for increasing VDDD while\_measuring the samples falling outside the acceptable lower limit (125mV) and upper limit (VDDD-125mV). The results are displayed in Table 3.10, 3.11, 3.12 respectively for INVX1, NAND2X1 and NOR2X1.

| VDDD | Vtrip_Lower<br>Bound (mV) | Vtrip_Upper<br>Bound (mV) | Vtrip_Inverter<br>(mV) | Vtrip_Inverter_ | Vtrip_Inverter_ | No of<br>inverter | Inverter_        |

|------|---------------------------|---------------------------|------------------------|-----------------|-----------------|-------------------|------------------|

| (mV) | Dound (mv)                | Bound (mv)                | (111)                  | Mean (mV)       | Sigma (mV)      | out of<br>range   | Faliure<br>Rate% |

| 300  | 125                       | 175                       | 150                    | 150.1           | 15.674          | 33                | 16.5             |

| 320  | 125                       | 195                       | 160.1                  | 160.224         | 15.7047         | 11                | 5.5              |

| 340  | 125                       | 215                       | 170.2                  | 170.367         | 15.7314         | 6                 | 3                |

| 360  | 125                       | 235                       | 180.3                  | 180.465         | 15.755          | 0                 | 0                |

Table 3.10 Failure Rate for INVX1 vs increasing VDDD(200pt MC simulation)

Table 3.11 Failure Rate for NAND2X1 vs increasing VDDD(200pt MC simulation)

| VDDD( | Vtrip_Lo | Vtrip_Uppe |           | Vtrip_   | Vtrip_NAND_ | No of        |        |

|-------|----------|------------|-----------|----------|-------------|--------------|--------|

| mV)   | wer      | r Bound    | Vtrip_NAN |          |             |              |        |

|       | Bound    |            | D         | NAND_    | Sigma       | NAND         | NAND_F |

|       |          | (mV)       |           |          |             |              | aliure |

|       | (mV)     |            | (mV)      | Mean(mV) | (mV)        | out of range | Rate%  |

| 300   | 125      | 175        | 149.8     | 149.364  | 15.1059     | 44           | 22     |

|       |          |            |           |          |             |              |        |

| 320   | 125      | 195        | 160.2     | 159.746  | 15.1339     | 11           | 5.5    |

|       |          |            |           |          |             |              |        |

| 340   | 125      | 215        | 170.6     | 170.112  | 15.158      | 6            | 3      |

|       |          |            |           |          |             |              |        |

| 360   | 125      | 235        | 181       | 180.463  | 15.1797     | 1            | 0.5    |

|       |          |            |           |          |             |              |        |

Table 3.12 Failure rate of NOR2X1 vs increasing VDDD(200pt MC simulation)

| VDDD(mV) | Vtrip_Lower<br>Bound(mV) | Vtrip_Upper<br>Bound<br>(mV) | Vtrip_NOR<br>(mV) | Vtrip_NOR_<br>Mean(mV) | Vtrip_NOR_<br>Sigma(mV) | No of NOR<br>out of range | NOR_Faliure<br>Rate% |

|----------|--------------------------|------------------------------|-------------------|------------------------|-------------------------|---------------------------|----------------------|

| 300      | 125                      | 175                          | 150               | 148.989                | 11.1461                 | 8                         | 4                    |

| 320      | 125                      | 195                          | 160.1             | 159.041                | 11.1591                 | 7                         | 3.5                  |

| 340 | 125 | 215 | 170.2 | 169.068 | 11.1681 | 2 | 1 |

|-----|-----|-----|-------|---------|---------|---|---|

| 360 | 125 | 235 | 180.2 | 179.006 | 11.1738 | 0 | 0 |

It is clearly observable that the failure rate for INVX1, NAND2X1 and NOR2X1 is zero at VDDD=360mV for CMOS logic. The reason is, the trip point( $V_{Trip}$ ) distribution Mean( $\mu$ ) shifts to a higher value while the Sigma( $\sigma$ ) changes insignificantly. However, we can also decrease the failure rate by increasing NOF(area) of both NMOS and PMOS. This is shown in Table 3.13 where we measure the Vtrip variation of an Inverter with increasing NOF for both NMOS and PMOS. It shows that sigma\_Vtrip actually decreasing w.r.t. increasing NOF proportional to 1/SQRT(WL) as expected.

Table 3.13 Change in INVX1 Failure Rate with increasing device fingers at VDDD=300mV

| Inverter | Inverter | Inverter | Inverter | Inverter | Inverter | Vtrip_Inv | Sigma_Vt   | Mean_Vtr   | Failure |

|----------|----------|----------|----------|----------|----------|-----------|------------|------------|---------|

| NMOS     | NMOS     | NMOS     | PMOS     | PMOS     | PMOS     | erter     | rip_Invert | ip_Inveter | Rate %  |

| Width    | Length   | NOF      | Width    | Length   | NOF      |           | er         |            |         |

|          |          |          |          |          |          |           |            |            |         |

| 220      | 180      | 1        | 220      | 180      | 2        | 150       | 15.674     | 150.1      | 16.5    |

|          |          |          |          |          |          |           |            |            |         |

| 220      | 180      | 2        | 220      | 180      | 4        | 148.3     | 13.42      | 148.53     | 6.5     |

|          |          |          |          |          |          |           |            |            |         |

| 220      | 180      | 3        | 220      | 180      | 6        | 147.8     | 12.6632    | 147.789    | 2.5     |

|          |          |          |          |          |          |           |            |            |         |

| 220      | 180      | 4        | 220      | 180      | 8        | 147.5     | 12.2665    | 147.399    | 2.5     |

|          |          |          |          |          |          |           |            |            |         |

Now we verify as to which of the following is a better approach to reducing failure rate.

- 1. Increase VDDD to shift the distribution and Vtrip\_Mean to a higher value so that more samples fall within acceptable range. This produces an insignificant change in Sigma\_Vtrip.

- 2. Increase NOF or area of both PMOS and NMOS to reduce Sigma(6) of Vtrip distribution.

To make the choice, we take the best cases from Table 3.10 and Table 3.13 for an inverter where they have lower failure rates. We take the beta matched INVX1 (1st device sizing in Table 3.13) and make an 11 stage FO4 inverter stage[1] to measure Delay, Pavg, PDP at 360 mV ( we obtained a failure rate of zero at VDDD=360mV). We then run the same experiment taking 4th the device sizing for INVX1 from Table 3.13) and measure the same parameter at VDDD=300mV and compare these two cases. The results are displayed in Table 3.14. *Table 3.14 reveals the fact that reducing the failure rate by increasing VDDD is preferred in terms of PDP*.

Table 3.14 PDP measurement for INVX1 from Table 3.10 and Table 3.13

| NMO<br>S<br>Width<br>(nm) | NMOS<br>Length<br>(nm) | NMOS<br>NOF | PMOS<br>Width<br>(nm) | PMOS<br>Length | PMOS<br>NOF | Halfpt_<br>diff(ns) | Integrat<br>ed<br>current(<br>fA) | avg_cur<br>rent (A) | VDD(<br>mV) | Pavg(w<br>att)  | PDP<br>(J)   |

|---------------------------|------------------------|-------------|-----------------------|----------------|-------------|---------------------|-----------------------------------|---------------------|-------------|-----------------|--------------|

| 220                       | 180                    | 4           | 220                   | 180            | 8           | 376                 | 27.5                              | 7.31383<br>E-08     | 300         | 2.19415<br>E-08 | 8.25E<br>-15 |

| ſ | 220 | 180 | 1 | 220 | 180 | 2 | 124.3 | 8.103 | 6.51891 | 360 | 2.34681 | 2.917 |

|---|-----|-----|---|-----|-----|---|-------|-------|---------|-----|---------|-------|

|   |     |     |   |     |     |   |       |       | E-08    |     | E-08    | 08E-  |

|   |     |     |   |     |     |   |       |       |         |     |         | 15    |

|   |     |     |   |     |     |   |       |       |         |     |         |       |

#### 3.5 EXTENSION TO T-GATE LOGIC GATES

We next extend our analysis to T-Gate designs and then compare the proposed T-Gate designs with classical CMOS logic. The trip point of T-Gate based NAND2X1 and NOR2X1 is acceptably\_close to VDDD/2 due to having beta matched inverters as the output stage. In this case varying the device size has no useful effect. The butterfly plot at VDDD=300mV for T-gate NAND2X1 driving T-Gate NOR2X1 and vice versa, is used to obtain the worst case scenario of SNM and plotted (Figure 3.14) side by side with the best case of CMOS topology for comparison. Figure 3.14 clearly shows that standard CMOS logic having better noise margin compared to the T-gate design. Thus verifying that standard CMOS design topology is more robust compared to T-Gate logic designs.

Figure 3.14: Butterflies: best case of CMOS Logic and best case of T-gate Logic

We measure the failure (as defined earlier) rate as described earlier and then attempt to reduce it by increasing VDDD. The results are shown for INVX1, NAND2X1 and NOR2X1 as before, in Table 3.15, 3.16, 3.17 respectively.

| VDDD(mV | Vtrip_Lower | Vtrip_Upper | Vtrip_Inverte | Vtrip_Inverte | Vtrip_Inverte | No of        | Inverter_F |

|---------|-------------|-------------|---------------|---------------|---------------|--------------|------------|

| )       | Bound(mV)   | Bound(mV)   | r(mV)         | r_Mean(mV)    | r_Sigma(mV)   | inverter out | aliure     |

|         |             |             |               |               |               | of range     | Rate%      |

|         |             |             |               |               |               |              |            |

| 300     | 125         | 175         | 150           | 150.1         | 15.674        | 33           | 16.5       |

|         |             |             |               |               |               |              |            |

| 320     | 125         | 195         | 160.1         | 160.224       | 15.7047       | 11           | 5.5        |

|         |             |             |               |               |               |              |            |

Table 3.15 Failure Rate of INVX1 vs Increasing VDDD

| 340 | 125 | 215 | 170.2 | 170.367 | 15.7314 | 6 | 3 |

|-----|-----|-----|-------|---------|---------|---|---|

|     |     |     |       |         |         |   |   |

| VDDD(m<br>V) | Vtrip_Lower<br>Bound(mV) | Vtrip_Upper<br>Bound(mV) | Vtrip_NAND<br>(mV) | Vtrip_NAND<br>_Mean(mV) | Vtrip_NAND<br>_Sigma(mV) | No of NAND<br>out of range | NAND_F<br>aliure<br>Rate% |

|--------------|--------------------------|--------------------------|--------------------|-------------------------|--------------------------|----------------------------|---------------------------|

| 300          | 125                      | 175                      | 147.1              | 148.564                 | 11.69                    | 18                         | 9                         |

| 320          | 125                      | 195                      | 157                | 158.394                 | 11.878                   | 5                          | 2.5                       |

| 340          | 125                      | 215                      | 166.9              | 168.21                  | 12.0715                  | 0                          | 0                         |

Table 3.16 Failure Rate of T-Gate NAND2X1 vs increasing VDDD

Table 3.17 Failure Rate of T-Gate NOR2X1 vs increasing VDDD

| VDDD(m | Vtrip_Lower | Vtrip_Upper | Vtrip_NOR( | Vtrip_NOR_ | Vtrip_NOR_ | No of NOR    | NOR_Fali  |

|--------|-------------|-------------|------------|------------|------------|--------------|-----------|

| V)     | Bound(mV)   | Bound(mV)   | mV)        | Mean(mV)   | Sigma(mV)  | out of range | ure Rate% |

| 300    | 125         | 175         | 149        | 145.242    | 11.3954    | 28           | 14        |

|        |             |             |            |            |            | -            |           |

| 320    | 125         | 195         | 159.4      | 155.608    | 11.5774    | 2            | 1         |

| 340    | 125         | 215         | 169.8      | 165.925    | 11.7501    | 1            | 0.5       |

|        |             |             |            |            |            |              |           |

It is clear that the failure rate for T-gate NAND2X1 and NOR2X1 goes to zero at a lower voltage (340mV) than its standard CMOS equivalent. However, INVX1 does not produce a zero failure rate at VDDD=340mv (From Table 3.15).

Finally we find the optimum operating frequency given a particular VDDD of interest. To do so, we simulate a 7 stage NAND-NOR ring oscillator representing a hypothetical critical path. We find out the optimum clock frequency that can propagate through this loop. Also the drift in frequency is noted as we move from tt process corner to ss process corners. The results are summarized in Table 3.18.

Table 3.18 Ring Oscillator frequency vs increasing VDDD

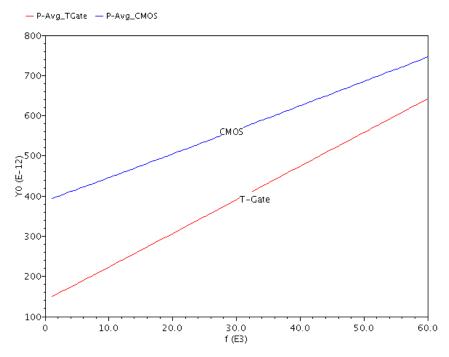

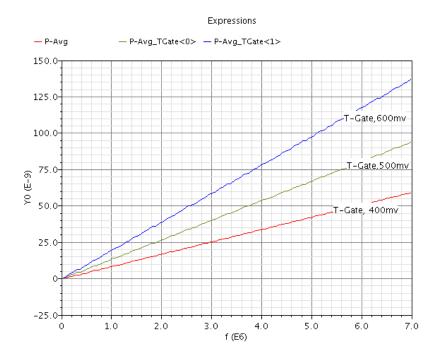

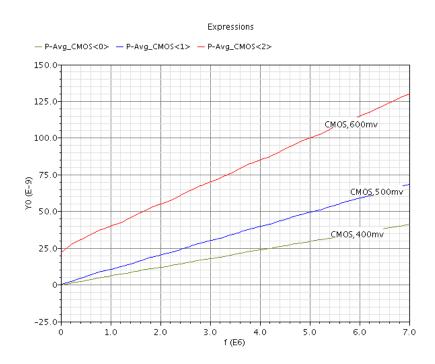

| Design<br>Topology | VDDD(mV) | Ring Oscillator Output Freq_TT<br>Corner(MHz) | Ring Oscillator Output Freq_SS<br>Corner(MHz) | % Frequency Degradation |