## **INTERCONNECT DESIGN WITH LARGE**

## TRANSISTOR CONSTRAINTS FOR

# **MULTI-CHIP MODULES AND**

## LARGE DIE SOI/SOS

By

## JIE WEN

Bachelor of Science

Huazhong University of Science and Technology

WuHan, China

1989

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of MASTER OF SCIENCE May, 1998

# INTERCONNECT DESIGN WITH LARGE

# TRANSISTOR CONSTRAINTS FOR

## **MULTI-CHIP MODULES AND**

# LARGE DIE SOI/SOS

Thesis Approved: Thesis Advisor 1 Dean of the Graduate College

### ACKNOWLEDGEMENTS

This study was conducted to develop a set of general design guidelines and performance estimation equations of long interconnects for high-speed multi-chip modules and large die SOI/SOS applications. Analysis and simulation results are presented. A novel layout for transistors with large width is also developed.

I wish to express my sincere appreciation to my major advisor, Dr. Chriswell Hutchens for his intelligent supervision, constructive guidance and inspiration. My sincere appreciation extends to my other committee members Dr. Louis G. Johnson and Dr. Scott Shepard. I would like to thank the Naval Ocean Surveillance Command for providing the research opportunity and financial support to this project.

Moreover, I wish to express my sincere gratitude to my colleagues who provided suggestions and assistance for this study.

I would also like to give my special appreciation to my wife, Li Zhou, for her strong encouragement at times of difficulty, love and understanding throughout this whole process. Thanks also go to my parents for their support and encouragement.

Finally, I would like to thank the Department of Electrical and Computer Engineering for supporting during these years of study.

# **TABLE OF CONTENTS**

| Ch | apter      | Pa                                                                                                  | ge |

|----|------------|-----------------------------------------------------------------------------------------------------|----|

| 1. | INTRODU    | UCTION                                                                                              | 1  |

|    | 1.1 Object | tive                                                                                                | 3  |

|    | 1.2 Organ  | ization                                                                                             | 5  |

| 2. | EXTRAC     | TION OF <i>R</i> , <i>L</i> , <i>C</i> AND $Z_0$                                                    | 7  |

|    | 2.1 Transr | nission Line                                                                                        | 7  |

|    | 2.2 Select | ion of Material for the Substrate                                                                   | 9  |

|    | 2.2.1 H    | Effective Dielectric Constant of Substrate                                                          | 9  |

|    | 2.2.2 8    | Selection of Material of Substrate                                                                  | 10 |

|    | 2.3 Extrac | tion of Self Capacitance and Inductance of Microstrip                                               | 11 |

|    | 2.3.1      | Calculation of Self Capacitance ( <i>pF/cm</i> ) and inductance<br>Microstrip( <i>nH/cm</i> )       | 11 |

|    | 2.3.2      | Properties of Self Capacitance and Inductance of Microstrip                                         | 12 |

|    | 2.3.3      | Comparison of Self Capacitance on Insulating Substrate and on<br>Oxide-Passivated Silicon Substrate | 14 |

|    | 2.4 Extrac | tion of Self Resistance (Ω/cm) of Microstrip                                                        | 15 |

|    | 2.4.1      | Calculation of Sheet Resistance                                                                     | 15 |

|    | 2.4.2      | Skin Effect                                                                                         | 16 |

|    | 2.4        | 4.2.1 Calculation of Resistance with Skin Effect                                                    | 16 |

|    | 2.4        | 4.2.2 Cutoff Frequency                                                                              | 17 |

|    | 2.5 Comp   | utation of Characteristic Impedance $Z_0(\Omega)$                                                   | 18 |

|    | 2.5.1      | Characteristic Impedance $Z_0$ of Transmission Line                                | 18 |

|----|------------|------------------------------------------------------------------------------------|----|

|    | 2.5.2      | A Comparison of the Microstrip Characteristic Impedance on<br>Different Substrates | 10 |

|    | 2 C Deinte | Different Substrates                                                               | 19 |

|    | 2.0 Points | of Design                                                                          | 21 |

| 3. | DESIGN     | OF TRANSMISSION LINES                                                              | 22 |

| 5. | DESIGN     | OF TRANSMISSION LINES                                                              | 23 |

|    | 3.1 Lossle | ss, Lossy and Fully Lossy Transmission Line                                        | 24 |

|    | 3.1.1      | Definition of Lossless, Lossy and Fully Lossy Transmission Line                    | 24 |

|    | 3.1.2      | Characteristic of Three Types of Transmission Line                                 | 25 |

|    | 3.2 Optim  | al Delay Design of A Transmission Line                                             | 27 |

|    | 3.2.1      | First Incidence Voltage                                                            | 28 |

|    | 3.2.2      | Lumped RLC Model for a Lossy Transmission Line                                     | 29 |

|    | 3.2.3      | The Delay Estimation for a transmission line                                       | 32 |

|    | 3.2.4      | Delay Factor Sensitivity Analysis                                                  | 34 |

|    | 3.2.5      | Oscillation of Series RLC Circuits                                                 | 35 |

|    | 3.2.6      | Optimizing the Delay                                                               | 37 |

|    | 3.3 Periph | eral Parts' Effect on Interconnection Performance                                  | 39 |

|    | 3.4 Loss o | f Transmission Line                                                                | 41 |

|    | 3.5 PSPIC  | E Simulation of Transmission Line Signal Delay                                     | 43 |

|    | 3.6 Points | of Design                                                                          | 46 |

|    |            |                                                                                    |    |

| 4. | DESIGN     | CONSIDERATIONS TO ELIMINATE SELF GENERATED NOISE                                   | 48 |

|    |            |                                                                                    |    |

|    | 4.1 Reflec | tion Noise                                                                         | 49 |

|    | 4.1.1      | Series Termination                                                                 | 49 |

|    | 4.1.2      | Optimal Resistor Value of Termination                                              | 51 |

|    | 4.1.3      | Signal Termination Simulation                                                      | 54 |

|    | 4.2 Driver | Size Design                                                                        | 56 |

|    | 4.2.1      | Driver Size Estimation Model                                                       | 56 |

|    | 4.2.2      | Simulation and Discussion                                                          | 58 |

|    | 4.3 Crosst | alk                                                                        | 62  |

|----|------------|----------------------------------------------------------------------------|-----|

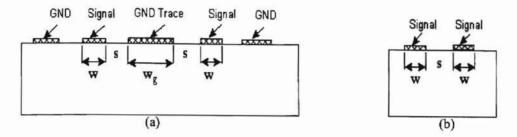

|    | 4.3.1      | Calculation of Crosstalk                                                   | 63  |

|    | 4.3.2      | Simulation of Cross-Talk                                                   | 67  |

|    | 4.3        | 3.2.1 The Accuracy of Mathematical Model                                   | 68  |

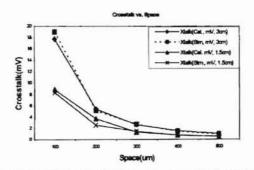

|    | 4.3        | 3.2.2 Cross-Talk Vs. Spacing Between Two Signal Lines                      | 69  |

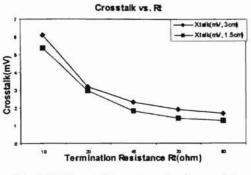

|    | 4.3        | 3.2.3 Cross-Talk Vs. Termination Resistance                                | 71  |

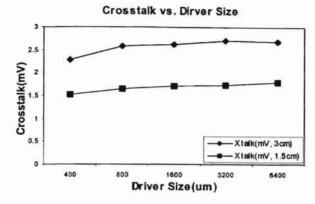

|    | 4.3        | 3.2.4 Cross-Talk Vs. Transmission Line Driver Size                         | 72  |

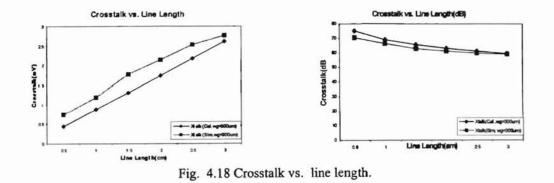

|    | 4.3        | 3.2.5 Cross-Talk Vs. Transmission Line Length                              | 73  |

|    | 4.3        | 3.2.6 Comparison of Coplanar Waveguides and Adjacent Microstrips           | 74  |

|    | 4.3.3      | Discussion and Reduction of Cross-Talk                                     | 76  |

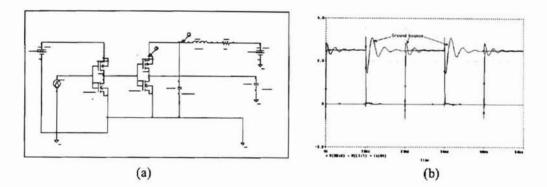

|    | 4.4 Simult | aneous Switching Noise (Ground Bounce)                                     | 78  |

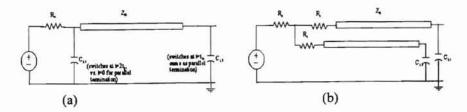

|    | 4.4.1      | Analysis of Simultaneous Switching Noise                                   | 80  |

|    | 4.4.2      | Forming Damped RLC Equivalent Circuit of Power Trace                       | 83  |

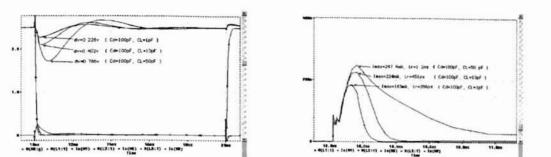

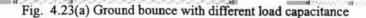

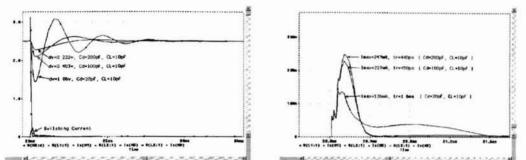

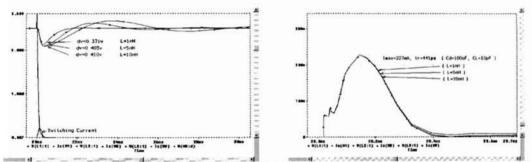

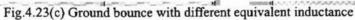

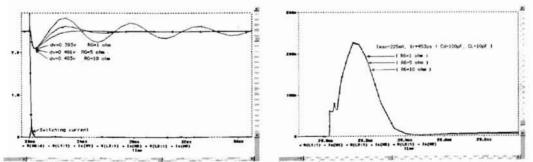

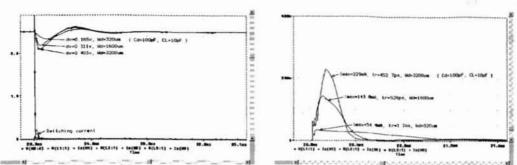

|    | 4.4.3      | Simulation of Ground Bounce                                                | 85  |

|    | 4.4.4      | Summary of Ground Bounce Reduction                                         | 91  |

|    | 4.5 Points | of Design                                                                  | 92  |

|    |            |                                                                            |     |

| 5. | NOVEL L    | AYOUT DESIGN FOR LARGE TRANSISTOR                                          | 96  |

|    |            |                                                                            |     |

|    | 5.1 Overv  | iew of problems                                                            | 97  |

|    | 5.2 The E  | ffect of $R_g$ on $f_T$ , $f_{max}$ , Thermal Noise and Transient Response | 98  |

|    | 5.2.1      | Cutoff Frequency $f_T$                                                     | 99  |

|    | 5.2.2      | Maximum Frequency of Oscillation fmax                                      | 100 |

|    | 5.2.3      | Thermal Noise                                                              | 102 |

|    | 5.2.4      | Device Delay                                                               | 103 |

|    | 5.3 The E  | ffect of $R_s$ on $g_m$ , $g_{ds}$ and Bandwidth                           | 104 |

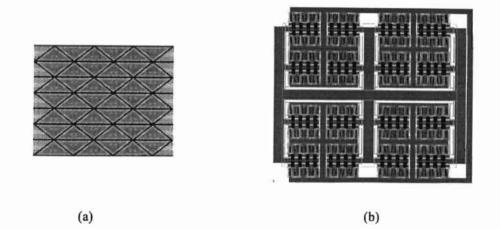

|    | 5.4 Novel  | Structure for Large Transistor                                             | 106 |

|    | 5.4.1      | Selection of Basic Cell                                                    | 107 |

|    | 5.4.2      | Novel Layout Based on Triangle and Diamond Cell                            | 108 |

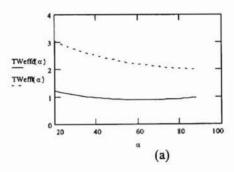

|    | 5.5 Comp   | arison of Triangle and Finger Structure                                    | 113 |

|    | 5.6 Conclu | usion                                                                      | 115 |

| 6. | CONCLUSION AND SUGGESTION                    | 116 |

|----|----------------------------------------------|-----|

|    | 6.1 Conclusion                               | 116 |

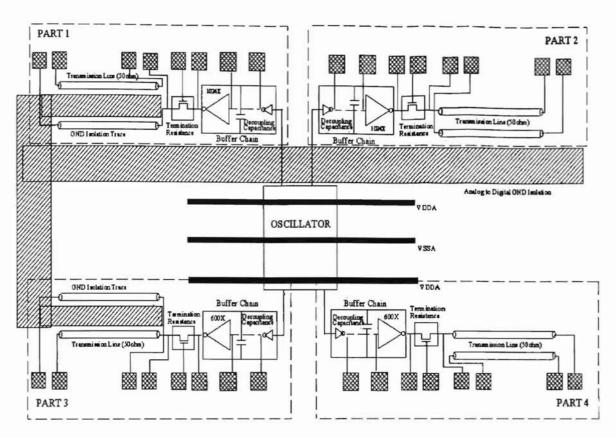

|    | 6.2 Test Structure                           | 120 |

|    | 6.3 General Design Procedure and Suggestions | 122 |

| BI | BLIOGRAPHY                                   | 128 |

# LIST OF TABLES

| Table                                                                       | age |

|-----------------------------------------------------------------------------|-----|

| 2.1 (a)(b) Example cal. Parameter data of a lossy transmission              | 21  |

| 3.1 Definition of lossless, lossy and fully lossy transmission line         | 25  |

| 3.2 Sensitivity of line delay to various parameters                         | 34  |

| 3.3 Calculation and simulation data of signal delay for a transmission line | 44  |

| 4.1 Series termination simulation data                                      | 53  |

| 4.2 The effect of driver width on signal risetime                           | 59  |

| 4.3 Risetime calculation and simulation data with different line lengths    | 60  |

| 4.4 Calculation and simulation data for mathematical model accuracy         | 68  |

| 4.5 Simulation and calculation data of crosstalk vs. Spacing                | 70  |

| 4.6 Simulation data of crosstalk vs. termination resistance $R_t$           | 72  |

| 4.7 Simulation data of crosstalk vs. driver size                            | 73  |

| 4.8 Simulation and calculation data of crosstalk vs. different line lengths | 74  |

| 4.9 Crosstalk simulation data for waveguides with separating GND trace<br>and adjacent microstrip lines with separating GND trace | 75  |

|-----------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.10 Ground bounce simulation data                                                                                                | 88  |

| 5.1 The extracted data comparison between triangle and finger structure                                                           | 114 |

# LIST OF FIGURES

| gure Page                                                                                                      |

|----------------------------------------------------------------------------------------------------------------|

| 1 A simple diagram of interconnection 4                                                                        |

| 1 Cross-sections of typical transmission line structure                                                        |

| 2 Cross-sections of microstrips on insulating substrate (a) and oxide-passivated silicon (b) 11                |

| <ul> <li>3 Microstrip self capacitance and inductance versus line width (w) and substrate height (h)</li></ul> |

| 4 Self capacitance on oxide-passivated silicon, sapphire and GaAs 14                                           |

| 5 Effect of parallel loads on characteristic impedance                                                         |

| 6 Properties of characteristic impedance                                                                       |

| 1 The basic lumped <i>RLC</i> segment for a lossy transmission line                                            |

| 2 (a) "Tee" type symmetric lumps; (b) "Pi" type symmetric lumps;<br>(c) "Gamma" type lumps                     |

| 3 Lumped and distributed model for interconnection                                                             |

| 4 Typical series <i>RLC</i> circuits and typical response                                                      |

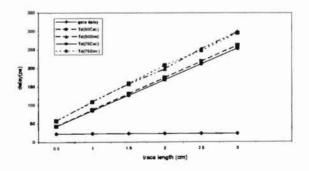

| 3.5 Delay versus line width                                                                                                                                                                                                                       | 38 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.6 Graphical illustration of bond wire delay                                                                                                                                                                                                     | 39 |

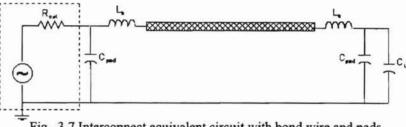

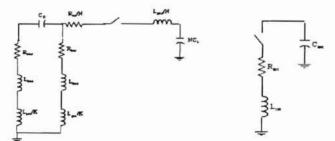

| 3.7 Interconnect equivalent circuit with bond wire and pads                                                                                                                                                                                       | 40 |

| 3.8 Equivalent RLC circuit of input and output ends                                                                                                                                                                                               | 41 |

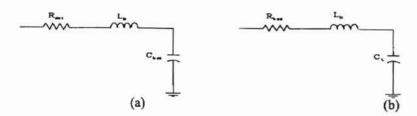

| 3.9 (a) Resistance attenuation constant versus line width; (b) Resistance attenuation versus operating frequency                                                                                                                                  | 43 |

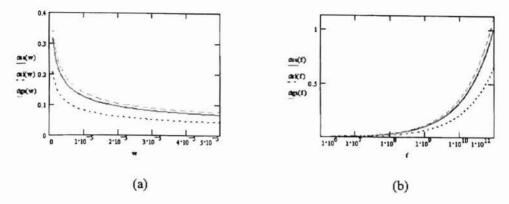

| 3.10 Delay simulation schematics and segments                                                                                                                                                                                                     | 44 |

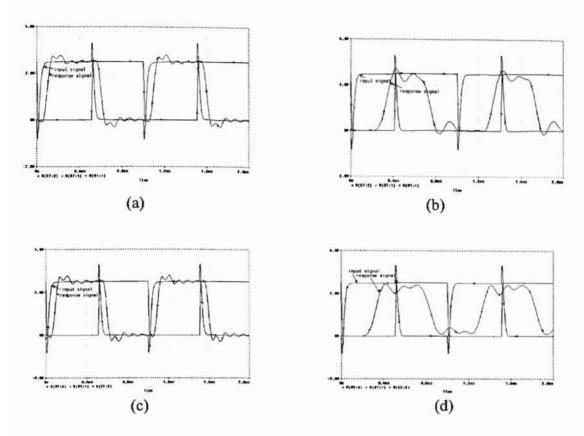

| 3.11 Delay simulation results (a), (b), (c) and (d)                                                                                                                                                                                               | 45 |

| 3.12 Comparison of calculation and simulation data for signal delay                                                                                                                                                                               | 45 |

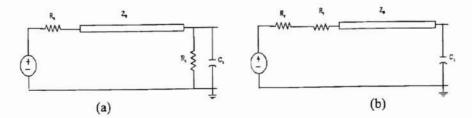

| 4.1 (a) Parallel termination; (b) Series termination                                                                                                                                                                                              | 49 |

| <ul><li>4.2 (a) Second-incidence switching problem of series termination with multiple loads;</li><li>(b) Parallel fan-out with multiple series termination</li></ul>                                                                             |    |

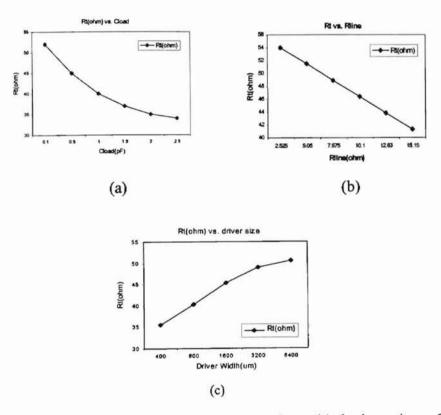

| <ul> <li>4.3 The function of termination resistance, R<sub>t</sub>, vs. (a) load capacitance C<sub>L</sub>;</li> <li>(b) line resistance, R<sub>line</sub>; (c) Driver channel resistance, R<sub>on</sub></li> </ul>                              | 53 |

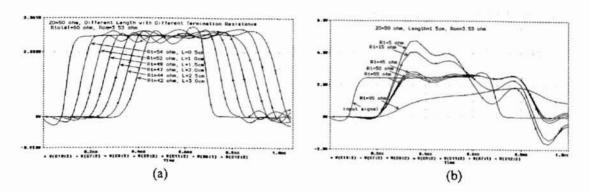

| <ul> <li>4.4 Simulation waveform of series termination <ul> <li>(a) Optimal termination with different transmission line length;</li> <li>(b) Different termination resistance with fixed line length i.e. line resistance</li> </ul> </li> </ul> | 55 |

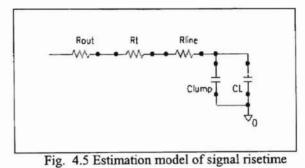

| 4.5 Estimation model of signal risetime                                                                                                                                                                                                           | 57 |

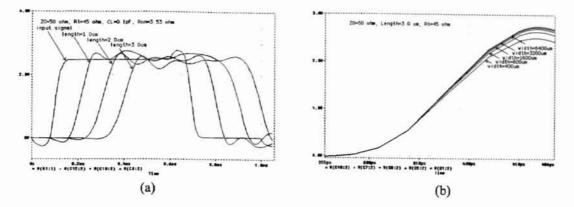

| 4.6 The simulation results of signal risetime (a) risetime versus transmission line length and (b) risetime versus driver size.                                                                                                                   | 59 |

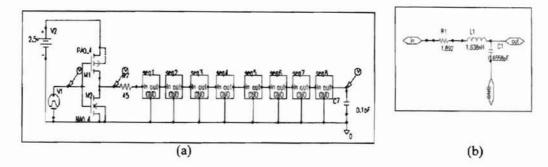

| 4.7 Risetime simulation schematics and segment                                                                                                                                                                                                    | 59 |

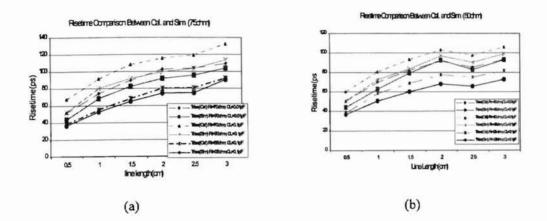

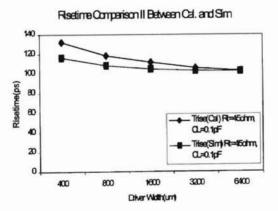

| <ul> <li>4.8 Risetime comparison between calculation and simulation (a) Z<sub>0</sub>=50Ω and</li> <li>(b) Z<sub>0</sub>=75Ω with different load capacitance, termination resistance and line width</li> </ul> | 61 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.9 Risetime comparison between cal. and sim. with different driver size                                                                                                                                       | 61 |

| 4.10 Cross-sections of (a) coplanar waveguides; (b) microstrips                                                                                                                                                | 64 |

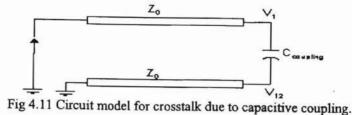

| 4.11 Circuit model for crosstalk due to capacitance coupling                                                                                                                                                   | 65 |

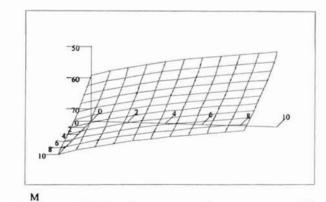

| 4.12 Capacitance crosstalk of coplanar waveguides versus ground line width and signal frequency                                                                                                                | 66 |

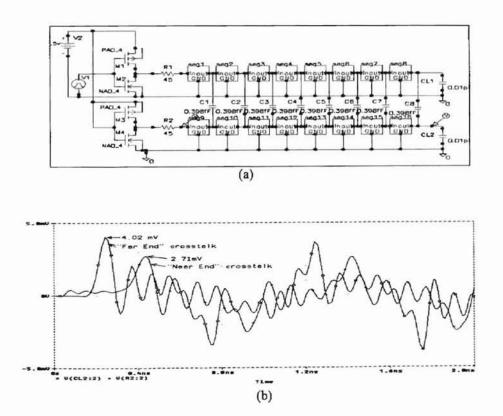

| <ul><li>4.13 Capacitance crosstalk simulation (a) Simulation schematics;</li><li>(b) One sample simulation waveform</li></ul>                                                                                  | 67 |

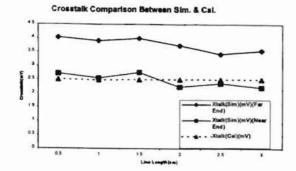

| 4.14 Crosstalk comparison between simulation and calculation data                                                                                                                                              | 69 |

| 4.15 Capacitive crosstalk versus spacing of two signal lines                                                                                                                                                   | 70 |

| 4.16 Crosstalk versus termination resistance                                                                                                                                                                   | 72 |

| 4.17 Crosstalk versus driver size                                                                                                                                                                              | 73 |

| 4.18 Crosstalk versus line width                                                                                                                                                                               | 74 |

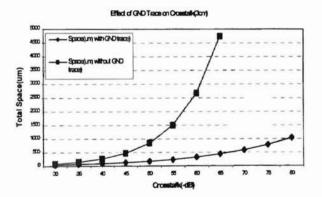

| 4.19 Effect of GND trace on crosstalk                                                                                                                                                                          | 75 |

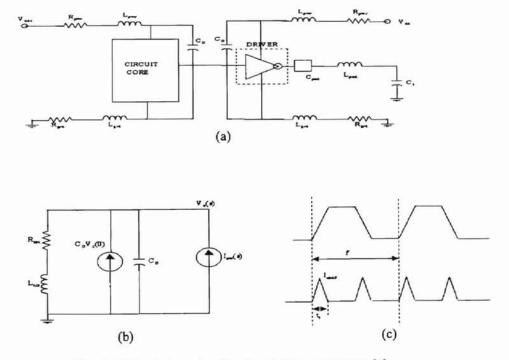

| 4.20 Equivalent circuit and switching current model                                                                                                                                                            | 80 |

| 4.21 Equivalent RLC circuit for power supply system                                                                                                                                                            | 83 |

| 4.22 Ground bounce simulation circuit and typical response                                                                                                                                                     | 85 |

| 4.23 Ground bounce simulation results (a), (b), (c), (d) and (e)                                                                                                                                               | 87 |

| 4.24 Ground bounce vs. Decoupling capacitance to load capacitance ratio                                                                                                                                        | 88 |

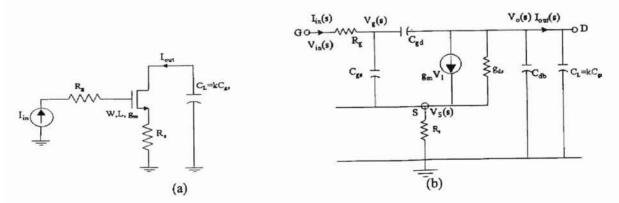

| 5.1 | Equivalent circuit models used in analysis of $R_g$ effect on transistor performance.<br>(a) lumped model; (b) small-signal model of a MOSFET                                            | 98  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

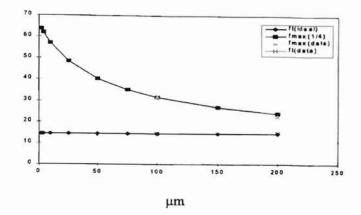

| 5.2 | Calculated $f_T$ and $f_{max}$ data versus test data                                                                                                                                     | 102 |

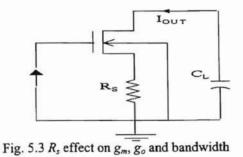

| 5.3 | $R_s$ effect on $g_{m_s} g_{ds}$ and bandwidth                                                                                                                                           | 105 |

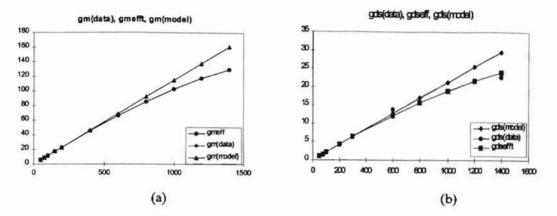

| 5.4 | (a) $g_m$ versus transistor width; (b) $g_{ds}$ versus transistor width                                                                                                                  | 106 |

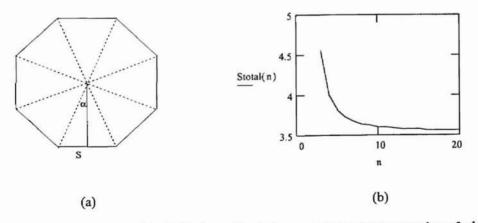

| 5.5 | <ul><li>(a) Polygon with n identical edges;</li><li>(b) Polygon perimeter versus number of edges</li></ul>                                                                               | 107 |

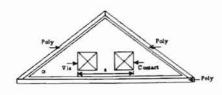

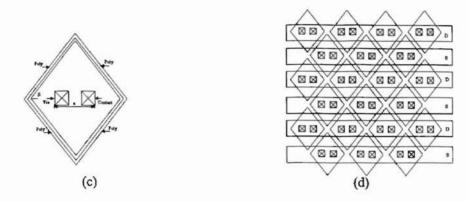

| 5.6 | Triangle and diamond basic cell and layout structure. (a) triangle cell;<br>(b) layout structure based on triangle cell; (c) diamond cell;<br>(d) layout structure based on diamond cell | 109 |

| 5.7 | Comparison of triangle and diamond structure (a), (b), (c), (d) and (e)                                                                                                                  | 113 |

| 5.8 | Side by side comparison of layouts with triangle and finger structure                                                                                                                    | 113 |

| 6.1 | Test structure for transmission line and large transistor                                                                                                                                | 121 |

# NOMENCLATURE

| c <sub>0</sub> | Speed | of Light | in Vacuum |

|----------------|-------|----------|-----------|

|                |       | 0        |           |

| C Line Capacitance per Uni | C | Line | Capacitance | per | Unit |

|----------------------------|---|------|-------------|-----|------|

|----------------------------|---|------|-------------|-----|------|

C<sub>coupling</sub> Mutual Capacitance for Crosstalk

- C<sub>gs</sub> Gate to Source Capacitance of Transistor

- C<sub>db</sub> Drain to Body Capacitance of Transistor

- Cline Total Line Capacitance

- Clump Capacitance of Lumped RLC segment

- C<sub>source</sub> Capacitance of Signal Source

- Ctotal Total Capacitance of Interconnection

- C<sub>D</sub> Decoupling Capacitance

- C<sub>L</sub> Load Capacitance

- d Interconnect Line Length

- d<sub>b</sub> Bond Wire Length

- d<sub>max</sub> Maximum Interconnect Line Length

- f Signal Operating Frequency

- fc Cutoff Frequency of Skin Effect

- f<sub>T</sub> Cutoff Frequency of Transistor

- fmax Maximum frequency of transistor

- g<sub>m</sub> Transconductance Parameter

- gds Drain to Source Transconductance Parameter

- h Height of Substrate

- L Line Inductance per Unit Channel Length for Transistor

- L<sub>b</sub> Bond Wire Inductance

| L <sub>lump</sub>         | Inductance of Lumped RLC segment                            |

|---------------------------|-------------------------------------------------------------|

| $L_{line}$                | Total Line Inductance                                       |

| L <sub>total</sub>        | Total Inductance of Interconnection                         |

| Ν                         | Number of Lumped RLC segments                               |

| Q                         | Quality Factor                                              |

| r                         | Radius of round Wire                                        |

| R                         | Line Resistance per Unit                                    |

| $R_g$                     | Gate Resistance of Transistor                               |

| Rs                        | Source Resistance of Transistor                             |

| R <sub>critical</sub>     | Resistance set to "critical damping" for Series RLC circuit |

| R <sub>lump</sub>         | Resistance of Lumped RLC segment                            |

| $R_{line}$                | Total Line Resistance                                       |

| $R_{\text{sheet}}$        | Sheet Resistance of Metal Trace                             |

| Ron                       | Turn-on Resistance of Transistor                            |

| Rout                      | Output Impedance of Driver                                  |

| $\mathbf{R}_{\mathbf{S}}$ | Source Output Resistance                                    |

| $R_t$                     | Termination Resistance                                      |

| $R_{\text{teff}}$         | Effective Termination Resistance                            |

| R <sub>total</sub>        | Total Resistance of Interconnection                         |

| S                         | Spacing Between two Parallel Traces                         |

| t                         | Thickness of Interconnection Line                           |

| t <sub>b</sub>            | Bond Wire Induced Delay                                     |

| t <sub>d</sub>            | Delay of Interconnect including Buffer Chain                |

| tdi                       | Delay of interconnect                                       |

| t <sub>db</sub>           | First Stage Delay of Buffer Chain                           |

| t <sub>ds</sub>           | Delay of One Lumped RLC Segment                             |

| tf                        | Time-of-flight                                              |

| t <sub>ox</sub>           | Thickness of Oxide Layer                                    |

| tr                        | Signal Risetime                                             |

| $V_{12}$                  | Crosstalk Voltage                                           |

| $V_{\text{first}}$        | First Incidence Voltage                                     |

|                           |                                                             |

| $\mathbf{V}_{in}$ | Input Voltage                                                            |

|-------------------|--------------------------------------------------------------------------|

| $V_{A}$           | Fast Rising Portion of Unit Step Signal Response for a Transmission Line |

| $V_{\text{dd}}$   | Positive Power Supply                                                    |

| $V_{\text{GS}}$   | Gate to Source Voltage                                                   |

| $V_{\text{IH}}$   | Minimum Input High Voltage                                               |

| $V_{\text{IL}}$   | Maximum Input Low Voltage                                                |

| $V_R$             | Slow Rising Portion of Unit Step Signal Response for a Transmission Line |

| $\mathbf{V}_{T}$  | Threshold Voltage                                                        |

| w                 | Interconnection Width                                                    |

| Weff              | Effective Width of Interconnection                                       |

| $\mathbf{w}_{g}$  | GND trace width                                                          |

| W                 | Channel Width of Transistor                                              |

| $W_{\text{eff}}$  | Effective Channel width of Transistor                                    |

| $Z_0$             | Characteristic Impedance of Transmission line                            |

| $Z_{\text{load}}$ | Effective Load Impedance                                                 |

| α                 | Scaling Factor of Buffer Chain                                           |

| $\alpha_D$        | Dielectric Attenuation Constant                                          |

| $\alpha_R$        | Resistance Attenuation Constant with Skin Effect                         |

| $\alpha_{s}$      | Resistance Attenuation Constant without Skin Effect                      |

| β                 | Electrical "Length" of Lumped RLC segment                                |

| ε                 | Dielectric Constant of Material                                          |

| ε <sub>0</sub>    | Permittivity of Free Space                                               |

| Eeff              | Effective Dielectric Constant                                            |

| ε <sub>r</sub>    | Relative Dielectric Constant                                             |

| μ                 | Magnetic Permeability of Free Space                                      |

|                   | Transistor Self Gain                                                     |

| $\mu_r$           | Relative Magnetic Permeability of Material                               |

| ρ                 | Resistivity of Material                                                  |

| $\delta_s$        | Skin Depth                                                               |

| ω                 | Signal Frequency                                                         |

|                   |                                                                          |

- v Signal Propagation Speed

- τ Signal Delay of per Unit

- ΔC Mutual Capacitance per Unit

- Δv Inductance Induced Voltage

#### CHAPTER 1

## INTRODUCTION

The development of integrated circuit has gone through the stages of small-scale integration, medium scale integration and very large scale integration (VLSI). This technology revolution increases complexity and density of semiconductor devices allowing electronic systems to reach even higher performance. To keep pace with the advances in IC technology, a higher performance packaging and interconnection have been developed [5][7]. Large die SOI/SOS and multiple chip modules (MCMs) are developed as advanced system applications with complex functions and high speed. In large size single die and MCMs applications, the interconnection density and length increases dramatically. For example, the die size has grown up to  $20mm \times 20mm$  [6] in a recent report. In MCMs, the wiring capacity is greater than 400cm/cm<sup>2</sup>, and the size reaches 127.5mm ×127.5mm (IBM ES900) [1] with the maximum length reaching to tens of cm. Simultaneously, as the fabrication technology has improved, the device geometry has scaled down to  $L_{eff} = 0.09 \mu m$ , with a highest unity-current-gain frequency of 100GHz for NMOS,  $(f_T)$  [55]. Due to the greater line length, finer metal1/metal2 etc., small dielectric thickness and higher operating frequency (a few GHz), the interconnect can no longer be modeled as a lumped circuit and becomes a critical factor in large highspeed system design [2][3].

The electrical high performance constraints of an electronic system are the system working frequency (i.e. system bandwidth, settling time or clock frequency), signal

Sent tes - an

integrity and noise level. For a given architecture, the system must be designed to run at a maximum operating frequency correctly and reliably. To maximize operating frequency, the delay in critical paths, i.e. the paths with maximum delay, should be minimized. The system reliability is limited by the system noise level. Electrical noise may induce inadvertent logic transition, i.e. errors in the system. To achieve high performance, both maximum operating frequency and acceptable noise level are the most important issues in the design exclusive of process yield.

In an electronic system, total delay is the sum of various delays in the system. Delays caused by devices and interconnections are the two dominant factors. Device delays are reduced by improvements in fabrication technology. Since the fabrication technology has made significant advances in recent years, interconnect delays are becoming the dominant problem replacing gate delay. Interconnect capacitance can become larger than gate capacitance hence determining the overview speed performance of the system. This large capacitance also increases power consumption and noise. For a properly designed interconnect, delay is totally determined by the conductor material and the line geometry.

Circuit density is the maximum number of electronic elements that can be contained in a chip or MCMs [1][2]. It is determined by the wiring capacity. Wiring capacity is affected by several factors, one of which is wiring density. Wiring density is a function of minimum line width, line separation and via size. The characteristic length of a line with minimum line width, separation and via size is specified by electrical effects. Too high a density can result in unexpected noise. If an interconnect is not properly designed, signal reflects and shape degrades significantly. In addition, two parallel signal lines must be separated by a specific minimum spacing to avoid excessive crosstalk noise.

In high-speed digital design, in contrast to low frequency design, the parasitic circuit elements of an interconnect, such as resistance, capacitance and inductance can not be neglected. These design issues are focused on the behavior of passive circuit elements, such as the wires, circuit boards and integrated-circuit packages. At low frequency, the effects of passive elements are typically neglected as just parts of a product's packaging. However, in high frequency application, they play a direct and important rule in electrical performance [2].

Interconnection has a greater and greater effect on system electrical performance. The proper interconnect (including packaging) design distributes to the achievement of high speed, high reliability and lower power dissipation in high speed and high-density applications. The effects of parasitic parameters of an interconnect line on signal propagation (ringing and reflection, etc.), interaction between signals (crosstalk) and other interference (simultaneous noise, etc.) has become very critical issues in designing valuable high speed system.

#### 1.1 Objective

The objective of this thesis is to develop a novel layout for large transistor based on triangle cell to mitigate the gate and source resistance limits on transistor performance. A set of general design guidelines and theoretical parameter and performance estimation equations are also developed for interconnects with long lengths or used in high speed applications (a few *GHz*) on MCMs and large *SOI/SOS* dies. This research is based on the investigation of interconnect parasitic parameters extraction, review of transmission line properties, signal delay analysis, crosstalk estimation, simultaneous noise calculation, termination resistance selection, proper driver design and novel layout realization. The simulation and layout-extracted results are also presented to support this proposal.

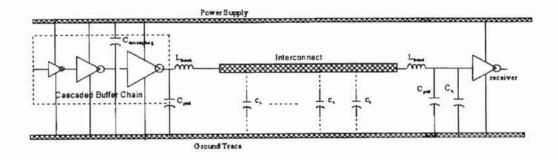

Figure 1.1 shows a simple interconnection diagram. The main parts include interconnection wires, loads, signal drivers and power supply. The design issues covered in this thesis are outlined as follows.

Fig. 1.1 A simple diagram of interconnection

- 1. Chapter 2. Extraction and calculation of electrical parasitic parameters of an interconnection.

- Chapter 3. Interconnection types, lossless, lossy and fully lossy transmission line; and the application of each.

- 3. Chapter 3. Maximum line length and proper signal risetime applied.

- 4. Chapter 3. How to achieve the optimal delay; Line geometry design (width, selection of characteristic impedance).

- 5. Chapter 4. Proper termination methods (parallel or series) and the optimal termination resistance.

- 6. Chapter 4. Proper driver size and fanout topology design

- 7. Chapter 4. Crosstalk reduction and effect of distribution parameters.

- 8. Chapter 4. More issues on line geometry design (line spacing and termination)

- Chapter 4. Controlling ground bounce, estimating decoupling capacitance and effect of distribution parameters.

- Chapter 5. Limitations in the design of transistor with large effective width. A novel transistor layout and its advantages.

#### **1.2 Organization**

Chapter 1 introduces the background and proposes for this study.

Chapter 2 reviews the extraction of parasitic parameters, i.e. self capacitance, inductance, resistance and characteristic impedance of an interconnect. The effect of substrate material, line width, substrate height and operating frequency is also discussed.

Chapter 3 discusses basic issues of a transmission line design, especially in optimal delay design. Three different types of transmission lines and their characteristics are discussed. A distributed Lumped *RLC* model is used for lossy transmission line simulation. Optimal delay design issues, including delay estimation, peripheral part effect, i.e. bond wire and pads, and parameter sensitivity to delay, are discussed and simulation results are presented. The signal loss for very long interconnects is also included in this chapter.

Chapter 4 analyzes the control of reflection, crosstalk and simultaneous noise. The proper driver size design is also covered along with the proper selection of a termination type and resistance value. In section 4.1, signal reflection and termination method is studied and simulation results are presented as verification. In section 4.2, proper driver size design is discussed. In section 4.3, a crosstalk estimation model is reviewed and the effect of a GND separation, termination results confirm the selected model. In the last section, a simultaneous noise model is presented along with analysis and verification through simulations. In conclusion, simple guidelines for proper termination, GND trace width design for reduction of crosstalk and higher trace density, decoupling capacitance selection and proper driver size design are given.

Chapter 5 presents a novel layout for large transistor based on the analysis of gate and source resistance limitations on transistor performance, specially cutoff frequency  $f_T$ , maximum frequency of oscillation  $f_{max}$  [4], thermal noise, gate delay, transconductance  $g_m$  and output conductance  $g_{ds}$ . The extracted results and comparison with a conventional finger structure are presented.

Chapter 6 summarizes the conclusion and recommendations. A test structure and general design flow diagram are presented.

### **CHAPTER 2**

## EXTRACTION OF R, L, C AND Z<sub>0</sub>

With the increase of circuit operating frequency and the advent of deep submicron technologies, the VLSI interconnects become one of the most important limiting factors in high-speed and high-density circuit performance. For system-level designs, such as large on-chip circuits or VLSI, multi-chip modules (MCMs) and printed circuit boards (PCBs), the interconnects can induce considerable delays and coupling noise due to transmission line effects. In general, the interconnect delay and coupled noise must be considered in the evaluation of total system performance.

To model the interconnect effects, the electrical parameters must be first extracted. The general description of the electrical parameters of an interconnect, assuming it is a transmission line, requires five electrical parameters: line capacitance, line inductance, line series resistance, line shunt conductance and line characteristic impedance [8][9]. In VLSI and MCMs applications, the shunt conductance can generally be neglected without losing generality. These parameters are determined by the interconnect geometry and play a very important role in the analysis of interconnect performance, such as generated noise and delay. The following parts of this chapter give out a general and relatively simple estimation of interconnect electrical parameters.

#### 2.1 Transmission Line

Interconnects in VLSI and MCMs applications can be represented by several different models. The RC and transmission line models are the two most frequently used models. In the RC model, only resistance and capacitance effects are considered, but in the transmission line model, the effect of line inductance is included. The RC model is normally adequate for lower clock frequencies and short interconnects giving fairly accurate results for those applications. However, if the interconnect is sufficiently long or the clock frequency is sufficiently fast, a transmission line model must be used since the RC model is no longer sufficient. In Chapter 3, the definition for a RC and transmission line model will be discussed in detail. In MCMs applications, interconnects are normally considered as transmission lines.

Figure 2.1 Cross-sections of typical transmission line Structure

Figure 2.1 presents the cross-sections of different transmission line structures which are used to model the different interconnects in different electrical applications. The wire above ground model (2.1a) can be used to represent a bond interconnect. Figure 2.1b is a coaxial model used for local area network or test probe connections. The on-chip interconnect is normally modeled as microstrip line (2.1c) and both microstrip and strip line (2.1d) are used in MCMs and PCBs. In recent years, the microstrip has been used extensively because it is easier to be fabricated and supplies a free and accessible surface for solid-state device. A strip line is more expensive than microstrip. In this thesis, all transmission lines are microstrips.

#### 2.2 Selection of Material for the Substrate

The selection of the substrate on which the die will be mounted is one of the considerations for MCMs application. In the following sections, it will be illustrated that some electrical parameters of interconnect like line capacitance  $C_{line}$  and characteristic impedance  $Z_0$  are dependent on the dielectric constant of substrate. Different choices of a substrate material result in different signal delays and losses. Reference [10] gives out the advantages and limitations of two commonly used substrate materials, organic and ceramic. In this part, The guideline of MCMs substrate selection is illustrated.

#### 2.2.1 Effective Dielectric Constant of Substrate

The relative dielectric constant is defined as  $\varepsilon_r = \varepsilon/\varepsilon_0$  ( $\varepsilon_0 = 8.854 \cdot 10^{-12} F/m$ ). The effective dielectric constant depends on the selected material, line width and substrate height. J. Howard gives out the following formula for effective  $\varepsilon_r$  as in (2.2.1) [2],

$$\varepsilon_{eff}(w_{eff}) = \frac{\varepsilon_r + 1}{2} + \frac{\varepsilon_r - 1}{2} \left[ \left( 1 + \frac{12 \cdot h}{w_{eff}} \right)^{-0.5} + 0.04 \cdot \left( 1 - \frac{w_{eff}}{h} \right)^2 \right]$$

(2.2.1)

$$w_{eff} = w + \frac{1.25 \cdot t}{\pi} \left( 1 + \ln \left( \frac{4 \cdot \pi \cdot w}{t} \right) \right)$$

(2.2.2)

where h is the height of substrate,  $w_{eff}$  is the effective width of signal microstrip, t is the thickness of signal microstrip and  $\varepsilon_r$  is dielectric constant of substrate material. Fig. 2.2 shows the typical cross-section of microstrip.

Dielectric constant has effect on signal delay and loss. More detail discussion will be given in Chap. 3. Normally, the dielectric loss can always be neglected in MCMs applications when maximum frequency is less than 10GHz [11][15]. But large magnetic loss should be considered for *Si* in high frequency application.

2.2.2 Selection of Material of Substrate[11]

- $\varepsilon_r$  should remain constant over the frequency and temperature range of interest.

- ε<sub>r</sub> often reduces slightly (~5%) as frequency increases from dc to high frequency. The value of ε<sub>r</sub> around 100M~10GHz should be used for simulating high-speed signal propagation, not the dc value.

- Dielectric resonance may exist at microwave frequency (>>10GHz), but is not general concern for MCMs applications.

- Low dissipation factor or loss tangent (tan  $\delta$ ).

- For Polymer dielectrics,  $\varepsilon_r$  increases with ambient humidity.

- High thermal conductivity.

- Low expansion in X-Y (substrate) plane.

- ε<sub>r</sub> should be as small as feasible. In this thesis, ε<sub>r</sub> =2.6 ~4.3 for MCMs; ε<sub>r</sub>=4.0 for SiO<sub>2</sub>; ε<sub>r</sub>=10.5 for sapphire.

## 2.3 Extract Self Capacitance and Inductance of Microstrip

Line capacitance and inductance are very important electrical parameters of interconnects. They determine the interconnection delay and coupling noise (mutual capacitance and inductance).

#### 2.3.1 Calculation of Self Capacitance and Inductance of Microstrip (pF/cm)

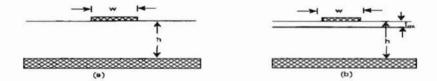

Figure 2.2 shows the cross-sections of microstrips fabricated on insulating substrate and oxide-passivated silicon substrate.

Fig. 2.2 Cross-sections of microstrips on insulating substrate (a) and oxide-passivated silicon

In the above figure, w is microstrip width, h is the substrate height  $(100\mu m \sim 250\mu m)$  for SOS and Bulk applications;  $10\mu m \sim 30\mu m$  for MCMs application [15]).  $t_{ox}$  is the oxide thickness (field oxide plus bulk oxide) for SOI  $(5000A^o \sim 10000A^o)$ . Under such conditions, the formulas suitable for calculating capacitance and inductance of an microstrip which can be derived from characteristic impedance of a microstrip transmission line have been studied previously by Scheider [12] and Hassegawa *et al.* [13]. These formulas are:

$$C = \frac{2\pi\varepsilon_{eff}\varepsilon_{0}}{\ln\left(\frac{8h}{w_{eff}} + \frac{w_{eff}}{4h}\right)} \qquad (2.3.1)$$

$$C = \varepsilon_{r}\varepsilon_{0}\left[\frac{w_{eff}}{t_{ox}} + 2.42 - 0.44\frac{t_{ox}}{w_{eff}} + \left(1 - \frac{t_{ox}}{w_{eff}}\right)^{6}\right] \qquad w_{eff} >> t_{ox} \qquad (2.3.2)$$

$$L = \frac{\mu_{0}}{2\pi}\ln\left(\frac{8h}{w_{eff}} + \frac{w_{eff}}{4h}\right) \qquad (2.3.3)$$

Equation (2.3.1) is used for a microstrip on an insulating substrate (SOS and MCMs) and (2.3.2) is used for a microstrip on an oxide-passivated silicon substrate (SOI). The same equation (2.3.3) can be used to estimate the inductance for a microstrip for SOS/SOI and MCMs with proper ground plane [14].

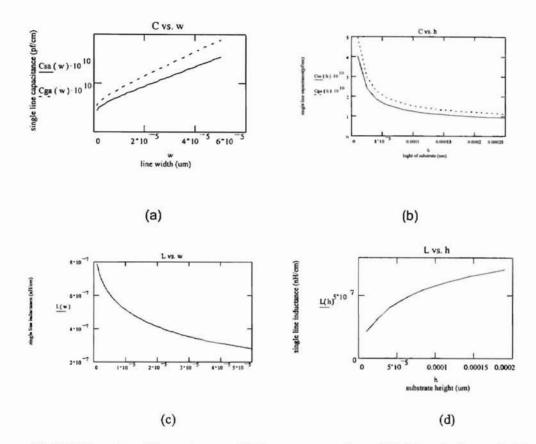

#### 2.3.2 Properties of Self Capacitance and Inductance of Microstrip

The plots in fig. 2.3 shows capacitance and inductance change versus line width and substrate height. The selected substrate materials are sapphire, gallium arsenide and oxide-passivated silicon. The height (h) used for calculation is  $25\mu m$  for MCMs and  $250\mu m$  for SOS.  $t_{ox}$  (6000A°) is used for SOI. Induced capacitance reduces quickly as the height of substrate increases for SOS and MCMs applications. To keep capacitance to a small value, larger substrate height and narrow line width are preferred. When line width is much smaller than the height of substrate, i.e. h/w>>3, the capacitance reduces slowly. This implies that the capacitance can't be reduced more when the thickness of substrate increases beyond h/w >> 3. For SOI, thicker isolating layer and narrower line induces smaller capacitance.

Fig 2.3 Microstrip self capacitance and inductance versus line width (w) and substrate height (h)

The inductance for SOS and MCMs reduces as the width of the transmission line increases. To keep the inductance small, wider lines are preferred. However this will increase the capacitance and results in decreased wiring capacity. The inductance for SOI wiring increases as line width increases and substrate height decreases  $(L \propto \ln(w/4h))$ . A narrow line has both a smaller capacitance and inductance for a SOI system. In high-speed application, the reduction of inductance is a very important issue. The proper selection of line width is determined by which parameter, capacitance or inductance, is dominant in system performance.

Besides the self-capacitance and inductance, there is also mutual capacitance and inductance between two or more adjacent parallel transmission lines. We will discuss the model and resulting design method in the "crosstalk" section in Chapter 4.

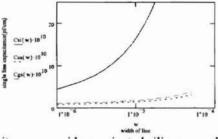

2.3.3 Compare the Self-capacitance on Insulating Substrate and on Oxide-passivated Silicon Substrate

Fig. 2.4 Self capacitance on oxide-passivated silicon, sapphire and GaAs

Figure 2.4 shows that the line capacitance increases as the line width increases on all three substrates. The interconnection made on an insulating substrate (Sapphire, GaAs) induces considerably small capacitance  $(0.5pF\sim5pF)$ . The capacitance on silicon substrate is larger than that on insulating substrate. However, this advantage diminishes at small line widths. The capacitances are scaled differently, being a logarithmic function on the insulator but a linear function of line width on the silicon substrate. The reason for larger capacitance on silicon is the thin oxide layer,  $t_{ox}$ , forming a large capacitor. For the purpose of capacitance estimation of on-chip interconnects, the thickness of field oxide (bulk) or thickness of field oxide plus buried oxide (*Simox*) should be used.

#### 2.4 Extract Self Resistance of Microstrip ( $\Omega$ /cm)

#### 2.4.1 Calculation of Sheet Resistance

The resistance of conductors in MCMs and large die SOI/SOS has a significant effect on signal integrity, delay and termination. At low frequency, the line resistance is its dc resistance and is given by equation (2.4.1), where  $\rho$  is conductor material resistance, t is line thickness,  $R_{sheet}$  is the sheet resistance of metal trace,  $R_{sheet} = \rho/t$ , d and  $w_{eff}$  are line length and width respectively.

$$R_{line} = \rho \frac{d}{w_{eff}t} = R_{sheet} \frac{d}{w_{eff}}$$

(2.4.1)

D.B. Tuckerman [15] points out the following issues should be noted in MCMs applications:

- Thin film resistivities are greater than bulk resistivities and depends on the grain size and impurities.

- Alloy resistivities are greater than pure metal resistivities.

- High temperature resistivities are greater than that at room temperature. For Al and Cu, it is normally 0.3%~0.4%/°C. This resistance increase can be significant at high temperature applications.

- Conductors often have a non-rectangular cross-section. To estimate resistance more accurately, more complex models should be used.

Line width and line thickness may vary from design value by up to 10% because of process factors.

#### 2.4.2 Skin Effect

At low frequencies, the current is distributed uniformly throughout the cross section of conductor through which it flows; however, at high frequency, the current distribution can be imagined as concentric tubes. The inner rings have more inductance than the fatter outer rings. The current follows the path with least inductance at high frequency, i.e. the current is concentrated on the surface of conductor. This is known as skin effect.

#### 2.4.2.1 Calculation of Resistance With Skin Effect

A constant called skin depth  $\delta_s$  is used to measure the skin effect. It is the distance at which current density becomes a fraction 1/e of its value at the surface. The skin depth  $\delta_s$  is expressed as (2.4.2). It is inversely proportional to the square root of frequency. Here, f is the operating frequency and  $\mu = 4\pi \times 10^{-7}$  Henrys/meter. For Al and Cu,  $\rho = 2 \sim 3\mu\Omega \cdot cm$  [15]

$$\delta_s = \sqrt{\frac{\rho}{\pi\mu f}} \tag{2.4.2}$$

So the effective resistance of transmission line with skin effect is

$$R = \rho \frac{d}{w_{eff} \delta_s} = \frac{d}{w_{eff}} \sqrt{\pi \mu f \rho}$$

(2.4.3)

For example, for a 3.3 $\mu$ m plated Cu trace,  $\rho = 2.8\mu\Omega \cdot cm$ , when f=1GHz,  $\delta_s = 2.6\mu$ m; when f=10GHz,  $\delta_s = 0.8\mu$ m and 25% larger for Al on die. As the signal frequency increases, skin depth becomes thinner resulting in increased line resistance.

Equations (2.4.1) and (2.4.3) shows that at low frequencies, a conductor has a constant dc resistance; while at high frequency, resistance grows proportional to the square root of frequency.

### 2.4.2.2 Cutoff Frequency

There is a cutoff frequency [2][15] for any interconnect with a specific thickness, at which the conductor thickness is equal to the skin depth. It is defined as (2.4.4). For every interconnect, the cutoff frequency,  $f_c$ , offers a criterion to determine if the skin effect can be ignored.

$$f_c = \frac{\rho}{\pi \mu t^2} \tag{2.4.4}$$

When  $f < f_c$ , skin effect can be ignored. The proper thickness of conductor is roughly equal the skin depth  $t \approx \delta_s$  or  $t \approx \sqrt{\rho/(\pi \mu f)}$  (equation 2.4.2) to achieve the maximum line length at the lowest resistance (see Section 3.2.1). Too thick a trace doesn't help to reduce resistance and increases material cost and signal distortion. The effect of skin effect on signal attenuation and selection of transmission line types is discussed in Chapter 3.

## 2.5 Computation of Characteristic Impedance Z<sub>0</sub>

2.5.1 Characteristic Impedance Z<sub>0</sub> of Transmission Line

Characteristic impedance  $Z_0$  is another basic parameter of transmission line. It is defined as

$$Z_0 = \sqrt{\frac{R + j\omega L}{G + j\omega C}} = \left(\frac{L}{C}\right)^{1/2} \sqrt{1 + \frac{R}{j\omega L}}$$

(2.5.1)

where R is the resistance per unit along the line

L is the per unit inductance along the line

G is the per unit conductance shunting the line

C is the per unit capacitance shunting the line

When  $R/j\omega L \ll 1$ , i.e.  $\omega \gg R/L$

$$Z_{0} \approx \sqrt{L/C} \tag{2.5.2}$$

The characteristic impedance at lower frequencies is not real or constant. It has a substantial capacitive component. A "50 $\Omega$  line" or "75 $\Omega$  line" is only a meaningful concept at sufficient high frequency.

The different transmission line structures, such as microstrip, stripline, coaxial line, etc., have different approximate equations for  $Z_0$  [2]. The microstrip  $Z_0$  is approximately given by

$$Z_{0} = \frac{60}{\sqrt{\varepsilon_{eff}}} \ln \left( \frac{8h}{w_{eff}} + \frac{w_{eff}}{4h} \right)$$

(2.5.3)

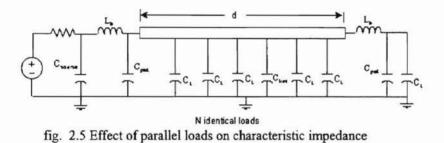

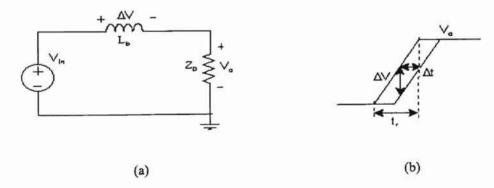

Parallel capacitive loads and peripheral parts, such as bond wire and input/output pads, change the value of characteristic impedance. In the case shown in figure 2.5, the effective  $Z_0$  is given by equation (2.5.4). Note, the non-transmission line parameters ( $L_b$ ,  $C_{pad}$ ,  $C_{source}$ ) should be comparable to the transmission line per unit L and C in this case.

$$Z_{eff} = \sqrt{\frac{L_{line} + 2L_b}{C_{source} + C_{line} + NC_L + 2C_{pad}}}$$

(2.5.4)

#### 2.5.2 A comparison of the microstrip characteristic impedance on different substrates

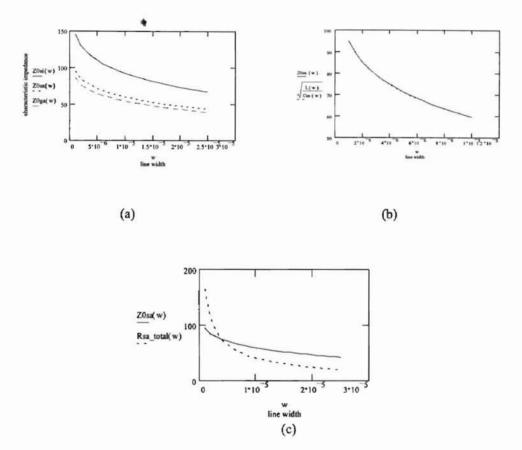

Figure 2.6 gives out some information of characteristic impedance  $(Z_0)$ . Microstrips with same geometry on different substrate have different  $Z_0$  (Plot (a)). Plot (b) compares two  $Z_0$  estimation models (equation (5.2.2) and (5.2.3)) and Plot (c) compares  $Z_0$  and line resistance and gives important information for  $Z_0$  selection.

• Plot (a) presents the change of  $Z_0$  on different substrates with the change of line width.  $Z_{0si}$ ,  $Z_{0sa}$  and  $Z_{0ga}$  are characteristic impedances of microstrips on Si, Sapphire and GaAs respectively. The plot implies  $Z_0$  reduces and the change becomes slower as the line width increases. A line built on sapphire has lower characteristic klahoma State University Library

impedance than that on a silicon substrate. To get a smaller  $Z_0$ , larger dielectric constant should be chosen.

A comparison of Z<sub>0</sub> estimation using equations (2.5.2) and (2.5.3) is shown in plot

(b). The equation (2.5.2) is simple and accurate enough and is also useful in line inductance estimation using TDR (See Chapter 3).

Fig. 2.6 Properties of Characteristic impedance

• From plot (c), when  $Z_0$  has a large value, the line resistance is very large. That implies higher resistive attenuation. The high  $Z_0$  (>100 $\Omega$ ) should be avoided in MCMs application due to high line resistance. But larger  $Z_0$  helps to achieve smaller driver size (smaller power dissipation but lower speed) (see section 3.2.1). So there is a tradeoff in the selection of the proper  $Z_0$  between signal loss and line length/driver design.

• Line resistance becomes smaller than  $Z_0$  as the width increases (plot (c)). An additional series resistance should then be added to achieve the optimal delay and termination,  $R_{total} \approx (1 \sim 3)Z_0$  (See section 3.2.6)

#### 2.6 Points of Design

| W(µm) | C(Pf/cm) | L(nH/cm) | $R(\Omega/cm)$ | $Z_0(\Omega)$ | $d_{min}(cm)$ | $d_{max}(cm)$ |

|-------|----------|----------|----------------|---------------|---------------|---------------|

| 28,83 | 2.233    | 3.568    | 3.29           | 40            | 1.216         | 11.4          |

| 16.85 | 1.749    | 4.36     | 5.08           | 50            | 0.98          | 10.1          |

| 3.915 | 1.128    | 6.336    | 13.91          | 75            | 0.54          | 6.1           |

| 0.707 | 0.828    | 8.273    | 36.77          | 100           | 0.272         | 3.3           |

Table 2.1a Example cal. parameter data of a lossy trans. line.  $(t = 5 \mu m$ , (with skin effect))

Table 2.1b  $t = 1 \mu m$  (without skin effect)

| W(µm) | C(Pf/cm) | L(nH/cm) | $R(\Omega/cm)$ | $Z_0(\Omega)$ | d <sub>min</sub> (cm) | d <sub>max</sub> (cm) |

|-------|----------|----------|----------------|---------------|-----------------------|-----------------------|

| 32.5  | 2.247    | 3.59     | 9.91           | 40            | 0.4                   | 3.8                   |

| 20.2  | 1.76     | 4.394    | 15.35          | 50            | 0.326                 | 3.3                   |

| 6.11  | 1.138    | 6.387    | 42.5           | 75            | 0.176                 | 2.0                   |

| 1.52  | 0.834    | 8.34     | 113.2          | 100           | 0.088                 | 1.1                   |

Table 2.1 gives out example calculation data of C, L, R and  $Z_0$  with  $h = 25 \mu m$  (MCMs), f = 1GHz ( $\delta_s = 2.6 \mu m$ ). Concluding the analysis above, the following design highlights are most important consideration for R, L, C and  $Z_0$  extraction. The line geometry, signal frequency and material of conductor and substrate determine interconnect parameters.

- Use verified physical data for the technology in the intended design

- Dielectric constant ε<sub>r</sub>

- Conductor sheet resistance

- Layer thickness (h) and conductor line width (w)

- Intended characteristic impedance (Z<sub>0</sub>)

- Interested operating frequency

- Thickness of metal trace t has no influence on L, C.

- Line capacitance increases but inductance decreases as the line width increases or substrate height decreases for MCMs and SOS.

- The design of line width and substrate height is determined by either the self capacitance or inductance, which is dominant in system performance. Factors considered include signal delay, integrity and coupling noise

- If the maximum line length is desired, the thickness of metal trace should be set to the skin depth t = δ<sub>s</sub>(f). Too thick a metal trace is not helpful in improving the performance of a transmission line. If t > δ<sub>s</sub>(f), extraneous material is wasted; if t < δ<sub>s</sub>(f), higher resistance will be resulted. Under the satisfaction of signal delay (risetime) and loss requirements, the thickness of line is preferred to be thinner with a maximum value δ<sub>s</sub>(f).

- If thickness t is less than skin depth, the resistance of trace will increase. This characteristic helps to design short lossy transmission lines, for example, an on-chip transmission line.

- Too high a characteristic impedance should be avoided because of larger line resistance. The most popular used values of Z<sub>0</sub> are 50Ω (75Ω) or less (30Ω~100Ω). The parallel loads may reduce the effective value of Z<sub>0</sub>.

Oklahoma State University Library

## **CHAPTER 3**

#### DESIGN OF TRANSMISSION LINES

As the signal frequency and circuit density increase, the performance of interconnect becomes increasing significant. In an electronic system, interconnects include: on-chip wires, wires on the MCM substrates, wires on PCBs, the package pins, lead frames, bonding wires and solder bumps, etc. Their electrical performance varies widely and depends on the lengths and cross-sections of interconnects and operating frequencies. The most popular used models are the *RC* and transmission line models.

As mentioned in part 2.1, the transmission line model is used for high frequencies and long interconnects. In this model, interconnect inductance has been considered. N. Sherwani and Q. Yu [1] offer a simple merit to determine whether the *RC* or transmission line model should be used for given geometry. In brief, when the signal risetime,  $t_r$ , is much less than signal time-of-flight,  $t_f$ , i.e.,  $t_r < 2.5t_f$ , a transmission line model should be used. On the other hand, when  $t_r$  is much larger than  $t_f$ , i.e.,  $t_r > 5t_f$ , lumped *RC* model is sufficient. When  $t_r$  is between 2.5 $t_f$  and 5 $t_f$ , either model will suffice.  $t_f$  is the time-of-flight of the signal and is given by:

$$t_f = \frac{d}{v} \qquad \qquad v = \frac{c_0}{\sqrt{\varepsilon_r \mu_r}} = \frac{c_0}{\sqrt{\varepsilon_r}} \tag{3.1}$$

where  $c_0$  is speed of light in vacuum  $(3 \cdot 10^8 m/s)$ ;  $\varepsilon_r$  and  $\mu_r$  are the relative permittivity and permeability of propagation medium.  $\mu_r$  is approximately 1 for nonmagnetic material. Oklahoma State University Library

For MCMs applications, interconnects are typically modeled as transmission lines due to short risetime and long lengths. In figure 2.1, four typical transmission line crosssections were presented. Compared to ordinary point-to-point wiring, a transmission line has less signal distortion, less radiation and less crosstalk due to the reduction of line inductance and the short distance to the ground plane [2].

#### 3.1 Lossless, Lossy and Fully Lossy Transmission Line

An ideal transmission line consists of two perfect conductors. There are: balanced (twisted pair) and unbalanced (coax, microstrip and stripline) transmission lines. An unbalanced transmission line is also called a single-ended line. In this type of transmission line, signal current flows through one signal trace and returns back along the ground trace. The ground trace is usually wider than signal trace and can be shared among many signal traces [2].

Every transmission line goes through lossless  $(LC) \rightarrow \text{lossy}(RLC) \rightarrow \text{fully lossy}$ (distributed RC) transition as operating frequency or length increases. The key factor is the total line resistance  $(R_{line})$ . The ratio of  $Z_0 = \sqrt{L/C}$  ( $\Omega$ ) to line resistance per unit R ( $\Omega/cm$ ) determines the critical useful length.

# 3.1.1 Definition of Lossless, Lossy and Fully Lossy Transmission Line

Recall the formula (2.5.1), if the conductance G is ignored, the transmission line characteristic impedance is a function of frequency.

$$Z_{0} = \sqrt{\frac{R + j\omega L}{j\omega C}} = \left(\frac{L}{C}\right)^{\frac{1}{2}} + \left(1 + \frac{R}{j\omega L}\right)$$

(3.1.1)

The following Table gives out a definition of the three type transmission lines

Table 3.1 Definition of lossless, lossy and fully lossy transmission line

| types       | Definition(I)                                                         | Definition(II)          |

|-------------|-----------------------------------------------------------------------|-------------------------|

| Lossless    | $\frac{R}{\omega L} << 1  \text{or}  \omega >> \frac{R}{L}$           | $R_{total} \ll Z_0$     |

| Lossy       | $\frac{R}{\omega L} \approx 1  \text{or}  \omega \approx \frac{R}{L}$ | $R_{total} \approx Z_0$ |

| Fully lossy | $\frac{R}{\omega L} >> 1$ or $\omega << \frac{R}{L}$                  | $R_{total} >> Z_0$      |

The critical length of each transmission line type is given by:

$$d = K \sqrt{L/C} / R \tag{3.1.2}$$

where L, C and R are the inductance, capacitance and resistance per unit of a transmission line. For lossless line,  $K \le 0.1$ ; for lossy line,  $0.1 \le K \le 2$ ; and for fully lossy line,  $K \ge 2$ . The critical length increases from lossless to lossy and fully lossy. The skin effect in high frequency applications will reduce the critical length [15].

For example, if  $R = 10\Omega/cm$  (recall table 2.1) and  $Z_0 = 50\Omega$ , when  $d \le 0.5cm$ ;  $0.5cm \le d \le 10cm$  and  $d \ge 10cm$ , we have lossless, lossy and fully lossy transmission lines respectively.

# 3.1.2 Characteristics of Three Types of Transmission Line

Normally, the interconnects, such as wires on the PCB, package pins, lead frames, bonding wires and solder bumps, all have low resistance due to their large cross-sections.

Oklahoma State University Library

As a result, these interconnects can frequently be treated as lossless transmission lines or inductors.

For MCMs wiring, because of their small dimension and long length, the resistance is usually significant and they are treated as lossy transmission line. This case will be more common for large die on-chip interconnects in the future.

A brief description of the properties of lossless, lossy and fully lossy transmission line is presented as follows [15]:

a. lossless transmission line

- R is neglected and  $Z_0$  is a real constant in the frequency of interest.  $Z_0 = \sqrt{L/C}$

- No energy loss occurs in the line.

- Propagation delay is linear with length and the signal propagation speed is given by formula (3.1).

- The signal is undistorted along the line but should be terminated.

- b. lossy transmission line

- R, L and C can not be ignored and  $Z_0$  is complex and frequency dependent. In most cases,  $Z_0 \approx \sqrt{L/C}$ .

- Significant energy loss exists in line and series termination or nontermination is useful because of significant line resistance (DC losses) (more discussion in section 4.1)

- Signal delay ranges from linear to quadratic

- Signal is somewhat distorted

- c. fully loss transmission line

Oklahoma State University Library

- L is neglected. Z<sub>0</sub> is complex, frequency dependent and is not an useful concept at any frequency.

- High line energy dissipation and no signal reflections.

- Signal propagation is proportional to RC, and quadratic with length.  $\tau \sim RC \sim length^2$ .

If there are multiple loads along the line, attempts should be made to use a lossless transmission line since the signal has no distortion and only delay at different points along the line. Use of a lossy transmission line can be difficult for multiple loads due to the signal distortion. If there is only one load on the end, both lossless and lossy transmission line can be applied. When a lossy transmission line must be applied to connect multiple loads, parallel fanout is preferred.

The selection of transmission line type for an application depends on loading, operating frequency and line length. For long interconnects on large single die or MCMs, they are usually lossy transmission lines. The resistance  $R_{line}$  is limited by

$$0.1 \left(\frac{L}{C}\right)^{1/2} \le R_{line} \le 2 \left(\frac{L}{C}\right)^{1/2}$$

(3.1.3)

#### 3.2 Optimal Delay Design of a Transmission Line

All electrical devices from basic gates to large chips have their specific delay. The cumulative effects of inductance and capacitance result this delay. The gate delay reduces faster due to the scaled down device geometry and the interconnect delay becomes one of the most important limiting factors in today's high-speed and highdensity circuit performances. As a result, it is vital to minimize interconnect delay to achieve the highest performance. The interconnect delay is determined by many factors, such as line length, conductor geometry and material, etc. In this section, the design of optimal delay will be discussed.

#### 3.2.1 First Incidence Voltage

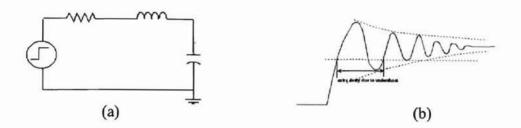

Assuming a unit step signal is applied in the input end of a transmission line, the response of this line at a distance x from the input end is consisted of two parts: the fast rising portion,  $V_A$ , and the slow rising portion,  $V_R$ .  $V_A = e^{-\alpha x}$  is an attenuated function exponentially dependent on attenuation constant  $\alpha$  and the distance x;  $V_R$  represents a *RC*-like behavior [1][16].

To achieve minimum propagation delay on a transmission line, the fast rising portion,  $V_A$ , must have sufficient amplitude. In another words, the first signal (first incidence voltage) to arrive at the end of the line must have sufficient voltage to switch the receiver, e.g. its value should exceed  $V_{IH}$  on  $1 \rightarrow 0$  transition or  $V_{IL}$  on a  $0 \rightarrow 1$ transition.  $V_{IH}$  is minimum voltage that is required to be input of receiving device for a logic 1;  $V_{IL}$  is the maximum voltage that is applied to the input of a receiving device for logic 0. This situation is referred to as first incidence switching [16].

The first incidence voltage at the receiving end is given by

$$\frac{V_{first}}{V_{in}} = \frac{Z_0}{R_{out} + Z_0} \cdot e^{\left(-\frac{Rd}{2Z_0}\right)}$$

(3.2.1)

$$d_{\max} = \frac{-2Z_0}{R} \ln \left( \frac{0.5 \cdot (Z_0 + R_{out})}{Z_0} \right)$$

(3.2.2)

where  $V_{in}$  is the open circuit output of driver, R is the per unit resistance of transmission line, d is transmission line length and  $d_{max}$  is the maximum length for fixed driver size, characteristic impedance  $Z_0$ . When  $Z_0 >> R_{out}$  and  $V_{in}$  equals  $V_{dd}/2$ :

$$d_{\max} \approx 1.38 Z_0 / R \tag{3.2.3}$$

To get enough first-incidence-switch value  $V_{first}$ , the resistance *R* should be small and  $Z_0$  should be significantly greater than driver output impedance  $R_{out}$ . Because  $Z_0$  of a transmission line will always be chosen between  $(30\Omega \sim 100\Omega)$ , the output impedance of a CMOS driver is designed around  $(5\Omega \sim 20\Omega)$ . If  $Z_0$  is selected too small, a large width driver is required to achieve small output impedance. Too a large driver width results in higher power dissipation and device performance limitations due to the increased gate  $(R_g)$  and source resistance  $(R_s)$  (see Chapter 5). If  $Z_0$  is too large, line resistance will be large (see section 2.5.2). This may in turn create problems in meeting the signal risetime and loss requirements resulting longer line unavailable The selection of  $Z_0$  should be a tradeoff between signal speed/loss and driver size/power consumption.

#### 3.2.2 Lumped RLC Model for A Lossy Transmission Line

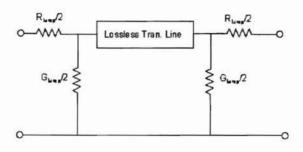

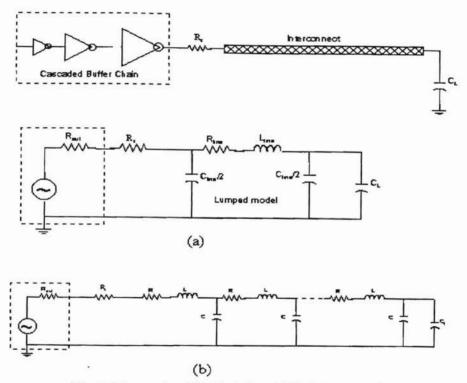

As mentioned in the beginning of this chapter, the *RC* and transmission line models are the two most popular models being used to describe the properties of interconnects. A lossy transmission line can be modeled and simulated as a series lumped *RLC* segments using lossless transmission line sections separated by lumped resistance and conductance. Figure 3.1 presents the structure of this basic segment [17]. Oklahoma State University Library

The characteristic impedance  $(Z_0 = \sqrt{L/C})$  and lossless transmission line delay  $(\tau = d_s \cdot \sqrt{LC})$  for each segment are the same and the segment delay is the total delay divided by the number of segments.  $d_s$  is the line length of each segment.

Fig.3.1 The basic lumped RLC segment for a lossy transmission line

The only consideration in basic segment design is the number of segments should offer a fine enough granularity such that for each lumped segment, the propagation delay is much smaller than signal risetime. In another words, the *RLC* lumped segment's propagation delay  $d_s(LC)^{1/2}$  should be a small fraction  $\beta$  of the risetime. The quantity  $\beta$  can be thought as the electrical "length" of each lumped segment ( $\beta = \frac{1}{3} \sim \frac{1}{10}$ ).

$$d_s (LC)^{1/2} / t_r = \beta, \qquad (\beta = \frac{1}{3} \sim \frac{1}{10})$$

(3.2.4)

Assuming  $\beta = 1/10$ , the number of lumped sections, N, is given by:

$$N \ge 10 \frac{d\sqrt{LC}}{t_r} \tag{3.2.5}$$

where d is total transmission line length; L and C are line inductance and capacitance per unit respectively. The lumped capacitance, inductance and resistance are given by:

$$R_{lump} = \frac{R \cdot d}{N} \tag{3.2.6}$$

Oklahoma State University Library

$$L_{lump} = \frac{L \cdot d}{N} \tag{3.2.7}$$

$$C_{lump} = \frac{C \cdot d}{N} \tag{3.2.8}$$

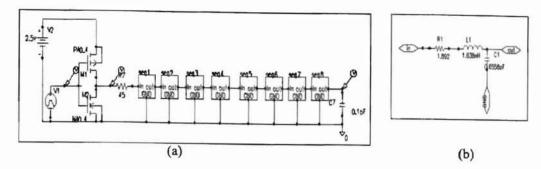

For example, assuming a lossy transmission line with  $Z_0=50\Omega$ , d=3cm, C=1.76pF/cm, L=4.394nH/cm,  $R=15.35\Omega/cm$  (Table 2.1) and signal risetime  $t_r=350ps$ . with number of segments, N, equal 8 then  $C_{lump}=0.66pF$ ,  $L_{lump}=1.648nH$ , and  $R_{lump}=5.76\Omega$ .

This series lumped segment model of a lossy transmission line can be used in PSPICE for transmission line simulation. The input should be "filtered" (i.e. using an inverter) to avoid introducing unphysically high frequencies, which may excite resonance of the individual lumped segment.

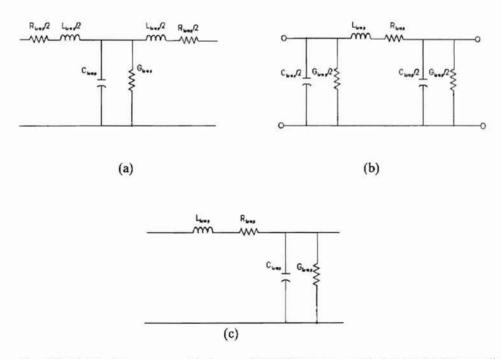

Fig. 3.2 (a) "Tee" type symmetric lumps; (b) "Pi" type symmetric lumps; (c) "Gamma" type lumps;

Figure 3.2 gives out other three types but equivalent segments used for simulation where G is always neglected. In this thesis, a "Gamma" type lumped segment is used and recommended to reduce network size.

# 3.2.3 The Delay Estimation for A Transmission Line

101

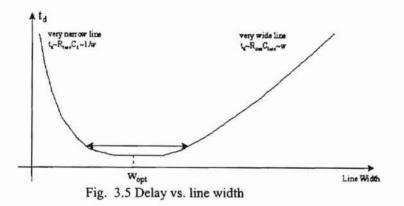

The extraction formulas for capacitance, inductance and resistance of a lossy transmission line were illustrated in Chapter 2. It is known the line capacitance, inductance and resistance are functions of the line width w. Roughly the following equations are held:

| $R(w) \propto f_1(w)$    | (3.2.9) |   |

|--------------------------|---------|---|

| $\Lambda(w) \sim f_1(w)$ | (3.2.9  | , |

$$C(w) \propto f_2(w) \tag{3.2.10}$$

$$L(w) \propto f_3(w) \tag{3.2.11}$$

Figure 3.3 presents an interconnect driven by cascaded buffer chain (a) lumped model; (b) distributed model (series *RLC* model).

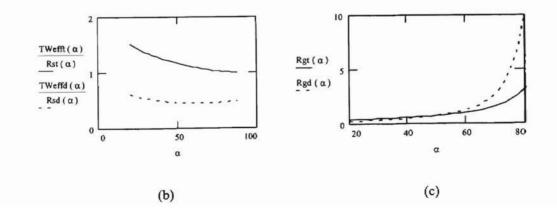

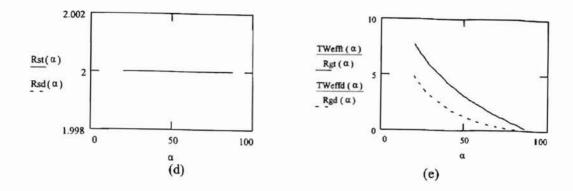

It is well known that the cascaded buffer chain with increasing width ratio,  $\alpha$ , offers the minimum delay and it is easy to show  $\alpha = e(2.718)$  for ideal case. Practically  $\alpha$  always varies from 2.5~5 depending on the process.