## OPTIMIZING FIR FILTER COEFFICIENTS USING CSD REPRESENTATION AND DM TECHNIQUE

Ву

WEN FUNG LEONG

Bachelor of Science Oklahoma State University Stillwater, Oklahoma 2000

Submitted to the Faculty of the Graduate College of the Oklahoma State University In partial fulfillment of The requirements for The Degree of MASTER OF SCIENCE May, 2002

# OPTIMIZING FIR FILTER COEFFICIENTS USING CSD REPRESENTATION AND DM TECHNIQUE

Thesis Approved:

Thesis Adviser

Dean of Graduate College

### **Preface**

Hardware saving criteria is one of the research fields in digital signal processing. Particularly on hardware saving in digital filter designs, which are due to the usefulness of digital filters in various fields especially in engineering fields. The main advantages in hardware savings are reduce hardware complexity and reduce the usage of hardware resources. One particular interest is to write a CAD program that can optimize the require hardware for the filter design. Many researchers have developed various CAD software programs for digital filter design with hardware realization capability. Some of the researchers include the hardware reduction as the main theme of the CAD program.

This whole thesis is related to the second-generation public domain CAD program and the main priority is to generate a set of FIR filter coefficients that requires little hardware. The program is to allow users to design any transpose direct form linear phase FIR filter with the least hardware needed and to be user friendly. However, the main direction of this thesis is to discuss the techniques and algorithms that are incorporated into the program with the main goal of meeting the filter specifications configured by the user. One of the sections discusses the implementation of Canonical Signed Digit (CSD) representation to the filter coefficients. The CSD coefficients are further optimized by the three optimization algorithms, which contribute in more hardware savings for the filter.

Another section introduces another representation technique that provides better results compared to CSD representation. This technique is called as the Dempster and Macleod (DM) technique. The Signal Noise Ratio is also included to determine the structural adder or delay size of the filter. The thesis also covers the details of the CAD programs such as the instructions to use the program and the block diagrams that construct the program.

## **Acknowledgements**

I sincerely thank my research advisor Professor Michael A. Soderstrand, who provide the advice, patience and support through my master program. Under his guidance, I have not only learned a lot from him but also learn to understand the basics of DSP, which I had studied during my undergraduate program. I also acknowledge Professors Louis G. Johnson and Keith A. Teach for reviewing my thesis and serving as my thesis committee. I thank all my Digital Signal Processing and Communications (DSPC) research colleagues for being cooperative and provide a friendly environment for our lab. In addition, I thank all the faculties and staffs from Electrical and Computer Engineering Department of Oklahoma State University. My special thank to Professors H. Jack Allison and Gary G. Yen who not only help me a lot while pursuing my master degree but for their inspiration, support and encouragement. I express my deepest gratitude to my family for their love, encouragement, support and patience. Moreover, I express my appreciation to my parents who have supported and provided me the opportunity to study in Oklahoma State University. Finally, a particular thanks to Professor Joan Barrick for proofread the thesis.

## **Table of Contents**

| 1. In | troduction                                         | 1  |

|-------|----------------------------------------------------|----|

|       |                                                    |    |

| 1.1   | Introduction                                       |    |

| 1.2   | Objective                                          |    |

| 1.3   | Finite Impulse Response Filter (FIR)               | 3  |

| 1.4   | Fixed Point Representation                         | 5  |

| 1.5   | Thesis Outline                                     | 6  |

| 2. Ba | ackground                                          | 9  |

|       |                                                    |    |

| 2.1   | Other Filter Design Programs                       | 9  |

| 2.2   | Cost Definition                                    |    |

| 2.3   | Order-Wordlength Tradeoff                          |    |

| 2.4   | Scaling                                            |    |

| 2.5   | Adder Extraction                                   |    |

| 2.6   | Roundoff Error Analysis                            |    |

| 3. Co | ost Analysis of Binary, CSD and DM Implementation  | 15 |

|       |                                                    |    |

| 3.1   | Introduction                                       |    |

| 3.2   | Number Representations                             |    |

| 3.2   | .1 Binary Representation                           |    |

| 3.2   | 2 CSD Representation                               | 17 |

| 3.2   | DM Representation                                  | 18 |

| 3.3   | Cost Analysis of Binary, CSD and DM Representation | 19 |

| 4. CS   | D Optimization Techniques                                  | 27 |

|---------|------------------------------------------------------------|----|

| 4.1     | Introduction                                               | 27 |

| 4.2     |                                                            |    |

|         | 2.1 Procedure for Determining Optimum Order and Wordlength |    |

|         | 2.2 Function Introduction.                                 |    |

| 4.3     |                                                            |    |

| 4.      | 3.1 Theory                                                 |    |

| 4.      | 3.2 Procedure of Determining Minimum Order and Wordlength  |    |

| 4.      | 3.2 Function Introduction                                  | 37 |

| 4.4     | ******                                                     |    |

|         | 4.1 Procedure of Adder Extraction                          | 40 |

|         | 4.2 Function Introduction                                  |    |

| 4.5     | Example Result of Three Optimization Techniques            | 44 |

| 5. Der  | npster and Macleod Implementation                          | 47 |

| 5.1     | DM Optimization Introduction                               | 47 |

| 5.2     | DM Optimization Procedure                                  |    |

| 5.3     | Function Introduction.                                     |    |

| 5.4     | Implement DM technique after Optimization                  | 50 |

| 6. Sigi | nal to Noise Ratio                                         | 54 |

| 6.1     | Introduction and Approach                                  | 54 |

| 6.2     | SNR Computation                                            |    |

| 6.3     | Pseudocode For SNR Computation                             |    |

| 6.4     | Example Simulation Result                                  |    |

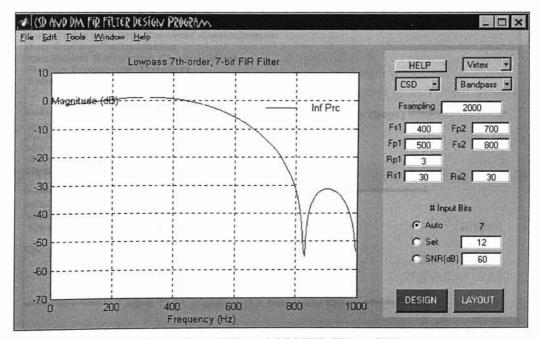

| 7. Pro  | gram Review                                                | 64 |

| 7.1     | GUI Overview                                               |    |

| 7.2     | Program Overview                                           | 67 |

| 7.3     | Technology and Cost Review                                 | 70 |

| 8. Cor | clusion and Future Work                                   | . 72 |

|--------|-----------------------------------------------------------|------|

| 8.1    | Conclusion                                                | 72   |

| 8.2    | Future Works                                              | 74   |

| BIBL   | IOGRAPHY                                                  | . 76 |

| Apper  | ndix A: Binary to CSD representation Conversion Algorithm | . 80 |

| Apper  | ndix B: CSD and DM FIR Filter Design Program              | . 82 |

| B.1    | Introductory Menu                                         | 82   |

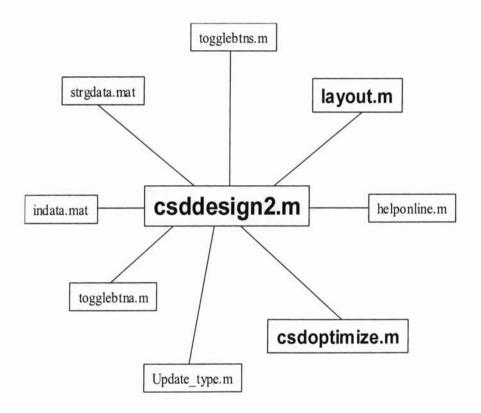

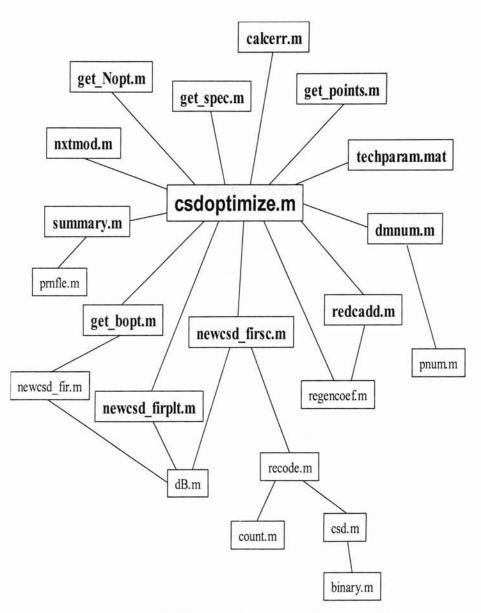

| B.2    | File Chart                                                |      |

## **List of Figures**

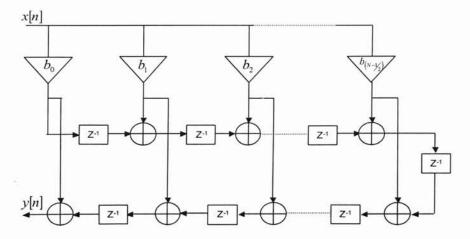

| Figure 1.1 | General Transpose Direct Form FIR filter                    | 5  |

|------------|-------------------------------------------------------------|----|

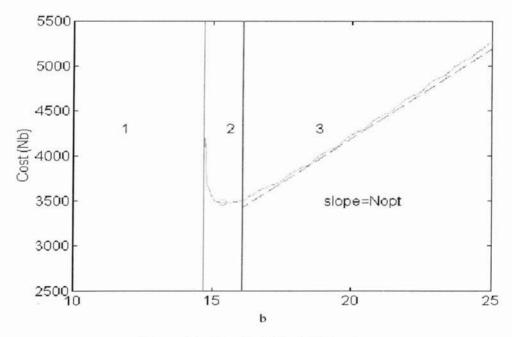

| Figure 2.1 | Graph of Cost (Nb) vs b                                     |    |

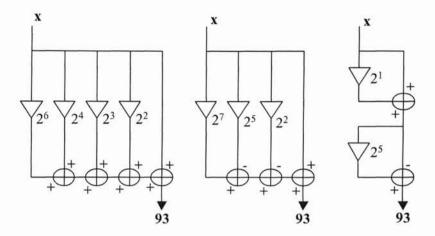

| Figure 3.1 | (a) Binary Implementation of Multiply by 93                 | 16 |

|            | (b) CSD Implementation of Multiply by 93                    | 16 |

|            | (c) DM Implementation Multiply by 93                        | 16 |

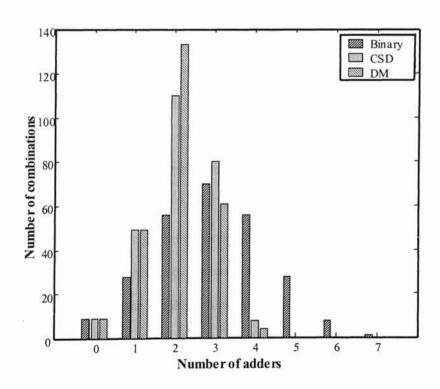

| Figure 3.2 | Histogram of Number of adders Vs Number of                  |    |

|            | Combinations for 8-bits wordlength                          | 21 |

| Figure 3.3 | Histogram of Number of adders Vs Number of                  |    |

|            | Combinations for 16-bits wordlength                         | 24 |

| Figure 3.4 | Plot of Average Adder for Coefficient Multipliers with      |    |

|            | Wordlength Range from 4 bits to 20 bits                     |    |

| Figure 4.1 | Optimum Order, Nopt Algorithm Block Diagram                 |    |

| Figure 4.2 | Optimum wordlength, Bopt Algorithm Block Diagram            | 33 |

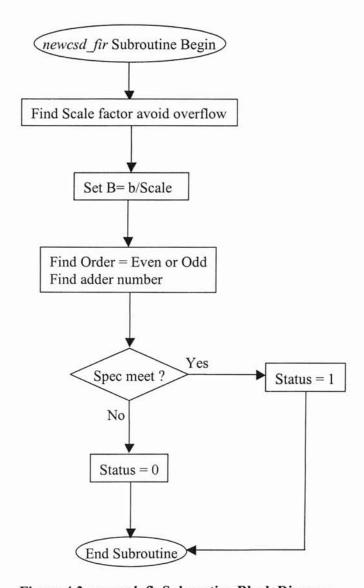

| Figure 4.3 | newcsd_fir Subroutine Block Diagram                         | 34 |

| Figure 4.4 | Scaling Algorithm Block Diagram                             |    |

| Figure 4.5 | newcsd_firsc Subroutine Algorithm Block Diagram             | 39 |

| Figure 4.6 | Adder Extraction Optimization General Routine Block Diagram | 42 |

| Figure 4.7 | Adder Extraction Algorithm Block Diagram                    | 43 |

| Figure 5.1 | DM Optimization Algorithm Block Diagram                     |    |

| Figure 6.1 | Transpose Direct Form FIR Filter with Noise Model           |    |

| Figure 6.2 | Pseudocode of SNR subroutine                                | 59 |

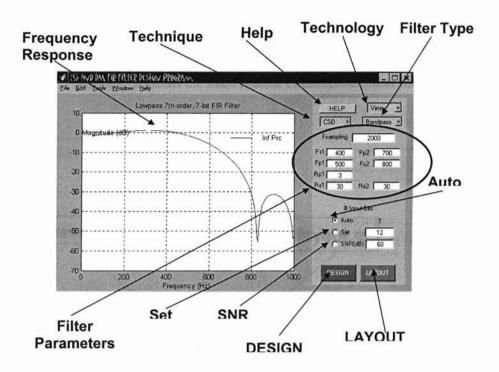

| Figure 7.1 | CSD and DM FIR Filter GUI                                   | 65 |

| Figure 7.2 | An Example Summary Box                                      |    |

| Figure 7.3 | Summary Data in Work Window Command.                        | 66 |

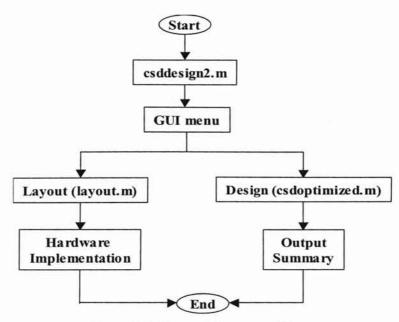

| Figure 7.4 | General Program Flow                                        |    |

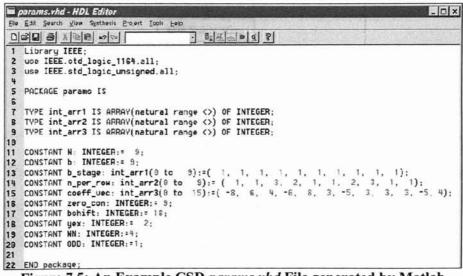

| Figure 7.5 | An Example CSD params.vhd File generated by Matlab          | 68 |

| Figure 7.6 | Program Flow Chart                                          |    |

| Figure B-1 | CSD and DM FIR filter design program.                       |    |

| Figure B-2 | Top Level of Program File                                   |    |

| Figure B-3 | File Chart for the Optimization Process                     | 85 |

## Section One

## Introduction

#### 1.1 Introduction

Digital Signal Processing (DSP) has grown widely during the past decades, due to the technological advancement in computers. DSP has revealed more advantages in terms of flexibility, cost reduction and performance compared to conventional analog signal processing. Additionally, its advantages also cover versatility and stability. In the industry, areas that require DSP applications such as medical applications, time series analysis, and communication areas use digital signal processors with specialized hardware, instructions and mathematical computations instructions for processing digital signal projects.

DSP operations usually have two basic categories, which are signal analysis and digital filtering. Implementation of new structures using digital filters is very popular due to the flexibility of various applications of digital filters such as noise elimination and frequency band separations. In general, a digital filter is a discrete time convolver since the output of the filter is actually the sum of the weighted previous input and output.

Therefore, a digital filter is actually formed by three basic hardware elements, which are adders, multipliers and registers.

There are numerous automated software programs available for engineers to design any type of filter with reduced hardware requirements and the ability to implement the design in different technologies. Designing a digital filter that has less hardware complexity is important because reduced complexity can contribute to a reduction in power, size and cost while increasing speed. The main contribution to complexity for digital filtering is the coefficient multipliers, which are usually implemented using binary arithmetic. There are many ways to reduce hardware complexity that range from Hartley[10] numerical reduction method to direct building (Finite Impulse Response) FIR filter using components available in the hardware realization software such as KCM multipliers [20]. With new techniques implemented to improve the digital filter design with hardware reduction as a goal in mind, both Canonical Signed Digit (CSD), and Dempster and Macleod (DM) techniques appear very promising for filter design purposes.

#### 1.2 Objective

Previously, Husinga [1] developed an automated software program to design highpass and lowpass FIR filters by using the CSD technique to minimize hardware complexity. This Computer Aided Design Program is designed for linear phase transpose direct form Finite Impulse Response (FIR) filters with minimal hardware complexity. There are three optimization techniques that are used to obtain better results with the

CSD technique. The three techniques used are order-wordlength tradeoff, scaling and adder extraction. These are the three objectives in this thesis. Firstly, Husinga's work is revised, identifying some errors and limitations occurring during the optimization process. Then, the program is expanded by adding more features and selections. Finally, a new hardware saving technique based upon the Dempster and Macleod (DM) implementation [6-7] is introduced into the program. This program is aimed at automatically generating a hardware layout for different targeted technologies such as Xilinx FPGA's and MOSIS CMOS processes. This paper will not cover the automation of hardware layout. However, a script file called the *params.vhd* is mentioned since it is included in the GUI program as one of the functions. The program does offer choices for different targeted technologies that can be added in the future when needed.

#### 1.3 Finite Impulse Response Filter (FIR)

According to many textbooks and articles [1-2],[16-19], FIR filters are simple to design, flexible and there is no possibility of limit cycles. In addition, the reason that FIR filters are also stable is because it is guaranteed to be a bounded-input bounded-output (BIBO) system. Moreover, FIR filters with symmetrical characteristics will guarantee a linear phase frequency response as linear phase response produces constant amounts of delays, which make the design problem somewhat simpler. Therefore, the design of FIR filters is the focus for this thesis.

The transfer function of an FIR filter in the z-domain is

$$H(z) = \sum_{k=0}^{M-1} b[k] z^{-k}$$

(1.1)

Hence a general difference equation for causal FIR system is represented as

$$y[n] = \sum_{k=0}^{M-1} b[k]x[n-k]$$

(1.2)

This equation shows that if it is subjected to an impulse, the output will equal zero after the impulse has passed through all the summation. This operation is equivalent to convolution of input data samples with the desired unit impulse response of the filter, which is defined as Finite Impulse Response (FIR).

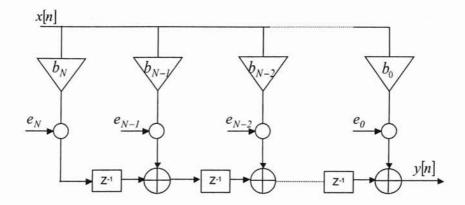

The transfer function from Equation (1.1) can be implemented using a variety of equivalent structures, which are equivalent in terms of transfer function but differ in hardware complexity. These structures, which are equivalent in terms of transfer function have different characteristics depending on quantization results due to finite wordlength limitation. Mitra [18] does mention a few equivalent FIR filter structures such as the direct form FIR filter structure, cascade form FIR filter structure, linear phase FIR structure and polyphase FIR structure. For this thesis, the linear phase form FIR filter is selected because of its wide applications. A characteristic of the linear phase form is that the coefficients are in symmetrical form and this can be exploited to reduce the number of filter coefficients by almost one half. In addition, the filter is selected for its transpose direct form because it supports the linear phase form FIR structure better in terms of hardware requirements for the filter coefficients. Transpose direct form also has a better timing characteristic since the input is directly connected to the filter coefficient

multiplication. Figure 1.1 shows an example of a general transpose direct form of a Norder linear phase FIR filter. However, there is a disadvantage of using transpose direct from, which is the size of the delay which must be a reasonable size to prevent quantization and this problem does not occur in direct form structure because all the delays are at the input bit size. In fact direct form structure will result in less hardware requirements compared to transpose direct form. In transpose direct from, half of the total number of adders are connected at the input bit size whereas the rest of the adders are connected at the output after the multipliers with the wordlength of input bit size plus the coefficients bit size. Another interesting point is if the sharing block in the CSD or DM realization is adapted to both the transpose direct form and direct form structures, the hardware requirement is much lower. Anyway, this thesis focuses on the transpose direct form FIR filters with no sharing block in CSD or DM realization, which is presented in Figure 1.1.

Figure 1.1 General Transpose Direct Form FIR filter

#### 1.4 Fixed-Point Representation

Fixed-point format is used to represent the coefficients since this format is flexible both in DSP processing and VLSI implementations. This is because the binary point is fixed at a certain location of a binary representation of a coefficient. We use this representation to represent fractional numbers. A general fixed-point format for the fractional number with a dynamic range of -1 to approximate 1 is shown below:

$$b_0 \bullet b_1 b_2 b_3 \cdots b_{Rit} \tag{1.3}$$

where '•' is the binary (radix) point.

According to Mitra [18], when the binary point is fixed, arithmetic operations are simpler to implement and the positive fixed-point number is easy to represent. In general, there are three formats to represent a fixed-point negative number. If we consider binary representation as the main basis to represent the fractions, the three formats are sign magnitude format, ones' complement format and twos' complement format. These formats do apply to signed radix-2 fixed-point numbers. Note that the binary point plays an important part in fixed-point representation.

#### 1.5 Thesis Outline

Section 2 reviews previous work and research areas that are related to this thesis and it will include an overview of the CAD design. Other main topics included are cost calculations and optimization techniques that reduce the hardware requirement.

The following section will discuss the cost analysis of Binary, Canonical Signed Digit (CSD) and Dempster and Macleod (DM) techniques. A simple explanation for these representations is to produce hardware savings. The simulated results are presented using the Matlab program for the ease of comparing each technique.

Section 4 describes and reviews the CSD optimization techniques that were implemented in this thesis taken from previous research work done by other authors. Basically it contains the procedure of all techniques with block diagrams and definition function, while integrating the algorithm step by step and translating them into block diagrams for future reference. The example results presented are also compared for robustness in difference techniques.

Section 5 will introduce the new method, Dempster and Macleod (DM) technique into the CAD as an added option for users and also to minimize hardware complexity. The DM optimized algorithm for this technique is also presented with a block diagram. When the filter coefficients are found, the coefficients will undergo optimization techniques and then they are implemented only with the DM technique. The reasoning behind this idea is discussed and example results from the Matlab program are presented.

Section 6 describes the computation of signal to noise ratio (SNR) in both cases. The first case is one in which the user does not specify a SNR requirement while the other case is to find the SNR value that meets the SNR requirement specified by the user. Both the procedures are discussed and a pseudocode and example results are included in this section.

Section 7 explains the routine of the CAD program. The features and block diagrams are provided to simplify the explanation. This chapter includes the introduction

of the program and the procedure to run the program. It also discusses the reason that the new cost function is introduced to the program.

The last section concludes this thesis based on the results discussed from the previous sections. Future work is also recommended to future researchers who are interested in improving the work done.

## Section 2

## **Background**

#### 2.1 Other Filter Design Programs

Many programs have been written to construct a constant coefficient FIR filter based on various user-defined parameters. For example, Matlab version 6-demo toolbox for signal processing has a program that allows the user to compute a FIR filter with many options. Intensive research into writing software programs that includes a hardware implementation option has also been done by other researchers in the past. Research done by Jain et al. [11] produced a FIRGEN program that automatically generated the architecture and floorplan for integrated circuit fixed point FIR filters that achieves a high sample rate with compact layout. Another example is the construction of a FIR filter using the graphical toolbox available in Simulink toolbox provided by Mathworks in Matlab version 6. The design is then translated into hardware programming language, which produces hardware in Register-Transfer-Level (RTL) in VHDL that maps into a FPGA using CAD tools. The paper written by Haldar et al. [12] uses this technique. The authors presented their MATCH compiler that takes the Matlab input and implements the digital filter design in a FPGA chip. While Husinga and Darren [1-2] wrote a Matlab

program which does takes certain technological specification into consideration. The results from the program can be implemented in Xilinx FPGA's or other targeted technologies.

#### 2.2 Cost Definition

Cost measurement is essential in order to evaluate the cost needed for a digital filter design while performing any optimization routines. Most papers define the cost based on the number of adders/subtractors and delay elements of a filter. Even so, cost function is not a unique function. In Dempster [8] the cost is defined as a cost equation for CSD representation, which is based on fewer adders needed for the multipliers compared to the binary representation. The Dempster cost equation is represented in the form of,

$$Cost = M \times A(w) + A + D + \alpha$$

(2.1)

where

M is the number of multipliers or coefficients; A(w) is the average number of adders expected from graph multiplier of wordlength, w; A is the number of structural adders; D is the number of structural delays and  $\alpha$  is the weighting factor, equivalent to the number of adders in a delay.

In previous work done by Husinga and Darren[1-2] the cost function is defined based on specific target technology. Therefore, different technology has a different fundamental unit size and this will result in a different cost value for the different technologies. Both Husinga and Darren estimated the cost using lookup tables, which

contain a list of fundamental cost units that represent a particular size of adders and delay elements of the specific targeted technology. The following shows the general cost function used by Husinga and Darren:

$$Cost = \alpha(w)A + \beta(w)D$$

(2.2)

Both the  $\alpha(w)$  and  $\beta(w)$  are technology dependent cost units of each adder and delay of wordlength, w. The A and D are the number of adders and delays. The cost function is just an estimated number to describe the hardware complexity. Cost function will vary within different filter structures, hence cost is generalized as a function evaluation to aid the optimization algorithms.

#### 2.3 Order- Wordlength Tradeoff

There are different ways to compute the minimum wordlength required for a digital filter. One approach is the use of the coefficients sensitivity function to compute the required wordlength for each coefficient. Debrunner [21] uses this technique for Infinite Impulse Response (IIR) filter design implementation. However, both Husinga and Daren use the order and wordlength tradeoff technique introduced by Kodek [9]. Kodek introduced the construction of a graph where the cost product of order and wordlength, Cost(Nb) versus the wordlength, b, is shown in Figure 2.1. Kodek found out that at a certain point there is an optimum point that optimizes both the order and the wordlength. The optimum point is referred to as a global minimum. He also noticed that, as the wordlength increases further than the optimum wordlength, the curve becomes a constant positive slope. On the other hand, when the wordlength decreases from

optimum wordlength towards zero, the wordlength will be too small to represent the filter coefficient. Therefore, the filter specification will not be met. By observing the characteristic of the graph, which is shown in Figure 2.1, Kodek drew some conclusions and derived an equation that can compute the minimum wordlength from minimum order. This method is very useful because when the order of the filter is increased without changing the filter specifications, it will result in the decrease of wordlength needed in the filter. This tradeoff provides the ability to find the best quantized coefficients that will reduce the hardware area such as the number of CLBs for Xilinx's FPGA's. Section 4 explains the algorithm used for this method and for future reference the notation N and b refer to order and wordlength respectively.

Figure 2.1: Graph of Cost (Nb) vs b

Source: D. L. Husinga, Digital of Optimized Filter Using CSD Coefficient Representation [1]. Master's Thesis, University of California, Davis, CA.1995.

#### 2.4 Scaling

Though scaling has been the oldest technique, it is still the best in DSP or hardware applications. The drawback of using fixed point arithmetic for every addition or subtraction operation in each stage of the filter is that overflows may occur. DSP textbooks [17-19] use the norm and bound conditions to describe the scaling equation. While Darren's [2] approach is by scaling both the numerator coefficients and denominator coefficients (for IIR filter only) separately, and Husinga [1] scales down the inverse sum of the coefficients since the filter design is FIR filter. In previous papers, there are several techniques such as using scale factor to reduce the number of nonzero digits suggested by Serna [14] and using minimum weight representation (MWR) approach by Yagyu [22], which modifies the filter coefficients with CSD representation by using a scale factor approach. Another advantage of using scaling is to find the coefficients with minimum hardware implementation cost. This thesis will use scaling introduced by Husinga to overcome overflow and reduce the hardware complexity. Section 4.3 explains the search method to find the optimum scale factor that will result in the minimum hardware requirement.

#### 2.5 Adder Extraction

The adder extraction technique was based on the work done by both Soderstrand and Serna [15]. In previous work, Darren, Hunsinga and Balasubramanian [1-3] used this method to further minimize the coefficients hardware requirement cost. The idea is to reduce the number of adders by replacing the non-zero digit with zero and

check for specifications response of the new filter to make sure that the specifications are still met; both Daren and Husinga included this technique in their programs.

#### 2.6 Roundoff Error Analysis

Rounding and truncation after multiplication is often needed since all devices only have finite wordlength. Roundoff error is modeled as noise, while roundoff error can be avoided in FIR filters by making sure that the wordlengths are sufficient to accommodate all mathematical operations. This leads to excessive hardware. Signal to Noise ratio (SNR) is evaluated to make sure that the filter has a decent output performance. Usually, for FIR filter the SNR is relatively large due to the zero feedback, which means that it is easier to maintain the precision of the FIR filter coefficients. Hartley's [10] method of calculating SNR is used because the coefficients are represented in CSD representation. Section 6 will explain the procedure for computing SNR using Hartley's method.

## Section 3

## Cost Analysis of Binary, CSD and DM Implementation

#### 3.1 Introduction

In digital signal processing theory, the coefficient multipliers are represented in the real number system with infinite precision. However, in order to implement these coefficients in the digital hardware, a digital number system with finite length coefficients that are compatible with the digital hardware is required. Since the ideal coefficients are expressed in infinite precision, the hardware implementation of the digital processing systems may not be able to represent the coefficients very precisely or accurately. There are various types of digital number representations and usually digital hardware, such as DSP chips and digital computers, use a form of the binary number system or representation. Therefore, in this thesis, the digital number system or representation will represent the coefficient multipliers of the FIR filter. Finally, the digital number representations play an important role in hardware reduction of the filter so Section 3.3 will demonstrate the hardware cost reduction using three different digital number representations.

#### 3.2 Number Representations

Figure 3.1: (a) Binary Implementation of Multiply by 93

- (b) CSD Implementation of Multiply by 93

- (c) DM Implementation Multiply by 93

#### 3.2.1 Binary Representation

The binary number system is mainly used in modern digital systems and is actually the combination of the digits {1,0}. In fact binary representation is favored by digital applications because it is simple to represent the inherent on or off nature of digital hardware. Fractional numbers can also be represented by radix-2 binary number system by using a binary point to separate the integer part and the fractional part. That is how binary representation can represent the coefficient multiplications of the filter. For example, taking a simple example of a multiplier with the value 93, it can be represented as

$$93 = 2^6 + 2^4 + 2^3 + 2^2 + 2^0 (3.1)$$

From this representation, the number 93 can be written as an eight bit wordlength, which is 01011101<sub>2</sub>. Figure 3.1(a) also shows the equivalent model of a multiplier of the value of 93 in a binary representation. Also note that there would be four elements multiplied by the power of two and four adders. Since the elements are just multiplied by the power of two, this represents shifts of number that can be accomplished by appropriate hardware wiring. Hence, multiplying by positive or negative integer powers of two does not require real hardware. In the case of Figure 3.1(a) the four adders are considered the real hardware while the multipliers are just hard wiring.

#### 3.2.2 CSD Representation

A "signed digit" (SD) number system has the combination of  $\{\bar{1}, 0, 1\}$ , where 1 represents a negative one. The signed digit number system is useful in designing high-speed arithmetic machines. Since this is a radix-2 number system with three possible digits (ternary), there are redundancies to represent a simple decimal number, which make SD representation not unique. However, by selecting the SD representation with the fewest non-zero bits from the list of redundant representations, we can minimize the hardware required to represent a binary number. Canonical signed digit is a unique representation of signed digit numbers such that there are no adjacent nonzero digits. CSD format has a maximum of  $\frac{(N+2)}{2}$  nonzero bits, which is roughly one half that of binary representation. Taking the same example as above, the CSD representation is

$$93 = 2^7 - 2^5 - 2^2 + 2^0 ag{3.2}$$

The implementation of multiplying by 93 is shown in Figure 3.1(b). Comparing this to the binary implementation, CSD only requires three adders or subtractors. Based on this example, there is a 25% hardware saving over binary implementation. In addition, using signed digit for fixed-point format will allowed negative fractions to be represented in fixed-point format. The algorithm (described by Hwang [5]) that converts binary representation of a constant number to canonical signed digit is presented in Appendix A.

#### 3.2.3 DM Representation

The Dempster and Macleod (DM) [6-7] technique is another technique to represent the multipliers in digital applications. The basic idea proposed by Dempster is a multiplier that is factorized into a set of prime numbers, where the constraint is that the coefficient must not be a prime number. To use the same example discussed previously, the factored numbers are 3 and 31, which now can be two module multipliers. Notice that the numbers are now prime numbers, therefore each factored number or module will be represented by a new number system, which is the best way is to represent the factored numbers in CSD representation. The following demonstrates that example in a mathematical form.

$$93 = 3 \times 31 = (2^{1} + 2^{0}) \times (2^{5} - 2^{0})$$

(3.3)

Figure 3.1(c) is the equivalent model of the Equation 3.3. The figure shows that the multiplier is connected in a cascading style, so for this example, only two adders or subtractors are required. In this case, there will be a 50% and 33% hardware savings over binary and CSD implementation respectively.

#### 3.3 Cost Analysis of Binary, CSD and DM Representation

Section 3.2 describes the three digital number representations with an example multiplier that results in the reduction of hardware complexity. As the wordlength represented by the multipliers becomes smaller, the chances of hardware savings by using Dempster and Macleod (DM) technique over CSD technique are reduced. Table 3.1 shows the average number of adders needed for all combinations with the positive dynamic range of four bits for each of the digital number representations mentioned in Section 3.2. In other words, for a four bit wordlength, there are 0 to 2<sup>4</sup>-1 combinations, which means there are combinations that range from 0 to 15. The phrase *number of combinations* represents the number of multipliers. These multipliers are also used to calculate the average number of adders by taking the sum of the adders for all the combinations and dividing by the total number of combinations. For Table 3.1, total number of combinations is 16.

|         | Number | Of Combi | Total Adders |        |        |        |

|---------|--------|----------|--------------|--------|--------|--------|

| Adder   | Binary | CSD      | DM           | Binary | CSD    | DM     |

| 0       | 5      | 5        | 5            | 0      | 0      | 0      |

| 1       | 6      | 9        | 9            | 6      | 9      | 9      |

| 2       | 4      | 2        | 2            | 8      | 4      | 4      |

| 3       | 1      | 0        | 0            | 3      | 0      | 0      |

| Total   | 16     | 16       | 16           | 17     | 13     | 13     |

| Average | 1      | 1        | 1            | 1.0625 | 0.8125 | 0.8125 |

Table 3.1 Average Number of Adders for 4-bit Number of Combinations

By examining Table 3.1, the *ADDER* column means the number of adders. The *Number of combinations* column gives the number of combinations while it is related to a specific number of adders by referring to the *ADDER* column. The *Total ADDERS* column displays the total number of adders of the required number of combinations. Observing the highlighted row of the table on the previous page, it can be seen that under the *Number of combinations* heading, there is only one combination for binary representation and zero combinations for both CSD and DM representations. Therefore, the total adders required are three for binary representation and zero for both CSD and DM representation. The average number of adders produced by CSD and DM representation is 0.8125. Nevertheless, both CSD and DM techniques show a 23.53% savings of adders required over binary representation. For large numbers, which are determined by their available wordlength, if they are represented in CSD representation, an additional bit is required. For example, the number '14' in a four bit word length is *1110*<sub>2</sub> in binary representation, but in CSD representation, it is represented as *100*10<sub>2</sub>.

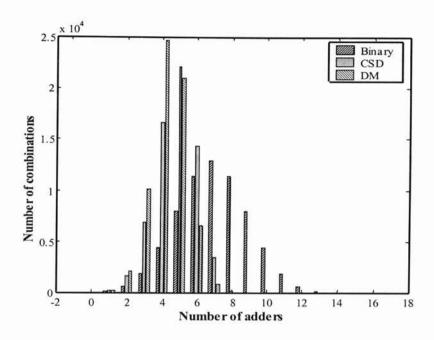

The earlier case shows the average numbers for DM and CSD is the same due to the fact that the wordlength is small. However with larger wordlength, the chances of hardware savings using DM technique over CSD technique are much higher. For discussion, observe Table 3.2 with eight bit dynamic range, which means that the numbers range from 0 to 2<sup>8</sup>-1. The average numbers of adders for Binary, CSD and DM representation are 3.0038, 2.1133 and 2.0078 respectively. The percentage savings for CSD and DM over Binary representations are 29.65% and 33.16% respectively.

|         | <b>Number Of Combinations</b> |     |     | Total Adders |        |        |

|---------|-------------------------------|-----|-----|--------------|--------|--------|

| Adders  | Binary                        | CSD | DM  | Binary       | CSD    | DM     |

| 0       | 9                             | 9   | 9   | 0            | 0      | 0      |

| 1       | 28                            | 49  | 49  | 28           | 49     | 49     |

| 2       | 56                            | 110 | 133 | 112          | 220    | 266    |

| 3       | 70                            | 80  | 61  | 210          | 240    | 183    |

| 4       | 56                            | 8   | 4   | 224          | 32     | 16     |

| 5       | 28                            | 0   | 0   | 140          | 0      | 0      |

| 6       | 8                             | 0   | 0   | 48           | 0      | 0      |

| 7       | 1                             | 0   | 0   | 7            | 0      | 0      |

| Total   | 256                           | 256 | 256 | 769          | 541    | 514    |

| Average | 1                             | 1   | 1   | 3.0039       | 2.1133 | 2.0078 |

Table 3.2 Average Number of Adders for 8-bit Number of Combinations

Figure 3.2: Histogram of Number of adders Vs Number of Combinations for 8-bit wordlength

The histogram presented in Figure 3.2 is based on the data from Table 3.2. The vertical axis represents the number of combinations that are required by the number of adders, while the horizontal axis represents the number of adders. From this histogram, notice that for the DM technique there are no combinations available starting from five adders onwards which is the same for CSD representation. When the number of adders is two, both CSD and DM technique achieve the highest number of combinations.

Another result is presented in Table 3.3 and the result is the average adder number for all the positive combinations of sixteen bit wordlength. The average number of adders for each combination is 7, 4.7778 and 4.3261 for binary, CSD and DM representations respectively. Hence, in this case, the percentage savings for CSD representation over binary representation is much higher, which is 31.45%. Similarly, the percentage savings for DM technique over Binary representation is 38.2%. The results show a higher savings for sixteen bit wordlength due to the number of combinations is significantly large compared to the case for eight bit wordlength. If taking the consideration of comparing DM technique over CSD representation, the percentage savings for eight bit and sixteen bit wordlength are 4.98% and 9.45% respectively. The savings is increased by approximately 5% between eight bit to sixteen bit wordlength. Relatively speaking, as the wordlength increases the percentage hardware savings will also increase. The histogram presented in Figure 3.3 is the graphical representation of the results from Table 3.3. By observing the histogram in Figure 3.3, the number of adders at the highest number of combinations for CSD representation is five while for DM technique, the number of adders where the highest number of combination is achieved is four. Also notice that for

both the CSD and DM representations, there are no more combinations left starting from nine adders onwards.

|         | Numbe  | r Of Comb | inations |        | <b>Total Adder</b> | s      |

|---------|--------|-----------|----------|--------|--------------------|--------|

| Adders  | Binary | CSD       | DM       | Binary | CSD                | DM     |

| 0       | 17     | 17        | 17       | 0      | 0                  | 0      |

| 1       | 120    | 225       | 225      | 120    | 225                | 225    |

| 2       | 560    | 1638      | 2133     | 1120   | 3276               | 4266   |

| 3       | 1820   | 6864      | 10140    | 5460   | 20592              | 30420  |

| 4       | 4368   | 16632     | 24631    | 17472  | 66528              | 98524  |

| 5       | 8008   | 22176     | 21072    | 40040  | 110880             | 105360 |

| 6       | 11440  | 14400     | 6522     | 68640  | 86400              | 39132  |

| 7       | 12870  | 3456      | 778      | 90090  | 24192              | 5446   |

| 8       | 11440  | 128       | 18       | 91520  | 1024               | 144    |

| 9       | 8008   | 0         | 0        | 72072  | 0                  | 0      |

| 10      | 4368   | 0         | 0        | 43680  | 0                  | 0      |

| 11      | 1820   | 0         | 0        | 20020  | 0                  | 0      |

| 12      | 560    | 0         | 0        | 6720   | 0                  | 0      |

| 13      | 120    | 0         | 0        | 1560   | 0                  | 0      |

| 14      | 16     | 0         | 0        | 224    | 0                  | 0      |

| 15      | 1      | 0         | 0        | 15     | 0                  | 0      |

| Total   | 65536  | 65536     | 65536    | 458753 | 313117             | 283517 |

| Average | 1      | 1         | 1        | 7      | 4.7778             | 4.3261 |

Table 3.3 Average Number of Adders for 16-bit Number of Combinations

Figure 3.3: Histogram of Number of adders Vs Number of Combinations for 16-bit Wordlength

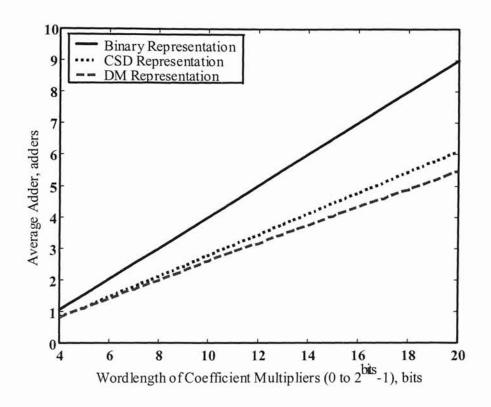

Table 3.4 shows the average adders for each combination for three different number representations from four bit to twenty bit wordlength. Basically, Table 3.4 is obtained by finding the average adder number for each combination for every wordlength, which ranges from four bits to twenty bits. Figure 3.4 is plotted based upon the data presented in Table 3.4. The plot illustrates the three different curves that explain the adders savings using the three different techniques described by the legend. Overall, the performances of DM and CSD representations are better than Binary representation. By comparing DM and CSD representation, DM representation shows a promising result in hardware reduction as the wordlength increases, but note that at wordlength from 4 bits to approximately 5.5 bits both CSD and DM implementation produce the same average

number of adders. By observing Figure 3.4, the slope computed for the binary, CSD and DM technique are 0.498, 0.333 and 0.29 respectively. The slope for binary representation is steeper than that for DM and CSD representation. Also note that the slope for CSD representation is steeper than that for DM representation. This pattern shows a distinct result that more adders are saved as the wordlength increases for both CSD and DM representation. By taking Figure 3.4 as a reference to obtain the average number of adder information, A(w), the cost function derived by Demspter shown in Section 2 can be put into full use.

| Wordlength | Average Adder Number for each Combination |        |        |  |  |  |

|------------|-------------------------------------------|--------|--------|--|--|--|

| Wordlength | Binary                                    | CSD    | DM     |  |  |  |

| 4          | 1.0625                                    | 0.8125 | 0.8125 |  |  |  |

| 5          | 1.5313                                    | 1.125  | 0.125  |  |  |  |

| 6          | 2.0156                                    | 1.4531 | 1.4188 |  |  |  |

| 7          | 2.5078                                    | 1.7813 | 1.7109 |  |  |  |

| 8          | 3.0039                                    | 2.1133 | 2.0078 |  |  |  |

| 9          | 3.5020                                    | 2.4453 | 2.3008 |  |  |  |

| 10         | 4.0010                                    | 2.7783 | 2.5986 |  |  |  |

| 11         | 4.5005                                    | 3.1113 | 2.8911 |  |  |  |

| 12         | 5.0002                                    | 3.4446 | 3.1785 |  |  |  |

| 13         | 5.5001                                    | 3.7778 | 3.4644 |  |  |  |

| 14         | 6.0000                                    | 4.1111 | 3.7525 |  |  |  |

| 15         | 6.5000                                    | 4.4445 | 4.0391 |  |  |  |

| 16         | 7.0000                                    | 4.7778 | 4.3261 |  |  |  |

| 17         | 7.5000                                    | 5.1111 | 4.6128 |  |  |  |

| 18         | 8.0000                                    | 5.4444 | 4.8999 |  |  |  |

| 19         | 8.5000                                    | 5.7778 | 5.1873 |  |  |  |

| 20         | 9.0000                                    | 6.1111 | 5.4751 |  |  |  |

Table 3.4: Average Adder Number for each Implementation

Figure 3.4: Plot of Average Adder for Coefficient Multipliers with Wordlength Range from 4-bits to 20-bits

## Section 4

## **CSD Optimization Techniques**

#### 4.1 Introduction

In previous work, Husinga [1] has demonstrated her ingenuity by incorporating the three optimization techniques to find a set of optimum coefficients represented in CSD representation. It is worthwhile to mention and revise all these techniques. Recall that the three optimization techniques are order-wordlength tradeoff, scaling and adder extraction. The purpose of optimization is to eliminate the adders' requirement of the filter coefficients. The restriction for each optimization process is that the specification of the FIR filter must be maintained. The following subsections describe the three optimization techniques and the results analysis which results in a reduction of adders.

#### 4.2 Order- Wordlength Tradeoff

Matlab program is used to determine the coefficients and the order of a FIR filter with required filter specifications. The coefficients are in infinite precision so in order to determine the optimum wordlength that represents the coefficients, the optimum order filter is computed. This optimum wordlength and order will be the guideline for the next

optimization technique, and it is the primary step of the three optimization process. This optimization technique is the implementation of Kodek's [9] idea discussed in Section 2. The idea is to determine an optimum filter order that meets the specifications with optimum wordlength to represent the filter coefficients. This will result in the minimized coefficients wordlength and consequently reduce hardware requirement.

### 4.2.1 Procedure for Determining Optimum Order and Wordlength

Remezord and Remez function available in Matlab will determine the overall order and coefficients for any type of FIR filter. First of all remezord function will produce an equivalent filter order and a set of coefficients that meets the filter specifications. By taking these parameters as a guideline, remez function is used again to determine the optimum filter order. This is done by reducing the overall order one at a time and for each order we apply to the remez function again to generate a new set of coefficients. These coefficients are feed to the freqz function to obtain the frequency response data. This data will be evaluated to check if the filter specifications are met. This process will repeat itself until an optimum order is found. The objective function that describes the task of obtaining the optimum order is shown below:

$$Nopt = \arg \min_{order} \{ remez \ function \ that \ meet \ filter \ spec fications \}$$

(4.1)

where Nopt is the optimum order.

Since there are four types of filters, which are lowpass filter, highpass filter, bandpass filter and bandreject filter, the specifications are classified as the constraints for all the objective functions. The notation used to represent the filter specifications for all filter types is presented as follow:

- Fsamp (fs) Sampling Frequency (Hz)

- Fp1 and Fp2 Passband Frequency (Hz)

- Fs1 and Fs2 Stopband Frequency (Hz)

- Rp Passband Ripple (dB)

- Rs Stopband Ripple (dB)

These frequencies and ripple parameters give the characteristic of the frequency response of the filter. To determine if the filter design meets the specifications constraint, the specific magnitude frequency response,  $H(e^{jw})$  is evaluated. There are two inequality constraints and they are determined based on the criteria and the filter type prompt by the user. The following are the two general inequality constraints.

$$\max \left[ 20 \log_{10} \left| H(e^{jw}) \right| - \min \left[ 20 \log_{10} \left| H(e^{jw}) \right| \right] \le R_p$$

(4.2)

$$\max 20\log_{10} \left| H(e^{jw}) \right| \le R_s \tag{4.3}$$

| Filter Type | Frequency Range for<br>Passband Ripple,Rp               | Frequency Range for<br>Stopband Ripple,Rp               |  |

|-------------|---------------------------------------------------------|---------------------------------------------------------|--|

| Lowpass     | 0≤ω≤ω <sub>p</sub>                                      | ω <sub>s</sub> ≤ω≤ω <sub>N</sub>                        |  |

| Highpass    | ω₅≤ω≤ω <sub>N</sub>                                     | 0≤ω≤ω <sub>p</sub>                                      |  |

| Bandpass    | ω <sub>p1</sub> ≤ω≤ω <sub>p2</sub>                      | 0≤ω≤ω <sub>s1</sub> , ω <sub>s2</sub> ≤ω≤ω <sub>N</sub> |  |

| Band reject | 0≤ω≤ω <sub>p1</sub> , ω <sub>p2</sub> ≤ω≤ω <sub>N</sub> | ω <sub>s1</sub> ≤ω≤ω <sub>s2</sub>                      |  |

Table 4.1: Frequencies Range For Passband Ripple and Stopband Ripple of All Filter Types.

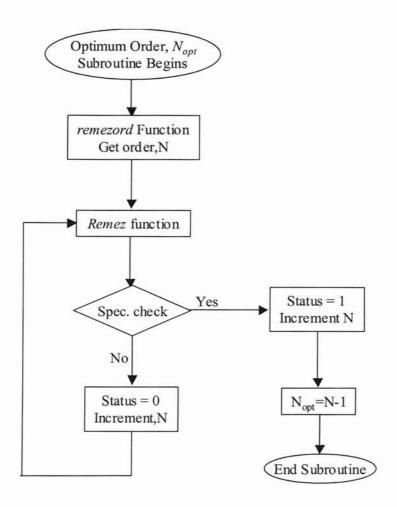

Figure 4.1 presents the frequencies range corresponds to the two inequalities constrains shown in Equation 4.2 and Equation 4.3. The purpose of inequality constraint is to meet the passband and stopband ripples criteria at the right frequency ranges. As long as the inequality constraints are met, the original order is decreased by one or vice versa. This procedure is repeated until the optimum order, *Nopt* is found.

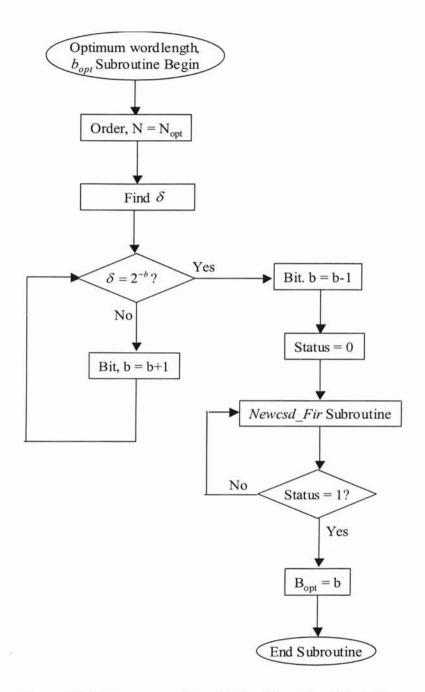

The next step is to determine the optimum coefficients wordlength, *bopt* using the equation defined by Kodek [9], and the following equation proposed is:

$$\delta_R(N,b) \cong 2^{-(wordlength-1)} \sqrt{\frac{(2 \times order) - 1}{3}}$$

(4.4)

where  $\delta_R = \delta_T - \delta_A$

Note that  $\delta_T$  is the total deviation, which is the stopband deviation set by the user;  $\delta_A$  is the approximation error of stopband deviation due to infinite precision coefficients; and  $\delta_R$  is the round off error. Once the wordlength is determined using Equation 4.4, the filter specifications are checked. If the filter specifications are not met, the wordlength will increase by one, and this process is repeated until an optimum wordlength is found. Figure 4.1- 4.3 display flowcharts that explain this optimization algorithm. Figure 4.1 describes the algorithm for finding the optimum order; *Nopt* while Figure 4.2 presents the block diagram for obtaining the optimum wordlength, *bopt*. In *bopt* algorithm there is a small subroutine named *newcsd\_fir*, which is presented in Figure 4.3. This subroutine is to check the filter specification status.

#### 4.2.2 Function Introduction

The function to determine the optimum order, Nopt is get\_Nopt. The function is shown as follows:

$$[Nopt, Fo, Mo, Bopt, csdRs] = get\_Nopt$$

(4.5)

Where the function returns the following parameters:

- Nopt Infinite precision optimum order

- Fo The cutoff frequencies vector for remez function

- Mo Magnitude description of frequency response vector for remez function

- Bopt Optimum set of coefficients (infinite precision)

- csdRs Stopband Ripple Peak

The optimum wordlength function is get bopt and it is shown as follows:

$$[bopt] = get\_bopt(Bopt, Nopt, csdRs)$$

(4.6)

Where the *Bopt*, *Nopt* and *csdRs* are the input of the function and return the optimum wordlength value, *bopt*. In *get\_bopt* function, there is another function called *newcsd\_fir* that checks for filter specifications and returns the optimum wordlength, *bopt*, that meets the specifications. The following shows the *newcsd\_fir* function:

$$[torf] = newcsd _ fir(B, N, b)$$

(4.7)

where the inputs are infinite precision coefficient, B; optimum order, N and wordlength, b. The function returns the status value, torf, where if the filter specifications are met, the status value is equal to one.

Figure 4.1: Optimum Order,  $N_{opt}$  Algorithm Block Diagram

Figure 4.2: Optimum wordlength,  $B_{opt}$  Algorithm Block Diagram

Figure 4.3: newcsd\_fir Subroutine Block Diagram

## 4.3 Scaling

### 4.3.1 Theory

Because we are implementing the digital filter in fixed-point arithmetic, overflow may occur at certain internal nodes. Scaling is normally used to minimize the probability of overflow occurring in the filter. To pick a scale factor, first of all the maximum gain of the transfer function,  $K_{\text{max}}$  must be determined. The maximum scaling factor is the inverse of the maximum gain that is  $\frac{1}{K_{\text{max}}}$ . In our case, however, we will use the scaling factor to reduce the number of adders in the coefficients. This is done by searching possible scale factors between the ranges of the minimum gain factor, which is  $\frac{1}{2K_{\text{max}}}$  to the maximum gain factor,  $\frac{1}{K_{\text{max}}}$ . The optimum scale factor will result in the best set CSD coefficients which in turn results in more hardware savings. Also notice that the minimum scaled factor is scaled by half, which is the power of two and is implemented simply by shift operation. Scaling down the coefficients will result in a slight decrease in SNR and precision.

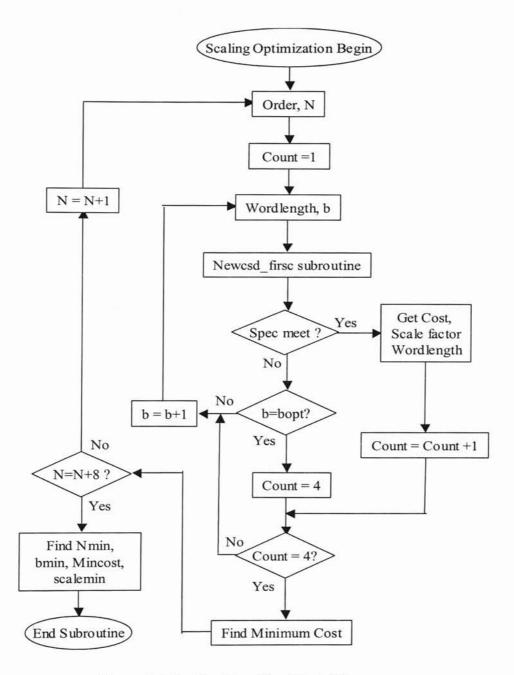

### 4.3.2 Procedure For Determining Minimum Order and Wordlength

To determine both the minimum order and wordlength, cost function is incorporated in the program where the cost function is technology dependent. First the search region is defined for both order and wordlength, hence they are noted as

$\mathbf{N} = \{N_{opt} \leq N \leq 8 + N_{opt}\}$  and  $\mathbf{B} = \{b_{opt} * 0.5 \leq b \leq b_{opt}\}$  respectively. The search regions of both order and wordlength are chosen to be wide enough to search for the minimum order and wordlength that provide the least hardware requirement for the specific FIR filter design. Each element from set  $\mathbf{N}$  is evaluated with all the elements from set  $\mathbf{B}$ . A new search region with different scale factors is determined by different sets of coefficients and the step size of each scale factor is incremented by 0.1. Each scale factor is computed using the formula described below:

Scale factor,

$$S = \frac{K}{(1+0.1I)}$$

$I = 0,1,...9$  (4.8)

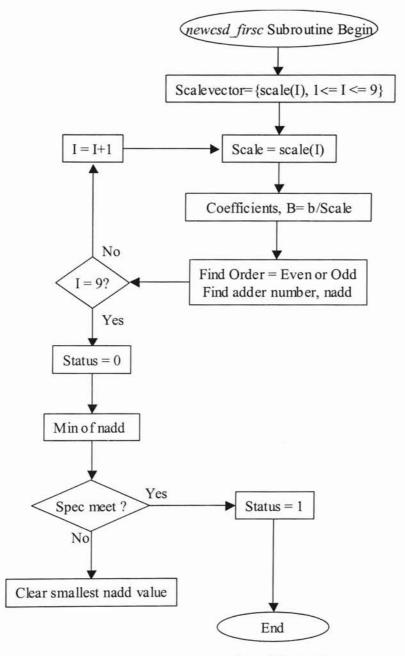

Equation 4.8 shows the region of the scaling factor as ranging from  $\frac{1}{1.9}$  to 1. It now forms a set, S, where the elements are the scale factors varying from  $\frac{1}{1.9}$  to 1. Every coefficient within the search region will multiply by a single scale factor obtained from the set, S, to generate a new set of coefficients. The new set of coefficients is evaluated where the filter's frequency response must meet the filter specification constraints. If it meets the filter specifications, then the particular wordlength, order and scale factor are recorded. So, for every three sets of costs, scale factors and wordlength that meet the filter specifications will be stored in a new matrix. From this matrix, the least cost and scale factor are preserved while the rest of the unimportant data will be eliminated. This procedure will repeat until the search region meets the last order and wordlength of the search regions. As the procedure ends, the most minimized order, Nmin and wordlength, bmin will be determined from a list of corresponding minimum cost table and the minimum scale factor. The flowcharts presented in Figure 4.4 and Figure 4.5 give a

general overview of the algorithm described. Figure 4.4 illustrates the role of the scaling algorithm in the main program and Figure 4.5 illustrates the procedure steps of the scaling algorithm.

### 4.3.2 Function Introduction

The function of optimizing the coefficients using the scaling technique is as follows:

$$[addcnt, addcef, spcsmet, scaleopt] = newcsd firsc(IC, Nvec(i), bvec(k))$$

(4.9)

# Where the inputs are

- IC Infinite precision coefficients

- Nvec Filter order obtain from the search region

- Bvec Coefficient wordlength from the search region

### And the outputs are

- addcnt Total number of structural adders

- addcef Total number of adders of the coefficients

- spcsmet Status of meeting the specifications

- scaleopt The optimum scale factor from the search region

Figure 4.4: Scaling Algorithm Block Diagram

Figure 4.5: newcsd\_firsc Subroutine Algorithm Block Diagram

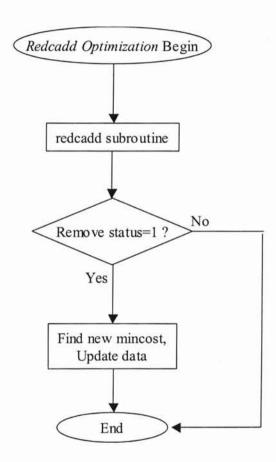

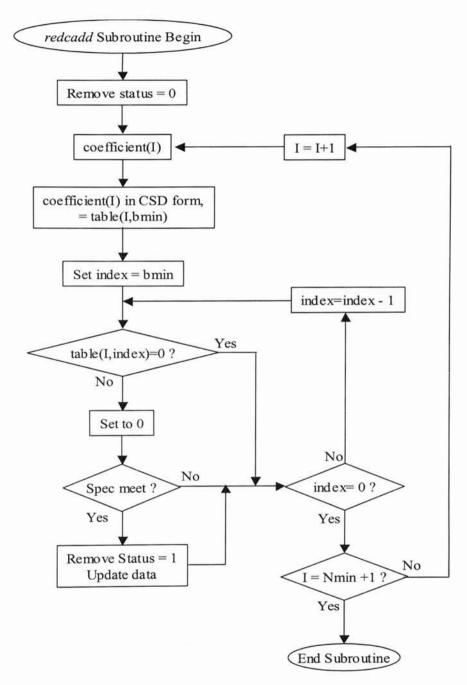

### 4.4 Adder Extraction

The adder extraction technique removes non-zero bits from the coefficient table in binary numbers and replaces them with zero digits. Thus, a new set of coefficients will be generated and the frequency response is checked to make sure the filter specifications are met. If the specifications are meet, then the coefficient table is updated. Hence a new minimum cost is computed. This technique will usually work if the coefficients are represented by a large wordlength such as 16 bits and 20 bits with many nonzero digits. The process usually takes place on the least significant bit from strings of binary numbers.

#### 4.4.1 Procedure of Adder Extraction

Once the new set of coefficients is determined from the scaling optimization, these coefficients are implemented using the adder extraction process, which is the last optimization. This algorithm uses exhaustive search because each binary number obtained from each coefficient is evaluated for each iteration. Every time this process is done the filter specification constraints are checked to make sure that the filter specification meets the requirement. If the filter specifications are met, each coefficient is updated and this process continues for every coefficient for all the non-zero bits. Figure 4.7 shows a detailed explanation of adder extraction algorithm. Note that since it is a linear phase FIR filter, the coefficients are in symmetry so there is a very high chance that two coefficients will be affected. Once all the coefficients have been evaluated, the adder extraction subroutine will produce sufficient output to the main program for further

evaluation. Figure 4.6 presents the role of adder extraction process in the main program. If the optimization of the coefficients has occurred, a status describing the outcome of the adder extraction will occur. If there are any nonzero bits that are extracted, the status will return a true statement. At this point, a new minimized cost is recalculated and the new coefficients replace the old coefficients. If no coefficients are minimized from adder extraction subroutine, then all the results will be sustained.

### 4.4.2 Function Introduction

The *redcadd* function operates the adder extraction optimization and returns the updated result.

$[rmvd, Hrmvd, newtable, newaddcefmin, newRpl] = (scalemin, table, Nmin, bmin, addcefmin) \eqno(4.10)$

### Where the inputs are

- scalemin Optimized scale factor

- table A set of optimized coefficients in CSD representation

- Nmin Minimum order

- bmin Minimum wordlength

- addcefmin Total number of adders of the coefficients

### Where the outputs are

- rmvd Adder extraction status

- Hrmvd Complex frequency response after adder extraction process

- newtable A set of optimized coefficients in CSD representation

- newaddcefmin Total number of adders of the coefficients

- newRp1 New set of ripples information in dB.

Figure 4.6: Adder Extraction Optimization General Routine Block Diagram

Figure 4.7: Adder Extraction Algorithm Block Diagram

## 4.5 Example Result of Three Optimization Techniques

The following tables show the example cost results of the four types of filters. Each filter has its own fixed filter specifications except the passband ripple, Rp is varied ranging from 5.5dB to 0.1dB. The sampling frequency is fixed on 24KHz and the input wordlength is set at 8 bit. The filter type and its filter specification profile are listed on the heading of each table. Referring to Tables 4.2 to 4.5, the cost results of each filter are recorded under three main headings, which are Order-wordlength tradeoff, Scaling and Adder Extraction. Additionally, the heading % Reduction (1) means the percentage cost savings computed from the difference between the first technique, Order-wordlength tradeoff over the second technique, Scaling. Similarly, the heading % Reduction (2) displays the percentage cost savings for the second technique, Scaling and the third technique, adder extraction. Also note that the cost is computed based on the cost equation, which will be discussed in Section 7.3. From the observation, the percentage savings of the second technique over the first technique range from 3% to 45%. On the other hand, the percentage reduction obtained from the second and third techniques is extremely low. The reduction range is 0 to 1.8 percent only. The reason is the large saving occurs during the scaling optimization. Therefore, if there is no saving shown, this means that the hardware representation of the coefficients is truly minimized. In short, adder extraction optimization's role is to make sure that the hardware required for the coefficients is minimized. Overall, the average hardware savings for scaling technique over order-wordlength tradeoff is about 20% and the average hardware savings for adder extraction technique over scaling technique is approximately 0.3%.

| Lowp |                                  |           | = [5000 6000] <br>Ripple, Rs = 40 |                     |                   |

|------|----------------------------------|-----------|-----------------------------------|---------------------|-------------------|

| Rp   | Order-<br>Wordlength<br>Tradeoff | Scaling   | %Reduction<br>(1)                 | Adder<br>Extraction | %Reduction<br>(2) |

| 5.5  | 1872                             | 1572      | 16.03                             | 1560                | 0.76              |

| 5    | 1956                             | 1614      | 17.48                             | 1614                | 0.00              |

| 4.5  | 2093                             | 1685      | 19.50                             | 1685                | 0.00              |

| 4    | 2022                             | 1806      | 10.68                             | 1794                | 0.66              |

| 3.5  | 2494                             | 1880      | 24.62                             | 1869                | 0.59              |

| 3    | 2144                             | 1906      | 11.10                             | 1894                | 0.63              |

| 2.5  | 2431                             | 2078      | 14.52                             | 2078                | 0.00              |

| 2    | 2878                             | 2068      | 28.14                             | 2068                | 0.00              |

| 1.5  | 2860                             | 2304      | 19.44                             | 23.04               | 0.00              |

| 1.0  | 3402                             | 2548      | 25.10                             | 2548                | 0.00              |

| 0.5  | 5112                             | 2798      | 45.27                             | 2798                | 0.00              |

| 0.2  | 4603                             | 3532      | 23.27                             | 3493                | 1.10              |

| 0.1  | 5488                             | 3826      | 30.28                             | 3826                | 0.00              |

|      | Av                               | erage (1) | 21.96                             | Average (2)         | 0.29              |

Table 4.2: Percentage Cost reduction for Lowpass Filter Example

| High |                                  | Frequency = [5000 6000]Hz<br>Stopband Ripple, Rs = 40dB |                   |                     |                   |

|------|----------------------------------|---------------------------------------------------------|-------------------|---------------------|-------------------|

| Rp   | Order-<br>Wordlength<br>Tradeoff | Scaling                                                 | %Reduction<br>(1) | Adder<br>Extraction | %Reduction<br>(2) |

| 5.5  | 1728                             | 1567                                                    | 9.32              | 1567                | 0.00              |

| 5    | 1900                             | 1762                                                    | 7.26              | 1762                | 0.00              |

| 4.5  | 1888                             | 1726                                                    | 8.58              | 1726                | 0.00              |

| 4    | 2145                             | 1795                                                    | 16.32             | 1795                | 0.00              |

| 3.5  | 2156                             | 1700                                                    | 21.15             | 1700                | 0.00              |

| 3    | 27.16                            | 1773                                                    | 34.72             | 1773                | 0.00              |

| 2.5  | 2698                             | 1992                                                    | 26.17             | 1992                | 0.00              |

| 2    | 2918                             | 2105                                                    | 27.86             | 2094                | 0.52              |

| 1.5  | 2795                             | 2088                                                    | 25.30             | 2088                | 0.00              |

| 1.0  | 3591                             | 2536                                                    | 29.38             | 2488                | 1.89              |

| 0.5  | 3172                             | 2552                                                    | 19.55             | 2552                | 0.00              |

| 0.2  | 4394                             | 3332                                                    | 24.15             | 3320                | 0.36              |

| 0.1  | 4833                             | 3696                                                    | 23.53             | 3696                | 0.00              |

|      | Av                               | erage (1)                                               | 21.02             | Average (2)         | 0.21              |

Table 4.3: Percentage Cost reduction for Highpass Filter Example

| Band |                                  |           | y = [3000 4000<br>Ripple, Rs = 40 |                     |                   |

|------|----------------------------------|-----------|-----------------------------------|---------------------|-------------------|

| Rp   | Order-<br>Wordlength<br>Tradeoff | Scaling   | %Reduction<br>(1)                 | Adder<br>Extraction | %Reduction<br>(2) |

| 5.5  | 2236                             | 1830      | 18.16                             | 1818                | 0.66              |

| 5    | 2184                             | 1906      | 12.73                             | 1884                | 1.15              |

| 4.5  | 2210                             | 1878      | 15.02                             | 1878                | 0.00              |

| 4    | 2210                             | 1987      | 10.09                             | 1987                | 0.00              |

| 3.5  | 2550                             | 2016      | 20.94                             | 2016                | 0.00              |

| 3    | 2682                             | 2158      | 19.54                             | 2132                | 1.20              |

| 2.5  | 2994                             | 2560      | 14.50                             | 2548                | 0.47              |

| 2    | 3583                             | 2726      | 23.92                             | 2690                | 1.32              |

| 1.5  | 4266                             | 2750      | 35.54                             | 2726                | 0.87              |

| 1.0  | 3640                             | 2868      | 21.21                             | 2868                | 0.00              |

| 0.5  | 2990                             | 2894      | 3.21                              | 2882                | 0.41              |

| 0.2  | 6648                             | 3600      | 45.85                             | 3588                | 0.33              |

| 0.1  | 5033                             | 3664      | 27.20                             | 3652                | 0.33              |

|      | Av                               | erage (1) | 20.61                             | Average (2)         | 0.52              |

Table 4.4: Percentage Cost reduction for Bandpass Filter Example

| Band   | Reject Filter:                   |           | y = [3000 4000<br>d Ripple, Rs = |                     |                   |

|--------|----------------------------------|-----------|----------------------------------|---------------------|-------------------|

| Rp     | Order-<br>Wordlength<br>Tradeoff | Scaling   | %Reduction<br>(1)                | Adder<br>Extraction | %Reduction<br>(2) |

| 5.5    | 1752                             | 1344      | 23.29                            | 1344                | 0.00              |

| 5      | 1699                             | 1412      | 16.89                            | 1412                | 0.00              |

| 4.5    | 1876                             | 1421      | 24.25                            | 1421                | 0.00              |

| 4      | 1699                             | 1385      | 18.48                            | 1385                | 0.00              |

| 3.5    | 2000                             | 1385      | 30.75                            | 1385                | 0.00              |

| 3      | 2012                             | 1385      | 31.16                            | 1385                | 0.00              |

| 2.5    | 2136                             | 1630      | 23.70                            | 1630                | 0.00              |

| 2      | 2368                             | 1884      | 20.44                            | 1884                | 0.00              |

| 1.5    | 2215                             | 2105      | 4.97                             | 2083                | 1.05              |

| 1.0    | 2925                             | 2223      | 24                               | 2212                | 0.50              |

| 0.5    | 3406                             | 2873      | 15.65                            | 2847                | 0.91              |

| 0.2    | 4200                             | 3592      | 14.48                            | 3566                | 0.72              |

| 0.1    | 4522                             | 4288      | 5.17                             | 4223                | 1.52              |

| 1705/S |                                  | erage (1) | 19.48                            | Average (2)         | 0.36              |

Table 4.5: Percentage Cost reduction for Band Reject Filter Example

# Section 5

# Dempster and Macleod Implementation

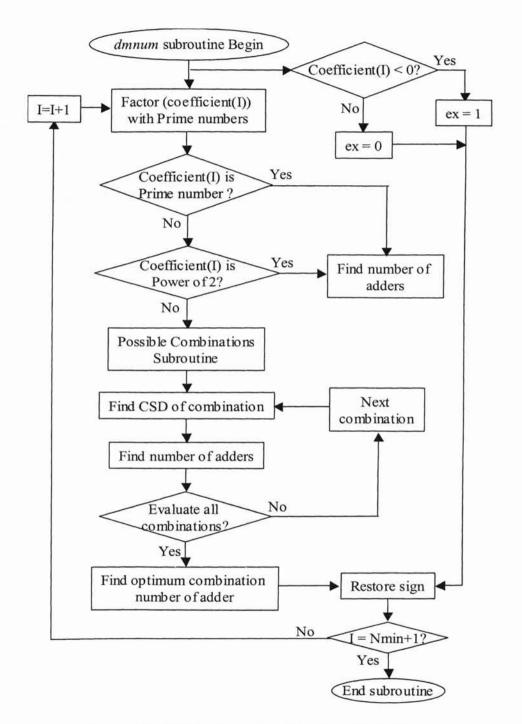

# 5.1 DM Optimization Introduction

The DM approach is based upon saving adders in coefficient multiplier implementation by factoring the coefficient into numbers that require fewer adders to implement the cascading of the factored coefficient multipliers. The initial step is to convert the coefficients into decimal format and then factor the decimal formed coefficients using only the prime numbers. The hope is that factoring the coefficient numbers with prime numbers will be a better choice compared to choosing a vast range of numbers for factorization. For some cases, factoring the coefficients with prime numbers may not result in a savings in hardware. Thus, other factoring numbers may need to be considered, and will result in many possible ways of factoring the coefficients. Many combinations that represent the coefficients are produced and usually many combinations are redundant. For a simple example, consider the coefficient with multiplier 297, the computation of prime factors is as below:

$$297 = 3 \times 3 \times 3 \times 11 = (2^{2} - 1) \times (2^{2} - 1) \times (2^{4} - 2^{2} - 1)$$

(5.1)

Notice that factors 3 and 11 are prime numbers. Equation 5.1 shows that the multiplier 297 needs 5 adders. But there is another alternative result, shown here:

$$297 = 9 \times 33 = (2^{3} + 1) \times (2^{5} + 1)$$

(5.2)

By just taking the factors of 9 and 11, now only two adders are needed. This result requires fewer numbers of adders compared to Equation 5.1. Notice that for this example the computation result has fewer adder requirements compared to CSD representation, which require the total of three adders. As the value of the multiplier increases, the number of possible combinations that represent the multiplier value increases. The only exception is where no combinations are generated when the multiplier itself is a prime number and then there is no need to perform DM optimization.

# 5.2 DM Optimization Procedure

Initially, all the coefficients are converted into decimal numbers based on the minimum wordlength obtained earlier. These multipliers will be evaluated one by one to determine the number of adders needed. First of all, each multiplier is tested to see if they are the result of the power of two or a prime number itself. If either of the conditions is true, then the number of adders will not be evaluated but will immediately state the number of adders based on the number of adders obtain from CSD representation. If the conditions are false, then all the possible combinations of the factored coefficients will be stored in a matrix and each combination is evaluated by counting the number of adders available. Note that if any of the factors is equal to two, it is ignored because no adders are required for this case. Another problem occurs is when a single number is a power of

Notice that factors 3 and 11 are prime numbers. Equation 5.1 shows that the multiplier 297 needs 5 adders. But there is another alternative result, shown here:

$$297 = 9 \times 33 = (2^{3} + 1) \times (2^{5} + 1)$$

(5.2)

By just taking the factors of 9 and 11, now only two adders are needed. This result requires fewer numbers of adders compared to Equation 5.1. Notice that for this example the computation result has fewer adder requirements compared to CSD representation, which require the total of three adders. As the value of the multiplier increases, the number of possible combinations that represent the multiplier value increases. The only exception is where no combinations are generated when the multiplier itself is a prime number and then there is no need to perform DM optimization.

# 5.2 DM Optimization Procedure