# TABLE DRIVEN ADAPTIVE, EFFECTIVELY HETEROGENEOUS MULTI-CORE ARCHITECTURE

# By

# **SURPRIYA TIKE**

Bachelor of Science in Electronics and

Telecommunication

Pune University

Pune, India

2007

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of MASTER OF SCIENCE December, 2011

# TABLE DRIVEN ADAPTIVE, EFFECTIVELY HETEROGENEOUS MULTI-CORE ARCHITECTURE

Thesis Approved:

Dr. James E. Stine Jr.

Thesis Adviser

Dr. Chris Hutchens

Dr. Louis G. Johnson

Dr. Sheryl A. Tucker

Dean of the Graduate College

# TABLE OF CONTENTS

| Chapt | er                                      | Page |

|-------|-----------------------------------------|------|

| 1.    | INTRODUCTION                            | 1    |

| 2.    | BACKGROUND                              | 1    |

|       | 2.1. Processor based platforms          | 1    |

|       | 2.1.1. OpenSPARC                        | 1    |

|       | 2.1.2. SimpleScalar                     | 2    |

|       | 2.1.3. SPIM                             | 2    |

|       | 2.1.4. Simics                           | 2    |

|       | 2.2. Other Related Work                 | 3    |

|       | 2.3. Proposed Solution                  | 4    |

| 3.    | IMPLEMENTATION                          | 6    |

|       | 3.1. Architecture Top Level description | 6    |

|       | 3.2. Performance Counters               | 10   |

|       | 3.3. Single-threaded core               | 10   |

|       | 3.3.1. Datapath                         | 11   |

|       | 3.3.2. Hazard Unit                      | 21   |

|       | 3.3.3. Coprocessor0                     | 21   |

|       | 3.4. L2 Data and Instruction Cache      | 21   |

|       | 3.5. Floating Point Units               | 22   |

|       | 3.6. Arbiter Logic                      | 25   |

|       | 3.7. Asynchronous FIFO                  | 27   |

|       | 3.8. Data Coherency                     | 29   |

|       | 3.8.1. Snooping                         | 29   |

|       | 3.8.2. Directory-based                  | 30   |

|       | 3.8.3. Snarfing                         | 30   |

| 4.    | TOOL FLOW AND DESIGN METHODOLOGY        | 34   |

|    | 4.1. ModelSim                           | 34 |

|----|-----------------------------------------|----|

|    | 4.1.1. Unit testing of module           | 37 |

|    | 4.1.2. Benchmark Testing                |    |

|    | 4.1.3. Challenge with Benchmark Testing | 37 |

|    | 4.1.4. Solution                         |    |

|    | 4.1.5. Script and Setup                 | 38 |

|    | 4.2. Design Compiler                    | 38 |

|    | 4.2.1. Design Compiler flow             | 38 |

|    | 4.2.2. Design Compiler file formats     | 39 |

|    | 4.2.3. Script and Setup                 | 41 |

|    | 4.3. Formal Verification                | 41 |

|    | 4.3.1. Need for Formal Verification     | 42 |

|    | 4.3.2. Script and Setup                 | 43 |

|    | 4.4. IC Compiler                        | 43 |

|    | 4.4.1. IC Compiler flow                 | 44 |

|    | 4.4.2. Script and Setup                 | 56 |

| 5. | . CONCLUSION                            | 57 |

| RE | REFERENCES                              | 59 |

| ΑF | APPENDICES                              | 62 |

# LIST OF TABLES

| Table                                                             | Page |

|-------------------------------------------------------------------|------|

| Table 1 - Implemented Instruction Set                             | 12   |

| Table 2 - Arbiter Bus - [Level1_Icache - Arbiter - Level2_Icache] | 25   |

| Table 3 - Arbiter Bus - [Level1_Dcache - Arbiter - Level2_Dcache] | 25   |

| Table 4 - Arbiter Bus - [Core_CX - Arbiter - Floating Point Unit] | 25   |

# LIST OF FIGURES

| Figure                                                                                | Page       |

|---------------------------------------------------------------------------------------|------------|

| Figure 1 - Top Level Architecture                                                     | 7          |

| Figure 2 - 5 Stage pipelined datapath                                                 | 9          |

| Figure 3 - Register File Set                                                          | 13         |

| Figure 4 - Integer Radix16 Divider (fast)                                             | 14         |

| Figure 5 - Integer Radix4 Divider (slow)                                              | 15         |

| Figure 6 - Level1 Dcache architecture flexibility                                     | 16         |

| Figure 7 - Memory Subsystem adapted into different architectures                      | 17         |

| Figure 8 - Memory moving from lower to higher set associativity                       | 18         |

| Figure 9 - Memory moving from higher to lower set associativity – encounters invalid  | entries 19 |

| Figure 10 - multi_match penalty evaluation                                            | 20         |

| Figure 11 - Pipelined Floating Point Unit                                             | 23         |

| Figure 12 - Arbiter Logic                                                             | 26         |

| Figure 13 - Asynchronous FIFO with Gray code read/write pointers                      | 27         |

| Figure 14 - Snooping based cache coherency                                            | 28         |

| Figure 15 - Directory Structure                                                       | 31         |

| Figure 16 - Tool Flow Methodology                                                     | 35         |

| Figure 17 - ModelSim Simulation of RTL                                                | 36         |

| Figure 18 - Design Vision showing the synthesized memory stage from datapath          | 40         |

| Figure 19 - Formality – Successful Verification with post-synthesis netlist for Core1 | 42         |

| Figure 20 - Initialize floorplan for complete design                                  | 45         |

| Figure 21 – Creating plan-groups for hierarchical sub-modules          | 45 |

|------------------------------------------------------------------------|----|

| Figure 22 – Placement of plan-groups along with hard macros            | 46 |

| Figure 23 - Committing final plan-groups                               | 46 |

| Figure 24 - Plan-group after placement                                 | 47 |

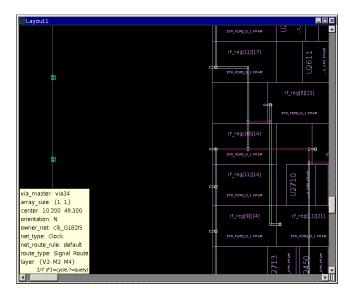

| Figure 25 - Zoom-in on the CTS stage showing clock routed on M3-M4     | 48 |

| Figure 26 - Post-route Layout                                          | 48 |

| Figure 27 - Global Routing Congestion for plan-group                   | 49 |

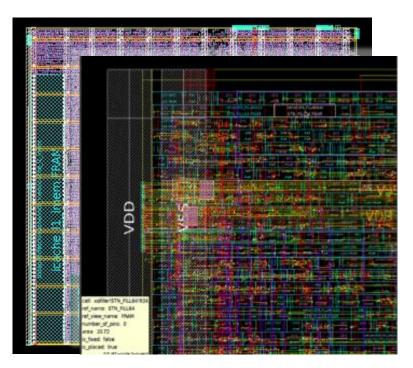

| Figure 28 - Chip Finish for plan-group                                 | 49 |

| Figure 29 - Initialization of the top-level design                     | 50 |

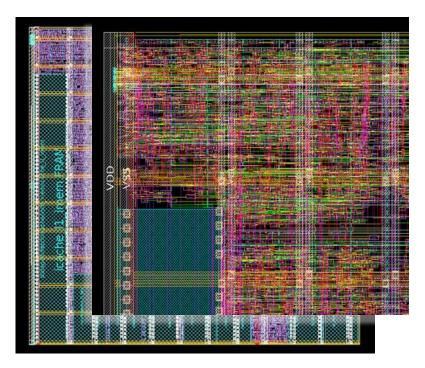

| Figure 30 - Post Route of Top-level design                             | 51 |

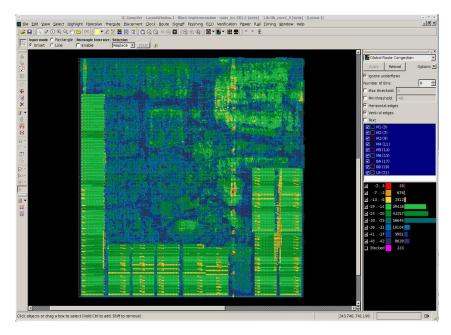

| Figure 31 - Global Routing Congestion for Top-level design             | 51 |

| Figure 32 - Chip Finish of Top-level design                            | 52 |

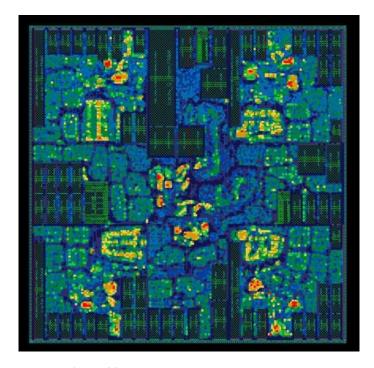

| Figure 33 - Pin Density Analysis (Map Mode)                            | 53 |

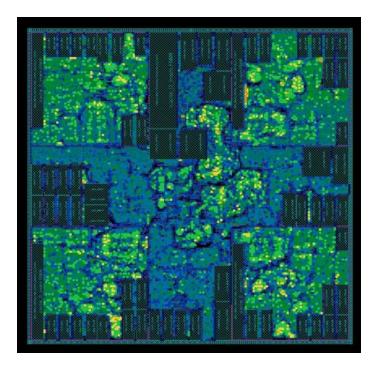

| Figure 34 - Cell Density Analysis (Map Mode)                           | 54 |

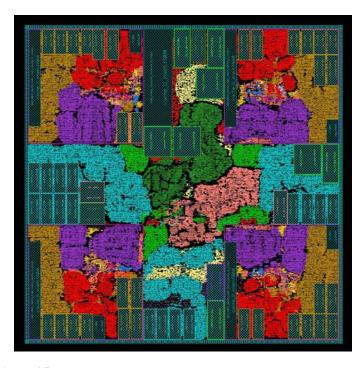

| Figure 35 - Color coded hierarchy across top level and all plan groups | 54 |

| Figure 36 - Color-coded hierarchies inside cores                       | 55 |

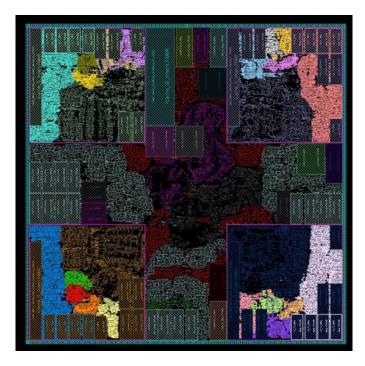

| Figure 37 - Locations of architecture unit in top-level floorplan      | 55 |

#### CHAPTER I

#### INTRODUCTION

Recent research and advancements with modern computer architecture emphasize heavily on the novel implementation techniques for performance enhancement. One of the techniques that have been under research is the exploitation of multi-core architectures. However, with increasing dynamic nature of the workloads of everyday computing, even general multi-core architectures seem to just touch an upper limit on the deliverable performance. This has paved way for meticulous consideration of heterogeneous multi-core architectures.

The notion behind the concept of heterogeneous multi-core architectures is smart allocation of workload to more equipped cores, which positively affects performance. Having multiple cores in a system, some dedicated for a special function certainly brings certain degree of flexibility in distributing workload more efficiently. However, these architectures can also face roadblocks in certain scenarios. Such architectures can be further enhanced by making the heterogeneity quality of the cores dynamic in nature. Making the cores dynamically heterogeneous implies that the cores can change their properties on-the-fly in accordance with the incoming loads.

This is quite significant, since the cores can change their properties independent of each other, and yet share processor resources on higher hierarchy levels. Some research and implementations have materialized in the past, which use workload monitoring to shut-off units for power optimizations. Some of these works also make use of Configuration ROMs or look-up tables being used for this purpose. Although, when managing multiple heterogeneous cores with ever-changing workloads, merely shutting of inactive units does not give the performance boost we are looking for.

This project, OSCAR (OSU Simulation for Computer Architecture Research) is an RTL based simulation environment for a heterogeneous multi-core architecture. The project implements four such dynamically configurable MIPS-like cores, which have shared memory resources on Level2 hierarchy through data coherency protocol. The dynamic configurations are done, by observing the nature of incoming workload for each core by deploying performance counters. The technique uses feedback from performance counters every couple of thousand instructions, and a configuration look-up table, to make the decisions for architecture changes.

Whilst this is a very powerful concept, future developments and expansions will make the architecture more proficient and promising. Another highlighting aim of the project is to make a framework of a modern multi-core architecture, which can be made available to the academia for further development.

#### **CHAPTER II**

#### **BACKGROUND**

In the past years, several platforms have been developed which actual showcase multicore architectures or simulation environments for the same. Some of them are OpenSPARC T1/T2 by Sun Microsystems, Simics, SPIM, SimpleScalar, etc. Developers of these platforms encourage students to make use of the tools for academic purposes. However, looking at the necessity of the ongoing research focus in the field, the mentioned platforms pose certain difficulties in their usage.

## 2.1. Processor based platforms

The following entries describe academically available processor based platforms. Most of these are developed in high level languages, which is undoubtedly easier to deal with, but do not account for the real hardware investment.

# 2.1.1. OpenSPARC

Of all mentioned above, only UltraSPARC T1/T2 from the OpenSPARC project [1] is hardware based open-source development platform.

All others are instruction accurate simulators for MIPS-like architecture which are usually designed in high level languages such as C, C# or Java. UltraSPARC T1 (Niagara) released in 2005 was a 32/64 bit threaded microprocessor with 8 cores, and a total 32 threads. The downside of this architecture was the use of just one FPU unit shared between 8 cores. This problem was moderated but not solved in the UltraSPARC T2 (Niagara2). Niagara2 implemented one FPU for each of the 8 cores.

#### 2.1.2. SimpleScalar

Dr. Todd Austin developed SimpleScalar [2] in 2001 while he was a PhD student at University of Wisconsin-Madison. The SimpleScalar architecture is derived from the MIPS-IV architecture. Several papers and articles published by him and his team point towards the need of an infrastructure for modeling and simulation.

These articles also emphasize on the need of such platforms to be open-source, and easily adaptable for academic use. Being written in a high level language, the tool provides limited detailing from implementation point of view.

#### 2.1.3. SPIM

Dr. James Larus developed SPIM [3] (reversal of letters *MIPS*) while he was a professor at University of Wisconsin-Madison in 1990. The latest version being 9.0, is now being developed using Qt framework (cross-platform for Windows/Linux/Mac) and is also open-source. Although, since thus lacks the hardware aspect too, we will face same troubles with SPIM.

#### 2.1.4. Simics

Simics [4] is a *full-system simulator*, which can be used to simulate complete computer systems. A full system simulator provides virtual hardware, which is completely independent of the host machine and its architecture. Simics can thus be used to create environments, which encompass multiple processors, memory units, network, and other interconnects. Thus, Simics

has been developed to provide a very high level of abstraction as far as computer architecture is concerned. This makes Simics an unsuitable choice for detail designing and implementation of a processor with multicore architecture.

These simulators that are designed using high-level languages might provide a user with faster design cycles, with little or no co-relation to its hardware implementation. These simulators are effective when the designers need a platform to perform basic development and testing of new ideas on MIPS-like architectures.

Using instruction accurate simulators certainly implies that developers need lesser time for development and testing, but the accuracy and importance of actual hardware implementation cannot be overshadowed.

#### 2.2. Other Related Work

One focus area for related research work has been the on-chip cache hierarchy. It has been suggested that an increasing percentage of die area is being devoted to caches, and that on-chip L1 caches can alone comprise over 40% of the total die power budget [5]. The 2007 International Technology Roadmap for Semiconductors (ITRS) also suggests that by 2014 more than 94% of the overall area of SoC designs will be occupied by memories [6]. Thus a lot of work is being done in optimizing the memory subsystems, instigating a tradeoff between increased performance, and reduced power requirements.

Some of such papers suggest shutting down some memory blocks when not needed, which results in power savings. One such paper [7] implements a technique called *Selective Cache Ways*, implements a set associative cache, and selectively disables data cache ways during phases of modest cache activity. This decision is controlled by keeping a check on *Performance Degradation Threshold* (PDT) for tolerable performance loss.

The advantage was that no flushing of cache was required when enabling/disabling the cache ways, which saves on the heavy time penalty. Enabling/disabling memory units eventually reflect impressive power numbers. But any increase in performance finally is gained at the expense of direct increased power.

Multiple level caches typically display unbalanced access patterns, since most data is serviced by L1 cache. Another paper takes a global ruling of turning off multiple tier caches which sit idle for long times [8]. A majority of these ideas involve exclusively reducing energy usage by disabling caches or redundant core resources to save on the associated leakage power [9] [10].

It has also been shown that using specialized low-leakage transistors can significantly help energy consumption in L1 and L2 caches [11]. Implementing such a technique will require either a manually routed memory block, or a compiler using such cells.

#### 2.3. Proposed Solution

OSCAR (OSU Simulation for Computer Architecture Research) is an RTL based simulation environment for a heterogeneous multi-core architecture. The advantage of an RTL based model is that the hardware can be modeled very accurately. Using cycle accurate simulation environment provides the required insight into the detail operations of the cores. The target library used for the project is IBM65LPE. Virage memory compilers from Synopsys was used to generate the on-chip memory blocks.

The project is completely synthesizable, and the resultant netlist can be used to evaluate power and timing numbers for all hierarchically modules, including the memory macros for various test codes. Thus this multi-core architecture with two on-chip memory hierarchies and a shared FPU unit, which is all modeled using RTL, makes a great platform for future development.

Looking at conventional units in microprocessor architecture, memories, heavy computational units, and core-to-core interconnect busses are typically the ones to create bottlenecks. Thus, the objective was to boost performance by tweaking these units. This work implements an idea having unit similar to selective cache ways [7], which change their architecture dynamically between 1way, 2way and 4way within each core. The cores can also be configured in three modes – power, speed, and adaptive. These settings can be made in the testbench.

The *power* mode is the most conservative mode, where minimal resources are allocated, which would save on overall power, but may be effectively more time consuming. The other *speed* mode deploys the fastest resources on the chip, which may consume more power than in power mode.

The third *auto* mode is the highlighting aspect of this work. Keeping in mind, that the multiple cores will have independent workloads with varied requirements, the cores in this mode adapt dynamically to suit these needs. Various units in the architecture, including some specific to each core, are modified as per need. This includes the execute and memory stage of pipeline per core, and the global FPU unit.

The Dcache will restructure itself to act as power and speed driven from time-to-time, depending on load requirements. When working on the heavy computational units in the Execute stage of the datapath, a separate provision for fast and slow multipliers/dividers has been made. Thus, depending on requirement, one of them can be used, while the other one remains inactive. The FPU unit(s) is a global resource for the four cores. For increased FPU type workloads for more than one core, both the FPU units are turned on for faster servicing rates.

#### **CHAPTER III**

#### **IMPLEMENTATION**

The RTL of the architecture has been implemented in Verilog using structural style of hardware modeling. This is specifically important because the project aimed at designing units that didn't use operators with huge untailored hardware for the computations.

## 3.1. Architecture Top Level description -

Four single threaded pipelined cores

4KB Level 1 Dcache per core withy LRU (configurable)

4KB direct mapped Level1 Icache for each core

16KB 4-way set associative shared Level2 Dcache

16KB direct mapped shared Level2 Icache

Two floating-point units (configurable)

Arbiter logic between cores and Level2 cache and FPUs

Directory implementation for data coherency

Besides the components mentioned above, the architecture also has a shared L3 Dcache and L3 Icache, which is considered to be the main memory, and resides outside the chip.

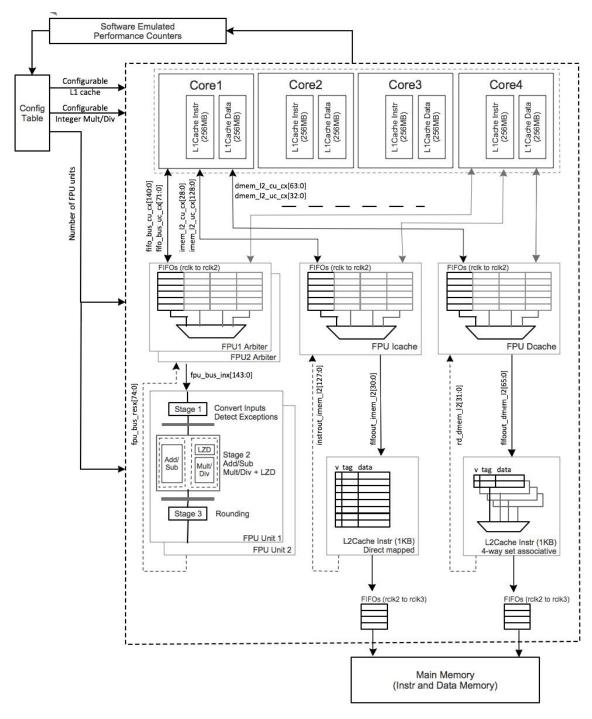

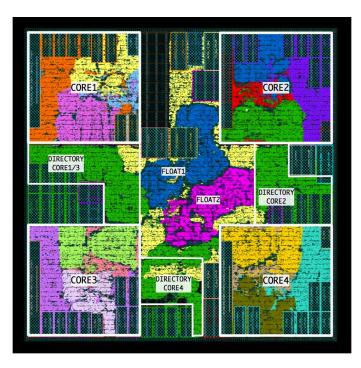

Figure 1 - Top Level Architecture

The top-level architecture consists of two levels of hierarchies. The top-level hierarchy illustrated in Figure 1 implements four MIPS-like cores. These are single-threaded cores with

independent 4KB L1 data and instruction caches. Each core also has a standard 5-stage pipelined datapath and exception handler unit (coprocessor0).

The four cores share 16KB Level2 data and instruction caches, and FPU unit(s). The directory structure also operates parallel to the Level2 Dcache. The arbiter layer efficiently handles the complete interface between the Level2 units and the cores. The major components of this hierarchy are the huge memory components, which is why they can't use the same clock as the core frequency. All the units in this hierarchy use a separate clock domain with reduced frequency called rclk\_2. The arbiter layer implements asynchronous FIFOs, which use writing clocks same as the core frequency (clk) and the reading clock same as the slower clock (rclk\_2).

Besides the memory elements and the directory structure, the Level2 hierarchy also implements pipelined Floating Point Unit(s). The arbiter layer also facilitates the sharing of the PFU unit(s) between the cores. Besides the normal floating-point operations of add/sub, the FPU unit also implements units for high radix combined unit for mult/div operations on single and double precision floating point numbers (IEEE754-1985).

One of the highlighting features of the design is adaptability of the architecture for different types of workloads. The goal of this flexibility is to attain power and speed efficient models and provide quantitative analysis on design trade-offs, thus suggesting the best possible architectural configuration for a specific workload.

Architectural changes are done through a lookup table (similar to a Config ROM), which dynamically adapts to different architectural configuration with the help of performance counter. Various performance counters are deployed at various locations in hardware to constantly gauge the workload individually for all cores. The performance counters examine workloads for integer mult/div, floating point and memory intensive instruction windows. The size of this window can be very easily set in the testbench.

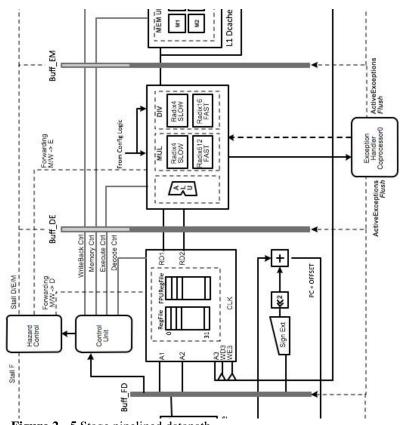

Figure 2 - 5 Stage pipelined datapath

The configurable components in architecture are -

#### a) Configurable number of FPU units

Floating point intensive applications will enable FPU units (one or two) depending on demand. Each pipelined FPU unit comprises of a Radix512 mult-div unit, adder, and integer-float conversion unit. By default one FPU unit is enabled; second FPU unit is enabled when the workload of more than two cores increases beyond a threshold. The user can configure this threshold.

#### b) Dynamically configurable-way L1 cache for memory intensive applications.

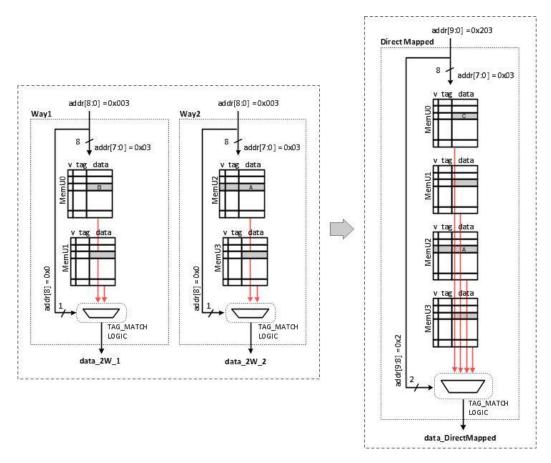

This decision is made independently for each core depending on needs. For a particular core, if Dcache misses exceed beyond a certain threshold, architecture for Level1 Dcache can be dynamically switched between direct mapped, 2way and 4way set associative. Again, the user

can configure this threshold. By default, the Dcache is configured to be in direct mapped. The user can configure the L1 Dcache to be in direct mapped, 2way or 4way architecture, or let the decision be made dynamically according to the requirements.

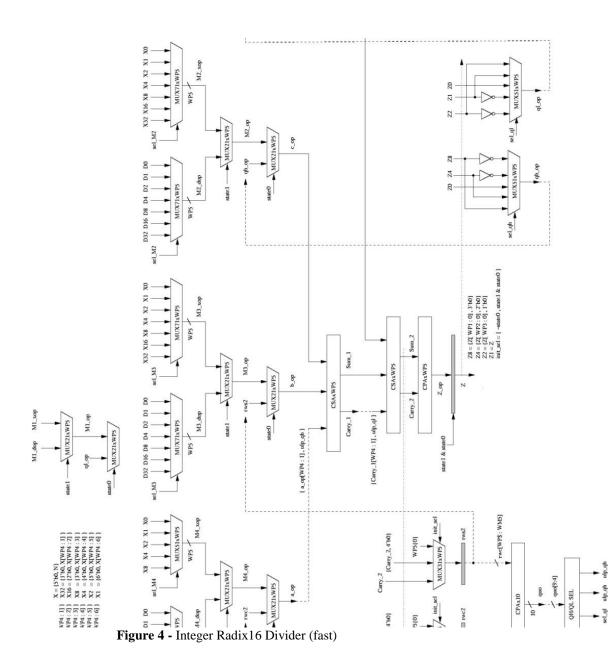

# c) Enabling and disabling high/low performance integer units

This decision is made independently for each core depending on needs. The user can configure the cores for high performance vs. low performance integer multiply-divide units in testbench. The high performance unit uses Radix512 multiplier and Radix16 divider. The low performance unit uses Radix16 multiplier and Radix4 divider. Units are enabled/disabled through clock gating. By default, the low performance integer unit is enabled. The user can also choose to configure otherwise.

The flexibility added in the architecture for the availability of dynamic configuration does add a lot of redundant hardware. This definitely will influence area numbers. Although, the area count of the active hardware in a given configuration will be lesser, and is important. Although, since the redundant hardware will be mostly clock gated when unused, the power numbers should not be influenced beyond scope.

#### 3.2. Performance Counters

Performance counters keep a measure of the workload in every instruction window (e.g.: 256 instructions for and 8-bit counter). Various performance counters are deployed in hardware to gauge workload for memory, FPU or integer mult/div intensive applications. These results from these counters are fed to the Config logic, where the architecture changes are decided for the next instruction window. The Config logic also contains several user-defined thresholds which when crossed, can trigger changes in architecture. Thus, some of the core configurations can be changed to enhance performance during run-time.

### 3.3. Single-threaded core

The chip consists of four single threaded pipelined cores, which share a common 16KB L2 Dcache, and 16KB L2 Icache, and FPU unit(s) through an arbiter. Each of the cores consists of basic blocks like the datapath, control unit, hazard control unit, and a coprocessor0 for exception handling. The following sub-sections will give descriptions about the various units of the architecture in details:

## 3.3.1. Datapath

The datapath is a classic five-stage pipeline consisting of following stages: fetch, decode, execute, memory, writeback. A detailed block diagram of the datapath is illustrated in Figure 2.

Buffers separate each of these stages. Fetch and Memory stages implement synchronous SRAM memories. The following sections describe the stages in the 5-stage pipeline.

#### 3.3.1.1. Fetch

The fetch stage implements a synchronous direct-mapped SRAM, which has a capacity of 256x16B (4KB), thus storing 4 instructions in each line of SRAM. Level2 Icache is also designed in the similar manner. Thus, when an instruction miss is generated for an address, four instructions are fetched at a time.

| J-type Instructions     |                     |       |       |     |      |     |

|-------------------------|---------------------|-------|-------|-----|------|-----|

| J (Jump)                | JAL                 | JALR  |       |     |      |     |

| R-type Instru           | ictions             |       |       |     |      |     |

| NOP                     | SYSCALL             | BREAK |       |     |      |     |

| Add Subtrac             | t                   |       |       |     |      |     |

| ADD                     | ADDU                | ADDI  | ADDIU | SUB | SUBU |     |

| AND                     | ANDI                | OR    | ORI   | XOR | XORI | NOR |

| Comparison              | type                |       |       |     |      |     |

| SLI                     | SLTI                | SLTU  | SLTIU |     |      |     |

| SLL                     | SLLV                | SRL   | SRLV  | SRA | SRAV |     |

| Integer Multiply Divide |                     |       |       |     |      |     |

| MULT                    | MULTU               | DIV   | DIVU  |     |      |     |

| MFHI                    | MFLO                |       |       |     |      |     |

| I-type Instru           | I-type Instructions |       |       |     |      |     |

| <b>Load Store</b>       | Load Store          |       |       |     |      |     |

| LW            | LB              | LUI     | LH      | LHU     | LBU     |

|---------------|-----------------|---------|---------|---------|---------|

| SW            | SB              | SHW     |         |         |         |

| Branches      |                 |         |         |         |         |

| BEQ           | BNE             |         |         |         |         |

| BGTZ          | BLTZ            | BGEZ    | BLEZ    | BGEZAL  | BLTZAL  |

| Coprocessor   | Instructions    |         |         |         |         |

| Floating Poin | nt Instructions |         |         |         |         |

| ADD.S         | ADD.D           | SUB.S   | SUB.D   |         |         |

| DIV.S         | DIV.D           | MUL.S   | MUL.D   |         |         |

| MOV.S         | MOV.D           |         |         |         |         |

| NGT.S         | NGT.D           | ABS.S   | ABS.D   |         |         |

| EQU.S         | EQU.D           | LT.D    | LT.S    | LE.D    | LE.S    |

| CVT.S.D       | CVT.S.W         | CVT.W.D | CVT.W.S | CVT.D.S | CVT.D.W |

| MTC0          | MFC0            | RFE     |         |         |         |

| MFC1          | MTC1            | CTC1    | CFC1    |         |         |

| LWC1          | SWC1            |         |         |         |         |

Table 1 - Implemented Instruction Set

# 3.3.1.2. Decode

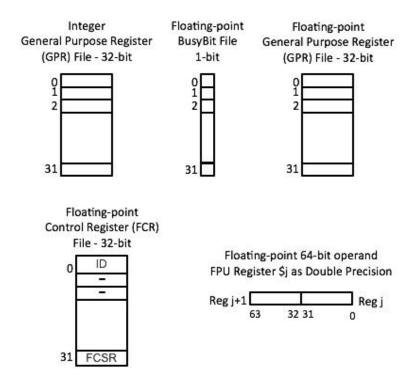

Decode stage has two register files, for integer and floating point numbers.

Figure 3 - Register File Set

This stage also has control unit logic, to evaluate the incoming instructions, and begin preparing the operands for the execute stage. Currently the architecture recognizes 87 instructions, which include both integer, and floating-point instructions. The currently implemented instruction set is illustrated in Table 1. Depending on the control signals coming from the control unit, the operands are prepared from the register file (integer register-file or floating-point register-file).

### 3.3.1.3. Execute

The execute stage consists of a basic ALU for integer add, subtract, shift, logical operations. There is a separate unit for integer multiplication and division. To provide certain degree of flexibility, there are two units of mult-div units placed per core – for high and low performance.

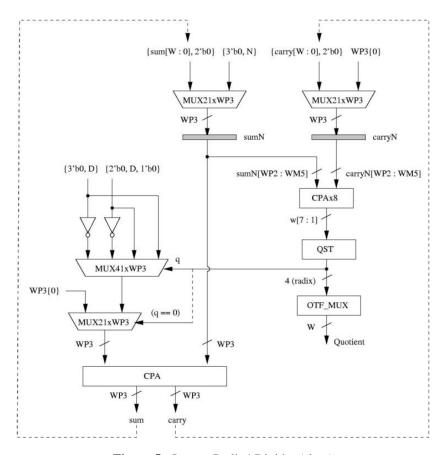

Figure 5 - Integer Radix4 Divider (slow)

The high performance unit uses Radix512 multiplier and Radix16 divider. The low performance unit uses Radix16 multiplier and Radix4 divider. Figure 5 and Figure 4 illustrate the block diagram for slow and fast dividers [12].

While the integer processing units are placed within the core, the floating-point units are placed outside the core and are shared between all four cores through the arbiter logic. For floating point instructions, the operands from the execute stage are routed to the floating point through the arbiter and asynchronous FIFOs.

# 3.3.1.4. Memory

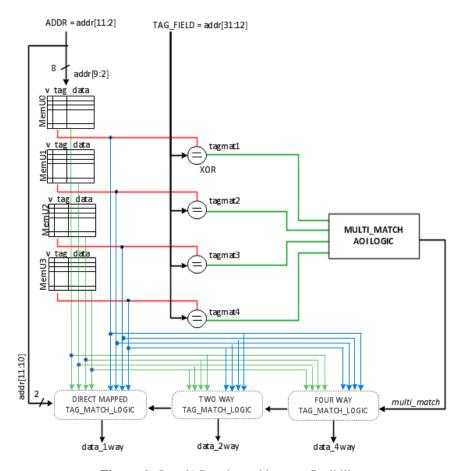

The memory stage implements the other synchronous SRAM, which has a net capacity of 256x4Bx4 (4KB), thus storing 1 word of data in each line of SRAM. As shown in the Figure 6, the Dcache is implemented in 4 units of memory, each having a capacity of 256x4B (1KB).

Figure 6 - Level 1 Dcache architecture flexibility

These four units are arranged to behave as direct mapped, 2way or 4way set associative depending on requirement. The architecture for the memory unit can be decided by selecting the mode in the testbench. When the processor is set in the auto mode, the memory units virtually rearrange themselves and switch between 1way/2way/4way set associative cache system, depending on the signal from the Config Logic. In addition to this flexibility, the Level1 Dcache also implements LRU replacement policy (not shown in the figure) when the memory is configured as 2way or 4way set associative.

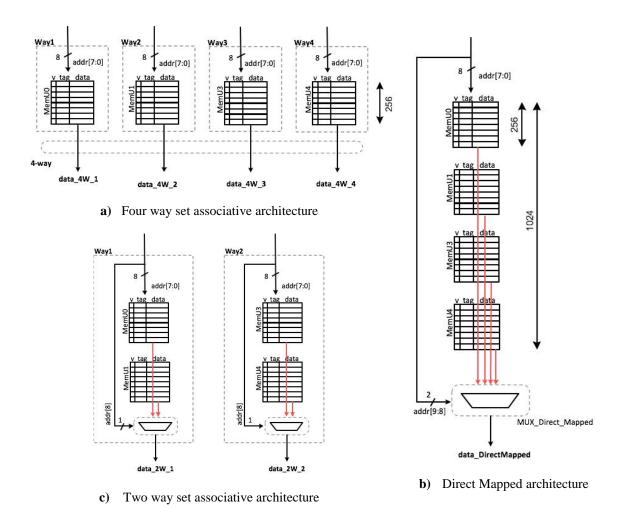

Figure 7 - Memory Subsystem adapted into different architectures

Figure 7 displays the units in their 1way (power mode), 2way and 4way (speed mode) set associative configurations. In all the cases, effective cache size is maintained to be 1kB, thus, needing maximum 10bits for addressing. The number of tag bits needed for tag-match comparisons will differ in each of the modes - 4way needs most bits (22bits), and 1way needs least (20bits). Thus, for this system to work correctly, tag memory stores 22bits, thus satisfying all cases. Besides, another bit is required as the valid bit.

## 3.3.1.4.1. Challenge with adaptive memory subsystem - Implementation of *multi\_match*

While dynamically switching the memory architecture improves the performance when required, this switching can result in limited data loss. No overhead losses are encountered when

the memory adapts into a higher set associative architecture. With memory intensive phases, the memory adapts into a lower set associative architecture, which can result in some initial miss counts due to reduced *atomicity of ways*. This is resulted due to duplicate or invalid data entries identified in the new lower order associative memory system.

Figure 8 - Memory moving from lower to higher set associativity

The following example illustrates this performance loss. The experiment goes through five steps: a) store data A at address 0x200, b) store data B at 0x000, c) change memory architecture, d) store data C at 0x000, e) load data from 0x000. Figure 12 shows the behavior of the memory units when architecture is changed from direct mapped to 2way set associative. From Figure 8 the architecture changes from direct mapped to 2way set associative. After a walkthrough of the five steps in the experiment are complete with the setup, the data can be read without any inconsistencies.

Figure 9 - Memory moving from higher to lower set associativity - encounters invalid entries

Now assume the set-up illustrated in Figure 9, where the memory architecture changes in the other direction, from two-way set associative to direct mapped. In this case, at the end of the 5th step when fetching data from the direct mapped memory two tag matches will be encountered. A technique needs to be implemented so the core does not use the invalid data entries from the cache.

One easy technique to handle this is flushing the cache units when the architecture change is made. Flushing the cache at every change can have very significant impact on the overall performance [13]. The impact is even greater with larger caches. OSCAR implements a technique where such cache entries are invalidated. As and when such invalid entries are identified, *multi\_match* is raised, the entries are invalidated, and a *data\_miss* is issued, and the true data is fetched from DcacheL2.

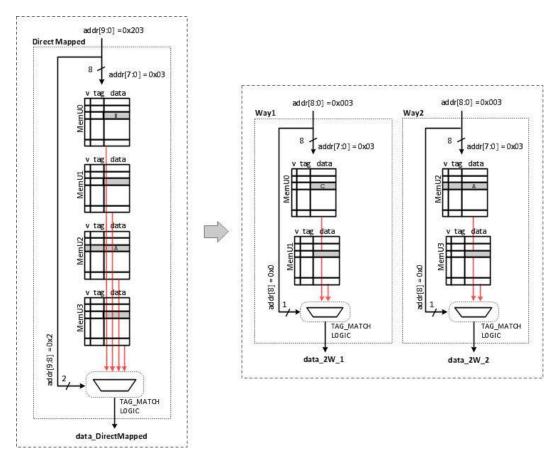

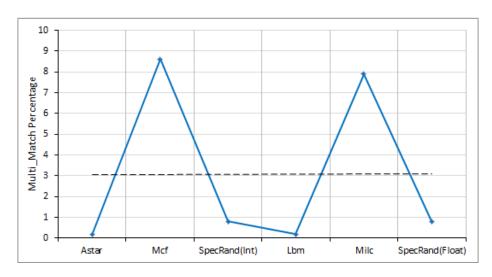

Figure 10 - multi\_match penalty evaluation

The overhead hardware investment for generating multi\_match is fairly compact, and comprises only of XOR gate arrays and and-or based logic. Signal multi\_match is generated only when going from higher to lower order associativity and the data read is erroneously aliased in the four memory units with the new cache system.

It's necessary to gauge the impact of the multi\_match on performance degradation. The frequency of such conflicts occurring and multi\_match being raised vary depending on the type of workload being tested. Figure 10 displays the percentage of data misses generated due to *multi\_match* for various benchmarks, while the cores were programmed in the *auto* mode. The average impact for integer and floating point is around 2.5% - 3%, which is quite less as compared to previous work.

#### 3.3.1.5. Writeback

This stage will write back the data to the decode stage into the integer or floating point register-file. This stage gets data from memory stage (from Level1 Dcache or result from execute stage).

#### 3.3.2. Hazard Unit

Hazard Unit takes care of data forwarding from memory and writeback stages to execute stage. It also takes care of data forwarding from writeback to decode stage. All this forwarding is not only managed for integer type instructions, but also for floating point instructions. This unit also generates stall signals for stages in datapath for all the exception conditions.

## 3.3.3. Coprocessor0

Exception unit determines the cause of exception in the normal flow of the program execution. Exception can be raised due to various reasons like external interrupts, system-call or break instruction, misaligned addresses while load/store, etc. When an exception occurs, Coprocessor0 is programmed to make the core to jump at exception routine, and then return back to the original code.

When any exception occurs, the Coprocessor0 raises a signal (active exception), which is sent to the core. This signal will flush all the stages in the pipeline, and the core is diverted to the address where exception handler is located. After the exception handler is executed, the control is sent back to the return address.

#### 3.4. L2 Data and Instruction Cache

Level2 Dcache is an on-chip resource, which is also shared between all four cores. This stage implements a synchronous 4-way set associative SRAM, which has a net capacity of 1024x4Bx4 (16KB). This hierarchy of memory directly fetches its contents from the main off-chip data memory.

The Level1 Dcache can be at most implemented as a 4way set-associative memory. This is why Level2 Dcache needs to be implemented at-least as 4-way set associative architecture. Level2 Icache is also an on-chip resource, which is shared between all four cores. This stage

implements a synchronous direct-mapped SRAM, which has a net capacity of 1024x16B (16KB), thus storing 4 instructions (4 words) in each set of memory.

This hierarchy of memory directly fetches its contents from the main off-chip instruction memory. Owing to the bigger sizes, these memories are expected to run at clock speeds slower than the core frequency. Thus, these memory units run at slower clock speed (rclk\_2). This is facilitated by the implementation of the asynchronous FIFOs in the arbiter logic.

The main data and instruction memories which are off-chip are expected to run yet slower clocks (rclk\_3). Thus, the interface between the Level2 memory units and the external memories also uses asynchronous FIFOs.

# 3.5. Floating Point Units

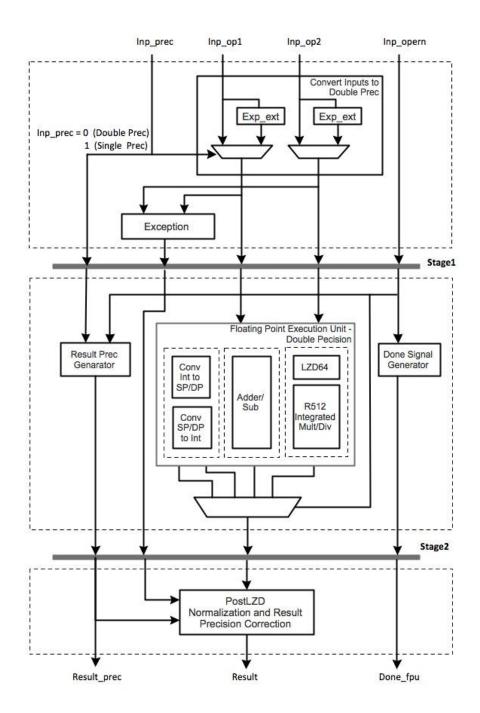

This unit consists of two symmetrical pipelined FPU units. The FPU units will be enabled or disabled depending on the workload from cores. Each pipelined FPU unit as shown in Figure 11 comprises of a Radix512 mult-div unit, adder, and integer-float conversion unit. The computed results are sent back to the decode stage of the core. Each FPU unit is implemented as a three-stage pipeline, which are also buffered:

Stage1 – The operands into FPU unit come from the execute stage of the core, through the arbiter switch. OSCAR supports both single and double floating-point instructions. Thus, for simplicity, the core floating-point operation processing units like adder or mult-div units are configured to process double precision floating point numbers.

Thus, all incoming operands need to go through a unit called 'convert\_inputs' which would convert all single precision floating-point numbers into double precision, and keep the double precision floating-point numbers untouched. After this, all the converted operands, along with the requested operation code must pass into a unit to check for any exceptions. This unit detects if there are any exceptions with the

operands (like all-zero, NaN, +Infinity, -Infinity) or the operation type. Following this, the resultant operands and other control signals are buffered.

Figure 11 - Pipelined Floating Point Unit

**Stage2** - Here, the operands can be passed to various units depending on the operation requested. The units can be mult/div, adder/sub, convert from single/double precision

floating-point to integer, and convert from integer to single/double precision floatingpoint. Each of these units produces a done signal, which indicates that the result has been computed, and is ready to move to Stage3 of the pipeline.

If the desired operation is adder/sub, the operands are directly passed into the unit. The unit evaluates the sign, exponent and mantissa of the result. If the desired result operation is mult/div, then the incoming operands need to go through LZD unit, so there are no leading zeros in the mantissa of the two operands.

So, the two operands are passed through and LZD, and using the counts obtained from the LZDs, the two operands and their exponents are corrected. Thus, the output from LZD is only fed to the mult/div unit, while the inputs of the Stage2 are directly fed to the adder/sub unit.

If the required operation is unary, either convert from/to integer, the incoming operand is directly passed to either of the units. If a floating-point number (originally either single/double precision) is converted into integer, the 64-bit final result will be the 32-bit final integer appended with 32 zeros. If an integer is converted into a floating-point number (finally needed to be single/double precision), the generated result is anyway generated as a double-precision number.

The results are again buffered and passed on to the 3rd pipeline stage.

Stage3 – The final result (if a floating-point number) is again normalized. If the result is an integer, the result from Stage2 is passed on as it is. Now, when dealing with floating-point numbers in Stage2, the numbers are always processed as double-precision numbers.

If the final result after the operation is required to be single precision, the double-precision result is converted into single-precision number appended with 32 zeros. The final result from Stage3 of the pipeline is de-muxed back to the correct core's decoding stage. In the decode stage, the result is either stored in the integer/floating-point reg-file. Even though the FPU unit is located along with the Level2 cache hierarchy, it can still be easily run at the core frequency to enhance performance of the unit even more.

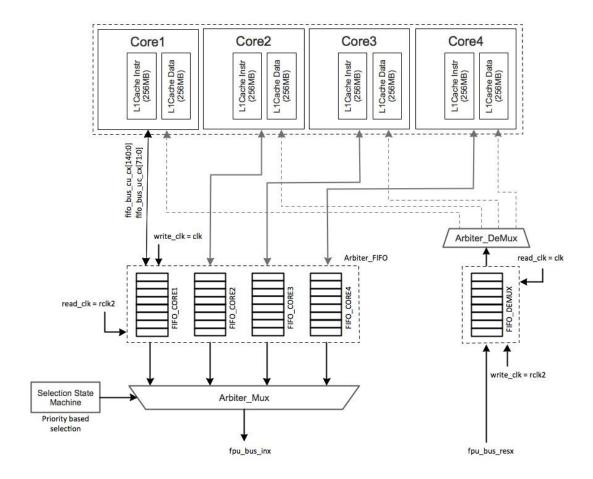

# 3.6. Arbiter Logic

The arbiter logic (Figure 12) is the crossbar logic, which connects four cores to the shared resources on Level2 hierarchy like Level2 Dcache, Level2 Icache, and FPU units. Each core is connected to the arbiter logic through asynchronous FIFO.

| Bus Name         | Width   | Source    | Destination | Description                                  |

|------------------|---------|-----------|-------------|----------------------------------------------|

| imem_l2_cu_cx    | [28:0]  | Core      | Arbiter     | Instruction request from Core-CX to arbiter  |

| imem_l2_uc_cx    | [128:0] | Arbiter   | Core        | Instruction (4words) sent back to Core_CX    |

| fifoout_imem_12  | [30:0]  | Arbiter   | L2 Icache   | Request from selected core sent to L2 Icache |

| instrout_imem_12 | [127:0] | L2 Icache | Arbiter     | Instruction (4words) sent from L2 Icache     |

Table 2 - Arbiter Bus - [Level1\_Icache - Arbiter - Level2\_Icache]

| Bus Name        | Width  | Source    | Destination | Description                                  |

|-----------------|--------|-----------|-------------|----------------------------------------------|

| dmem_12_cu_cx   | [63:0] | Core      | Arbiter     | Data request from Core-CX to arbiter         |

| dmem_12_uc_cx   | [32:0] | Arbiter   | Core        | Data (1word) sent back to Core_CX            |

| fifoout_dmem_l2 | [65:0] | Arbiter   | L2 Dcache   | Request from selected core sent to L2 Dcache |

| rd_dmem_12      | [31:0] | L2 Dcache | Arbiter     | Data (1 words) sent from L2 Dcache           |

Table 3 - Arbiter Bus - [Level1\_Dcache - Arbiter - Level2\_Dcache]

| Bus Name       | Width   | Source   | Destination | Description                                 |

|----------------|---------|----------|-------------|---------------------------------------------|

| fifo_bus_cu_cx | [140:0] | Core     | Arbiter     | FPU request from Core_CX to arbiter         |

| fifo_bus_uc_cx | [71:0]  | Arbiter  | Core        | Result sent back to Core_CX                 |

| fpu_bus_inx    | [143:0] | Arbiter  | FPU Unit    | Request from selected core sent to FPU unit |

| fpu_bus_resx   | [74:0]  | FPU Unit | Arbiter     | Result sent from FPU Unit                   |

Table 4 - Arbiter Bus - [Core\_CX - Arbiter - Floating Point Unit]

Figure 12 - Arbiter Logic

There are three sections in the arbiter logic – for Level2 Dcache, Level2 Icache and FPU units. Each core has three FIFO units connected to each of these three sections. Thus, for four cores, there are total 12 asynchronous FIFOs in the arbiter logic.

For each of the sections, the control is routed to the cores on first-come-first-served basis. In case when there are multiple cores with pending requests, the control is rotated between them in round-robin fashion.

The key feature of the arbiter is the implementation of asynchronous FIFOs, which allow reading and writing at different clock rates. Thus, while the core is running at maximum

frequency (say 500MHz), Level2 hardware (Level2 Dcache, Icache) can run at slower speeds. The busses that flow in and out of arbiter are shown in Table 2, Table 3 and Table 4.

# 3.7. Asynchronous FIFO

The multi-core environment deploys three on-chip clocks – fastest for the core, slower for the Level2 memories, and floating point unit, and the slowest for the interface to the external memory module. Thus, when moving between levels, the data should be synchronized on the destination clock. Three kinds of issues occur with synchronization – metastability, data loss and data incoherency.

One way to do this is by using *multi flip-flop synchronizers*, which help with the metastability issue and work great for synchronizing fewer bits. Although, when multi flip-flop synchronizers are used with data busses, it might result in data loss due to probability of unequal transition times of the bits on the bus. Thus, a second choice of *recirculative MUX-based synchronizers* can be used for busses. In this system, a data enable bit is added to the bus, and this bit is allowed to pass through a multi flip-flop synchronizer. If and when this enable bit is latched on the destination clock, the remaining bus is allowed to be passed through.

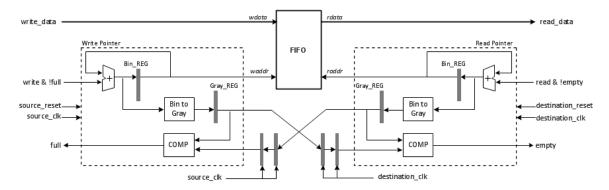

Figure 13 - Asynchronous FIFO with Gray code read/write pointers

Although, these methods are quite robust, they are effective only when the source and the destination clocks are derived from the same root clock. An asynchronous FIFO is rather more robust with asynchronous clocks, or clocks which are not derived from the same root clock.

Also, using gray codes for busses improves the performance of the synchronization circuit, by avoiding false intermediate stages during the synchronization of multiple bits across clock domain. Now, some control signals can be realistically converted as gray codes for the purpose of synchronization, but this cannot be done for all busses.

A simple solution that incorporates the use of asynchronous FIFO and gray codes is to keep the data busses as it is, but implement the read and write pointers using gray codes. Some articles suggest pros and cons of some implementation methods for FIFO based synchronizers. Analysis suggests that read and write pointers directly implemented using gray codes have certain difficulties [14].

Thus, original pointers in the source clock domain FIFO are implemented and maintained in binary, and converted into gray codes, just to facilitate the cross domain synchronization. The gray code pointers are then passed through flip-flops clocked to destination clock, which accomplishes one-way synchronization.

**Figure 14 -** Snooping based cache coherency

Like-wise, gray code pointers from the destination clock domain FIFO are registered at source clock to the source clock domain. These synchronized pointers are compared against the source clock domain pointers to evaluate the full and empty conditions of the FIFO. Figure 13 illustrates the block diagram of the implementation. The sequences of operations for synchronization are as detailed as below:

## 3.8. Data Coherency

One of the dominant aspects of any multi-core architecture is cache coherency across multiple cores. Without cache coherency the cores will be unable to share common memory spaces when executing applications. Over times, three kinds of mechanisms have been developed for data coherency in multi-processor architectures; they are called directory-based coherence, snooping and snarfing. There are pros and cons to all the mechanisms.

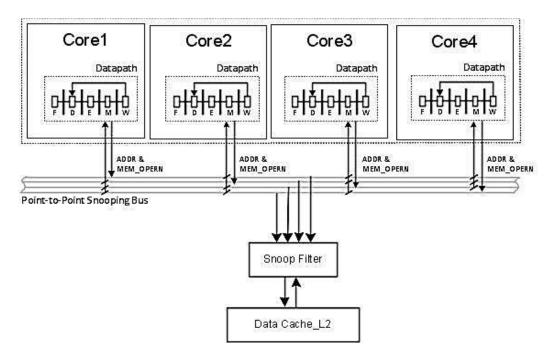

#### 3.8.1. Snooping

This mechanism (Figure 14) is implemented inside each core, and functions in the memory stage of the pipeline. With the snooping mechanism, each core monitors the address lines of other cores, for cache writing operations (store instructions). The core looks out for store operation being performed by other cores on locations that were already previously fetched.

When the core finds such an operation being performed, the core simply invalidates the entry in its own cache, and then continues the normal operation.

This directly implies that this mechanism is quite fast, but requires high bandwidth, since all memory operations need to be broadcasted to all other cores. So, as the number of cores increase, this local traffic also scales up, and will reflect as a significant impact on the cores' metrics.

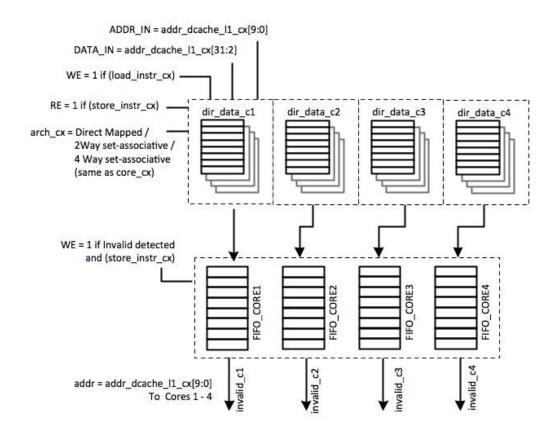

### 3.8.2. Directory-based

The directory structure (Figure 15) functions along-side with Level2 Dcache, and it maintains a record of all entries, which are loaded into Level1 Dcache of all four cores. When a core makes changes to a memory location, which the other cores had also fetched previously, directory structure invalidates the entries for these other cores.

This indicates that this mechanism reduces the local traffic by quite an extent. Also, the mechanism is not as complex as snooping to implement, since all the busses run from the cores to the directory structure logic. This is why, directly structure protocol is more widely used for complex and large multi-core systems.

## 3.8.3. Snarfing

Snarfing is the least preferred choices for implementing cache coherency. This protocol is very similar to snooping. Although, here, instead of just snooping out for addresses, the cores also check for data changes, and then update its outdated copy if needed.

This makes snarfing the worst choice, because of the heavy local traffic (which was also inherent with snooping), but also because of the additional data bus running point-to-point between all cores.

Figure 15 - Directory Structure

Directory structure ensures data coherency in multi-core environment when data space is shared across cores. The directory consists of a structure with 4 memory blocks, each one of which keeps a track of the functioning of L1 Dcache of its respective core. Thus, each one of the four memory units is just as big as L1 Dcache of any core. The outputs of this memory structure are connected to 4 FIFOs, which are connected to the four cores. Functioning of the directory structure can be explained by the following example:

Given condition: L1 Deache is structured as a 4KB direct mapped cache (1024x4B). Thus, the 1st memory block of the directory structure is of the same size and organization (direct mapped).

a. Now, say Core1 has a LW instruction for address 0x00001234. Data gets fetched from main memory into Level2 (if necessary) and finally from Level2 to Level1. While the

- data is being fetched from Level2, an entry is made in 1st memory block at address 0x08D (0x00001234 >> 2 for word offset = 0x0000048D).

- b. Now, after a couple of cycles, Core2 has a SW instruction for the same address, implying that the address space is shared between the two cores. For a core, SW instruction is implemented in a write-through policy. Thus, when the store instruction comes upto the Level2 Dcache, it also makes a check in the directory memory blocks of other cores (1st, 3rd and 4th) to see if some other core has a copy of the data, which should be updated now.

- c. Thus, when it understands that Core1 had fetched the data from the same address, it generates an invalidate signal for the address at Core1's Level1 Dcache. This request for invalidation is stored in a FIFO for Core1. When this request in the FIFO is serviced, it will stall all stages in the pipeline, and also invalidate the memory location in Level1 Dcache of Core1.

If multiple cores has fetched the same data, then there would be invalidates generated for multiple cores at once. Now, as described earlier, Level1 Dcache can be configured to be a direct mapped, 2way or 4way. Also, the memory block in directory structure must be an exact replication of the Level1 Dcache configuration.

Thus, when dynamically the Level1 Dcache changes its architecture from say, direct mapped to 2way set associative, the directory structure also must change its architecture likewise. Also, change of Level1 Dcache memory architecture for all four cores happens independently. Thus, the architecture changes in the four directory structure memory blocks also happen independently of each other.

The directory structure is also implemented as memory blocks similar to Level1 and Level2 caches. Thus, owing to its huge size, the directory structure is also facilitated to run at slower clock speeds as compared to core frequency

#### **CHAPTER IV**

#### TOOL FLOW AND DESIGN METHODOLOGY

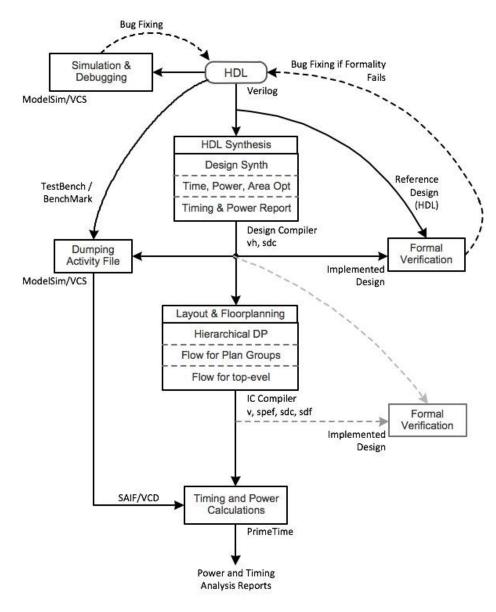

Besides designing the complete architecture, the other challenge during the project was setting up tools to do design testing and hierarchical design planning for synthesis and floorplanning. The tool flow for the project as illustrated in Figure 16 was carried out in 4 major steps: testing and debugging, design synthesis, floorplanning, and final timing and power analysis. ModelSim was used for simulation and debugging. Design Compiler, Design Vision, IC Compiler and Primetime were used from the Synopsys tool-chain for synthesis, floor planning, and timing and power analysis. The standard cell library used for the project was IBM65 low power library provided by Virage Logic. The following flowchart explains the steps for the complete tool flow.

#### 4.1. ModelSim

The highlighting aspect about the project is the ability of the front-end user to analyze the workload at every clock and dynamically configure some design units, so that the architecture delivers better performance in terms of either power or speed.

Figure 16 - Tool Flow Methodology

Many other similar hardware architecture models that have been designed and published have been written on platforms, which make use of high-level languages This may help prove the validity and feasibility of the proposed model; however, the accuracy of the obtained metrics and implementation techniques can be vague. This leads us to the need of a design platform, which should be easy to adapt to, should give the user good control over the design, but should also be realistic to the fabrication technologies. The complete designing of the project was done using RTL, which makes the hardware design very realistic.

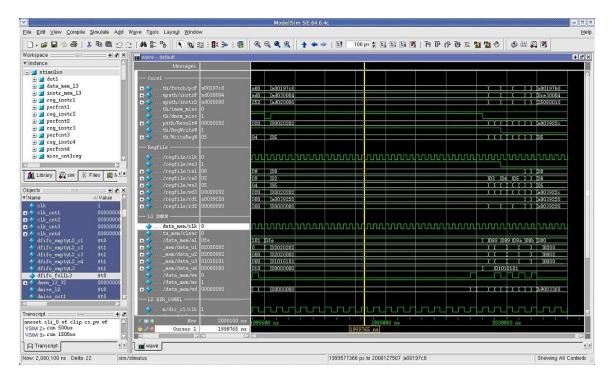

Figure 17 - ModelSim Simulation of RTL

ModelSim [14], which is a cycle-based simulator, has been used for simulation and testing of RTL Verilog code. There are several provisions made in the testbench for the user's benefit for debugging, and gathering run-time test results.

The dumped test results for each core contain information about instruction count, cycle count, information about the architecture configurations, and numbers which indicate nature of incoming workloads. These statistics are recorded in every 'instruction window'. When working with benchmarks, these numbers prove to be very useful to plot graphs for analyzing the architecture with changing workloads.

As mentioned earlier, ModelSim proves very useful when simulating RTL code of the design. Although, to completely verify the functioning of the design, it is also be important to verify that the post-synthesis netlist with timing information also simulates without errors. Figure 17 shows a sample simulation on OSCAR.

### 4.1.1. Unit testing of module

Validating the behavioral functioning of the various units is undoubtedly very important before testing the complete design with heavy benchmark simulations. All the units were individually tested with manually created test codes.

Some codes from the David Harris's test-codes [15] set were also used to validate functioning of the design units. Some other test routines were also designed to test the cache coherency with directory implementation. After several iterations of locating and resolving issues, the code was tested with SPEC benchmarks.

#### 4.1.2. Benchmark Testing

SPEC-CPU suites have benchmarks that can be used to test the CPU performance with applications, which quite resemble the present day workloads for a modern computer system. Thus, many researchers often use SPEC-CPU benchmark suites to evaluate their ideas and results. The project makes used SPEC-CPU2000 and SPEC-CPU2006 benchmarks for performance analysis.

#### 4.1.3. Challenge with Benchmark Testing

Although, when working with benchmarks, it is very important to realize that even the most moderately sized benchmarks usually will have nothing less than 50billion instruction. The benchmarks were initially simulated using the synthesized netlist (which was needed to dump VCD - switching activity file). Although, ModelSim was very slow with the synthesized netlist, and it took the tool around 4-5 hours to run about 1us worth of simulation run-time. Also, besides the run-time, the other problem in keeping up with this technique was the huge space consumed by the VCD files. The estimated memory space needed for a VCD dump was 1GB for every 10us worth of simulation run-time

#### 4.1.4. Solution

This is why the benchmarks need to be run on the RTL code directly, which makes the simulations on ModelSim run reasonably faster. A simulation run-time of 1ms usually will take around 1 hour in real-time. Thus, keeping in mind the size of the design, and the benchmarks, simulations were run with the RTL code, and not on the post-synthesis netlist.

## 4.1.5. Script and Setup

The ModelSim script file (.do) used for the project has been added in Appendix. The instructions for setting the environment and running the script is also given in the Appendix.

## 4.2. Design Compiler

The hierarchical design planning begins at the synthesis level. Design Compiler [16] and Design Vision from Synopsys were used for design synthesis, visually inspecting path groups, critical paths, and estimating timing and power numbers. The basic framework and file structure of the scripts can be downloaded from the Synopsys website.

### 4.2.1. Design Compiler flow

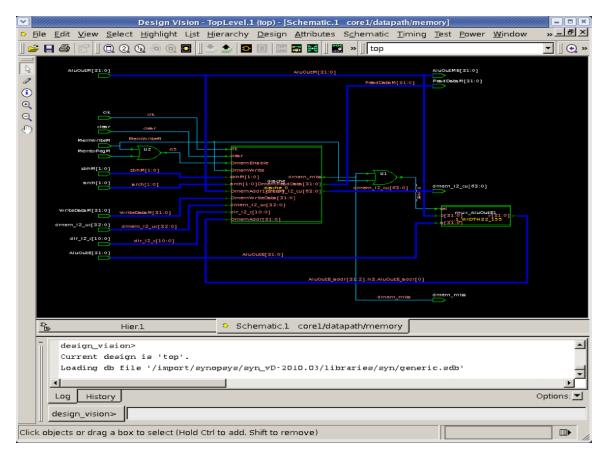

During synthesis, the RTL instantiations are broken down and mapped to the GTEH and DesignWare library components (if needed); the symbols are used extracted from the symbol library. If required, the design schematic can be reviewed using Design Vision to view the path groups for timing calculations, as in Figure 18. After the schematic review, the logic is optimized and the GTECH modules are mapped to technology library components. After the optimizations are done, the tool dumps the final synthesized netlist.

Besides the netlist, the other output files dumped by the tool are SDC (Synopsys Design Constraint), SDF (Standard Delay Format), DDC (Design Database), preliminary area, timing,

and power reports. Commands for dumping all these formats, can be found in the Design Compiler scripts in the Appendix.

## 4.2.2. Design Compiler file formats

The *synthesized netlist* (.vh) generated by the tool is highly influenced by the choice of switches and other related options with the compile commands – *compile* and *compile\_ultra*. The second command is very similar to the 1<sup>st</sup> one, except for some very few changes, which make it a push-button solution for timing-critical, high-performance designs. The second command does automatic ungrouping and boundary optimization across modules.

This can be particularly useful when synthesizing moderately sized designs. However, the user must be particularly careful when applying these switches directly to large designs. Command *compile\_ultra* was used for this project. Also, it's always preferable that the netlist is dumped in hierarchical manner. The commands for this are also mentioned in the scripts in the Appendix.

The SDC (Synopsys Design Constraint) is a Synopsys file format that is used to convey constraint information set by the user in Design Compiler to other compatible Synopsys tools (IC Compiler and PrimeTime). The user can set constraint information related to operating conditions, timing, power and area. Some of the design constraints are technology dependent and are directly taken from the technology library. Some examples include - set\_max\_capacitance, set\_min\_capacitance, set\_max\_fanout, etc. Other constraints can be customized by the user, e.g.: create\_clock, set\_input\_delay, set\_output\_delay, set\_max\_delay, etc. Understanding and setting these constraints with Design Compiler is very important, and can be used to keep a check on the design.

Figure 18 - Design Vision showing the synthesized memory stage from datapath

SDF (Standard Delay Format) is a widely used by EDA tools to pass delay information between multiple tools for static timing analysis. An initial SDF for the synthesized netlist can be generated using Design Compiler, which can then be used with IC Compiler for timing driven placement. Although, if there are timing violations with the layout, the SDF file can be back annotated from the IC Compiler to DC Compiler to revise design synthesis and re-analyze worst case paths.

DDC (Design Database) is an internal Synopsys format, which can be used to view the post-synthesis design graphically using Design Vision. DDC file written from Design Compiler saves all design objects from the design, net names, and design constraints.

## 4.2.3. Script and Setup

Design Compiler needs inputs in the form of HDL code (Verilog). Along with the RTL input, the tool needs the technology library, symbol library and DesignWare library from Synopsys. The symbol and DesignWare libraries are needed if the design should be inspected graphically using Design Vision. The scripts for Design Compiler along with the instructions have been added in Appendix.

Before starting to work with the tool, it's very important that a compile strategy should be decided for a given project. In a top-down strategy, the top-level design and all its modules are compiled all together. Usually the top-down approach is preferred for moderately sized design.

With bottom-up strategy, sub-modules are constrained and synthesized individually. After this, these sub-modules are tagged as 'dont\_touch' when finally the top-level module is being synthesized. While the bottom-up strategy might seem to be quite time-consuming, it's usually preferred for large designs.

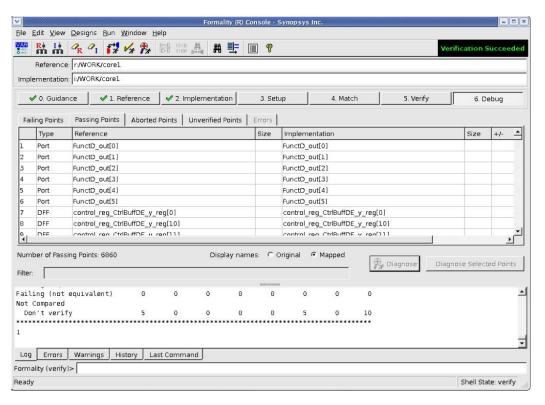

#### 4.3. Formal Verification

When working with Design Compiler, depending on the switches, the tool might try to optimize some logic within modules, and also perform some optimization across hierarchical boundaries. When working with timing-critical designs that are relatively moderate in size, the user can be assured of the quality and validity of the synthesis done by the tool.

This implies that even after optimizations, the synthesized netlist does not behave differently than actual RTL. To evaluate this, rigorous simulation tests need to be performed on the synthesized netlist with huge input vectors.

#### 4.3.1. Need for Formal Verification

For average sized designs, running post-synthesis simulations on cycle-based simulators such as ModelSim/VCS can also validate the same. This kind of testing becomes very tedious, time consuming and creates bottlenecks with large design, such as this project.

Figure 19 - Formality - Successful Verification with post-synthesis netlist for Core1

These bottlenecks are usually cased due to heavy memory requirements of the simulation tool, which directly makes the process sluggish. A better way to do the same verification is to use a Synopsys tool called Formality [17]. The inputs needed for the tool are the original RTL code, the synthesized netlist, and technology libraries for mapping the two netlists. The advantage of using the tool is that it generates detailed reports for all the differences between the two netlists.

Even though the tool does not need any input vectors like the conventional cycle-based simulators, the results obtained from Formality can be claimed to be dependable. This implies

only when rigorous testing has been performed on the original RTL code using simulators like ModelSim/VCS.

### 4.3.2. Script and Setup

Formality is a very easy and simple yet very resourceful tool, which can help save huge amount of reworks.

Knowing that the design is huge in size, this is especially important in the early design stages, since all the following stages are highly time-consuming. With Formality, the original RTL Verilog is called as the *reference design* and the synthesized netlist (in this case coming from the Design Compiler) is called as the *implemented design*. Along with designs, the technology libraries used for the synthesis also need to be imported. Following this, the two netlists are compared for the *match points*.

Once the match points are set, the tool is also set to run the verification. Once the verification is run, the tool tries to equate all the logic equivalence between the reference and the implemented netlists. After this, the reports of the verification stage can provide an insight into the differences if any.

It is important to know that the implemented design for Formality can also be taken from the netlist after the floorplanning is complete, that is the netlist dumped by IC Compiler. This netlist of course should be dumped without the physical only cells (such as tie-cells, internal diodes, etc.). The script and instructions for the tool have been given in the Appendix.

# 4.4. IC Compiler

IC Compiler [18] takes inputs from the Design Compiler that basically are the synthesized netlist, and preliminary timing information. The floor planning for large hierarchical designs can be a very time-consuming task.

## 4.4.1. IC Compiler flow

Design planning is the first and most important task in hierarchical floorplanning, especially when dealing with large designs. When doing design planning for hierarchical designs, it's best to start with the hierarchical flow scripts available on the Synopsys website, as a basic framework. The scripts should definitely be customized to suit the project requirements.

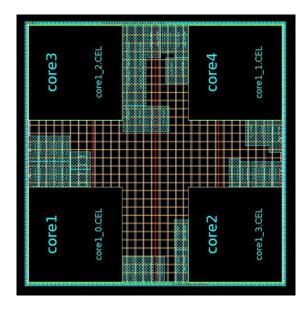

## 4.4.1.1. Need for Hierarchical design methodology

The procedure starts with the identification of the potential hierarchies inside top-level module that can be converted into design plan-groups. Each of these plan-groups or sub-blocks is processed separately and will later be treated as soft macros inside the main top-level module. Thus, in the design flow, complete PnR routine takes place sequentially for all the sub-modules, and then finally for the top-level.

The hierarchical design planning serves multiple goals. One of the important advantages is that, the tool does not have to work with the complete design in memory. Thus, even if the number of PnR iterations increase with the number of design plan-groups, the process becomes inherently faster. Also, using hierarchical methodology allows the user to make late minor changes to just one of the plan-groups. Thus, again, instead of running IC Compiler for the complete design, just the particular sub-module can be update in the design.

## 4.4.1.2. Design flow for hierarchical design planning

The process is divided into three phases: design planning and committing plan-groups, running IC Compiler flow on all the plan-groups, and finally running IC Compiler flow on the top-level module. The user can consider some factors while deciding on plan-groups. Plan groups can be made depending on the functionality of the modules, e.g.: in case of the multi-core project,

it would make a lot of sense to prepare plan-groups for the cores, the directory structure, and the FPU units. Another factor could be a module, which is likely to undergo design changes.

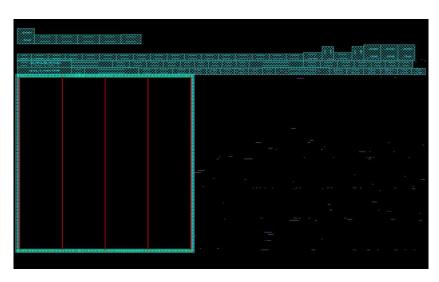

## 4.4.1.2.1. Phase 1 - Design planning and commit Plan-groups

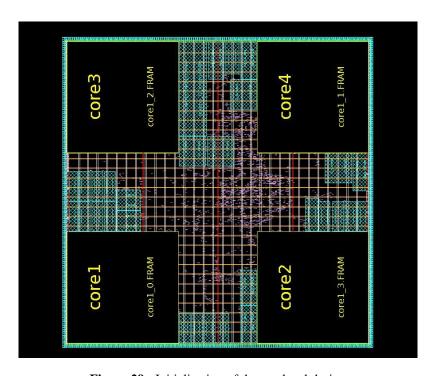

After the potential plan groups have been decided and defined by the user in the script (common\_setup.tcl), the floorplan needs to be initialized first with power planning for the chip. Figure 12-15 shows some snapshots from Phase 1.

Figure 20 - Initialize floorplan for complete design

Figure 21 – Creating plan-groups for hierarchical sub-modules

After this, tentatively sized plan groups are made as per requirements. These plan-groups are then placed inside the floorplan along with their hard-macros (memory blocks), if any. The tool also needs to check the routability within the plan-group. If the design and route congestion is found to be within limits, pin assignments can then be made on the outer edge of the plan groups.

Figure 22 – Placement of plan-groups along with hard macros

Figure 23 - Committing final plan-groups

Before committing, timing and area budgeting is done on the plan-groups. This ensures that the connections and congestion between these plan-groups is manageable in the top-level module. After this is done, the plan-groups can finally be committed. The script creates separate working folders, one for each plan-group.

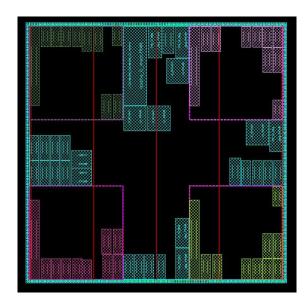

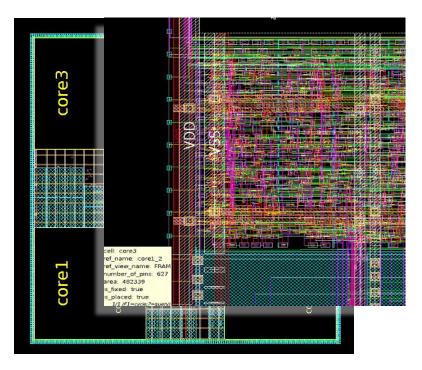

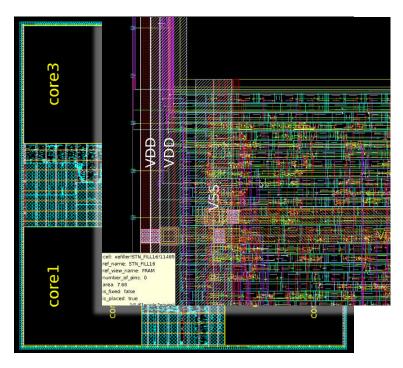

### 4.4.1.2.2. Phase 2 - Design flow for all Plan-groups

In this phase, the user must navigate inside each of the folders, and perform the complete design flow for all the plan-groups from cell placement to post-route, and then chip-finish. Below are some of the important snapshots of the flow. Figure 16-20 show some snapshots related to Phase 2.

Figure 24 - Plan-group after placement

Figure 25 - Zoom-in on the CTS stage showing clock routed on M3-M4

Figure 26 - Post-route Layout

Figure 27 - Global Routing Congestion for plan-group

Figure 28 - Chip Finish for plan-group

During this entire flow, Milkyway cells are saved for each step is saved in the work directory. This way, at the end of this phase, all the subgroups are fully ready with their Milkyway libraries, which can be readily used with the top-level module.

## 4.4.1.2.3. Phase 3 - Design flow for top-level module

Even if the majority portions of the design were divided into plan-groups, the design flow would still be needed for the top-level design. The only difference here is that the plan-groups for which the flow has already been done are now declared as macros with top-level design (for which we already have the Milkyway cells). Figure 21-24 show figures related to Phase 3.

Figure 29 - Initialization of the top-level design

Figure 30 - Post Route of Top-level design

The final chip\_finish script will generate the final GDSII, SDC, SDF, SPEF (Standard Parasitic Extraction Format), and final netlist (with and without physical cells).

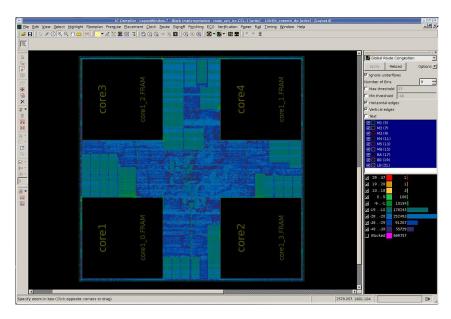

Figure 31 - Global Routing Congestion for Top-level design

Figure 32 - Chip Finish of Top-level design

The netlist without the physical cells can be verified against the post-synthesis netlist (from Design Compiler) using tools like Formality. This ensures the correctness of the layout against the original netlist.

The post-layout netlist can also be used with the SDF (timing information from layout) can be used to evaluate *post-layout simulations*, if needed. The post-layout netlist and SPEF (RC parasitic extraction from layout) along with some activity file VCD (Value Change Dump) / SAIF (Switching Activity Interchange Format) can be used with Power Compiler to evaluate *post-layout power numbers*. Power Compiler can be invoked from DC Compiler, IC Compiler, Primetime, and Formality. [19]

Even after all the care taken, timing violations can still be encountered during any stage of the flow in 2nd or 3rd phase. In these cases, there are possibly two options – either change can

be made in the RTL for the critical path(s), or the design constraints can be checked with the Design Compiler.

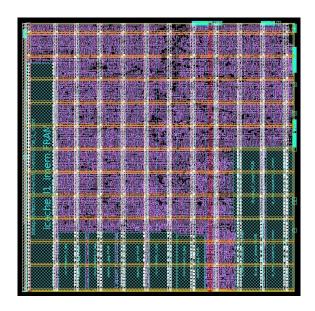

## 4.4.1.3. Graphical Analysis of Floorplan

Besides all the text reports generated by the IC Compiler, the final floorplan congestion can be graphically visualized in terms of cell density, and pin density. This graphical analysis is called 'Map Mode'. The user can customize number of bins and thresholds for the color-coded bins. Figures 26-27 show snapshots for the graphical analysis of cell and pin densities.

Various hierarchy levels can also be explored using a tool called Hierarchy browser that is built inside IC Compiler. Using Hierarchy browser, all or just some selected hierarchical cells, two examples of which are as shown in the Figures28-29. The Figures30 shows the location of top-level architecture units in the finalized floorplan.

Figure 33 - Pin Density Analysis (Map Mode)

Figure 34 - Cell Density Analysis (Map Mode)

Figure 35 - Color coded hierarchy across top level and all plan groups

Figure 36 - Color-coded hierarchies inside cores

Figure 37 - Locations of architecture unit in top-level floorplan

## 4.4.2. Script and Setup

The basic framework and file structure of the scripts can be downloaded from the Synopsys website. These scripts provide a good start-up scripts set, but do not cover all commands or procedures that might be needed for a project. But the scripts can be easily modified to add custom codes.

Besides the basic inputs fetched from Design Compiler, IC Compiler needs some more technology related inputs. Most of these additional inputs are same as the ones, which were needed for Design Compiler. The other files needed by IC Compiler are Milkyway technology file (.tf), and TLUP (min and max). These files provide IC Compiler with all the information needed for doing the layout of the synthesized design. The scripts for IC Compiler along with the instructions have been added in Appendix.

#### CHAPTER V

#### **CONCLUSION**

The aim of the project is to create a realistic platform for development of MIPS-based multicore architectures, which could be adopted as a good platform for academic development. Unlike the software simulators, which provide very high level of abstraction, OSCAR (OSU Simulation for Computer Architecture Research) provides a very truthful insight into the accurate hardware investment. The project implements an RTL based structural model, which is completely synthesizable. The design can be used to perform timing and power analysis on all hierarchical modules, including the 3<sup>rd</sup> party memory macros.

Besides the direct utilization of this platform for academic purposes, the design basically offers a solid framework. The project implements four dynamically configurable MIPS-like cores, with shared memory resources and data coherency protocol. The table-driven approach improves performance by changing architecture on-the-fly using feedbacks from performance counters

The concept of the dynamically changing architecture to save power and also improving performance is very powerful.

However, there is a lot of scope for potential growth in this project, which will make the framework even robust and versatile. The cache blocks can be implemented with protocols such as MESI, MOESI (AMD), MESIF (Intel). Implementing branch prediction techniques will reflect in performance increase when testing with realistic workloads like the SPEC benchmarks.

For Level2 cache system, several other techniques, like *cache morphing* [20] can be used to improve performance of the shared memory resource. Implementing banked memories for Level2 cache can also help improve latencies.

#### REFERENCES

- [1] S. Microsystems, "OpenSPARC T1 Microarchitecture Specification".

- [2] T. Austin, "SimpleScalar LLC," [Online]. Available: http://www.simplescalar.com/.

- [3] J. Larus, "SPIM A MIPS32 Simulator," [Online]. Available: http://pages.cs.wisc.edu/~larus/spim.html.

- [4] "Wind River Simics," [Online]. Available: http://www.windriver.com/products/simics/.

- [5] J. Montanaro, R. Witek, K. Anne, A. Black, E. Cooper, D. Dobberpuhl, P. Donahue, J. Eno, W. Hoeppner, D. Kruckemyer, T. Lee, P. Lin, L. Madden, D. Murray, M. Pearce, S. Santhanam, K. Snyder, R. Stehpany and S. Thierauf, "A 160-MHz, 32-b, 0.5-W CMOS RISC microprocessor," *IEEE Journal of Solid-State Circuits*, vol. 31, no. 11, pp. 1703 1714, 1996.

- [6] "International Technology Roadmap for Semiconductors (ITRS)," 2007.

- [7] D. Albonesi, "Selective cache ways: on-demand cache resource allocation," in *32nd Annual International Symposium on Microarchitecture (MICRO)*, 1999.

- [8] G. Bournoutian and A. Orailoglu, "Dynamic, non-linear cache architecture for power-sensitive mobile processors," in *Hardware/Software Codesign and System Synthesis* (CODES+ISSS), 2010 IEEE/ACM/IFIP International Conference on, 2010.

- [9] V. Kontorinis, A. Shayan, R. Kumar and D. Tullsen, "Reducing peak power with a table-driven adaptive processor core," in *Microarchitecture*, 2009. MICRO-42. 42nd Annual IEEE/ACM International Symposium on, 2009.

- [10] D. Benitez, J. Moure, D. Rexachs and E. Luque, "A reconfigurable cache memory with heterogeneous banks," in *Design, Automation Test in Europe Conference Exhibition (DATE)*,

2010.

- [11] H. Hanson, M. Hrishikesh, V. Agarwal, S. Keckler and D. Burger, "Static energy reduction techniques for microprocessor caches," *Very Large Scale Integration (VLSI) Systems, IEEE Transactions on*, vol. 11, no. 3, pp. 303-313, june 2003.

- [12] J. E. Stine, A. Phadke and S. Tike, "A recursive-divide architecture for multiplication and division," in 2011 IEEE International Symposium on Circuits and Systems (ISCAS), 2011.

- [13] A. Agarwal, J. Hennessy and M. Horowitz, "Cache performance of operating system and multiprogramming workloads," *ACM Transactions on Computer Systems*, pp. 393-431, Nov 1988.

- [14] C. E. Cummings, "Simulation and Synthesis Techniques for Asynchronous FIFO Design," in *Synopsys Users Group (SNUG)*, 2002.

- [15] M. Graphics, "ModelSim Manual," [Online].

- [16] HMC-MIPS. [Online]. Available: http://code.google.com/p/hmc-mips/.

- [17] Synopsys, "Design Compiler User Guide," [Online].

- [18] Synopsys, "Formality User Guide," [Online].

- [19] Synopsys, "IC Compiler Design Planning User Guide," [Online].

- [20] Synopsys, "PrimeTime User Guide," [Online].