# PERFORMANCE AND MICROARCHITECUTRAL ANALYSIS FOR IMAGE QUALITY ASSESMENT ALGORITHMS

By

### SIDDHARTH K. SHAH

Bachelor of Engineering

University of Pune

Pune, Maharashtra, India

2009

Submitted to the Faculty of the GraduateCollege of the OklahomaStateUniversity in partial fulfillment of the requirements for the Degree of MASTER OF SCIENCE December, 2012

# PERFORMANCE AND MICROARCHITECURAL ANALYSIS FOR IMAGE QUALITY ASSESMENT ALGORITHMS

Thesis Approved:

Dr. Sohum Sohoni

ThesisAdvisor

Dr. Damon Chandler

Dr. John Acken

#### ACKNOWLEDGMENTS

I would like to thank my Adviser, Dr. Sohum Sohoni for his help and support in the work presented in this thesis. He has been a great advisor and guide. I would also like to thank my lab mates Randal Allison for proof reading my thesis document and Wira Mulia for making me understand some important concepts.

I would also like to thank Dr. Damon Chandler and Thien for their research on Image Quality Assessment without them this thesis would not have been possible.

I would like to thank Dr. John Acken for his comments and guidelines for this thesis document. A special thanks to the researchers and contributors on the Intel VTune Amplifier XE forum for patiently answering and commenting on my queries about the tool and performance analysis.

Lastly, I want to thank my parents, Reema and all my other friends who have always been a driving force in my life.

#### Name: SIDDHARTH K. SHAH

#### Date of Degree: DECEMBER, 2012

### Title of Study: PERFORMANCE AND MICROARCHITECTURAL ANALYSIS OF IMAGE QUALITY ASSESSMENT ALGORITHMS

#### Major Field: ELECTRICAL ENGINEERING

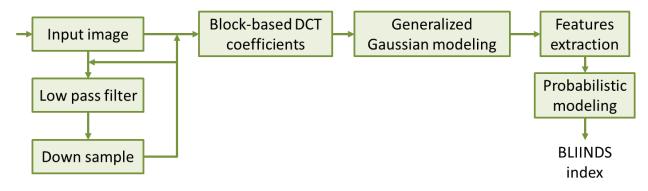

This thesis presents performance analysis for five matured Image Quality Assessment algorithms: VSNR, MAD, MSSIM, BLIINDS, and VIF. The performance parameter considered is execution time. First, we conduct hotspot analysis to find the most time consuming sections for the five algorithms. Second, Microarchitecural analysis is conducted to analyze the behavior of the algorithms for Intel's sandy Bridge microarchitecture and find architectural bottlenecks. The current research for improving performance for IQA algorithms is based on advanced signal processing techniques. This research focuses on the behavior of these algorithms with underlying hardware and architecture. We study the behavior of these algorithms with the architectural resources and propose techniques to improve performance using coding techniques that exploit the hardware resources and consequently improve the execution time and computational performance. Along, with software tuning methods, we also propose a generic custom IQA hardware engine based on the microarchitectural analysis and the behavior of these 5 IQA algorithms with the underlying microarchitectural resources.

## TABLE OF CONTENTS

| Chapter                                                                                                                                                                   | Page                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| I. INTRODUCTION                                                                                                                                                           | 1                                      |

| <ul> <li>1.1 Background on Image Quality Assessment Algorithms</li> <li>1.2 Signal Processing based Methodology and Techniques</li> <li>1.3 Research Objectives</li></ul> | 2<br>5<br>6<br>6                       |

| II. ANALYSIS METHODLOGY                                                                                                                                                   | 10                                     |

| <ul> <li>2.1 Experimental Setup</li> <li>2.2 Performance Profiling Methodolgy</li></ul>                                                                                   | 11<br>12<br>12<br>12<br>12<br>12<br>12 |

| III. VSNR                                                                                                                                                                 | 18                                     |

| <ul> <li>3.1 Overview</li> <li>3.2 Implementation Specifics and Details</li> <li>3.3 Hotspot Analysis</li> <li>3.4 Microarchitectural Analysis</li> </ul>                 | 19<br>20                               |

| Chapter                                             | Page |

|-----------------------------------------------------|------|

| IV. MAD                                             | 30   |

| 4.1 Overview                                        | 30   |

| 4.2 Implementation Specifics and Details            | 31   |

| 4.3 Hotspot Analysis                                |      |

| 4.4 Microarchitectural Analysis                     | 34   |

| V. MS-SSIM                                          | 39   |

| 5.1 Overview                                        | 39   |

| 5.2 Implementation Specifics and Details            | 40   |

| 5.3 Hotspot Analysis                                | 40   |

| 5.4 Microarchitectural Analysis                     | 43   |

| VI. BLIINDS                                         | 48   |

| 6.1 Overview                                        | 48   |

| 6.2 Implementation Specifics and Details            | 49   |

| 6.3 Hotspot Analysis                                | 50   |

| 6.4 Microarchitectural Analysis                     | 53   |

| VII. VIF                                            | 56   |

| 7.1 Overview                                        | 56   |

| 7.2 Implementation Specifics and Details            |      |

| 7.3 Hotspot Analysis                                | 58   |

| 7.4 Microarchitectural Analysis                     | 60   |

| VIII. DISCUSSION AND RECOMMENDATIONS                | 63   |

| 8.1 Memory Bottlenecks                              | 63   |

| 8.2 Core Bottlenecks                                | 68   |

| 8.3 Custom Image Quality Assessment Hardware Engine | 71   |

| REFERENCES                                          | 76   |

## LIST OF TABLES

| Table Page                                    |

|-----------------------------------------------|

| 1 Details: Subject Images and Analysis Setup9 |

| 2 Hardware Platform Specifications10          |

| 3 Features: Intel VTune Amplifier XE13        |

| 4 General Exploration Metrics17               |

| 5 Hotspot Analysis VSNR                       |

| 6 Microarchitectural Analysis VSNR23          |

| 7 Hotspot Analysis MAD32                      |

| 8 Microarchitectural Analysis MAD35           |

| 9 Hotspot Analysis MS-SSIM40                  |

| 10Microarchitectural Analysis MS-SSIM43       |

| 11 Hotspot Analysis BLIINDS50                 |

| 12 Microarchitectural Analysis BLIINDS53      |

| 13 Hotspot Analysis VIF                       |

| 14 Microarchitectural Analysis VIF60          |

| 15 Sample codes for cache utilization65       |

| 16 Mask bit for DAZ and FTZ modes | 71 |

|-----------------------------------|----|

|-----------------------------------|----|

## LIST OF FIGURES

| Figure Page                                                                 |

|-----------------------------------------------------------------------------|

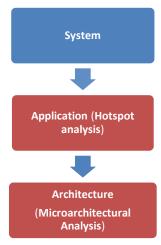

| 1. Top down Methodology for tuning12                                        |

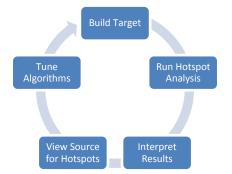

| 2. Hotspot analysis process and tuning                                      |

| 3. Summary window hotspot analysis                                          |

| 4. Bottom up pane hotspot analysis                                          |

| 5. Top down pane hotspot analysis16                                         |

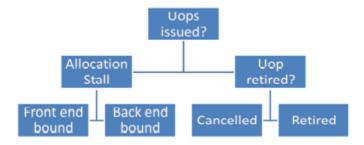

| 6. Retired pipeline slots categorization                                    |

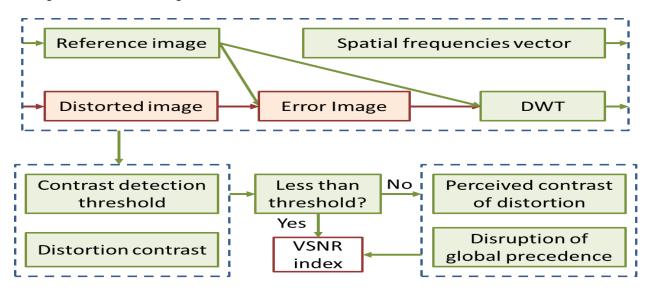

| 7. Block diagram for VNSR21                                                 |

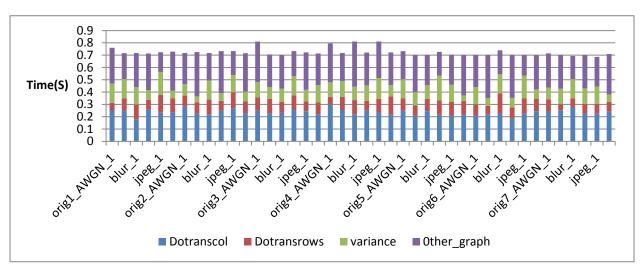

| 8. Execution time plot for all subjects Images: VSNR                        |

| 9. Average execution time varying across different distortion types: VSNR22 |

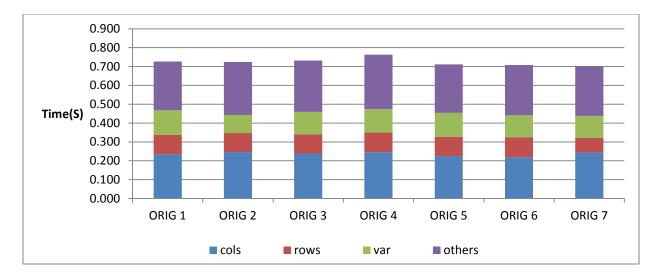

| 10. Average execution time varying across different image contents: VSNR27  |

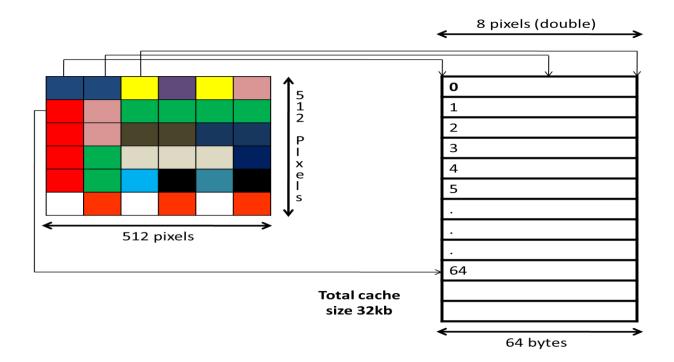

| 11. Image data mapped to cache memory locations                             |

| 12. VSNR blocks mapped with hardware bottlenecks                            |

| 13. Block diagram for MAD                                                   |

| 14. Execution time plot for all subjects Images: MAD                        |

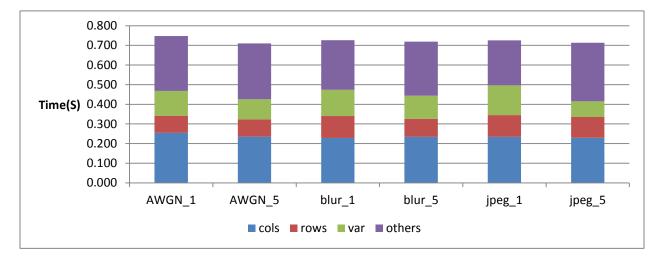

| 15. Average execution time varying across different distortion types: MAD34 |

| 16. Average execution time varying across different image contents: MAD         |

|---------------------------------------------------------------------------------|

| 17. MAD blocks mapped with hardware bottlenecks                                 |

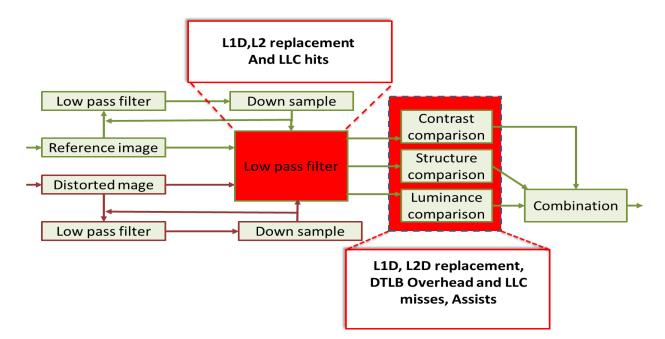

| 18. Block diagram for MS-SSIM41                                                 |

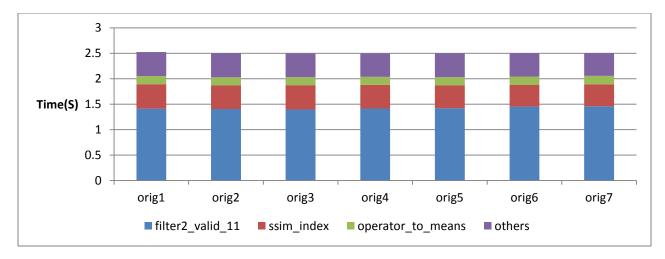

| 19. Execution time plot for all subjects Images: MS-SSIM                        |

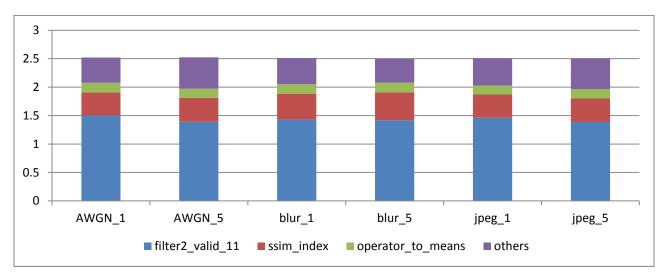

| 20. Average execution time varying across different distortion types: MS-SSIM42 |

| 21. Average execution time varying across different image contents: MS-SSIM47   |

| 22. MS-SSIM blocks mapped with hardware bottlenecks                             |

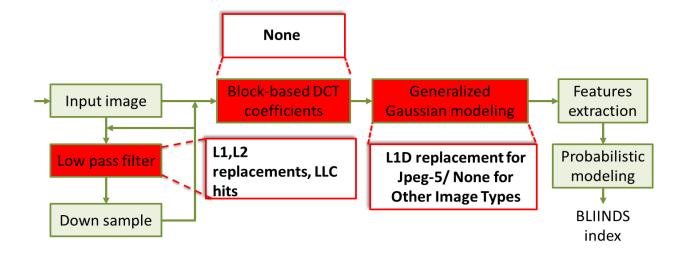

| 23. Block diagram for BLIINDS                                                   |

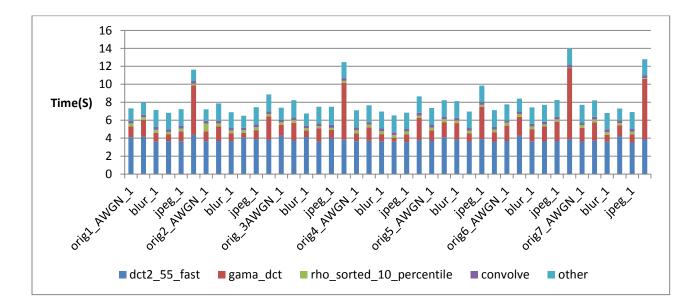

| 24. Execution time plot for all subjects Images: BLIINDS                        |

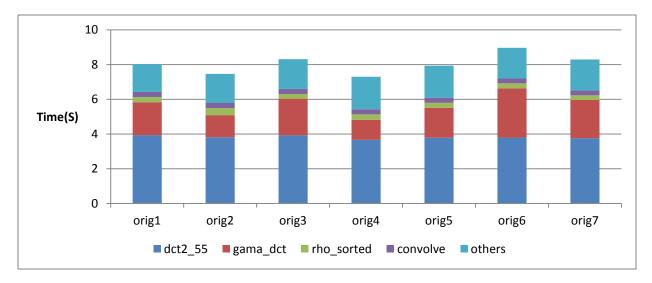

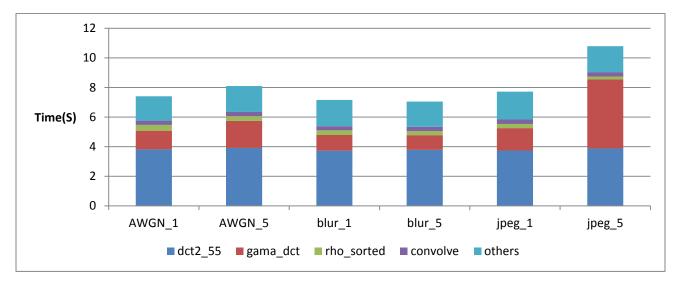

| 25. Average execution time varying across different distortion types: BLIINDS52 |

| 26. Average execution time varying across different image contents: BLIINDS55   |

| 27. BLIINDS blocks mapped with hardware bottlenecks                             |

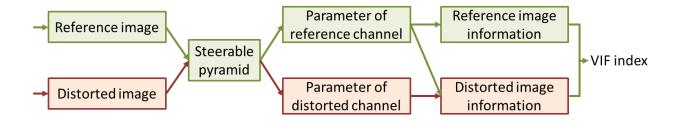

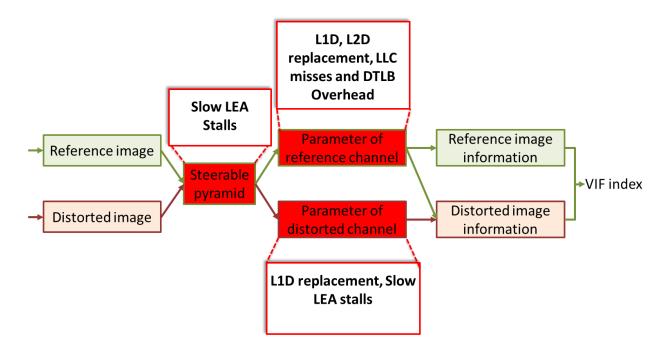

| 28. Block diagram for VIF                                                       |

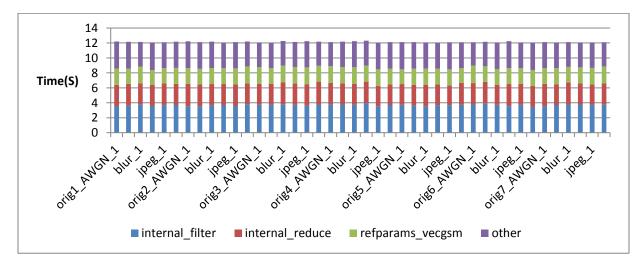

| 29. Execution time plot for all subjects Images: VIF                            |

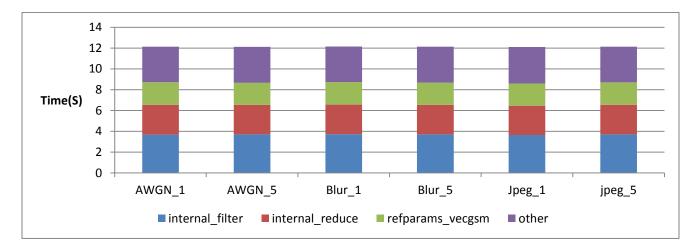

| 30. Average execution time varying across different distortion types: VIF59     |

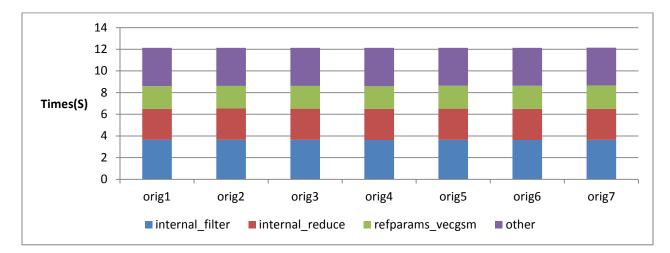

| 31. Average execution time varying across different image contents: VIF62       |

| 32. VIF blocks mapped with hardware bottlenecks                                 |

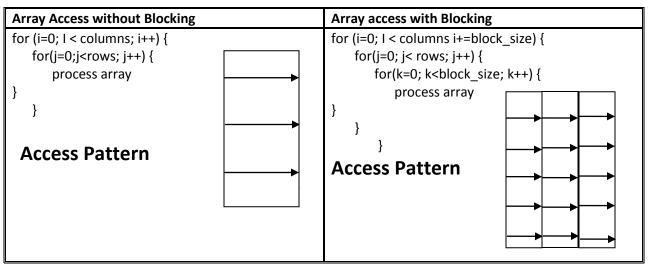

| 33. Example of Cache blocking  | 69 |

|--------------------------------|----|

|                                |    |

|                                |    |

| 34. Custom IQA hardware engine | 72 |

|                                |    |

#### CHAPTER I

#### **INTRODUCTION**

This research thesis is based on performance analysis of the Image Quality Assessment (IQA) algorithms. Image Quality Assessment is a technique to automatically judge visual quality of an image. IQA plays a very important role in numerous image processing applications. Currently, research in IQA spans two different domains. First, developing better IQA algorithms which agree more closely with the human visual system. Second, improving the computational performance and execution time for the current matured IQA algorithms. This thesis research focuses on the later research area.

This chapter introduces several aspects of the research work, namely a brief background discussion on the Image Quality Assessment (IQA) algorithms, current state of research in IQA, objectives and goals for the research. Section 1.1 presents a brief introduction to IQA and current state of research in its realm. Further, Section 1.2 discusses the current signal processing techniques and methodologies used by researcher to improve computational performance and execution time for the various IQA algorithms. Section 1.3 discusses the key issues the research addresses. Finally, section 1.4 gives an overview of the experimental setup and methodology for performance profiling.

#### 1.1 Background on Image Quality Assessment Algorithms

The visual quality of a digital image can degrade when they are captured, stored (compressed), transmitted or processed. Such degradation can change the appearance of an image, thus it is important to judge an image's visual quality before it is displayed to or used by the consumer. Many algorithms have been developed since the origin of research on IQA. IQA algorithms aim to provide an automated means of judging image's visual quality which is concurrent with human judgments of quality. Currently, IQA research is an active sub discipline of image processing and benefits a wide variety of applications

ranging from image compression (e.g., [1]–[3]), to denoising (e.g., [4]), to predicting intelligibility in sign language video [5].

There are currently two categories of IQA algorithms. The first is full reference IQA algorithms, where a reference image has a good/acceptable visual quality and a subject image (distorted version) whose visual quality needs to be judged is used. The output of such algorithms is either a scalar value denoting the overall visual quality or a spatial map estimating the local quality of each image region (e.g., [6]–[34]). More recently, researchers have begun to develop a second category of IQA algorithms. These are *no-reference* or *reduced-reference* algorithms. These algorithms estimate visual quality of an image without using a reference image or just use partial information about the reference image (no-reference IQA; e.g., [35]–[39]), (reduced-reference IQA; e.g., [40]–[45]).

With consistent research in IQA, all three types of IQA algorithms have been able to predict the visual quality of an image efficiently which agrees with human judgments of an image's visual quality. Some of the best-performing full-reference algorithms such as MS-SSIM [29], VIF [30], and MAD [34] estimate the visual quality of the image that highly correlates with human ratings of quality, typically yielding Spearman and Pearson correlation coefficients (measure of dependence between two variables reference and subject image in our case) in excess of 0.9. Research in no-reference and reduced-reference IQA is much less mature; but, recent methods such as DIIVINE [37], BRISQUE [38], and BLIINDS-II [39], yield quality estimates which also highly correlate with human ratings of quality.

# 1.2 Signal Processing based methodologies and techniques for improving computational performance

From a signal-processing viewpoint, it seems that the majority of computation and runtime are likely to occur in two key stages, employed by most IQA algorithms: (1) local frequency-based decompositions of the input image(s); and (2) local statistical computations on the frequency coefficients. The local frequency-based decomposition stage would require higher computation power and memory bandwidth

as well. Particularly, when a large number of frequency bands are analyzed, and when the decomposition must be applied to the image as a whole. On the other hand, the statistical computation on frequency coefficients would seem to require higher computation power, mainly when multiple statistical computations are computed for each local region of coefficients. For example, in MS-SSIM [29] an image is decomposed into different scales, and for each block of coefficients local image statistics are computed (via a sliding window). In VIF [30], wavelet subband covariances can be computed via a block-based or overlapping block-based approach. In MAD [34], variances, skewnessness, and kurtoses of log-Gabor coefficients are also computed for overlapping blocks in each subband. These approaches mimic the cortical processing in the human visual system (HVS) for some aspects. The statistics of local responses of neurons in primary visual cortex (modeled as coefficients) are computed and compared in higher-level visual areas. But still unlike the HVS, most modern computing platforms lack dedicated hardware for computing the coefficients and their local statistics.

The IQA algorithms are extensive used in image compression and computer vision. Consequently, a considerable amount of research focus has been on accelerating two-dimensional image transforms which provide local frequency-based decompositions which is one of the major operations in IQA that requires high computation power and memory bandwidth. For example, using variations of the same techniques used in the Fast Fourier Transform (FFT) the discrete cosine transform (DCT) has been accelerated at the algorithm level (e.g., [48]). Also, there has been significant improvement in performance by exploiting various algebraic and structural properties of the transform, e.g., via recursion [49], lifting [50], matrix factorization [51], cyclic convolution [52], and many other techniques (see [53] for a review). Along with techniques at the algorithm level, many techniques for hardware-based acceleration of the DCT have also been proposed using GPGPU-based and FPGA-based implementations (e.g., [54]–[57]). Examples for algorithm and hardware-based acceleration research for the discrete wavelet transform can be found in ([58]–[60]) and for Gabor transform can be found in (e.g., [61]–[64]).

Furthermore, for computing the local statistics, research has been conducted to accelerate the computation of local statistics in images, but to a lesser extent in comparison with transforms. Techniques like *integral images*, originally developed in the context of computer graphics [65], is a popular approach for computing block-based sums of any two-dimensional matrix of values (e.g., a matrix of pixels or coefficients). The integral image, also known as the *summed area table*, computed a table which has the same dimensions as the input matrix; it stores the sum of all matrix values above and to the left of the current position. Thereafter, the sum of values within any block of the matrix can be rapidly computed via addition/subtraction of three values in the table. A similar technique can be used to compute higher-order moments such as the variance, skewness, and kurtosis (see, e.g., [66], [67]).

Along with research for improving computational performance for the above two common operations for IQA algorithms, there has been research on techniques for accelerating specific IQA algorithms. For example, in [68], Gordon *et al.* investigated the acceleration of PSNR by using general-purpose-GPU (GPGPU) implementations in both CUDA and OpenGL. An investigation on how the application and system performance gets affected by utilizing GPGPU acceleration of PSNR in a model-based coding application (the primary bottleneck in model-based coding stems from the optimization procedure used to determine the model parameters from the input image) was made. From the analysis, they concluded that a non-GPGPU version of PSNR runs faster.

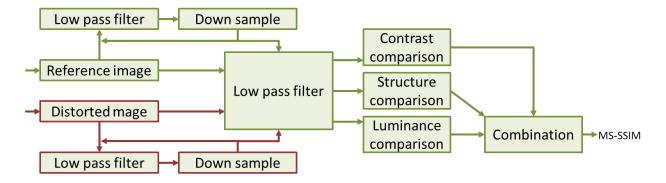

Chen and Bovik present techniques to accelerate execution of SSIM and MS-SSIM in [69]. Techniques like integral images for calculating the luminance block have been employed. They also use an integer approximation for the Gaussian weighing window for SSIM. For Fast MS-SSIM, a further algorithm level modification of skipping the contrast and structure computations at the finest scale was proposed. Implementing the calculations of the contrast and structure components via Intel SSE2 (SIMD) instructions, they achieved speedups of approximately 5 times for Fast SSIM and 14 times for Fast MS-SSIM were reported employing parallelization via a multithreaded implementation. In [70], Okarma and

Mazurek presented GPGPU techniques for accelerating SSIM, MS-SSIM, and CVQM (a video quality assessment algorithm developed previously by Okarma, which uses SSIM, MS-SSIM, and VIF to estimate quality).

In [67], Phan *et al.* conduct performance analysis to find sections of code that consume maximum of the total execution time and present techniques for accelerating the MAD algorithm targeting these sections[34]. MAD has one of the best predictive performance but is also one of the slowest IQA algorithms, it requires over 55 seconds for a 512x512 image when tested on several modern computers (Intel Core 2 and Xeon CPUs; see [67]). The results for performance analysis show that the main bottleneck for MAD is the appearance-based stage, taking about 98% of the total runtime. Within the appearance-based stage, the computing the local statistical differences accounted for most of the runtime, and computation of the log-Gabor decomposition was the other major bottleneck. Phan *et al.* proposed four techniques of acceleration: (1) Using integral images for the local statistical computations; (2) using procedure expansion and strength reduction; (3) using a GPGPU implementation of the log-Gabor decomposition; and (4) precomputation and caching of the log-Gabor filters. The first two techniques lead to a boost 17x speedup over the original MAD implementation.

Thus, we see that there are been significant research on improving performance using advance signal processing techniques. Very little or no research exists on the behavior of IQA algorithms with the computing platform and optimize/tune algorithms based on the hardware resource utilization of corresponding algorithms. This is a basis of the research objectives presented in the next section.

#### **1.3 Research Objectives**

Although these studies have successfully yielded more efficient versions of their respective algorithms, several larger questions remain unanswered. We will present a performance analysis for 5 matured IQA

algorithms VSNR, MAD, MS-SSIM, BLIINDS and VIF. This research is focused to answer the following questions and also present a framework for the mentioned 5 algorithms to further improve performance.

# **1.3.1** To what extent are the bottlenecks attributable to computational complexity vs. limitations in memory bandwidth?

As mentioned previously, there are two components to computational complexity with IQA algorithms. (1)Local frequency-based decompositions of the input image(s); and (2) local statistical computations on the frequency coefficients. Along with the computational complexity of the algorithms, Image processing inherently requires a higher memory bandwidth. Thus, we conduct microarchitectural analysis to investigate, how the algorithms behave on a general computing platform and study the memory requirements and bottlenecks.

# **1.3.2** Are there generic implementation techniques or microarchitectural modifications that can be used to accelerate all or at least several IQA algorithms?

We wish to compare and contrast the 5 IQA algorithms based on their performance profiling. This analysis can be would be a foundation to propose generic software optimization techniques, as well as hardware specific techniques to improve computational performance.

The research will provide important insights for (1) designing new IQA algorithms, which are likely to draw on multiple approaches used in several existing IQA algorithms; (2) efficiently implementing multiple IQA algorithms on a given hardware platform; (3) efficiently applying multiple IQA algorithms to specific applications; and (4) selecting and/or designing specific hardware which can efficiently execute multiple IQA algorithms.

#### **1.4 Outline**

The outline of the thesis is as follows:

- Chapter 2 provides a discussion on performance analysis and methodology along with a description of the profiling tool we use for the experiment: Intel Vtune Amplifier XE.

- Chapters 3, 4, 5, 6, 7 give the summary of each specific IQA, followed by results and discussion on hotspot analysis and microarchitectural analysis for VSNR, BLIINDS, MS-SSIM, VIF and MAD respectively.

- Chapter 8 discusses the results and answers the questions raised in section 1.3, and provides recommendations to improve performance. We also propose a hardware IQA engine framework which can be used to develop custom hardware for individual algorithms and a generic IQA engine.

#### CHAPTER II

#### **ANALYSIS METHODOLOGY**

For performance analysis and profiling we use the Intel Vtune Amplifier XE. The tool provides us with execution time of the algorithms along with execution time of the individual functions. With Vtune Amplifier XE we also conduct microarchitectural analysis, which provides details about the behavior of the code with the processor hardware.

This chapter provides an overview of the performance profiling tool, Intel VTune Amplifier XE [71]. Section 2.1 discusses the analysis procedure and methodlogy along with the specification of the hardware platform used. Section 2.2 provides a brief discussion about the tool in general. In section 2.3, we discuss hotspot analysis with reference to Intel VTune amplifier XE and discuss the way the Intel VTune Amplifier XE samples data to provide profiling results. Finally in section 2.4, we discuss microarchitectural analysis, specifically general exploration analysis type, the metrics used for analysis, and the hardware based event sampling utilized to provide results for microarchitectural analysis.

#### 2.1 Experimental setup

To begin to address the goals described in the previous chapter, we define an experimental framework for performance analysis designed to examine, compare, and contrast the performances of five popular IQA algorithms (VSNR [33], MAD [34], MS-SSIM [29], BLIINDS-II [39] and VIF [30]) on a typical desktop computing platform. To provide a common codebase, we implemented each of the algorithms in C++ based on the original MATLAB code provided by the authors of their respective algorithms. An initial code-level profiling was performed using Intel Vtune to identify and correct obvious inefficiencies in the baseline implementations. Next, we execute multiple trials of each of the five algorithms on 7 different images varying in image content. We use 3 different distortion types AWGN, Blurring, and Jpeg

compression with 2 levels of distortion, making a total of 42 Images from the CSIQ image database [34]. The details for the subject images are highlighted in Table1.

| Number of Images varying in Content | 7                                    |  |

|-------------------------------------|--------------------------------------|--|

| Types of Distortions                | 3 (AWGN, Blurring, Jpeg compression) |  |

| Levels of Distortions               | 2 (Level 1 and Level 5)              |  |

| Total subject Images                | 42                                   |  |

| Image size                          | 512x512                              |  |

| Frames (loops for the Algorithm)    | 30                                   |  |

| Hotspot Analysis sample time [72]   | 1ms                                  |  |

| Microarchitecture code name         | Sandy Bridge [73]                    |  |

| Microarchitectural Analysis Type    | General Exploration                  |  |

Table 1: Details of subject Images for performance profiling and microarchitectural analysis.

#### 2.2 Performance profiling methodology

After the experimental setup is fixed, with define the performance analysis flow and methodology. This section discusses an overview of performance profiling flow and the sequential steps for the analysis. First, we identify sections of program that should be targeted for improving the computation performance [74]. Such target sections of the program are called "hotspots" [75]. The process of identifying hotspots and improving performance is termed "tuning" [76]. Once the top hotspot functions are known, we conduct microarchitectural analysis to observe the interaction of the algorithm with the processor and other microarchitectural sub-systems. Microarchitectural analysis is used to inspect the processor resources used by the algorithm, related hardware bottlenecks and its reason. We use the Intel VTune Amplifier XE performance profiling tool to conduct our experiment and use the top down process suggested in the Intel optimization manual [77] for analysis. The suggested top down process in discussed below.

#### 2.2.1: System Tuning

The first step for optimization/ tuning of an application is System Tuning [76]. Deciding the hardware that best suits the given algorithm is called system tuning. For example, if your program is multithreaded, a multicore multi-threaded processor is advisable. We chose the hardware specifications to match the modern general purpose PC. We use the 2<sup>nd</sup> generation Intel core i5-2430M processor [78-79] clocked at 2.4GHz and a system memory (RAM) of 4GB .The microarchitecture is Sandy Bridge. Further details about the caches and memory hierarchy can be found in Table 2

| Processor                                     | Intel® Core™ i5-2430M |

|-----------------------------------------------|-----------------------|

| Frequency                                     | 2.4 GHz               |

| Microarchitecture                             | Sandy Bridge          |

| System Memory (RAM)                           | 4 GB                  |

| L1 Instruction Cache                          | 32KB per core         |

| L1 Data Cache                                 | 32KB per core         |

| L2 Cache (Unified Instruction and Data Cache) | 256KB per core        |

| L3 Cache (Unified Instruction and Data Cache) | 3MB shared            |

Table 2: Hardware specifications for the performance analysis experiement.

Since, the hardware specifications are fixed; we will focus our experiment on algorithmic and microarchitectural analysis.

#### 2.2.2: Algorithmic Analysis

Once the hardware specifications are fixed, the next step for optimization/ tuning is Algorithmic/ Hotspot analysis and tuning the algorithm based on software inefficiencies. During the prototyping phase, the software techniques employed usually aim for more readable and easier to debug programs. Such implementations are not optimized for a particular metric. The compiler does a tremendous amount of code optimization, but there are typically two situations where it cannot perform optimizations. First, when the inefficiency becomes apparent and occurs for only certain inputs that are not known at compile time, and second, when the inefficiency is at the algorithmic level. For example, for a sorting algorithm bubble sort has a computational complexity of O  $(n^2)$  while quick sort has O  $(\log (n))$  computational complexity. Thus using quick sort will have a better computational performance when compared to

bubble sort. We analyze the software for these inefficiencies that are beyond the scope of the compiler. While VTune cannot identify and recommend which sorting algorithm one must use, it does profile the code to point out sections of the code in which a majority of the execution time is spent. These sections of the code are the hotspots and can be targeted to improve performance. The algorithms can also be modified and a completely different implementation methodology can be used to improve performance [77]. During the Hotspot analysis phase of the experiment we note the total execution time for the algorithms, individual hotspots with their corresponding execution time and contribution to the total execution time.

#### 2.2.3: Microarchitectural Analysis

For algorithmic/hotspot analysis, we do not take into consideration the hardware specifics like memory utilization, instruction stalls during execution for tuning or optimizing the code. Microarchitectural analysis inspects the program as it traverses through the different subsystems of a processor and provides information to find architectural bottlenecks. This method is applied after hotspot analysis.

For microarchitectural analysis, we analyze the results to study the instruction throughput of the code as a whole and the instruction throughput of individual hotspot functions. The metric that we use is retired pipeline slots [72]. The retired pipeline slots metric is the number of instructions that exit the processor successfully, divided by the total number of clock cycles the hotspot utilized. The metric is normalized from 0 to 1. The Intel i5 2430M processor can generate and execute up to four instructions every clock cycle [78-79]. The instructions which do useful work are called retired [80]. Therefore, the retired pipeline slots metric gives us a measure of the number of instructions that exit the processor doing useful work. The ideal value for this metric is 1. However, the observed value is rarely equal to the ideal or maximum value. This can be due to several factors: some pipeline slots cannot be filled with useful work, either because the fetch and decode units of the processor could not fetch or decode instructions in time or because the execution units were overwhelmed and cannot accept more operations of a certain kind. This is called a structural hazard. Even if pipeline slots contain useful work it is possible that the instructions may not retire due to bad speculation like mispredicting a branch. After considering the retired pipeline

slots and determining the computing efficiency, we inspect hotspot functions for microarchitectural subsystem bottlenecks. A basic top down methodology for the complete tuning process is shown in Figure 1.

Figure 1: Top Down Tuning methodology for analysis and tuning

The goal of the research is to identify and point out sections of individual algorithms which are computationally intensive and take higher execution time.. The hotspot analysis type in the Vtune Amplifier XE gives a list of hotspot functions and corresponding relevant details. Using microarchitectural analysis, we analyze the behavior and interaction of such sections with the underlying hardware to find architectural bottlenecks. We conduct this microarchitectural analysis with the general exploration type of analysis in Vtune Amplifier XE. After both the hotspot analysis and microarchitectural analysis wemap the hotspot functions of specific execution blocks of the respective algorithm. Advanced software techniques along with microarchitectural consideration can be used to further improve computational performance.

#### 2.3 Intel Vtune Amplifier XE Overview

The Intel VTune Amplifier XE is a performance profiling tool which provides information about the application's execution on software basis as well as its interaction with different Intel hardware platforms [71]. Using the Intel VTune Amplifier XE, we can determine and locate hotspots, sections of code that have low instruction throughput and do not exploit hardware resources and related bottlenecks. For multi-

threaded applications the tool can also provide information about thread activity and transitions. In the following sections we describe a brief overview of hotspot analysis followed by microarchitectural analysis. Top features of the tool are highlighted in Table 3. More details about VTune Amplifier XE can be found at [71, 72, 76, and 77].

| Hotspot Analysis                                          | Located most time consuming sections of the code in a sorted list of functions.                                                                                                     |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Jump to source code                                       | Double click on the hotspot function in the results takes us directly to the source code.                                                                                           |

| Lock and waits Analysis                                   | We can analyze locks and waits for parallel<br>applications. These are the major cause for<br>slow multithreaded applications.                                                      |

| Low overhead/High resolution Hardware profiling           | Lightweight hotspot analysis, using performance monitoring units (PMU).                                                                                                             |

| Predefined Hardware Events and thresholds for bottlenecks | Advanced profiles like memory bandwidth<br>analysis, memory access and branch<br>mispredictions find tuning opportunities.<br>Predefined thresholds for identifying<br>bottlenecks. |

Table 3: Features of the performance profiling tool Intel Vtune XE Amplifier [71].

#### **2.3.1: Hotspot Analysis:**

In this section, we first discuss hotspot analysis w.r.t Intel VTune Amplifier XE and then describe the associated result windows: summary window, bottom-up pane, top-down pane and the call stack pane along with sampling of data for hotspot analysis. As discussed previously, hotspots are the most time consuming units in the program. A generic methodology for hotspot analysis and tuning as described in [81] is shown below.

Figure 2: Hotspot analysis methodology and the tuning process.

The process of tuning takes multiple iteration. It starts with building and compiling the application, run hotspot analysis and note the hotspots and corresponding execution time. Analyze the results and the calling functions and the source code for the hotspot function, make optimizations and build/compile the application again. This process is repeated till the target for optimization is achieved.

When we run the hotspot analysis the Intel VTune Amplifier XE finalizes the results and opens up the hotspot view which has the summary of the hotspots and also has options to open the bottom-up, call stack pane and top-down tree windows. A screenshot for the summary window is shown below.

| Function                                     | CPU Time |

|----------------------------------------------|----------|

| MADLoIndex::gaborConvolve                    | 10.139s  |

| MADLoIndex::coumputeStatisticsForLowIndex    | 4.109s   |

| cdft2d_sub                                   | 2.966s   |

| ooura::GFourier <double>::DoCmpxDFT</double> | 2.924s   |

| MADHiIndex::computeHiIndex                   | 2.830s   |

| [Others]                                     | 18.947s  |

Figure 3: Summary window hotspot analysis with top hotspot functions and corresponding execution time.

The summary window shows the total execution time of the program along with individual execution time for top hotspot functions. As seen from the figure, the top hotspot function is gaborConvolve which takes around 10.139s. The hotspot functions are arranged in a descending order in terms of their execution time. We can also navigate to bottom-up analysis or the top-down tree from the summary window. The bottom-up analysis next, then the top down tree and call stack pane.

The bottom-up pane shows the top hotspot as the first entry by default. It presents analysis specific data starting from the function up to their calling functions and hence bottom-up analysis [72]. If multiple functions call the hotspot function, the calling sequence for all the instances is displayed. Refer to the figure 4 below. We see that the function cdft\_2d\_sub is called by cdft2d as well as rdft2d.

| Grouping: Function / Call Stack                |            |               |                                                       |

|------------------------------------------------|------------|---------------|-------------------------------------------------------|

| Function / Call Stack                          | CPU Time 🕶 | Module        |                                                       |

| MADLoIndex::gaborConvolve                      | 10.139s    | MAD.ver.2.exe | MADLoIndex::gaborConvolve(class buf::GBuffer          |

| MADLoIndex::coumputeStatisticsForLowIn         | 4.109s     | MAD.ver.2.exe | MADLoIndex::coumputeStatisticsForLowIndex(            |

| □ cdft2d_sub                                   | 2.966s     | MAD.ver.2.exe | cdft2d_sub                                            |

|                                                | 2.849s     | MAD.ver.2.exe | cdft2d_sub                                            |

|                                                | 0.118s     | MAD.ver.2.exe | cdft2d_sub                                            |

| 🖃 ooura::GFourier <double>::DoCmpxDFT</double> | 2.924s     | MAD.ver.2.exe | ooura::GFourier <double>::DoCmpxDFT(class bi</double> |

| MADLoIndex::gaborConvolve ← MAI                | 2.769s     | MAD.ver.2.exe | ooura::GFourier <double>::DoCmpxDFT(class bi</double> |

| MADHiIndex::computeHiIndex ← GM                | 0.155s     | MAD.ver.2.exe | ooura::GFourier <double>::DoCmpxDFT(class bi</double> |

| Selected 0 row(s):                             |            |               |                                                       |

Figure 4: Bottom up pane, Hotspot analysis with a list of hotspot functions in a sorted order along with their complete calling sequence.

The top-down tree pane presents analysis specific data starting from the application root (usually main () function) down to function callees [71]. It is used to explore the call sequence flow of the application and analyze the time spent in each function or program section and on its callees. The top down tree can be used to find the critical path to the hotspot function. Figure 5 shows the top-down tree pane.

| Call Stack                              | CPU Time 🕶 | CPU Time:Total | Module  | Function (Full)                |

|-----------------------------------------|------------|----------------|---------|--------------------------------|

| 🗆 Total                                 |            | 100.0%         |         |                                |

| 🗆 console::GConsoleApp::DoRun           | 0s         | 100.0%         | MAD.ver | console::GCons                 |

| GMADApp::OnExecute                      | 0.062s     | 21.9%          | MAD.ver | GMADApp::OnE                   |

| MADHiIndex::computeHiIndex              | 2.830s     | 19.2%          | MAD.ver | MADHiIndex::co                 |

| MADHiIndex::getContrastSens             | 1.445s     | 3.4%           | MAD.ver | MADHiIndex::ge                 |

| ooura::GFourier <double>::Shif</double> | 0.985s     | 2.4%           | MAD.ver | ooura::GFourier                |

| □ MADHiIndex::coumputeStatist           | 0.776s     | 1.9%           | MAD.ver | MADHiIndex::co                 |

| buf::GBuffer <double>::GBu</double>     | 0.031s     | 0.1%           | MAD.ver | buf::GBuffer <do< td=""></do<> |

| buf::GBuffer <double>::GBuffe</double>  | 0.325s     | 0.8%           | MAD.ver | buf::GBuffer <do< td=""></do<> |

| □ ooura::GFourier <double>::Do</double> | 0.155s     | 1.8%           | MAD.ver | ooura::GFourier                |

| Selected 0 row(s):                      |            |                |         |                                |

Figure 5 Top Down window for Hotspot analysis. It displays the traversal of the application along with the execution time of individual sections.

As seen from figure 5, the application starts with the DoRun function and followed by the OnExecute function and so on down to the end of execution. Thus, the top down tree presents the functions in a sequence with which they traverse during the run time of the application.

#### 2.2.3: Microarchitectural Analysis

In this section, we discuss microarchitectural analysis, specifically general exploration type microarchitectural analysis, associated hardware metrics and discuss event based sampling for

microarchitectural analysis. The microarchitectural analysis provides an insight on how the application interacts with the CPU and consequently provide information to find architectural bottlenecks. The Intel VTune Amplifier XE uses the processors performance monitoring units (PMU) to sample hardware events [72]. First, we discuss an abstract view to the processor design and categorize the instructions entering a processor into 4 categories. 1: Retired 2: cancelled 3: Front end bound and 4: back end bound. This categorization in based on Intel Vtune optimization guide [77].

Processors are divided into two sections: the front end which fetches instructions and decodes them into micro-operations (Uops) to feed them to the respective execution units. For the i5-2430M machine the front end generates upto four micro-operations maximum [78-79]. These micro operations are then fed to the respective execution unit which is called the back end of the processor. If the front end cannot fetch and decode then the instruction is called to be "Frontend bound" and if the back end is not able to accept operations then the instructions are said to be "Backend bound". If the micro-operations exit the pipeline with doing useful work then these operations are said to be "retired" or else these operations are said to be "cancelled" [77]. The operations can get cancelled due to many reasons like branch misprediction or any other speculation done by the processor. The Intel®Vtune™ XE Amplifier classifies performance issues based on the pipeline slot the micro-operations can be in. The four categories and the corresponding hierarchy for the categories are shown in the figure 6 below.

Figure 6: Categories of Pipeline slots an instruction entering the processor can be in.

For microacrhitecturalanalysis, we first narrow down the bottlenecks into the above four categories and then highlight specific microarchitectural sub-systems which are bottlenecks for individual hotspot functions. The VTune Amplifier XE provides a wide variety of microarchitectural analysis like general Exploarion, Bandwidth analysis, Cycles and Uops etc. More details about the different analysis types within microarchitectural analysis can be found in the VTune Amplifier XE help manual [71]. We use the general exploration type of analysis. It is an analysis which has a set of hardware metrics predefined. All the metrics for the analysis in general Exploration are highlighted in table 4.

| Pipeline Slot Category  | Specific Hardware Metric            |

|-------------------------|-------------------------------------|

| Frontend Bound          | Icache Misses                       |

| Frontend Bound          | ITLB Overhead                       |

| Frontend Bound          | DSB to MITE switch overhead         |

| Backend Bound           | LLC load miss (memory latency)      |

| Backend Bound           | LLC miss (memory latency)           |

| Backend Bound           | LLC hit (memory latency)            |

| Backend Bound           | DTLB overhead (memory latency)      |

| Backend Bound           | Contested Accesses (memory latency) |

| Backend Bound           | Data Sharing (memory latency)       |

| Backend Bound           | L1 replacement (memory replacement) |

| Backend Bound           | L2 replacement (memory replacement) |

| Backend Bound           | LLC replacement(memory replacement) |

| Backend Bound           | Loads block (memory reissue)        |

| Backend Bound           | Split Loads(memory reissue)         |

| Backend Bound           | Split Stores(memory reissue)        |

| Backend Bound           | 4k aliasing(memory reissue)         |

| Backend Bound           | DIV Active (Core bound)             |

| Backend Bound           | Merge flags(Core bound)             |

| Backend Bound           | Slow LEA overhead (Core bound)      |

| Retired Pipeline slot   | Assists                             |

| Cancelled Pipeline slot | Branch Mispredict                   |

| Cancelled Pipeline slot | Cancelled pipeline slots            |

Table 4: General Exploration Hardware metrics with Pipeline slot categories and sub categories.

More details about the specific metrics, the related hardware issues and designs are discussed in the microarchitectural analysis section for individual algorithms when they are found to be bottlenecks.

#### CHAPTER III

#### VSNR

This chapter provides a brief description of the VSNR algorithm in Section 3.1. Section 3.2 provides an insight into the implementation details of the code and specific methods used. The performance profiling and hotspot analysis is discussed in Section 3.3 and finally, microarchitectural analysis with corresponding hardware bottlenecks mapped to the specific algorithmic block presented in Section 3.4.

#### 3.1. Overview

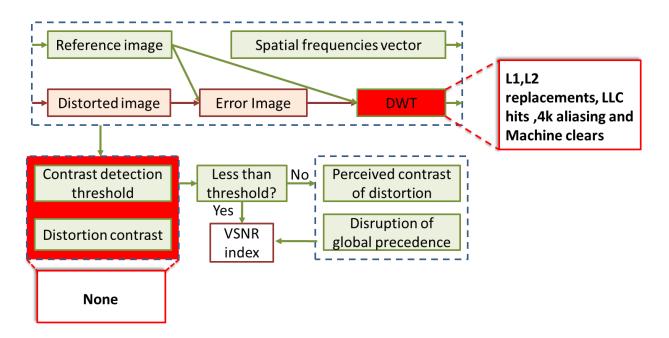

The VSNR algorithm [33] provides an estimation of the visual perception of distortions in natural images. The strategy for VSNR is to compute the root-meansquared (RMS) contrast by calculating the contrast thresholds for detection of distortions, the perceived contrast of the distortions and the extent to which the distortion affects global precedence, to degrade the image's structure. The block diagram for the algorithm is shown in figure 7.

#### Figure 7: Block Diagram for VSNR.

An efficient metric for quantifying the visual fidelity of natural images is the visual signal-to-noise ratio (VSNR). The metric is based on near-threshold and suprathreshold properties of human vision. The algorithm is divided into 2 stages. During the first stage, contrast thresholds for detection of distortions in

the presence of natural images are calculated. These thresholds are computed via wavelet-based models of visual masking and visual summation. The thresholds determine if the distortions are directly visible. If the distortions are below the threshold of detection then the distortions are not visible and the distorted image is considered to be of perfect visual quality with VSNR = infinity and the algorithm halts without conducting any further estimation of visual quality. But if the distortions cross the threshold; further processing is done which operates based on the low-level visual property of perceived contrast, and the mid-level visual property of global precedence. These two properties are then modeled as Euclidean distances in distortion-contrast space of multiscale wavelet decomposition, and VSNR is computed based on sum of these Euclidean distances.

#### 3.2 Implementation Details and specifics

The original C++ code of VSNR is obtained from author's website [82] and is optimized to remove obvious inefficiencies and have less execution time. As shown in Figure 11, the reference image and distorted image are loaded and stored in 2-D float arrays. The DWT decomposition step is implemented with five-level two-dimension wavelet transform based on lifting scheme using the default Cohen-Daubechies-Feauveau 9/7 wavelet [83]. In the second step, in order to have the contrast, we need to calculate the average luminance of the image. In this function, the original C++ code uses  $512 \times 512$  power operation, multiplication and addition. We modify this part using look up table technique to have a faster implementation which uses these operations only 256 times. In step 3, the global-precedence-preserving contrast signal-to-noise ratio, is computed using bisection search with index of visibility in the range of [0, 1].

#### **3.3 Hotspot Analysis**

As described in section 2.1, the process of finding critical sections of the program which consume higher execution time is called hotspot analysis. For our experiment, we find the hotspots for all the algorithms based on their contribution to the total execution time.

For the hotspot analysis for VNSR, we first find the total execution time for the algorithm. The average execution time for VSNR is 0.700s. After the finding the average execution time we observe the analysis results for hotspot functions to find the most time consuming sections of the code. The results for hotspot analysis are shown in table 5.

| Function/block | Average individual execution time(S) | % of total execution |

|----------------|--------------------------------------|----------------------|

| All            | 0.724                                | 100.00%              |

| 1D DWT-Columns | 0.236                                | 32.61%               |

| Variance       | 0.119                                | 16.45%               |

| 1D DWT-Rows    | 0.099                                | 13.68%               |

| Others         | 0.270                                | 37.28%               |

Table 5: Average execution time for the Hotspot function, also expressed as percentage of total execution time.

We find that the top hotspot or the most time consuming block/function for VSNR is 1D DWT-Columns. It takes about 32% of the total execution time an average of 236ms. As mentioned previously, the 1D DWT-Columns function computes a 1-D Discrete Wavelet Transform (DWT) across the columns of the original (distortion less) and the subject (Distorted image).

The next hotspot function/block is the variance block. It takes about 17% of the total execution time and 119 ms at an average. The variance function/block calculates variance for contrast and threshold detection. It is used for the image statistics.

Following the 1D DWT-Columns block the next hotspot function/block is1D DWT-Rows. The 1D DWT-Rows block consumes about 14% of the total execution time and 99 ms at an average. The 1D DWT-Rows function similar to 1D DWT-Columns calculates the DWT coefficients but across the rows on the reference as well as the subject image. Finally, all the other functions add up to 38% of the total execution

time and an average of 270ms. The results are plotted in figure 8, figure 9, and figure 10.

Figure 8: Individual execution time for all the hotspot functions and all the test images stacked to add up to the total execution time for a loop of 30 frames.

The figure shows that there is not a very high variation in the across the different test images with a few exceptions. To gather further insight into the variations, we plot the average execution of the different subject images across variation in distortions, figure 9 and across variation in image content, figure 10.

The plot shows the execution time of different images averaged across the different distortion levels. As seen from the graph, we find that there is no significant variation in the total execution time of the program as well across the different hotspot functions.

Figure 10: shows the average execution time of all the hotspot functions varied across 7 different image contents.

As seen from figure 10, we find that similar to variation across different distortions there is less variation in execution time of the complete program as well as individual hotspot functions with an except for orig 4 images. The orig 4 images have a higher execution time. Because the hotspot functions do not change ranks, the sequence/priority of the functions remains the same for optimization. As discussed in the methodology section, after the hotspot analysis we conduct microarchitectural analysis to analyze the behavior of the code with the underlying hardware. The results are discussed in the next section.

#### 3.4 Microarchitectural Analysis:

After the hotspot analysis, we conduct microarchitectural analysis to inspect the utilization of architectural resources. The goal is to identify what microarchitectural resources the hotspot functions need, and to find microarchitectural bottlenecks. First, we analyze the results to study the instruction throughput of the code as a whole and the individual hotspot functions. The metric that we use is retired pipeline slots. We observe that there are bottlenecks related to the memory sub-systems and thus, briefly discuss the memory hierarchy design of the processor to create a platform for our discussions on specific bottlenecks, than associate these bottlenecks with the algorithmic blocks.

The main memory or the RAM is fairly slow and takes about 100 clock cycles to deliver operands to the processor. So, to deliver operands to the processor every clock cycle a fast and small cache memory is placed between the processor and system memory. The cache memory closest to the processor is Level 1 cache or L1 cache. It is the fastest and smallest cache in the hierarchy. The next level of the cache memory is bigger and slower called the L2 cache. Usually, the L1 and L2 cache have 2 categories, First, Instruction cache where the instructions of the code are stored. The instruction cache aids to deliver the instructions to the processor every clock cycle and second, Data cache where operands and resultants for the instruction are stored. The level 3 or L3 is the last level cache which is the biggest and slowest. It is called the Last Level cache (LLC). Now, after knowing about the memory hierarchy we associate these memory sub-systems to the hotspot functions/blocks. More details about cache memories and memory hierarchy can be found in [80].

The results for the microarchitectural analysis, the hardware bottlenecks and associated blocks are shown in table 6

| Results | Summary. |  |

|---------|----------|--|

|         |          |  |

**Bosults Summary**

| Function/Block     | Image Type           | Pipeline Slot<br>Category | Backend Slot<br>Category | Retired<br>Pipeline slot | Hardware<br>Bottlenecks              |

|--------------------|----------------------|---------------------------|--------------------------|--------------------------|--------------------------------------|

| 1D DWT-<br>Columns | All                  | Backend                   | Memory                   | 0.100                    | L1,L2<br>replacement<br>and LLC hits |

| Variance           | All                  | None                      | None                     | 0.383                    | None                                 |

| 1D DWT-Rows        | All except<br>jpeg-5 | Backend                   | Memory                   | 0.350                    | 4k aliasing                          |

| 1D DWT-Rows        | Jpeg-5               | Backend                   | Memory                   | 0.221                    | Machine<br>clears                    |

Table 6: Microarchitectural analysis for VSNR with hotspot functions and associated bottlenecks.

L1D- Level 1 Data Cache, L2D- Level 2 Data Cache, LLC – Last level Cache.

Observing the hotspot analysis in the previous section, we find that 1D DWT-Columns block/function is the top hotspot. As mentioned, it is employed to do take a DWT across the columns of the subject image and the reference image. Conducting microarchitectural analysis, we find that the retire pipeline slot metric for the block is around 0.1 for all the images. Typically, if the metric is above 0.6, the section of the program is considered to be efficient. [76]. Thus, 1D DWT-Columns is highly inefficient. Upon further investigation we find that 1D DWT-Columns is backend bound memory bound. The major penalty is due to LLC hits which mean the program has to access the last level cache frequently. The LLC takes about 26-31 clock cycles [78-79] for a single memory access, which is very costly. Consequently, 1D DWT-Columns is the top hotspot. Along with LLC accesses as a bottleneck, we find that there are penalties due to data replacement in L1D and L2D caches. Since accessing the LLC requires high number of clock cycles, optimization should be made so that the processor doesn't have to access the LLC frequently. This can be done by reducing the L1D and L2D replacement and the L1D and L2D misses. We discuss the techniques to improve the cache performance in the later part of this section.

Followed by 1D DWT-Columns the next hotspot function is the 1D DWT-Rows which is similar to 1D DWT-Columns except that it is used to calculate DWT coefficients for rows. We investigate the retired pipeline slot metric to determine the efficiency of the block. We find that the retired pipeline slot metric is 0.35 which means that the function is inefficient. After investigating the architectural reasons we find that the block is backend memory bound and specifically there are memory reissues because of 4k aliasing.

To understand 4k aliasing, we need to look at how modern processors handle loads and stores. Load instructions refer to the transfer of data from memory to a CPU register. Stores do the opposite, i.e. write to a memory location from a CPU register [80]. A typical hardware optimization is to give priority to loads over stores, because loads are typically followed by arithmetic-type instructions that use the value that was loaded, and if a load is delayed, it stalls the subsequent use. Out-of-order execution is another common feature of modern processors, where instructions are executed out of the program order to make efficient use of hardware resources, but are retired in the correct program order [80]. Both the optimizations described above can give rise to a situation where a store instruction writes to the same memory location that subsequent loads read from, but the load instruction is actually processed before the store. This would yield a stale or incorrect value to be loaded from that memory location. This requires

checking the memory address that every load instruction gets its data from, with the target address for all pending store instructions. However, the pending stores might not have their effective addresses generated yet, and the load instruction could be delayed until at least all the store instructions have addresses that can be compared with the current load. This is not usually done, and the load is allowed to proceed. It is important to understand why modern architectures proceed with a speculative load in such a situation. As mentioned above, there could be instructions that depend on the load instruction. There are often several instructions that depend on a load, and delaying the load limits the options for the instruction scheduler for out-of-order processing. Furthermore, a load might miss in the first level cache, and might require several clock cycles to be serviced from the lower levels of the memory hierarchy (as seen above with the LLC accesses). Thus, it is important to issue the load without waiting for all the subsequent stores to have their addresses ready.

As this operation could require several comparisons, instead of comparing the entire 32-bit or 64-bit address, only the last 12 bits are typically compared. If these addresses are 4K bytes  $(2^{12})$  or multiple of 4096 bytes apart then a false hazard is detected. This is called 4k aliasing and the load has to be reissued. Consequently, because of 4k aliasing the processor has to perform loads again and the throughput goes down.

A possible solution to this problem from the hardware side is to check all 32/64 bits of the address instead of just 12. On the other hand, if most applications do not show the 4k aliasing to be a bottleneck, hardware designers are likely to check only 12 bits to save on hardware complexity, chip space, and power consumption.

There are some interesting solutions on the software side. One can investigate why there are so many 4k aliasing problems for this algorithm, and align data to 32 Bytes. Change offsets between input and output buffers if possible. Use 16-Byte memory accesses on memory which is not 32-Byte aligned. More details on solving 4k aliasing can be found in Intel optimization manual [77].

Also, as seen for jpeg images there are micro operations that get cancelled due to machine clears. Machine clears are typically caused by memory ordering violations or loads to illegal memory range. Based on the previous finding of 4k aliasing, we can conclude that the machine clears here are due to memory ordering violations, and are in fact caused by false positives from the 12-bit comparisons. Load and store instructions do not exit the processor until it is validated that there is no memory ordering violation in the actual order of execution that was used. Stores do not get sent to memory until they are ready to be retired. If the processor detects a memory ordering violation, it discards all unretired operations (including the offending memory operation) and restarts execution at the oldest unretired instruction. This is because the load might be speculative as described above, and all the instructions that depend on that load are also marked as speculative. After the comparison with the stores, if there is not violation detected, then the instructions are deemed good and are retired. If a violation is detected (either because there was a violation or because of the false sharing), then the load has to be reissued, and all the dependent instructions are also cleared and reissued.

From the hotspot analysis we notice that even though the DWT functions do exactly the same computation 1D DWT-Columns calculates the DWT coefficients across the columns and while 1D DWT-Rows across the rows of the reference and the subject image, there is a significant difference in the execution time for both the functions. To investigate the reason behind this we describe the design of the caches and how the data is brought and replaced in a cache.

The caches are design on the principle of locality of reference. It is based on the fact that the programs usually access the same or nearby memory locations repeatedly and frequently. Usage of same memory location repeatedly falls is called temporal locality while access of nearby memory locations is spatial locality [80]. An example for temporal locality would be instructions executed in a loop. These instructions are executed again and again and the processor fetches the instructions from the same memory location. For spatial locality, arrays serve as a great example. An image is basically a 2 dimensional array of pixels. Usually if a pixel is accessed, the next pixel or a nearby pixel is also

accessed. Based on the concept of locality, the cache controller brings a complete block of data and not just the operand that is required by the processor at that instant. The cache block for the Sandy bridge microarchitecture is 64bytes [78-79]. Thus, we can say the caches operate at a granularity of 64bytes. All the blocks brought into and removed from the cache are 64 bytes in size.

Now, we analyze how the image data is brought into the cache and correlate it with difference in execution time for calculating the DWT coefficients across columns and rows of an image. Figure 11 shows how image data is mapped to memory locations in an L1 cache.

Figure 11: L1 cache with a cache line of 64bytes along with mapping of image data to memory locations As seen from the figure the image pixels are brought in the cache row wise. A section of the image row is brought into the cache, when a block of data is stored in the cache. Specifically 8 pixels with double data type are brought into the cache. The calculations are shown below:

1 block of cache = 64 bytes (cache line width)/ 8 bytes (double data type size) = 8 pixels.

Thus, for getting a complete row of pixels in an image we require 64 blocks. Thus, a new column pixel is resides in the cache after every 64 cache line blocks. Therefore, in terms of memory every column pixel resides after 64x64 bytes= 4096 bytes or 4kb. Hence for a total cache size of 32k, if the cache is assumed to be only filled with image pixels, there can be only 8 column pixels. Whereas the number of row pixels that can reside into the cache is 4088. Thus, it is seen that the number of row pixels brought into the cache is much higher than the number of column pixels brought into the cache. Consequently, the hit rate for row pixels is higher, the processor has to go to the next level of cache less frequently to fetch pixels as more pixels can reside and the execution time is less.

Also, the other way to look at this problem is that for every block brought inside the cache all memory locations for that particular block are utilized by the 1D DWT-Rows functions (spatial locality) but for every block brought inside the cache there can be only one column pixel. Consequently, more blocks have to be brought and more current blocks residing inside the cache have to be replaced to make room for newer blocks. For this reason, the 1D DWT-Columns function has a higher L1D and L2D replacement penalty and has higher execution time.

A basic solution to cache memory replacement and cache misses problem is to use a chipset with larger cache size. This will lead more data to fit in the cache and increase the hit rate to improve performance. Another software technique to improve cache performance is called Loop tiling or loop Blocking. Loop tiling or loop blocking. As the title suggests, loop tiling or blocking is a mechanism in which the loops are broken into smaller chunks, to ensure that the data used by the loop fits in the cache and does not cause a miss. When we partition loop iteration (large array into smaller blocks), the accessed array elements fit into cache size, enhancing cache reuse and eliminating cache size requirements. Loop blocking allows reuse of the arrays by transforming the loops such that the transformed loops manipulate array strips that fit into the cache. In effect, a blocked loop uses array elements in sections that are optimally sized to fit in the cache. An example for loop blocking and how it improves cache utilization is presented in section 8.1.

Followed by the wavelet block the next hotspot function is variance. The retired pipeline slot metric is averages to 0.4 which means that the function is executed inefficiently but has a throughput better than the DWT functions. From the microarchitectural analysis we find that there are no hardware bottlenecks. This means that the function has complex instructions which take multiple clock cycles to execute. As mentioned, the variance function is used to calculate the variance for threshold and contrast detection. Calculation of variance is a floating point operation. Operating on floating point numbers is inherently slow, thus the function takes more time to execute. The analysis doesn't show a bottleneck because none of the floating point execution unit is overwhelmed and causes any stalls in processor.

After analysis of the hotspot functions and highlighting their corresponding bottlenecks we map these hotspot functions to algorithmic blocks so that the bottlenecks can be associated with the algorithm rather than specific code implementations and functions. The red sections in figure 12 show the hotspot blocks.

Figure 12: Block diagram of VNSR with top hotspots mapped to corresponding algorithmic blocks and their corresponding bottlenecks.

The DWT-Rows and the DWT-cols functions belong to the DWT block with L1D, L2D replacements and

LLC hits as bottlenecks for DWT cols and 4k aliasing a bottleneck for DWT rows. The variance function

belongs to the contrast detection and distortion contrast block. It suffers from no hardware bottleneck.

### CHAPTER IV

#### MAD

This chapter provides a brief description of the algorithm in section 4.1. Section 4.2 provides an insight into the implementation details of the code and specific methods used. The performance profiling and hotspot analysis is discussed in section 4.3 and finally, microarchitectural analysis and corresponding hardware bottlenecks mapped to the specific algorithmic blocks is presented in section 4.4.

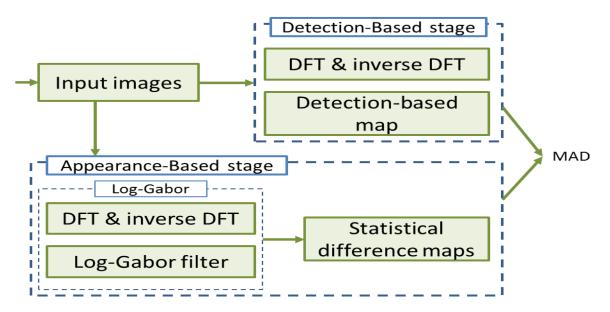

## 4.1 Overview

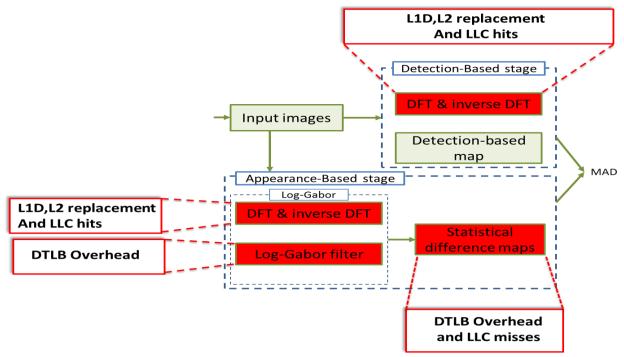

MAD is one of the algorithms which has high estimation accuracy for visual quality of an image. Most of the IQA algorithms focus on the most dominating strategy used by the Human Visual System (HVS) while MAD uses multiple strategies to determine image quality of an image [34]. For images with near threshold distortions, the algorithm uses detection based strategy. While, the appearance-based strategy is used when the images containing clearly visible distortions. The diagram of MAD algorithm is shown in Figure 13. Using the input images: the reference image and the distorted/ subject image, the MAD index is computed via two main stages, the detection-based stage and appearance-based stage. Using the detection-based strategy, the detection-based difference map, the difference between the original and distorted images is computed. For the appearance-based strategy, the appearance-based difference maps combined to get the high-quality and low-quality index. Weighted geometric mean of the indexes is computed. The final MAD index is computed using the weighted mean and a specific weight determined based on the amount of distortion.

Figure 13: Block Diagram for MAD.

## 4.2 Implementation details and specifics

The MAD code is ported to C++ from the Matlab version, which is publically available to download [71]. The input images are stored in 2-D double precision arrays using GBuffer image library. In the detectionbased stage, the images are taken to the luminance domain using look-up table. The Ooura's mathematical software packages [72] are employed for calculating Fast Fourier Transform and inverse FFT. This Ooura's library is also used in the log-Gabor decomposition in the appearance-based step. The statistical difference map is calculated using integral images for higher orders, detail can be found in our previous paper [67].

For each 512×512 image, MAD needs memory space for two input images, two luminance images, one for the error image, one for the CSF filter, four for the Ooura FFT computations, five for the masking and contrast maps, and around 80 images for the log-Gabor filter along with Ooura FFT, and statistical difference maps.

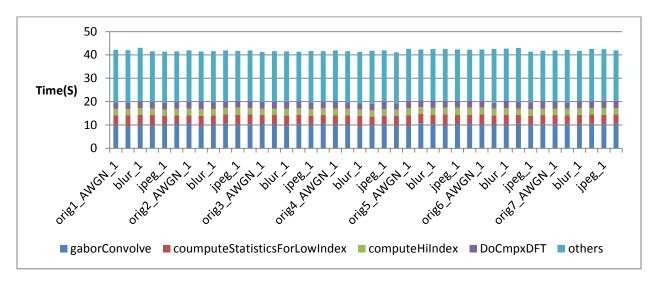

### 4.3 Hotspot Analysis

In this section, we discuss the top hotspot and their corresponding execution time for MAD. From the hotspot analysis we find that MAD has a very high execution time. The average total execution time and average execution time for individual hotspots, along with their % contribution to the total execution time is tabulated below.

| Function/Block | Average total execution time(s) | % of total execution time |

|----------------|---------------------------------|---------------------------|

| All            | 41.970                          | 100%                      |

| Gabor Convolve | 10.195                          | 24.29%                    |

| Low index      | 4.061                           | 9.67%                     |

| High index     | 2.827                           | 6.73%                     |

| DFT            | 2.906                           | 6.92%                     |

| Other          | 21.982                          | 52.38%                    |

Table 7: Average execution time for the Hotspot function, also expressed as percentage of total execution time.

As seen from the table, the top hotspot functions contribute about 50% of the total execution time and the other functions add up to the remaining 50%. So, to significantly remove performance or the total execution time all the top hotspot functions have to be targeted for optimizations. The top hotspot function is the Gaborconvolve function. It is used to calculate the appearance based difference map [34]. The function uses 5 scales and 4 different orientations to yield a total of 20 images for the original (reference) and the distorted (subject) image each. The function takes about 25% of the total execution time. Next is the Low Index function. It calculated the statistical difference map using variance, skew and kurtosis of the gabor filtered images [34]. The low index function takes about 10% of the total execution time. After the Lowindex function, the next hotspot is the High index function. It calculates the detection based map. The detection based map is calculated by finding the luminance of the reference and the distorted image, calculating the luminance error image and then applying a contrast sensitivity function to the DFT of the reference and the error image [34]. The final hotspot function is the DFT function; it converts the 2 input images into the Fourier domain. For the DFT function we use the Ooura's

mathematical software packages [72]. The high index and DFT function take about 7% of the total execution time. We plot the individual execution time for all the subject images in figure 14.

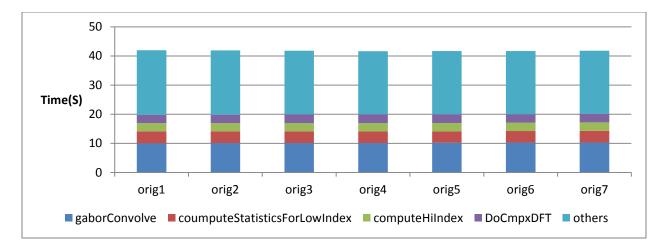

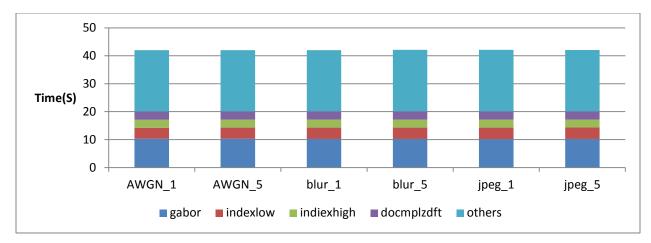

Figure 14: Individual execution time for all the hotspot functions and all the test images stacked to add up to the total execution time for a loop of 30 frames.

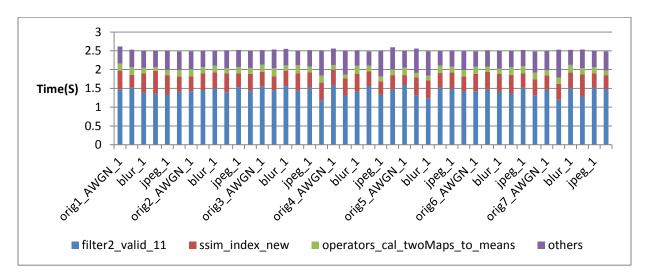

As seen from the figure MAD has very minimal variation in total execution time for the different subject images. Also, we analyze MAD to investigate if there are any variations in execution with change in Image content or the type of distortion of the subject Image. The results plotted and discussed below. Figure 15 shows the variation of average execution time of the hotspots w.r.t change in the Image contents. While, figure 16 shows the variation of average execution time for the hotspots w.r.t change in the type and level of distortion.

Figure 15: shows the average execution time of all the hotspot functions varied across 7 different image contents

Figure 16: Average execution time of the hotspot functions varied across the 6 different distortions.

As seen from both the plot, we find the algorithm is stable across changes in the image content as well as across changes in the type of distortion. Thus, all the hotspots can be targeted directly for optimization, without any consideration of the image content or the type of distortion. No Image specific or distortion specific techniques or hotspot optimization are required for MAD. The optimizations made would be universal.

## 4.4 Microarchitectural Analysis

From the Hotspot analysis we find that the execution time for the execution time for MAD is very high. The execution time for individual hotspot functions is also high. We investigate the microarchitectural sub-systems to find the reasons and bottleneck for higher execution time and analyze the behavior of the algorithm and its interaction with the underlying hardware. The results are shown in table 8.

| Function/Block | Image<br>Type | Pipeline slot<br>category | Backend slot<br>category | Retired pipeline slot | Hardware<br>bottlenecks                |