# A DYNAMIC RECONFIGURABLE COMPUTER WITH

# A DYNAMIC GENETIC ALGORITHM

By

# KAZUNORI NISHIMURA

Associate of Arts

Central Christian College of Kansas

McPherson, Kansas

2002

Bachelor of Science

Oklahoma State University

Stillwater, Oklahoma

2006

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of MASTER OF SCIENCE July, 2008

# A DYNAMIC RECONFIGURABLE COMPUTER WITH A DYNAMIC GENETIC ALGORITHM

Thesis Approved:

Dr. Sohum Sohoni

Thesis Advisor

Dr. Louis Johnson

Dr. Weihua Sheng

Dr. A. Gordon Emslie

Dean of the Graduate College

#### ACKNOWLEDGEMENT

First of all, I thank my parents, Mr. Kazuo and Ms. Reiko Nishimura, for their support. Without their help, I would not be able to come to U.S.A and continue studying for a long time. Also I thank my sister and brother for their patience and my host family for their support. I appreciate all faculty members that I took classes from. Among the faculty members, I give special remarks to my thesis committee members, Dr. Sohum Sohoni, Dr. Louis Johnson, and Dr. Weihua Sheng. Dr. Sohoni offered me the opportunities to use research resources and advice to complete my research. Without his help, I would not be able to complete my research. Also I thank to people in Writing Center for their help in the thesis edition and the lab assistants in CEAT labs and Alvin Ng for special accommodation on labs resources.

#### Kazunori Nishimura

# TABLE OF CONTENTS

| Chapter I                                                         |      |

|-------------------------------------------------------------------|------|

| CHAPTER 1<br>INTRODUCTION                                         | 1    |

| 1.0 Definition of reconfigurable computer                         | 2    |

| 1.1 Motivation                                                    | 4    |

| 1.2 Thesis Organization                                           | 6    |

| CHAPTER 2<br>REASONS AND PROBLEM STATEMENT                        | 7    |

| 2.0 Reasons for our proposal                                      | 7    |

| 2.1 Problem Statements                                            | 10   |

| CHAPTER 3<br>RECONFIGURABLE MULTI-CORE SYSTEM WITH GENETIC CONTRO | L 13 |

| 3.0 Assumptions                                                   | 13   |

| 3.0.0 Configuration constrains                                    |      |

| 3.0.1 Data centric approach                                       |      |

| 3.0.2 Inforuction Buffer                                          | 19   |

| 3.0.3 Brief idea of architecture of proposed system               | 19   |

| 3.1 Optimization Technique                                        |      |

| 3.1.0 General Genetic Algorithm: Background information           |      |

| 3.1.1 Specialized General Genetic Algorithm                       |      |

| 3.1.1.0 Dynamic population                                        |      |

| 3.1.1.1 Off by one theory                                         |      |

# **TABLE OF CONTENTS**

| Chapte       | er                                                          | Page     |

|--------------|-------------------------------------------------------------|----------|

|              | 3.1.1.2 Multiple Crossover Operation with multiple parents  |          |

| :            | 3.1.1.3 Fitness function                                    |          |

|              | 3.1.1.4 Running BEST                                        |          |

| CHAP<br>STAT | TER 4<br>TIC RECONFIGURABLE SYTEM: GENETIC ALGORITHM EVALUA | ATION 40 |

| 4.0          | Reason for static reconfigurable computer implementation    | 40       |

| 4.1          | Assumptions for Simulation                                  | 41       |

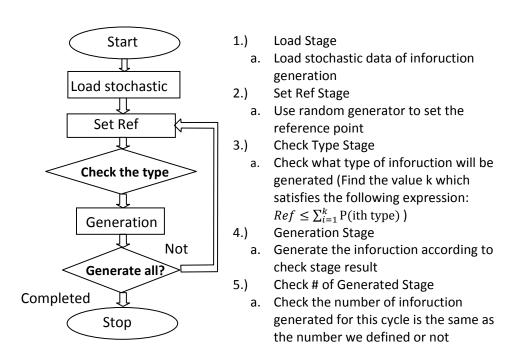

| 4.           | .1.0 Stochastic Inforuction Generator                       | 41       |

| 4.           | .1.1 Dependencies and inforuction stream                    | 44       |

| 4.2          | Genetic algorithm for the static operation                  | 45       |

| 4.3          | Simulation settings and simulation results                  |          |

| 4.4          | Simulation Results and Observations                         |          |

| CHAP<br>DYN  | TER 5<br>AMIC RECONFIGURABLE SYSTEM                         | 67       |

| 5.0          | Specific details of the dynamic genetic algorithm           | 67       |

| 5.1          | Simulation settings                                         | 70       |

| 5.2          | Simulation Results and Observations                         | 72       |

| CHAP<br>CON  | TER 6<br>CLUSION AND FUTURE WORK                            | 82       |

| 6.0          | Problems                                                    |          |

| 6.1          | Future work                                                 |          |

| 6.2          | Applications                                                |          |

| 6.3          | Conclusion                                                  |          |

# **TABLE OF CONTENTS**

| Chapter                                              | Page |

|------------------------------------------------------|------|

| APPENDIXIES                                          |      |

| APPENDIX A: REFERENCES                               |      |

| APPENDIX B: TABLES AND FIGURES: SETTINGS AND RESULTS | 93   |

| VITA                                                 |      |

| Table                                                                                                | Page |

|------------------------------------------------------------------------------------------------------|------|

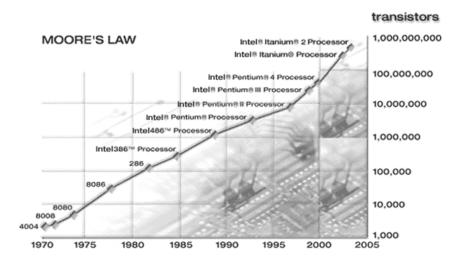

| FIGURE 1.1: GRAPH OF YEARS VERSUS NUMBER OF TRANSISTOR ON A SINGLE CHIP [2]                          | 1    |

| FIGURE 1.2: LIST OF THREE ESSENTIAL CHARACTERISTICS FOR THE PROPOSED SYSTEM                          | 6    |

| FIGURE 2.1 LIST OF PROBLEM STATEMENT WE WILL SOLVE TO CREATE THE PROPOSED SYSTEM                     | 12   |

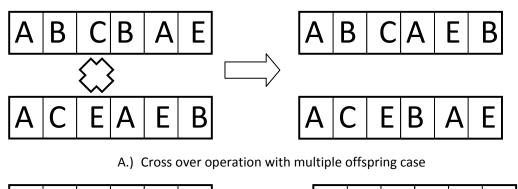

| FIGURE 3.1 OPERATION OF THE GENETIC ALGORITHM                                                        | 24   |

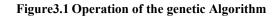

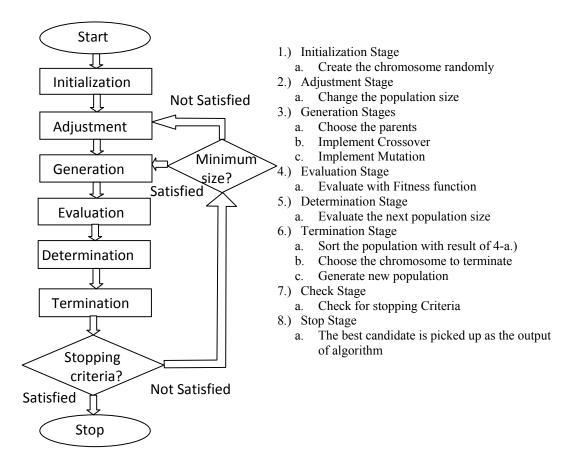

| FIGURE 3.2 OPERATION FLOWCHART FOR THE GENETIC ALGORITHM                                             | 24   |

| FIGURE 3.3 OPERATION FLOWCHART FOR THE MODIFIED GENETIC ALGORITHM                                    | 33   |

| FIGURE 3.4 OPERATION FLOWCHART FOR THE FITNESS FUNCTION                                              |      |

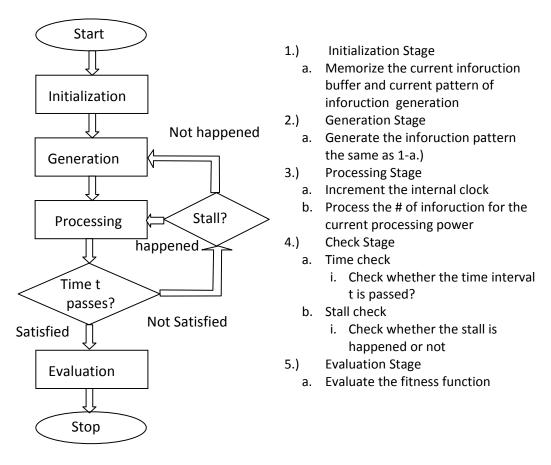

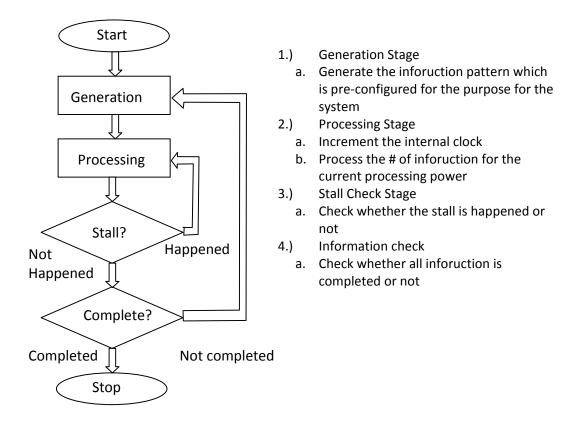

| FIGURE 4.1 OPERATION FLOWCHART FOR THE INFORUCTION GENERATION FOR EACH CYCLE                         | 44   |

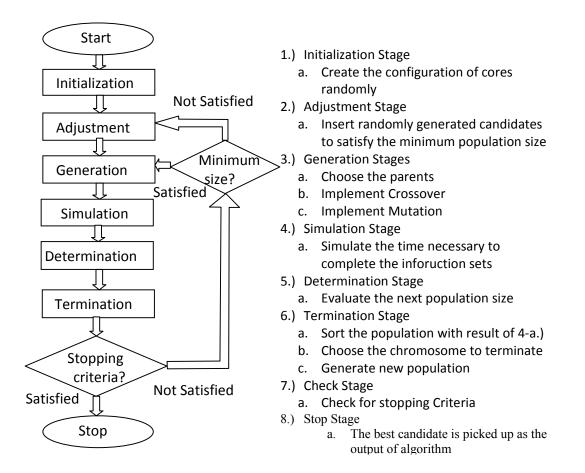

| FIGURE 4.2 OPERATION FLOWCHART FOR THE GENETIC ALGORITHM FOR STATIC OPERATION                        | 46   |

| FIGURE 4.3 OPERATION FLOWCHART FOR THE SIMULATION STAGE OF GENETIC ALGORITHM FOR STATIC APPLICATION. | 47   |

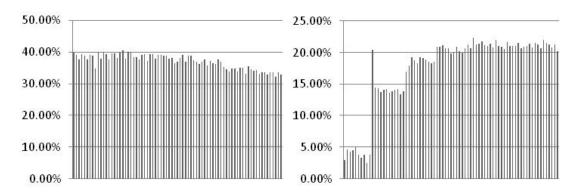

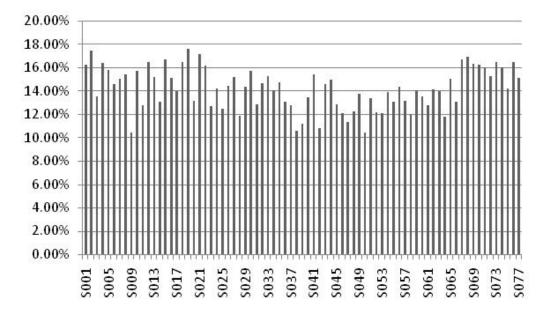

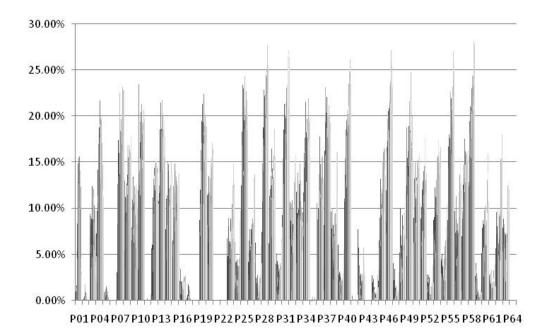

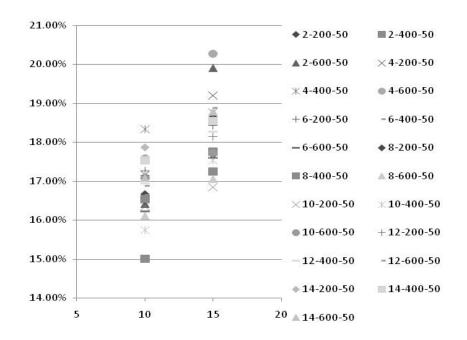

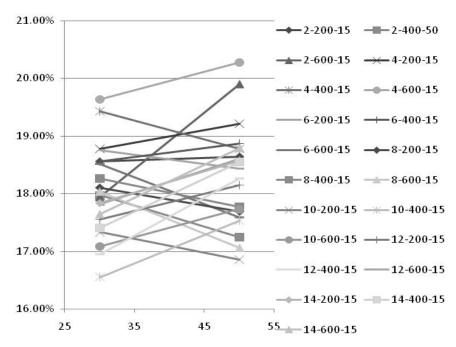

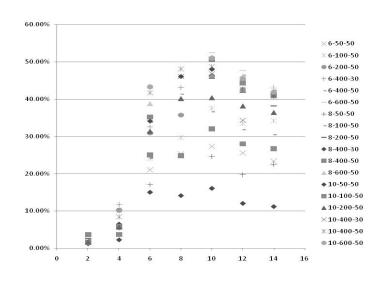

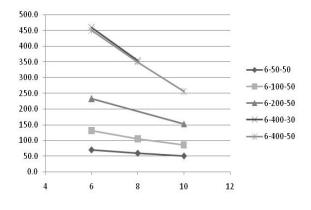

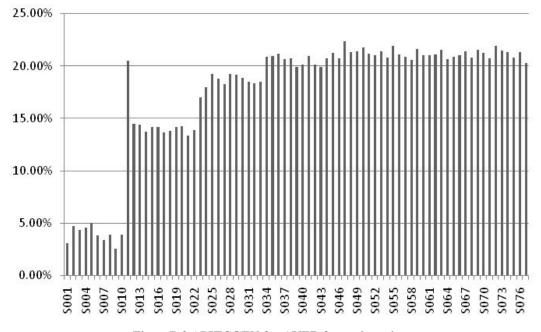

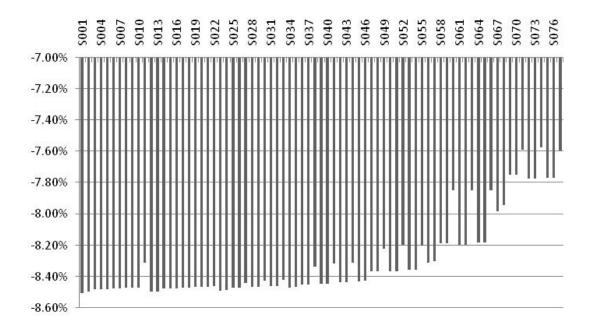

| FIGURE 4.4 APITCGEN FOR DIFFERENT TYPES OF SYSTEMS                                                   | 53   |

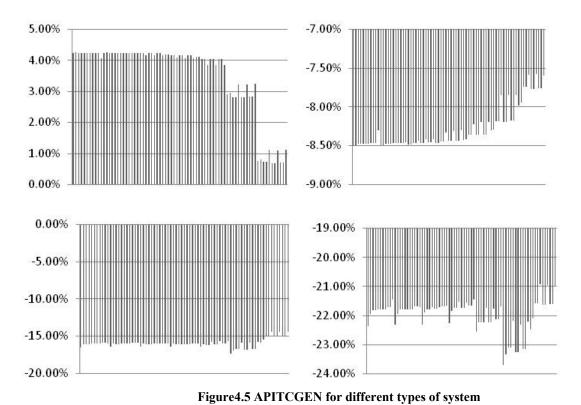

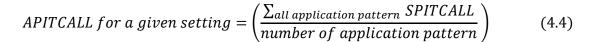

| FIGURE 4.5 APITCGEN FOR DIFFERENT TYPES OF SYSTEM                                                    | 54   |

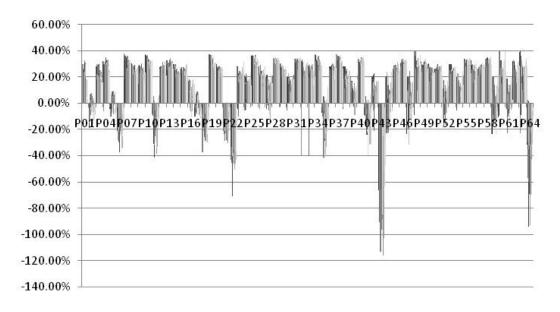

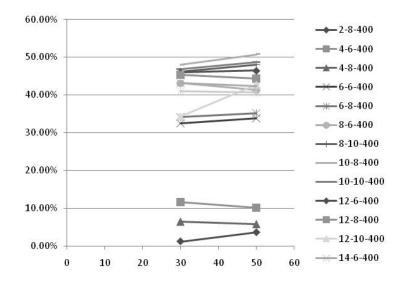

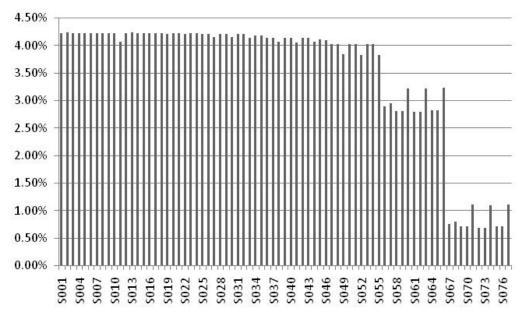

| FIGURE 4.6 APITCALL WITH BEST FOR DIFFERENT TYPES OF SYSTEMS                                         | 55   |

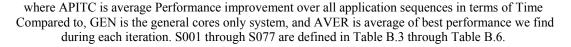

| FIGURE 4.7 SPITCALL WITH BEST AMONG SYSTEMS                                                          | 55   |

| FIGURE 4.8 APITCALL WITH AVER FOR DIFFERENT TYPES OF SYSTEM                                          | 57   |

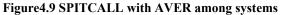

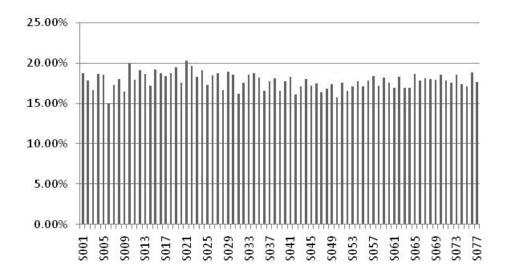

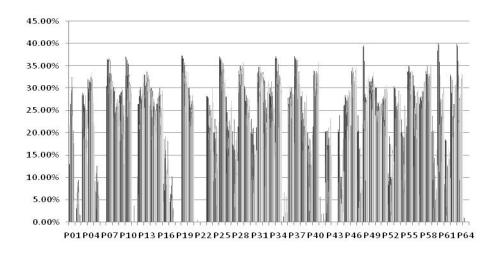

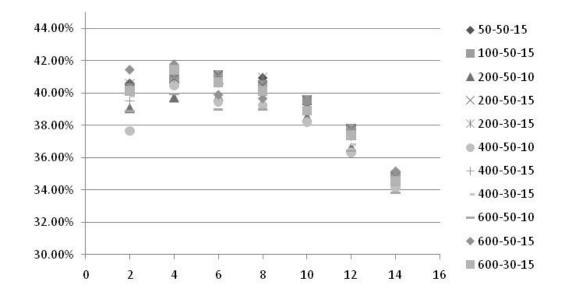

| FIGURE 4.9 SPITCALL WITH AVER AMONG SYSTEMS                                                          | 58   |

| FIGURE 4.10 APITCALL WITH BEST FOR DIFFERENT TYPES OF SYSTEM WITH MODIFIED ALGORITHM                 | 59   |

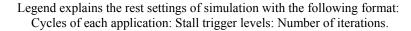

| FIGURE 4.11 SPITCALL WITH BEST AMONG SYSTEMS WITH MODIFIED ALGORITHM                                 | 59   |

| FIGURE 4.12 APITCALL WITH AVER FOR DIFFERENT TYPES OF SYSTEM WITH MODIFIED ALGORITHM                 | 60   |

| FIGURE 4.13 SPITCALL WITH AVER AMONG SYSTEMS WITH MODIFIED ALGORITHM                                 | 60   |

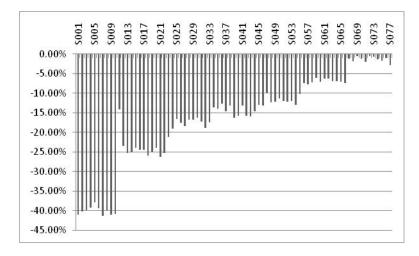

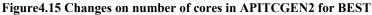

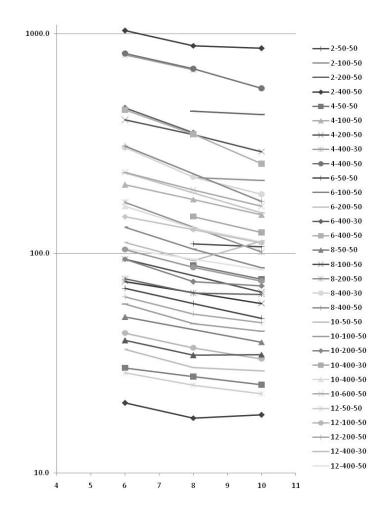

| FIGURE 4.14 CHANGES ON NUMBER OF CORES IN APITCGEN FOR BEST                                          | 61   |

| FIGURE4.15 CHANGES ON NUMBER OF CORES IN APITCGEN2 FOR BEST                                          | 61   |

| Table                                                                             | Page |

|-----------------------------------------------------------------------------------|------|

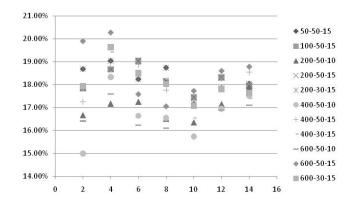

| FIGURE 4.16 CHANGES ON NUMBER OF CORES IN APITCALL FOR BEST                       |      |

| FIGURE 4.17 CHANGES ON APITCALL WITH DIFFERENT LENGTH OF SIMULATION FOR BEST      |      |

| FIGURE4.18 CHANGES ON APITCALL FOR BEST WITH DIFFERENT ITERATION                  |      |

| FIGURE4.19 CHANGES ON APITCALL FOR BEST WITH DIFFERENT STALL TRIGGER              |      |

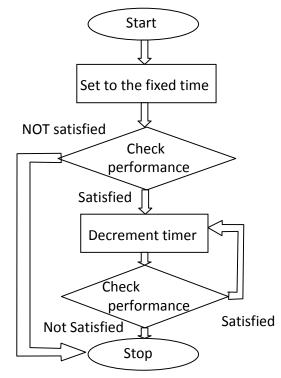

| FIGURE 5.1 RECONFIGURATION TIME DETERMINATION PROCESS                             |      |

| FIGURE 5.2 OPERATION FLOWCHART FOR THE DYNAMIC GENETIC ALGORITHM                  | 69   |

| FIGURE 5.3 BRIEF DESCRIPTION OF FLOWCHART OF THE DYNAMIC GENETIC ALGORITHM        |      |

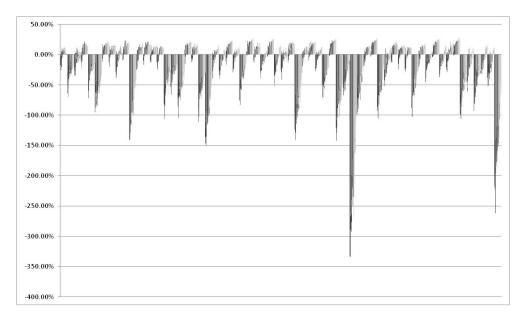

| FIGURE 5.4 SPITCBEST WITH DYNAMIC SYSTEMS                                         |      |

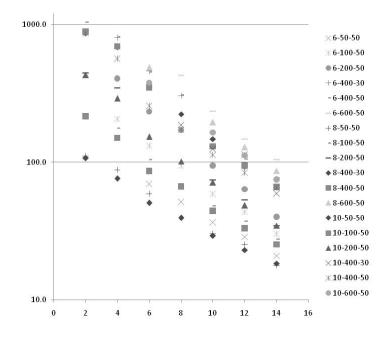

| FIGURE 5.5 APITCBEST WITH DYNAMIC SYSTEMS                                         |      |

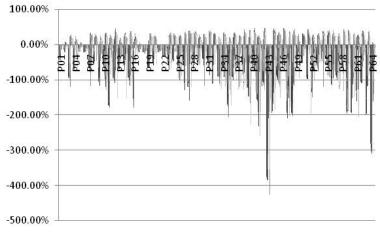

| FIGURE 5.6 SPITCGEN WITH DYNAMIC SYSTEMS                                          | 74   |

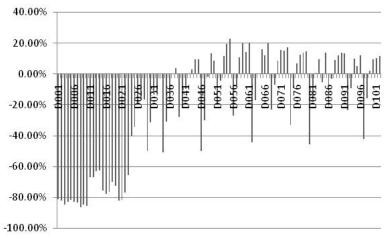

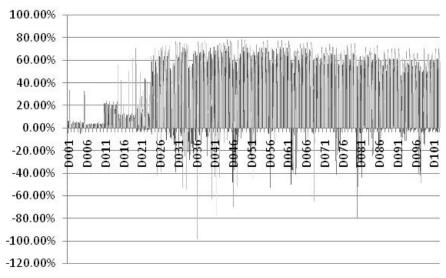

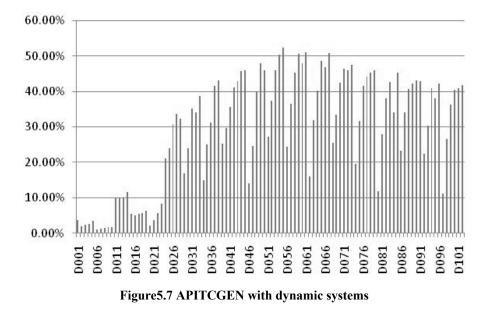

| FIGURE 5.7 APITCGEN WITH DYNAMIC SYSTEMS                                          | 74   |

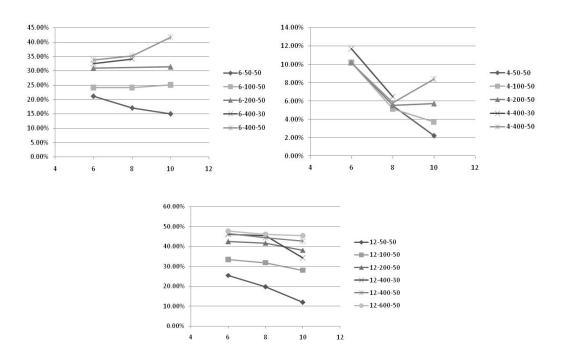

| FIGURE 5.8 APITCGEN WITH DYNAMIC SYSTEMS (CHANGING THE NUMBER OF CORE)            |      |

| FIGURE 5.9 NUMBER OF RECONFIGURATIONS (CHANGING THE NUMBER OF CORES)              | 77   |

| FIGURE 5.10 APITCGEN WITH DYNAMIC SYSTEMS (CHANGING THE DELAY CYCLES)             | 77   |

| FIGURE 5.11 AVERAGE NUMBER OF RECONFIGURATION (CHANGING THE DELAY CYCLES FOR 6 CO |      |

| FIGURE 5.12 APITCGEN CHANGES FROM THE CHANGE OF INFORUCTION BUFFER                | 79   |

| FIGURE 5.13 APITCGEN CHANGES FROM THE CHANGE IN CYCLES OF EACH APPLICATION        |      |

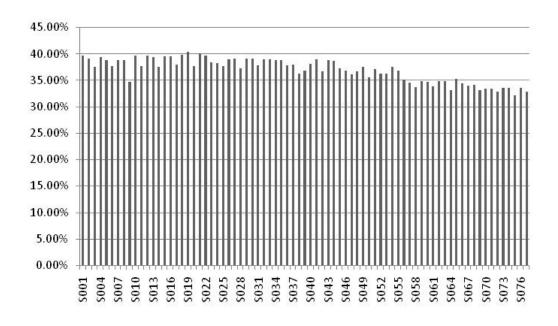

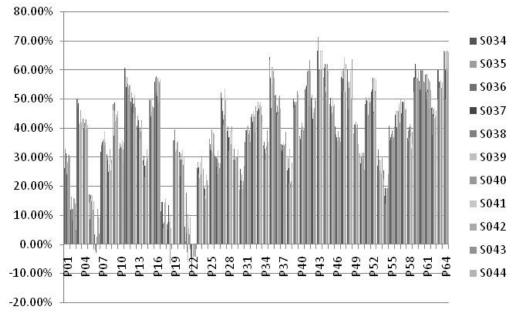

| FIGUREB.1 APITCGEN FOR BEST FOR EACH SETTING                                      |      |

| FIGUREB.2 APITCGEN FOR AVER FOR EACH SETTING                                      |      |

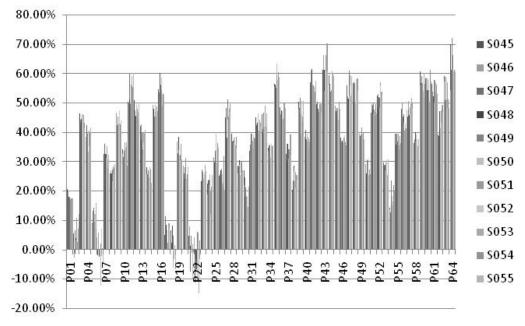

| FIGUREB.3 APITCGEN FOR LOG FOR EACH SETTING                                       |      |

| FIGUREB.4 APITCGEN FOR MAT FOR EACH SETTING                                       |      |

| FIGUREB.5 APITCGEN FOR FLP FOR EACH SETTING                                       |      |

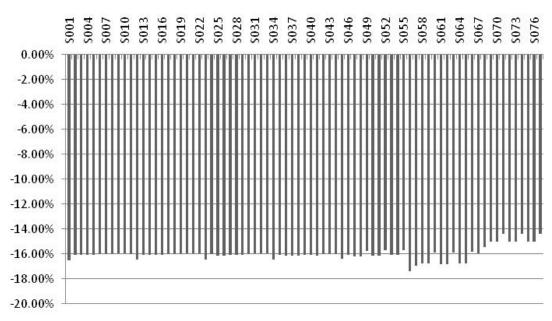

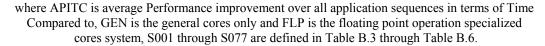

| FIGUREB.6 APITCGEN FOR MEM FOR EACH SETTING                                       |      |

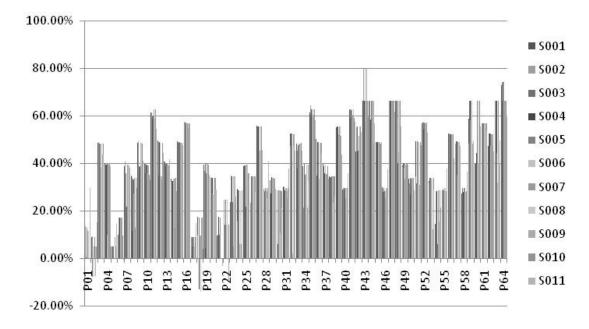

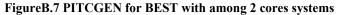

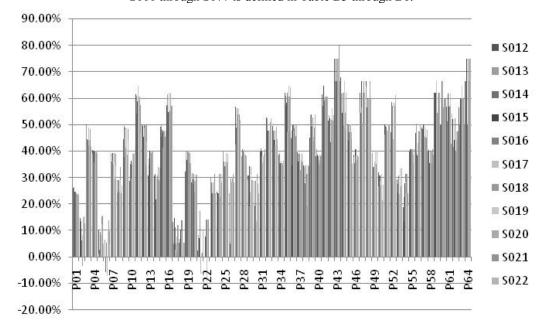

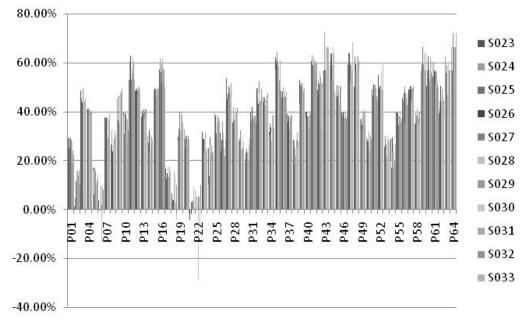

| FIGUREB.7 PITCGEN FOR BEST WITH AMONG 2 CORES SYSTEMS                             |      |

| FIGUREB.8 PITCGEN FOR BEST AMONG 4 CORES SYSTEMS                                  |      |

| Table                                                                               | Page      |

|-------------------------------------------------------------------------------------|-----------|

| FIGUREB.9 PITCGEN FOR BEST AMONG 6 CORES SYSTEMS                                    | 105       |

| FIGUREB.10 PITCGEN FOR BEST AMONG 8 CORES SYSTEMS                                   | 105       |

| FIGUREB.11 PITCGEN FOR BEST AMONG 10 CORES SYSTEMS                                  | 106       |

| FIGUREB.12 PITCGEN FOR BEST AMONG 12 CORES SYSTEMS                                  | 106       |

| FIGUREB.13 PITCGEN FOR BEST AMONG 14 CORES SYSTEMS                                  | 107       |

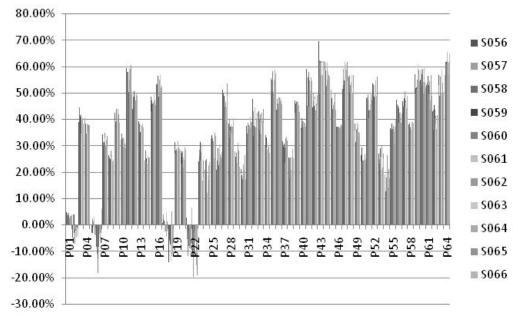

| FIGUREB.14 APITCGEN FOR BEST FOR EACH SETTING WITH MODIFIED ALGORITHM               | 107       |

| FIGUREB.15 PITCGEN FOR BEST AMONG 2 CORES SYSTEMS WITH MODIFIED ALGORITHM           | 108       |

| FIGUREB.16 PITCGEN FOR BEST AMONG 4 CORES SYSTEMS WITH MODIFIED ALGORITHM           | 108       |

| FIGUREB.17 PITCGEN FOR BEST AMONG 6 CORES SYSTEMS WITH MODIFIED ALGORITHM           | 109       |

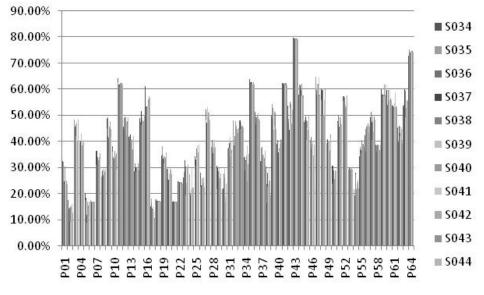

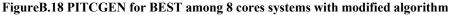

| FIGUREB.18 PITCGEN FOR BEST AMONG 8 CORES SYSTEMS WITH MODIFIED ALGORITHM           | 109       |

| FIGUREB.19 PITCGEN FOR BEST AMONG 10 CORES SYSTEMS WITH MODIFIED ALGORITHM          | 110       |

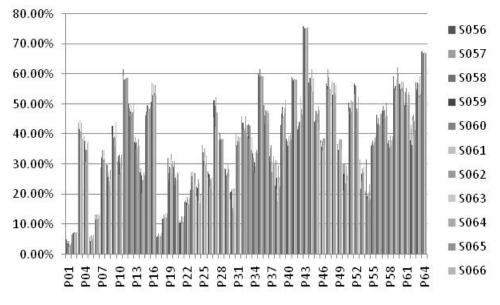

| FIGUREB.20 PITCGEN FOR BEST AMONG 12 CORES SYSTEMS WITH MODIFIED ALGORITHM          | 110       |

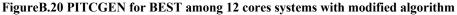

| FIGURE B.21 PITCGEN FOR BEST AMONG 14 CORES SYSTEMS WITH MODIFIED ALGORITHM         | 111       |

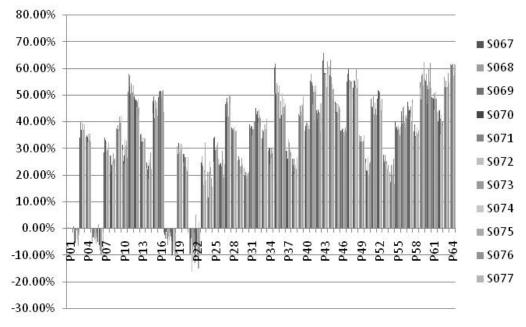

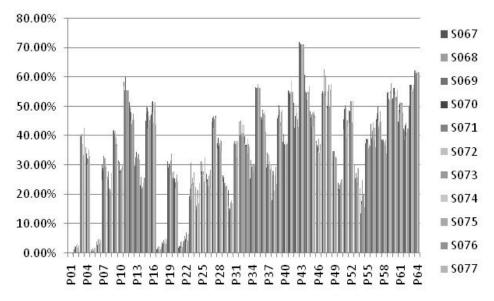

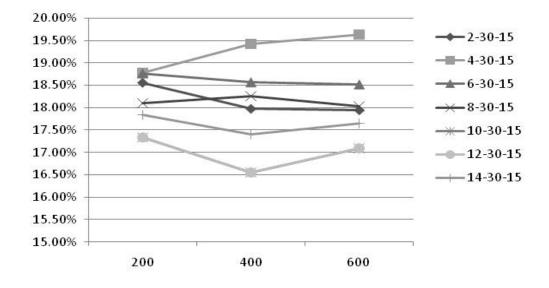

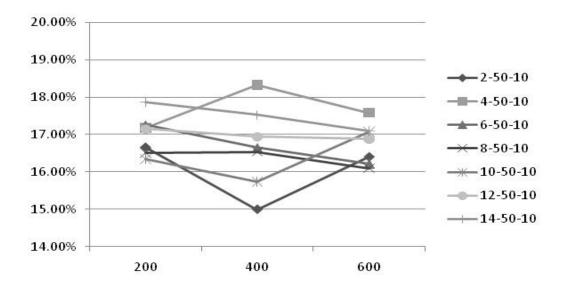

| FIGUREB.22 APITCGEN FOR BEST WITH DIFFERENT SIMULATION CYCLE                        | 111       |

| FIGUREB.23 APITCGEN FOR BEST WITH DIFFERENT SIMULATION CYCLE                        | 112       |

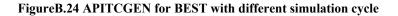

| FIGUREB.24 APITCGEN FOR BEST WITH DIFFERENT SIMULATION CYCLE                        | 112       |

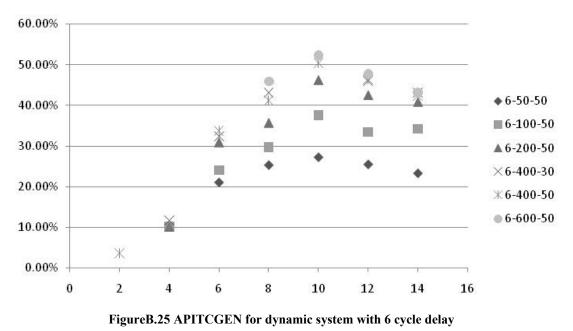

| FIGURE B.25 APITCGEN FOR DYNAMIC SYSTEM WITH 6 CYCLE DELAY                          | 117       |

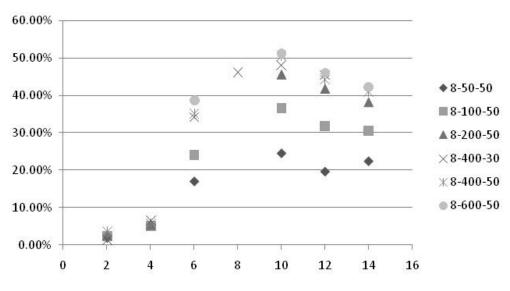

| FIGURE B.26 APITCGEN FOR DYNAMIC SYSTEM WITH 8 CYCLE DELAY                          | 117       |

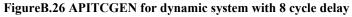

| FIGUREB.27 APITCGEN FOR DYNAMIC SYSTEM WITH 10 CYCLE DELAY                          | 118       |

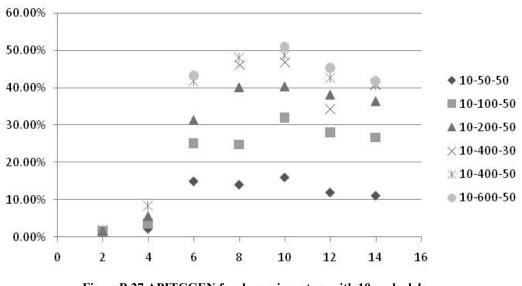

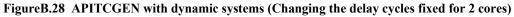

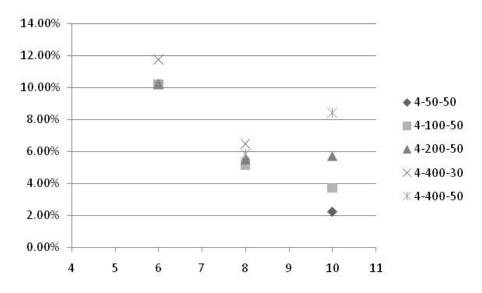

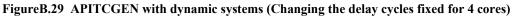

| FIGUREB.28 APITCGEN WITH DYNAMIC SYSTEMS (CHANGING THE DELAY CYCLES FIXED FOR 2 CC  | ores) 118 |

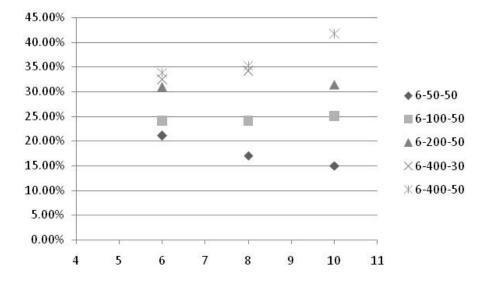

| FIGURE B.29 APITCGEN WITH DYNAMIC SYSTEMS (CHANGING THE DELAY CYCLES FIXED FOR 4 CC | ores) 119 |

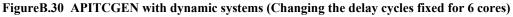

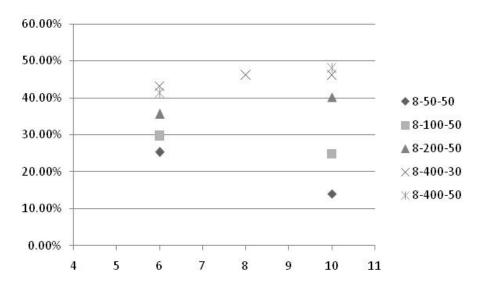

| FIGUREB.30 APITCGEN WITH DYNAMIC SYSTEMS (CHANGING THE DELAY CYCLES FIXED FOR 6 CC  | ores) 119 |

| FIGURE B.31 APITCGEN WITH DYNAMIC SYSTEMS (CHANGING THE DELAY CYCLES FIXED FOR 8 CC | ores) 120 |

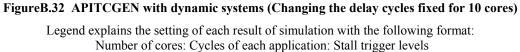

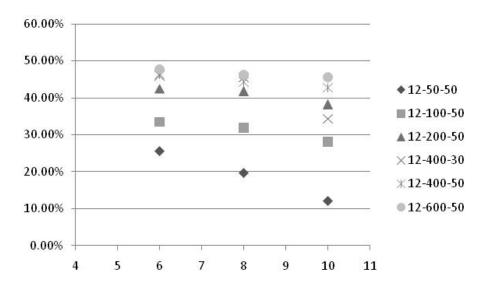

| FIGUREB.32 APITCGEN WITH DYNAMIC SYSTEMS (CHANGING THE DELAY CYCLES FIXED FOR 10 C  | ,         |

| FIGURE B.33 APITCGEN WITH DYNAMIC SYSTEMS (CHANGING THE DELAY CYCLES FIXED FOR 12 C |           |

| TablePa                                                                                     | age  |

|---------------------------------------------------------------------------------------------|------|

| FIGUREB.34 APITCGEN WITH DYNAMIC SYSTEMS (CHANGING THE DELAY CYCLES FIXED FOR 14 CORES      |      |

| FIGUREB.35 AVERAGE NUMBER OF RECONFIGURATION (CHANGING THE DELAY CYCLES FOR ALL CORES CASE) | .122 |

# LIST OF TABLES

| Table   Pa                                                                                         | ıge  |

|----------------------------------------------------------------------------------------------------|------|

| TABLE 1.1 DIFFERENT TYPES OF RECONFIGURABLE COMPUTERS IN OUR DEFINITION                            | 4    |

| TABLE 3.1 COMPARISON OF TWO METHODS OF RECONFIGURATION                                             | .17  |

| TABLE4.1 PERFORMANCE OF SIMULATION STATIONS                                                        | . 49 |

| TABLE4.2 STOCHASTIC DATA OF INFORUCTION GENERATION IN THE PERCENTAGE                               | . 50 |

| TABLE4.3 AMOUNTS OF INFORUCTION THAT EACH ARCHITECTURES CAN PROCESS IN THE GIVEN         TIME UNIT |      |

| TABLE4.4 COMMON SETTING FOR EACH CONFIGURATION IN SIMULATION                                       | . 51 |

| TABLE4.5 VARIABLES AND THEIR POSSIBLE SETTINGS                                                     | . 52 |

| TABLE4.6 STATISTICAL DATA OF SPITCALL WITH BEST                                                    | . 56 |

| TABLE4.7 STATISTICAL DATA OF SPITCALL WITH AVER                                                    | . 58 |

| TABLE 5.1 COMMON SETTING FOR ALL SIMULATION                                                        | .71  |

| TABLE 5.2 VARIABLE SETTING FOR EACH SIMULATION                                                     | .71  |

| TABLE6.1 PREVIOUS DYNAMIC APPROACH AND MAJOR PROBLEMS                                              | . 84 |

| TABLE B.1 CHANGES IN STOCHASTIC INFORMATION OF INFORUCTION GENERATOR – PART 1                      | .93  |

| TABLE B.2 CHANGES IN STOCHASTIC INFORMATION OF INFORUCTION GENERATOR – PART 2                      | . 94 |

| TABLE B.3 SETTING OF STATIC SYSTEMS (ONLY DISPLAYS VARIABLE SETTINGS) – PART 1                     | . 94 |

| TABLE B.4 SETTING OF STATIC CORES (ONLY DISPLAYS VARIABLE SETTINGS) – PART 2                       | .95  |

| TABLE B.5 SETTING OF STATIC CORES (ONLY DISPLAYS VARIABLE SETTINGS) - PART 3                       | . 96 |

| TABLE B.6 SETTING OF STATIC CORES (ONLY DISPLAYS VARIABLE SETTINGS) - PART 4                       | .97  |

| TABLE B.7 SIMULATION RESULT OF S001 IN PITCGEN – PART 1                                            | .97  |

| TABLE B.8 SIMULATION RESULT OF S001IN PITCGEN – PART 2                                             | . 98 |

| TABLE B.9 SIMULATION RESULT OF S001 IN PITCGEN – PART 3                                            | . 99 |

# LIST OF TABLES

Table

| FablePage                                                                            |

|--------------------------------------------------------------------------------------|

| CABLE B.10 SIMULATION RESULT OF S001IN PITCGEN – PART 4       100                    |

| CABLE B.11 SETTING OF DYNAMIC SYSTEMS (ONLY DISPLAYS VARIABLE SETTINGS) – PART 1113  |

| TABLE B.12 SETTING OF DYNAMIC SYSTEMS (ONLY DISPLAYS VARIABLE SETTINGS) – PART 2114  |

| CABLE B.13 SETTING OF DYNAMIC SYSTEMS (ONLY DISPLAYS VARIABLE SETTINGS) – PART 3 115 |

| TABLE B.14 SETTING OF DYNAMIC SYSTEMS (ONLY DISPLAYS VARIABLE SETTINGS) – PART 4116  |

# **CHAPTER 1**

#### **INTRODUCTION**

As a result of the major technology boost after World War II, some of the things that we had not even imagined have come true. Examples of such kinds of dreams are space stations, robots, digital cameras, mobile phones, handhelds, portable PCs, and portable music players. Many technological improvements and realization of dreams came from the invention of the transistor, and continuing improvement of transistor technology following Moore's Law, which predicts the growth of number of transistor in a single chip. This law predicts that the total number of devices in a chip will double every 12 months in the 1970s and the number of transistors will grow slower in the 1980s (it would be double every 24 months) [1].

Figure1.1: Graph of years versus Number of Transistor on a single chip [2]

The dramatic increase in the number of transistor in a single chip (depicted in Figure 1.1 above), and the reduction in gains from aggressive superscalar techniques has led to multi-core architecture for the CPU. Examples of multi-core CPU architectures are Intel® Core  $2^{TM}$  Duo, Core  $2^{TM}$  Quad or cell processor that was invented by IBM and Toshiba [3] – [5]. Since multi-cores superscalar architecture can have more processing power compared to single core [3] – [5], it is natural trend to change the computer architecture to obtain higher processing performance.

Also there is another trend in the area of computer architecture research. Many computer researchers set their focus on the reconfigurable computer since the reconfigurable computer has the potential to achieve higher processing performance compared to the processing performance of single core CPU architecture [6] - [8]. Even though we are using the same terminology *reconfigurable* computer, it has different meaning and represents different system for different researches. In other words, there is no clear single definition for the *reconfigurable* computer, and the meaning depends on the purpose of the research. Therefore we clarify the definition of reconfigurable computer in this study with several examples.

#### **1.0 Definition of reconfigurable computer**

Among different definitions of *reconfigurable* computer, there is one common property that we can easily find. The *reconfigurable* computer has the ability to adjust functionalities or architecture to achieve the correct functionalities or the superior performance. Keeping in mind this common property, we use the term *reconfigurable*  computer as the computer system that has the abilities to adjust the architecture and functionalities to achieve a specific objective. In our definition of *reconfigurable* computer, we can identify several different types of *reconfigurable* systems. One example of a reconfigurable system is the Central Processing Unit (CPU) of a general purpose computer. The current CPUs in the market have the multiple functionalities to implement the different logical operations and arithmetic operations. Examples of logic operations are AND, OR, XOR and NOT. Examples of arithmetic operations are addition, subtraction and multiplications. Among the different operations, the control command in the instruction set reconfigure the CPU to achieve the correct functionalities to process information [9]. Another example of *reconfigurable* computer is the current computer system. Since we have sufficient chips on the current high-end motherboards, we can operate the computer systems without any expansion cards. Although it is not necessary to install expansion cards, we usually enhance the performance of the computer system by installing graphic cards and sound cards and so on. In this case, we modify the system configuration by adding more resources to improve the performance.

In the previous paragraph, the first case also shows the example of run-time or *dynamic reconfigurable* computer. The *dynamic reconfigurable* computer changes its system configuration or architecture during the time when operations of the system are executing. The second example displays the off-line or *static reconfigurable* computer. The *static reconfigurable* computer changes its characteristics during the time when the system is not active or is turned off. In the other words, the reconfiguration is not only happened when the system is on. Table 1.1 summarizes the types of reconfigurable computer computer we describe in this section.

|         | Types                                       |  |

|---------|---------------------------------------------|--|

| Purpose | Performance or Correctness of the functions |  |

| Method  | Static or Dynamic                           |  |

Table 1.1 Different types of Reconfigurable computer in our definition

# 1.1 Motivation

In the area of computer architecture research, we know that specialized computer architecture has better performance than general computer where the specific application or purpose is concerned. There is no doubt for this statement since this fact is very clear from results of almost all previous researches in the area of computer architecture research. The better performance is obtained from the *optimized* architecture that is corresponding to the purpose of the system, such as mathematical operation, logical operation, graphical operations, encoding or decoding and so on. (In this paper from this point, the term *optimized* stands for "specialized" to obtain the current best performance configuration as far as we find so far.)

However, the specific computer architectures also have several disadvantages in the purpose that the system is not specialized for. This characteristic of computer in general is similar to the characteristics of human brain. Most people definitely have some specific fields that they are better in, than other areas, even though these superiorities and inferiorities in performance are different for each person. Some people might be good at memorizing mathematical equations, but they might be not good at playing music from music score without any practice. Other people might have superior capability in computer research and programming but they might not be good at writing papers. Examples that we described are limited to academic subjects, but we can find these performance differences all over human life from daily life to business world. These characteristics are based on the environmental causes, such as what we had more interest in, what we studied, how we grew up, and so forth. In other words, we optimized ourselves or our brain for the characteristics that we need or what we use more often. The proof of this performance optimization is clear on where we are concerned about the acquisition of languages. The children who grew up with English in their schools can speak English fluently compared to the children who did not speak English at all. This accommodation of language abilities does not only appear in speaking, but also in listening, writing, and reading. For example, children who grew up with Japanese can distinguish between the meaning of words, which can have several different meanings, even though they might sound similar or exactly same.

There is one significant characteristic difference between conventional computer architecture and human brain, even though we usually use analogy of human brain to explain computer operations. Human brains optimize performance or improve performance up to certain age, but normal computer does not change architecture after the production stage. Some *reconfigurable* computer changes architecture to obtain better performance for the specific tasks, but this specialization does not work in all situations.

Due to the technological improvements in the recent era, the complex *reconfigurable* computer is not just a dream any more. With continuous changing

motivation towards the technological front, we try to emulate the adjustability of human brain in a computer system using the *reconfigurable* computer. More specifically, we try to implement the flexibilities of human brain that is adjusting architecture for what we process currently. Therefore the heterogeneous *reconfigurable* computer that we want to propose has the three essential properties as summarized in Figure 1.2.

- Automatically adjustable architecture

- *Dynamic* or run-time Reconfiguration

• Optimization for specific objectives. Figure 1.2: List of three Essential Characteristics for the Proposed System

# **1.2** Thesis Organization

The remainder of the thesis is consisted of 6 Chapters. We start to discuss the reasons and problems statement for our proposed system in Chapter 2. In Chapter 3, we discuss the general idea of proposed system and the background concepts for the proposed system. In Chapter 4, we will do simulation to get the proof that the genetic algorithm can be used for simulation of computer architecture at high level. Also in this chapter, we briefly go over stochastics to introduce new assumption. The simulations in this chapter are implemented with static reconfiguration of computer architecture. Chapter 5 describes simulations of the proposed system and observations from the results of simulations. In Chapter 6, we finally conclude this thesis and offer suggestions for future research.

#### **CHAPTER 2**

# **REASONS AND PROBLEM STATEMENT**

#### 2.0 Reasons for our proposal

In this study, we propose a multi-core *reconfigurable* CPU as emulating the processing power of human brain. In this section, we go over several observations of the general *reconfigurable* computer to describe reasons of our choice. Additionally, we mention about problems that need to solve to create the system with the three properties listed in Figure 1.2: automatic reconfiguration, *dynamic* reconfiguration, and optimization for the specific target.

Assume we have a single *reconfigurable* core which implements the CPU, and our system has control unit which calculates the *optimized* architecture or configuration. Each time we try to reconfigure the system we cannot process the information during the reconfiguration time. We call this interval the *reconfiguration penalties*. If we try to implement the *static reconfigurable* CPU, the system does not try to process any information during reconfiguration. Therefore these penalties are not so important for the *static* implementation of the *reconfigurable* computer. As we describe in Chapter 1, we attempt to implement a system with the *dynamic* reconfiguration. The insignificance of the *reconfiguration penalties* is not same for our system. For the *dynamic* single core *reconfigurable* system, we definitely add one more term to calculate the total time needed to execute all information. We define the time unit we use for calculation of total Cycle Time (CT) as Cycle Time, which is time necessary to execute the specific instruction or the set of instruction. Relationship between total CT for *static reconfigurable* CPU and total CT for *dynamic reconfigurable* CPU for single core case is shown in expression (2.1) - (2.4) (Expression (2.2) is calculation for *static reconfigurable* CPUs and expression (2.3) is calculation for *dynamic reconfigurable* CPUs). We remark on one important fact of CT before moving to multi-core case. The CT would not be steady for both *dynamic* and *static reconfigurable* CPU. In other words, the time is dependent on the type of architecture we implement, and information we process during the period we are interested in. Also CT is measured as the average time obtained from tremendously large samples, since the instruction is not always executed in the same length of time.

$$CTSI = \sum_{\# of \ dif \ inst \ type} (\# of \ the \ specific \ inst \ to \ execute \ * \ CT)$$

(2.1)

$$TCT_{static} = CTSI \tag{2.2}$$

$$RP = \sum_{\# of \ recon} t_{recon} = \sum_{\# of \ recon} t_{Recon\_Process} + ex\_t_{find\_optimized}$$

(2.3)

$$TCT_{dynamic} = \sum_{\# of \ recon} CTSI + RP$$

(2.4)

where CT is Cycle Time, CTSI is Cycle Time for the Specific Instruction, dif is different, inst is instruction, TCT is Total Cycle Time, RP is *reconfiguration Penalties*, recon is reconfiguration, t is time, and ex is extra As we see in expression (2.1) - (2.4), we have several different terms in *reconfiguration penalties*. Extra time to find the *optimized* configuration in the controller unit is usually longer than the benefit of reconfiguration. Therefore the *dynamic* system might have several cases that end up with worse performance in term of total CT compared to the *static* system, due to the *reconfiguration penalties*. As a result, the average total amounts of information that the system can process in the given time interval cannot produce outstanding benefit from reconfiguration. For the single core operation, the *dynamic* reconfiguration would not have sufficient motivation to implement, since it might not produce enough benefits in term of processing power as described above.

Next we evaluate multi-core *reconfigurable* CPU briefly. If reconfiguration of cores in systems has dependencies in terms of processing information, which means that all cores in systems cannot process information during reconfiguration, the result of simple observation would be similar to the conclusion from observation of single core case. Therefore we need to develop a new system whose reconfiguration of each core is independent of each other. In other words, the remainder of cores, which would not reconfigure, can still execute information during the process of reconfiguration. In this situation, the *dynamic* system equation in expression (2.1) - (2.4) cannot be used to determine total CTs. We have to determine *reconfiguration penalties* with more complex equations such as expression (2.5) and (2.6). The complexity of calculation increases tremendously, even though expression (2.5) and (2.6) look like simple equations. So we cannot determine benefit of reconfiguration as easy as evaluation of single core case if we use CT as performance measurement.

$$TCT_{static} = \sum_{\# core \, used} CTSI$$

(2.5)

$$TCT_{dynamic} = \sum_{\# \ core \ used} (\sum_{recon} CTSI) + \sum_{\# \ core \ used} (\sum_{Static \ Operation} CTSI)$$

(2.6)

where CT is Cycle Time, CTSI is Cycle Time for the Specific Instruction,

dif is different, inst is instruction, TCT is Total Cycle Time, RP is *reconfiguration Penalties*, recon is reconfiguration, t is time, and ex is extra

#### 2.1 **Problem Statements**

From the previous argument, we need to develop new performance measurement, which we can easily use to determine the characteristics of *dynamic* systems and to compare the results with several different systems to find a better one. Also new measurement should be able to apply for *static* systems to compare performance between *dynamic* systems and *static* systems. As we discuss about performance of architecture, we not focus on the silicon area that is necessary for a whole system. We set our focus on processing power of systems. To determine processing power of systems, we cannot forget about one fact: results of performance measurements are dependent on benchmark programs we choose. For example, a result from one performance measurement shows outstanding benefits for a specific architecture. These differences come from the fact that different benchmark programs have different sequences of instructions, different measurement techniques, and different purposes of measurements which they are specialized for [10] - [13]. As a result of such specialization, we usually need to use several different performance measurements to determine benefits for implementing a

specific architecture. Also most benchmark programs are developed for conventional computer system, which might not be as dynamic as we propose. Some of the bench mark programs might be developed for *reconfigurable* computers, but we would not measure performance of brain-like computers easily with them. This is because our proposed system has more flexibility to adjust system configurations and architectures dynamically to purpose of systems. As we describe previously, our brain-like computer is changing architectures according to the information we need to process while the machine executes the information. Therefore a result of performance measurement might not be always the same, since processing of information would change as we run the system. From this point of view, we need to develop the new measurement method that we could use for our purpose.

In the previous paragraph, we emphasize the importance of developing new performance measurements for reconfigurable systems to compare each individual system configurations. We also need to develop a performance measurement for reconfigurations or *performance prediction*. *Performance prediction* has the huge impact on final overall system performance measurement. The reason of the importance of *performance prediction* comes from the fact that the optimization technique decides timings for automatic reconfiguration and candidates for next configuration based on the information obtained from *performance prediction*. Also the optimization technique is critical for our system. The relationship between control algorithm and performance of systems can be explained with analogy in a branch prediction. If branch prediction has great precision, the performance benefit from branch prediction becomes more obvious compared to systems without branch prediction. In automatic *reconfigurable* system, the

system with poorly developed optimization algorithm demonstrates only poor performance compared to the *static* systems. On the other hand, we can observe superior performance of *dynamic* automatic *reconfigurable* system from systems with welldeveloped optimization algorithm. Therefore control algorithm, its decision criteria, and performance prediction need to be developed carefully to obtain the sufficient results.

As we close this section, we summarize the problems obtained from our observation in Figure 2.1. With these problems in mind, we go over proposed brain-like system and its assumption in the next chapter.

- What kinds of evaluation technique or bench mark will we use?

- What kind of performance prediction will the optimization algorithm use?

- What kind of optimization algorithm will we implement for the system?

- What kind of performance measurement will we use for the system? Figure2.1 List of Problem Statement we will solve to create the proposed system

#### **CHAPTER 3**

#### **RECONFIGURABLE MULTI-CORE SYSTEM WITH GENETIC CONTROL**

#### 3.0 Assumptions

Before describing the general idea of our system with optimization technique and simulation technique we implement, we introduce several assumptions we use for this study. These assumptions are used efficiently to decrease the number of small problems and to reduce the complexity of problems in simulation of our system.

#### **3.0.0** Configuration constrains

There are two methods that we can use to find architecture configuration or design in *reconfigurable* computers. One of the methods is that we start designing the computer configuration from scratch. We design the candidate architecture with all aspects, such as number of gates logics and functions implemented in the architecture, without any previous information and any design constrains except the maximum number

of gate available in a reconfigurable core. This method can find the best architecture candidate in terms of performance for a specific purpose. Even for the single static core system, the search space of architecture configuration would be tremendously large since we have infinite choices. As a result, the search time that is necessary to find the best architecture would take more than a life time if we implement any search algorithm without blueprints. This search time issue would cause more serious problems for dynamic multi-core system. The search time that is necessary to find next configuration of each cores would take longer than a life time of production. The time needs for the search become too long for any numbers of cores if we do not use appropriate design constrains or pre-designs. Since all system change processing information as time goes, the "best" configuration of the past moment would not produce sufficient performance benefit if the search time is too long. In the other words, there are some opportunities that performance of system after reconfiguration would be worse than the performance of system prior to reconfiguration. This is caused by the "inappropriate" change of system architectures. As we describe about *reconfiguration penalties* in expression (2.3) - (2.4), search time to find the next configuration for all cores should include evaluation of performance measurement. In dynamic system, each core would be redesigned to find better performance for each chance for reconfiguration. Therefore if search time is too long such as the time necessary to find the next configuration from scratch, the performance benefits from reconfiguration also diminishes.

To reduce search time, we might be able to use the current designs or configurations of architecture as the start point of design. Such kinds of information might help to reduce search time that is necessary to find next configurations, but we cannot guarantee that the previous configuration would be efficient starting point for the architecture designs if we adjust systems for processing information in current time. We can verify this fact with a simple example. Assume a simple system which is processing "information A" for a long time and current configuration optimized to process "information A" as "configuration M". If "information A" changes to "information B" which require similar set of instructions to process, "configuration M" would be a sufficient starting point to improve performance. However, the opposite case would cause a different result. "Configuration M" would not be worthy of use if "information A" changes to "information C," which requires completely different pattern of instructions compared to the instruction pattern necessary to process "information A".

In the two previous methods, we cannot have any characteristic information for each candidate we evaluate to find the *optimized* candidate beforehand. Therefore we should measure performance of architectures after the design is completed. To compare the candidates of next architecture configuration in the optimization algorithm, we need to wait until several other candidates are designed and measured. We can reduce the time necessary for multiple candidate designs by making the design process as simultaneous operation instead of sequential single design process. However, even with such kind of systems we cannot reduce the time necessary to complete any single candidate. Therefore these methods are not appropriate for our dynamic system.

The *reconfigurable* computer with pre-defined configuration is the method we use. This method has several benefits that increase the performance of our system. The first benefit is that the performance increases from reduction of the time necessary to design core architecture. Since we only use architectures that are pre-configured, we do not

have to spend time for designing better architecture from the beginning. This idea is similar to the method of hierarchical design of Very Large Scale Integrated chip (VLSI) [14]. In the VLSI, we use the predesigned cells to create a larger and more complicated circuit. The cells used in the VLSI designs are extensively measured and well-designed to be specialized for certain objectives. In our system, we use well-designed architectures which are implemented in *reconfigurable* cores.

As we describe at the end of the previous paragraph, we only use well-defined core architecture which we know all performance characteristics such as power consumption, processing power, and Silicon area necessary to create. This fact generates several other benefits. We can reduce *reconfiguration penalties* due to the performance measurements of the next configuration candidates. We would know maximum performance of each architecture configurations without any assumptions since we can evaluate performance prior to use. We can also calculate the maximum performance of a multi-core system with simple arithmetic from the single core specifications. This wellestablished knowledge of performance can reduce the complexity of the optimization algorithm and the work load to find better configurations in the algorithm. In other words, the optimization algorithm is too complicated and time consuming without any prior knowledge of characteristic information since performance information is necessary to find better candidates. The reduction of reconfiguration penalties with preconfigured and well-defined systems are related to improvement in the processing performance. We go over one more benefit that is related to cost of implementation. Since we only use preconfigured architectures that we have the possibility to use, we can reduce the size of each reconfigurable core to the minimum requirement which is necessary to implement

the largest architecture we have. This benefit is related to the cost of Silicon area that is required to implement each core. If we are designing the architecture of a core from scratch, we cannot obtain the information for the minimum size requirement which might be used in our system. Therefore we have to prepare overhead areas up to the limit of the Silicon area we can use, and sizes of the *reconfigurable* core would be more than the necessary area, even though the size of the final configuration might be much smaller than what we prepare as the overheads. Table 3.1 displays comparison between two methods: designing from scratch and using the preconfigured designs.

|                                              | With Scratch               | With Preconfigured Designs |

|----------------------------------------------|----------------------------|----------------------------|

| Performance<br>Without RP ( <i>Static</i> )  | Better                     | Worse                      |

| Time Necessary to<br>Create Next Candidate   | Longer                     | Shorter                    |

| Time Necessary to<br>Evaluate Next Candidate | Longer                     | Shorter                    |

| Complexity of<br>Optimization Algorithm      | More Complicated           | Less Complicated           |

| Performance<br>With RP ( <i>Dynamic</i> )    | Worst                      | Better                     |

| Silicon Areas                                | Cannot be determined prior | Can be determined with     |

| Used for each Design                         | to complete designs        | characteristics of designs |

Table 3.1 Comparison of two methods of reconfiguration

RP stands for reconfiguration penalties

#### **3.0.1** Data centric approach

One of the performance measurements we can use is processing power of computers. This is one of the traditions we use in research of computer architecture. In general, we use throughput which described the number of instructions we can process in a given interval, the Instruction per Cycle (IPC), the Cycle per Instruction, and time necessary to complete specific instruction sets [9]. These measurements are focused on the number of instructions and the time needed to use the resources.

There is other approach which uses data instead of individual instructions [15], [16]. This performance measurement uses the number of data or information processed in a given interval. Our brains always process several different sets of information in our daily lives. For example, the brain processes information from eyes to create what we feel to "see" such as colors, dimensional aspects, textures, and distances of objects. Also our brains process multiple sounds and identify the necessary information at the same moments. This identification comes from frequencies, amplitude, and distance from sources. If you think about motion of hands to grab something, human brains also process several different sets of information to move hands as we think. Therefore as we emulate flexibilities of the human brain, it is natural to use data centric approach for our system to find better candidates. If we consider more details of such information sets, we might consider them as millions of small instructions that have many dependencies. To reduce the effects of dependencies, we not break them down to individual instructions; instead we treat them as a set, which we define as *inforuction* from this point. Since we use *inforuction* for finding the next candidate architecture configuration, our data centric approach needs to define several different types of inforuction to create the performance

measurement details. Using these types of information, all preconfigured architectures are measured with their characteristics such as the amount of *inforuction* they can handle in a given time interval. In other words, we know all performance measurements in term of the processing power of *inforuction*.

#### **3.0.2 Inforuction Buffer**

If we refer to architecture of superscalar processors in [9], we have an instruction buffer which stores instructions temporary till they feed to each individual pipeline. This mechanism allows us to control the flow of instructions and to utilize each pipeline as much as possible. We implement a similar mechanism in our system, which is identified as *inforuction buffer*. As we decide to use data centric approach, *inforuction buffer* stores each type of *inforuction* in different buffers. So each time *inforuction* is pre-fetched, the *inforuction buffer*. The *inforuction* in the *inforuction buffer* is processed in the order they are fed in, which is the same order as first-in and first-out (FIFO) operation. This order reduces probabilities that we have dependencies among information. Therefore the *inforuction buffer* controls the flow of information and utilizes each core as much as possible.

#### 3.0.3 Brief idea of architecture of proposed system

The General concept of our system would be similar to a cell processor [5] or similar to a tree. Therefore we explain our system architecture with an analogy to a tree. For a tree, we have one big trunk which holds minerals, some nutrients, and water

obtained from the roots. Then the trunk sends these substances to the branches. The branches have different number of leaves that can implement photosynthesis, which uses sunlight to convert some nutrients and water and carbon dioxides into oxygen and some useful nutrients. Each leaf has also different amounts of chlorophyll which determines the capability of photosynthesis in a given day. In our system, the trunk corresponds to the *inforuction buffer*, the number of leaves on a branch corresponds to the number of cores in a system, and different amounts of chlorophyll corresponds to different architecture configurations we implement. Therefore our system has one big information buffer which stores and sends the *inforuction* to each core at the certain time and each core has input and output port at the same location in the architecture design. Therefore we can switch configurations of cores without any connection problems.

# 3.1 **Optimization Technique**

In this section, we introduce the genetic algorithm as the optimization technique. The genetic algorithm is one of the newly developed field and one of the hottest topics in research of computational intelligence. Application of genetic algorithm to research of computer architecture is not new. The algorithm is used for research of VLSI design to find the *optimized* area and *optimized* number of VIAs for the situation [17] - [21]. These references and [22] give more details for genetic algorithm which we do not go over deeply. In this study, we only provide the minimum knowledge to understand operations of the genetic algorithm.

#### **3.1.0** General Genetic Algorithm: Background information

The genetic algorithm is inspired from mechanism in the natural world [22]. As we try to emulate flexibilities of a human brain with multi-core processors, the genetic algorithm emulates the optimization mechanism of species such as natural selection, evolution, and mutation. In the natural world, we know that there is natural selection and theory of evolution, which are proposed by Charles Darwin. The natural selection theory tells us that the species with characteristics more suitable to environment will prosper, and the species which cannot survive in the environment will decline in number, and will be terminated eventually [23]. The evolution theory tells us that the species would change its characteristics based on environment through generations [23]. These two theories can explain as we go over the history of Earth. For example, the dinosaurs prospered in a certain time in the ancient earth, but they do not survive in the current era. There might be several different hypotheses for reasons of termination, such as climate changes due to strike of large meteor, and survival races with the small size Mammal species that started to prosper. All of those hypotheses tell us that there might have been dramatic environmental changes in the ancient era and the dinosaurs could not adjust their characteristics to the changes in the environment. There is another mechanism which keeps the varieties of species. In the natural selection mechanism, each species would converge to the optimized characteristics, but the other mechanism generates the diversity in the species. This mechanism is called mutation. With mutation, the genes of the offspring generation would have different traits from the parent generation.

We introduce several terms which are commonly used in the genetic algorithm prior to going over the operations of the genetic algorithm. Most definitions that we use come from [22]. To implement the genetic algorithm, we need to decide the targets of optimization and how we evaluate systems with the objective we define. The targets of optimization are anything that can be evaluated with numeric values from distance of travels in the Traveling Salesman problems (TSP) to areas and numbers of VIAs in VLSI designs [21] [24] [25]. The method of evaluation is called the *fitness function* and numerical values obtained from *fitness functions* are called the *fitness values*. The numeric data of *fitness values* represents quality of measurement of the objective. To establish the *fitness function*, we also need to decide how we represent systems with some DNA like combinations, which is called *chromosome*. In other words, *chromosome* is representation for a possible candidate configuration of a whole system. Each entry in *chromosomes* represents some traits of a system, as each set of entries in DNA represent some kind of characteristics. For example of TSP, *chromosome* is the traveling path which travelers will follow to visit necessary cities, and the entry in *chromosome* or *gene* corresponds to a specific city which he has to visit. Set of multiple *chromosomes* is called *population*.

At the initial stage, general genetic algorithm produces a set of *chromosomes* up to *population* size which is defined by designer, and would not change the *population* size for the entire algorithm. We usually use random generation method, in which each *gene* in *chromosomes* is set randomly to include various *chromosomes* in *population*. We identify these initially generated candidates as *population* of the *first generation*. After we set *population*, we pick up parents of offspring with some methods such as random, weighted random, and other methods. With chosen parents, we use some methods to create set of offspring. One of the commonly used methods in process of offspring

generation is called *crossover*. With the *crossover* operation, children have some common pattern of genes from both parents. As the name implies, crossover generates the offspring by exchanging some gene pattern between parents which is similar to mechanism of gene pattern succession in the offspring. Example of crossover is displayed in Figure 3.1. After generating a candidate or candidates of next population, we implement the mutation operation. This changes part of gene pattern randomly. Example of mutation is also displayed in Figure 3.1. Then we evaluate generated offspring and old generation with fitness functions. With fitness values and superiorities of *fitness values* that we decide, we sort entire set of *chromosomes* which contains both offspring and the entire *population* of previous generation. Then we implement termination mechanism to adjust the number of *chromosomes* in the *population* to the size of *population* we decide to use. After creating the new *population*, we designate this set as *population* of the second generation. In other words, we increment generation number each time we create new *population*. The processes after production of population of the first generation are repeated continuously till certain conditions are achieved. This condition is identified as stopping criteria. Examples of stopping criteria are optimized candidate have sufficient *fitness value* or maximum generation we define is passed. Figure 3.2 shows a flowchart of the genetic algorithm. The term *iteration* is used to count the number of repetitions for the entire flowchart in Figure 3.2.

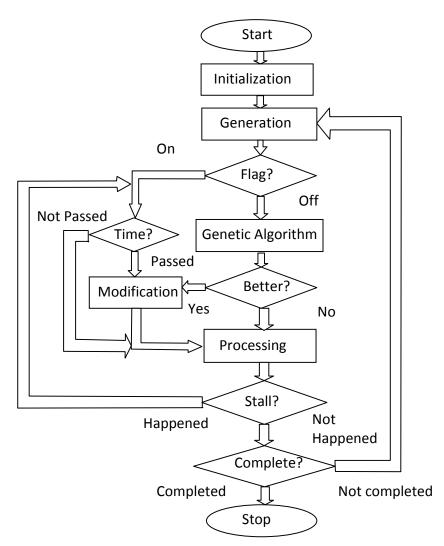

Figure 3.2 Operation flowchart for the genetic algorithm

There is significant benefit for applying the genetic algorithm as the optimization technique. The genetic algorithm is an optimization algorithm which has both global search and local search abilities. With the *crossover* operation, we implement the local search. With mutation operation, we implement the global search, which checks randomized candidate other than similar candidates which we produce with *crossover*. In conventional optimization algorithm, most algorithms have only one search method, not both. Also the conventional optimization technique uses the sequential evaluation, in which the algorithm generates only single candidate, evaluates and compares with the current system. Example of sequential optimization is simulated annealing [25]. For the genetic algorithm, we use the parallel optimization. We can find better candidates, more efficiently since we check more candidates simultaneously and choose better candidates.

In this section, we discuss the general genetic algorithm. As we close this section, we define two terms: *global optimum* and *local optimum* according to [23]. The *local optimum* is better candidate than all other candidates in terms of *fitness values* among results of the current search. The *global optimum* is best candidates among all other *local optimum* in terms of *fitness values*. Relationship between these optimums is similar to cost of gas in a certain state. We can find cheapest price of gases in a city when we compare prices inside a city. This cheapest price or *local minimum* might not be cheapest price all over the state or *global minimum* since we might find better result from another city. This terminology would be used in this section. In next section, we go over the genetic algorithm that we implement in our system

#### 3.1.1 Specialized General Genetic Algorithm

In the previous section, we introduce background information for the genetic algorithm. The actual genetic algorithm that we implement in our system has more functions and is slightly different from the general genetic algorithm. In this section, we describe the characteristics of the specialized genetic algorithm.

#### 3.1.1.0 Dynamic population

As we explained in the previous section, the basic genetic algorithm has a fixed size of *population* which is not changed for the entire algorithm. The choices of appropriate size of *population* are one of the hottest topics in research of genetic algorithms. The reason is that the size of the *population* is deeply related to abilities of the *optimization* and time necessary to complete the search algorithm. We can explain this with a simple example. Assume we have the genetic algorithm which implements a fixed number of generations. If we increase the size of the *population*, the possibilities to find *optimized* candidate or the best candidate would be greater than with smaller sizes, but calculation costs of each generation would also expand. On the other hand, if we reduce the size of the *population*, calculation costs will get smaller but, the possibilities to find the best candidate will also decrease. In our *dynamic* system case, we want to reduce the calculation cost as much as possible, but at the same time we want to increase possibilities to find better candidates as much as possible. So the determination of a good *population* size is too sensitive of an issue since the choice of the *population* changes the functionality of algorithm dramatically. To overcome issues related to finding the best population size, we use the dynamic population size approach instead of the fixed

*population* size as [26]. With this approach we start from the relatively smaller initial *population* size which we define. After the genetic algorithm starts, we do not know the *population* size since the size is automatically adjusted according to the current condition of the *optimization* process.

There are several characteristics we have to define for the dynamic *population* approach. Those characteristics are what would be the trigger of change the population size, how we will change it, and how much we will change it. If we do not choose each category carefully, the dynamic *population* algorithm does not work correctly or simply works as the fixed size *population* approach.

The first question we tackle is what would start the process of changing the size of the *population*. Since the dynamic *population* is part of the genetic algorithm which uses the *fitness values* to determine whether candidates are better or not, we can use the *fitness values* of the *population* to trigger changes of the *population* size. There are several different statistical data of the *fitness values*. Examples are the best *fitness value*, the worst *fitness value*, the mean *fitness value*, and the median *fitness value* of the *population*. Within these values, we use the average or mean *fitness value* of the current *population* and the mean *fitness value* of the group which consisted of both the current *population* and the candidates which we generated. This idea came from a question that was asked by then Ph.D. Student Wen-Fung Leong during one of my course presentations. Since the average *fitness value* displays the performance of the optimization process as a whole in a given moment, the dynamic *population* would ensure proper resource management for the search ability of the genetic algorithm. Each

time we obtain the new *fitness values* of candidates and the new *fitness values* of the current *population*, we initiate the process of the dynamic *population* algorithm. As we decide when we will change the size of the *population*, we need to decide how we will change it according to the difference between two average *fitness values*. There are two different resource management strategies we can use to determine how we will change the *population* size. These two methods of resource management are similar to methods that students commonly use in their studying for final exams. Some students prefer spending more time for subjects that they are very good at, and spending less time for topics they hate. As a result, students would answer the question extremely well for the subject they studied and cannot answer the questions they did not study well. Or more simply, students become specialized in specific subjects they like. On the other hand, other types of students would spend more time on subjects which they are not good at and spend less time for the subjects which they feel strong in. These people use time where it is necessary to spend it. Comparing these two types of students, the second type of student has more chances to have better grade point average (GPA). This example is true among different disciplines.

Back to method of resource management, we describe and evaluate two types of strategies for increasing the chance of generating better average *fitness values*. The first type of resource management technique uses more computational resources when we have better average *fitness values* and uses less when we have poor results. In other words, we spend more time where we find better average *fitness values* and less time for where we cannot find good average *fitness values*. This strategy might find a *local optimum* quicker than the other method, but one problem of this method is that the *local*

*minimum* we find is not always the *global minimum* as we describe at the end of the previous section. For the second strategy, we utilize more resources when we have a hard time to find the better average *fitness values* and less when we can easily find better *fitness values*. This method spends more time where we cannot find better average *fitness values* and less time where we find better average *fitness values*.

The comparison of these two strategies in a real situation can be explained with an analogy of open-book/open note exam. Assume we try to solve two different types of questions: questions that we have enough knowledge to solve and questions that we do not have any idea how to solve. To solve the first type of questions, we only need to check the correctness of our memory with books to obtain better scores. In this case, we just have to use resources which relate to the concepts we need. If we just go over each topic in the text books, it is just wasting time and we will end up running out of time to solve the other questions. To solve the second type of questions, we cannot review specific topics since we do not have any idea how we can solve them. We have to go over each topic briefly to find any related concepts which can be used to solve the questions. If we randomly choose specific chapters in books to read in detail, the exam time is too short to find necessary information. The first method of taking exams demonstrates a similar situation as the case when we know the *fitness value* of the *global* optimum. This is not the situation where we are during the search, since we do not know what the *global optimum* is. Therefore, we have to apply the second strategy instead of the first method. In other words, we will increase *population* size when we have a hard time to find better average *fitness values* or very close to *optimum* (either *global* or *local*) and reduce the size when improvement in average *fitness values* is sufficient. In this

method, we would have better opportunities to find the *global optimum*. There is one problem while applying the second strategy: the *population* size might get too small to keep operation of the algorithm correct if we constantly improve the *average fitness values*. We discuss the solution for this issue in the latter section of this chapter.

We have already decided the timing of change and the method of change, but we have not yet finished the argument for the degree of change in the *population* size. This question has also several different strategies such as the constant fixed change method, dynamic fixed change method and proportional change method. We briefly go over each strategy with problems and benefits. The first strategy is simple enough to implement, since the size of change in the population is defined at the beginning of the algorithm. Therefore, we do not have to change it and also we do not have to calculate the degree of change according to the improvement in the average *fitness value*. The problem of this approach is very obvious, the size always changes constantly no matter what the current size of the *population* we have, and how much we improve the average *fitness values*. In extreme example, a result of twenty-five percent improve in the average *fitness value* cause the same degree of change in the *population* size as a result of one percent decrease in the average *fitness value*. Also the impact of change does not take into consideration the change in the *population* size. If we only use a fixed number of candidates to change the *population* size, the impact of change would not be efficient when the size of *population* is large. For example, we would double the size of the *population* if we change its size from 10 to 20. However, there will be only ten percent of increase in the size of *population* if we change the size from 100 to 110. The impact of the changes in the average *fitness value* in the previous two examples is not the same. The second

approach requires several conditional statements to implement the algorithm, so the calculation cost will increase slightly compared to the first approach. The degree of changes in the *fitness values* are reflected in the second approach, but the impact of changes that is dependent on the *population* size is not included in this algorithm. The third approach treats both the degree of changes and the impact of changes. Instead of a fixed size algorithm implemented in the previous two approaches, it uses the proportional changes which are dependent on both the *population* size and the degree of changes in the average *fitness values*. The calculation cost for implementing the third method is slightly greater than the second approach. Even with the disadvantage in the calculation cost, the third approach is worth implementing, since we can change the *population* more dynamically compared to the other approaches.

## 3.1.1.1 Off by one theory

We now explain the method we implement to avoid errors in the algorithm due to the reduction of the *population* size. Since we implement *crossover* operation, we definitely require at least more than two *chromosomes* in the *population*. The method is that we insert new sets of the *chromosomes* into the current *population* whenever the *population* size does not meet the minimum size requirement of the algorithm. New sets of the *chromosomes* are generated with some randomization mechanism.

Before we explain randomization mechanism to fix violation of the minimum size requirement, we go back to several observations we discuss previously. In section 3.0.1, we describe that the current adapted core architecture configuration in the *dynamic* system would not guarantee good performance in the future. This statement is true when we observe processing performance of computer systems. For short time observation, we

can say that current configuration would produce sufficient performance to use as seeds of randomized chromosomes, since the contents of inforuction buffer changes slowly unless it is completely empty. Therefore the current configuration would offer several hints to find the next configuration. If we only add the same configuration to the population, the abilities of both global and local search would decrease. Therefore we need to generate randomized candidates from the current configuration. In the randomization process, we generate candidates according to the off by one theory. This theory tells us that it would be better to change the architecture of only one *reconfigurable* core in the randomization process. This theory is derived from the careful observation of the assumption we made earlier. We assume that during the process of reconfiguration the reconfiguring core cannot process any *inforuction*. Therefore, if we increase the number of core which reconfigure, it implies the number of cores that cannot process *inforuction* in several intervals. As a result, performance of the system would decrease significantly during reconfiguration. Hence, candidates that only change one core would yield similar performance as the current configuration of the system. In most cases, generated candidates would have less performance in the processing power due to the *reconfiguration penalties*. From this observation, we create candidates which randomize only single core from the current configuration, and we insert generated chromosomes into the population to prevent failure of the algorithm and to maintain diversity in the *population*. Figure 3.3 illustrates the flow of the modified genetic algorithm.

Figure 3.3 Operation flowchart for the modified genetic algorithm

### 3.1.1.2 Multiple Crossover Operation with multiple parents

There are several papers which study about the effect of multiple *crossover operations* in the genetic algorithm. Examples of such studies are [27] [28] [29]. The multiple *crossover* operators have one important benefit. This method enhances the global search abilities of the genetic algorithm. Even though the *crossover* operation implements local search, each different *crossover* operator would search through different search spaces. The variety of children in each generation would increase compared to the implementation of single *crossover* operation. Also, the multiple parents would increase the global search ability, since we choose several different sets of parents

for each type of *crossover* operator. So many traits of *chromosomes* are effectively used to create the next *population*.

#### **3.1.1.3 Fitness function**

In this section, we talk about the most important topic of the genetic algorithm. This is not an exaggerated expression since the result of *fitness function* is used for control of reconfiguration and control of the *dynamic* population. We go over several facts that are used to develop our *fitness function*. To compare each configuration of the system, we can use the processing performances of configurations after we complete the process of reconfiguration since they are simple enough to calculate. Even though we know the processing characteristics of each core which we obtain from measurements, the actual performance of cores and systems might be lower than what we calculate. There are three types of barriers that make system performance lower. One of the barriers is the *stall*. The *stall* is the time we cannot have the full abilities of processing power since some *infoructions* are not ready to process [9] or we have too much stock of *inforuction* in the *inforuction buffer*. This is caused by dependencies in *inforuction*. In the *stall* condition, systems cannot obtain any new *infoructions*.

Another barrier has a *similar* effect as the *stall*, but the cause of this barrier is slightly different. We name this barrier *empty-running*. As the name implies, the system does not store sufficient amounts of specific types of *infoructions* in the *information buffer* compared to the maximum performance we have. We explain the problem of this situation with an example. We feed each type of *infoructions* into the corresponding *inforuction buffer* each time we pre-fetch. Each *reconfigurable* core in the system processes *infoructions* from this set of *inforuction buffers*. If we have sufficient pre-

fetched *infoructions* for all types of *inforuction buffers*, the system can process as much as possible with its maximum potential and there is no problem for this situation. However, if the *inforuction buffer* contains fewer amounts of some types of *inforuction*, cores cannot utilize the full-processing power as we calculate. It can only process the amounts of *inforuction* in the *inforuction buffer*. After it completes processing, it becomes idle or runs with the emptied *inforuction buffer* till the next set of infoructions is ready.

Another barrier is *reconfiguration penalties*. During reconfiguration, the processing power of systems decreases compared to full specification since several cores are isolated or excluded from our system. After reconfiguration, the isolated cores become active to process *infoructions*. Therefore these performance changes during the process of reconfiguration also make the processing power difficult to use as the *fitness values* of our system. With all three of these barriers together, we cannot use processing power directly to determine the *fitness values* of a given system configuration.

The appropriate *fitness function* should treat all three barriers. We use the predicted amounts of *infoructions* we can process in a certain time interval as our *fitness values*. The detail of *fitness function* is described in expression (3.1). The time parameter t is used in expression (3.1). This time parameter should be longer than the *reconfiguration penalties* since we know the performance of a *dynamic* system during reconfiguration is lower than the system which stays the same as the current configuration. If we take a longer time interval for the parameter t, calculation costs of reconfiguration would increase dramatically since the *fitness function* emulates behaviors of systems to predict amounts of information we might process. To predict the

performance of dynamic systems, we have to predict the amount of *infoructions* which will be generated in the time interval t since the *inforuction* we need to process in the future time is unknown.

Fitness Value = # of infortation that predict to process in time t

= (# of infortation in the infortation buffer after time t)

+ (# of infortation that assume to generate in the given time t)

- (# of infortation in the infortation buffer before) (3.1)

The approach we take for prediction of the future *infoructions* uses the similar concept in the neural network system [30]. In the neural system, we train the network with some sample patterns which model the operation of the system. The neural network trains to obtain the correct result or desirable results in terms of purpose of the system with the differences of simulated results, and preferable results. For our system, we will train our prediction mechanism with the data of the generated *infoructions* which are fed into our *inforuction buffer* whenever we do not reconfigure the system. Our training method is straightforward. We take the data for occurrence of each *inforuction* for a specific time interval. This time interval is related to the time parameter (t) we use in the *fitness function*. As a result of the *fitness value* evaluation, we conclude that we do not have to reconfigure our system, since the current system configuration might have better performance within the time interval (t). Therefore we might not have to reconfigure our system during the time interval. At the same time, we do not have to evaluate the candidates with the genetic algorithm. We use the time interval in which the

optimization process does not operate, and resources which is usually used in the optimization algorithm. We discuss the meaning of the data of *inforuction* occurrences in the later chapter.

We will evaluate the impact of misprediction. The misprediction occurres when the data for occurrence does not correspond to the actual behavior of systems. It happens when sets of *inforuction* produced are changed dramatically from what we observe. The impact caused by the misprediction would not be severe since it is softened by the *inforuction buffers*. This is because the sets of *inforuction* in the *inforuction buffer* should be processed prior to the sets of *inforuction* predicted with the prediction mechanism. In other words, we always have some portion of *inforuction buffer*. Therefore, the ratio of amounts of mispredicted *inforuction* handled in the *fitness function* to the *infoructions* that are predicted to be handled would be always less than 1. Even though there is a possibility of misprediction, our prediction mechanism represents the actual behavior of systems more accurately than the simplest prediction method, which assumes to have exactly the same number of each *inforuction* during our prediction.

As we close this section, we show the flowchart of the *fitness function* in the Figure 3.4. Our *fitness function* is a short time simulation of the system since we need to determine the performance in the future for both types of systems: the system with the current configuration and the system with the candidate configurations during the process of *optimization* for the multi-core system.

Figure 3.4 Operation flowchart for the fitness function

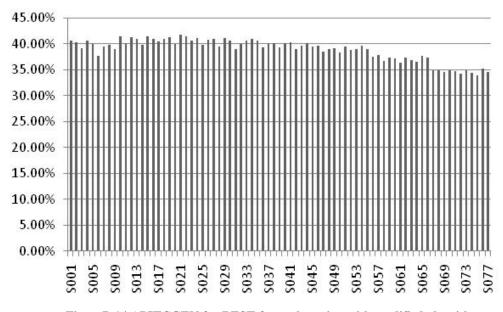

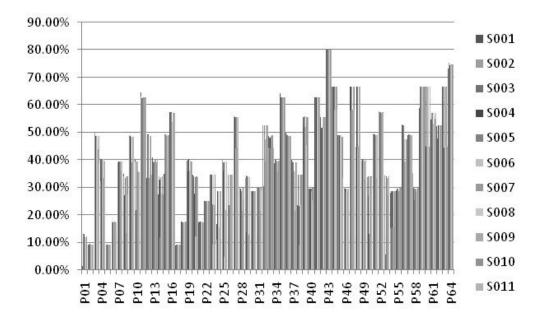

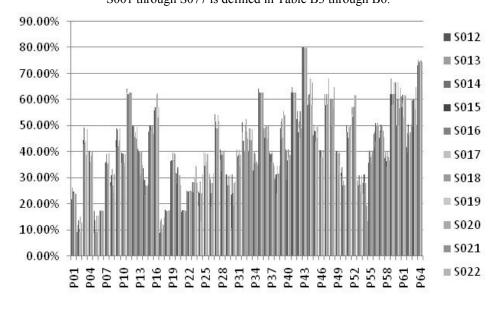

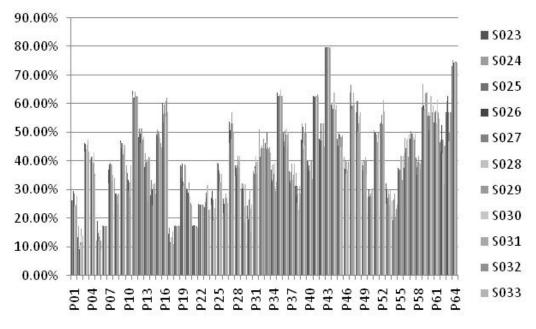

## 3.1.1.4 Running BEST