# DESIGN, CHARACTERIZATION AND AUTOMATION OF AN ULTRA-HIGH TEMPERATURE STANDARD CELL LIBRARY FOR HARSH ENVIORNMENTS

#### BY

#### VENKATARAMAN JEYARAMAN

Bachelor of Engineering

University of Madras

Chennai, India

2001

Submitted to the faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of MASTER OF SCIENCE December, 2004

# DESIGN, CHARACTERIZATION AND AUTOMATION OF AN ULTRA-HIGH TEMPERATURE STANDARD CELL LIBRARY FOR HARSH ENVIORNMENTS

| Thesis Approved:             |

|------------------------------|

| Dr.Chris Hutchens            |

| Thesis Advisor               |

| Dr.Louis Johnson             |

| Dr.Yumin Zhang               |

| Dr.A.Gordon Emslie           |

| Dean of the Graduate College |

#### **ACKNOWLEDGEMENTS**

First, I would like to thank my committee chairman and advisor Dr. Chris Hutchens, through whose patience, understanding, and valuable advice, this work has been accomplished. I would also like to express my gratitude to Dr. Louis Johnson and Dr. Yumin Zhang for serving as my committee members.

I would also like to convey my special thanks to the members of the MSVLSI (Mixed Signal VLSI) Group at the Department of Electrical and Computer Engineering, Oklahoma State University, namely – in no particular order – Dr. Liu, Xunyu Zhu, Narendra Kayathi, Sameer Kadam, Jerry Brewer, Vinay Chitturi, Jianning Wang and Saurabh Kasat for all their help and suggestions along the course of this work.

I would like to thank my Parents and Sister for their encouragement and motivation. I would like to thank my friends for their support. To all of them I dedicate this work.

This work was funded by Halliburton Energy Services.

#### TABLE OF CONTENTS

| Chapter                                                                                                                                | Page     |

|----------------------------------------------------------------------------------------------------------------------------------------|----------|

| I Introduction                                                                                                                         | 1        |

| <ul><li>1.1 Comparison between SOS and Bulk Process.</li><li>1.2 Synthesis Tool-Based Design</li><li>1.3 Thesis Organization</li></ul> | 6        |

| II Cell Library Format.                                                                                                                | 8        |

| 2.1 Introduction to ASIC design 2.2 Standard cell Library Process Flow 2.3. Cell Format 2.4. Example of a cell                         | 11       |

| III Timing Characterization                                                                                                            | 22       |

| 3.1 Background                                                                                                                         | 24       |

| 3.2.1.1 Total Delay Equation                                                                                                           |          |

| 3.2.1.2. Propagation Delay                                                                                                             | 26       |

| 3.2.2 Scalable Polynomial Delay Model                                                                                                  | 29       |

| 3.2.3 Piecewise Linear Delay Model 3.2.4 CMOS2 Delay Model                                                                             | 30<br>32 |

| 3.2.4.1. Total Delay Equation                                                                                                          | 33       |

| 3.2.5.1 Intrinsic Delay                                                                                                                | 34       |

| 3.2.5.4 Connect delay 3.2.5.4.1 Best Case Tree Model                                                                                   | 39<br>40 |

| 3 2 5 4 2 Worst Case Tree Model                                                                                                        | 40       |

| 3.2.5.4.3 Balanced Case Tree Model                               | 40        |

|------------------------------------------------------------------|-----------|

| 3.2.5.5 Interconnect delay                                       |           |

| 3.3 Estimation of Linear Delay Model Parameters                  |           |

| 3.3.1 Linear delay parameters Estimation for Combinational Logic | 44        |

| 3.3.1.1 Intrinsic delay Measurement                              |           |

| 3.3.1.2 Transition delay and Output resistance Measurement       | 46        |

| 3.3.1.3 Slope delay Measurement                                  | 47        |

| 3.3.2 Linear delay parameters Estimation for Sequential Logic    | 49        |

| 3.3.2.1 Estimation of Setup and Hold Time                        | 50        |

| 3.3.2.2 Estimation of Recovery and Removal Time                  |           |

| 3.3.2.3 Estimation of Minimum and Maximum pulse widths           |           |

| 3.4 Estimation of Capacitance and Area                           | 54        |

| 3.5 Estimation of Power dissipation                              | 55        |

| IV Cell Library Validation                                       | 58        |

| •                                                                |           |

| 4.1 Observation:                                                 |           |

| 4.2 Delay Estimation:                                            |           |

| 4.3 Hardware Verification of Cell Library.                       |           |

| 4.3.1 DC and Functional Verification:                            |           |

| 4.3.2 Delay model verification for Combinatorial Logic           |           |

| 4.3.3 Delay model verification for sequential Logic              | 02        |

| V Measurements and Results                                       | 86        |

| 5.1 Measured Delay of Combinatorial Logic:                       | 86        |

| 5.2 Measured Delay of Sequential Logic:                          |           |

| 5.2.1 Benchmark Circuit 1:                                       |           |

| 5.2.2 Benchmark Circuit 2:                                       | 94        |

| 5.3 Power Consumption:                                           |           |

| VI Conclusion and Future Work                                    | 9(        |

|                                                                  |           |

| 6.0 Conclusion: 6.1 Future Work:                                 |           |

| O.1 1 didio 11 OIR                                               | ····· ) i |

| References                                                       | 98        |

| Appendix A                                                       | 102       |

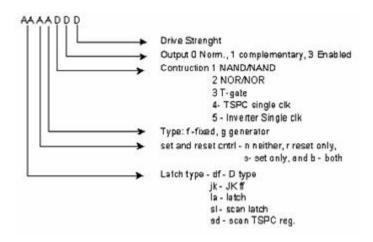

| A.1 Naming convention for Sequential logics.                     | 102       |

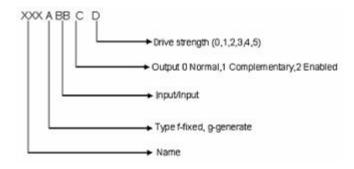

| A 2 Naming convention for other Roolean logics                   | 103       |

| A.4 Latches and Flip Flops | . 106 |

|----------------------------|-------|

| A.5 Padframe cells         |       |

| Appendix B                 |       |

#### LIST OF TABLES

| Table                                          | Page |

|------------------------------------------------|------|

| Table 1.1 Cell geometry definitions and values | 14   |

| Table 4.1 Test Plan                            | 77   |

| Table 5.1 Measured Intrinsic delay             | 87   |

| Table 5.2 Measured Transition delay            | 87   |

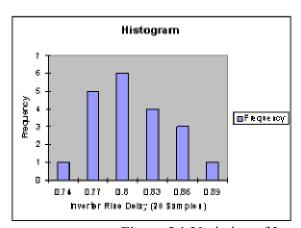

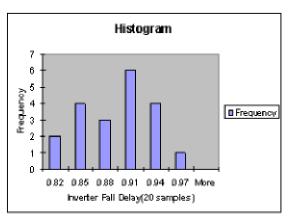

| Table 5.3 5-Sigma Delay Variation.             | 88   |

| Table 5.4 Power Consumption                    | 95   |

#### LIST OF FIGURES

| Figure                                                                              | Page |

|-------------------------------------------------------------------------------------|------|

| Figure 1.1 Comparison of standard bulk CMOS to Peregrine USTi® [1]                  | 2    |

| Figure 1.2 VTC curve of 3-Input NAND gate                                           | 3    |

| Figure 1.3 Variation of Kp and Threshold with Temperature                           | 4    |

| Figure 2.1 ASIC Design Flow [21]                                                    | 9    |

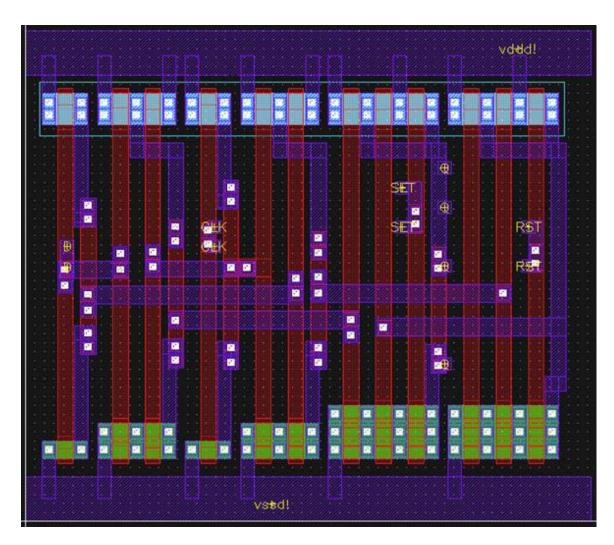

| Figure 2.2 Layout for logic cell library                                            | 14   |

| Figure 2.3 Definition of Routing Pitch [2]                                          | 15   |

| Figure 2.4 The general layout of a complete SE-routed chip [2]                      | 18   |

| Figure 2.5 Stacking of Cells by SE [2]                                              | 19   |

| Figure 2.6 Active high D Latch with Async Set and Reset                             | 20   |

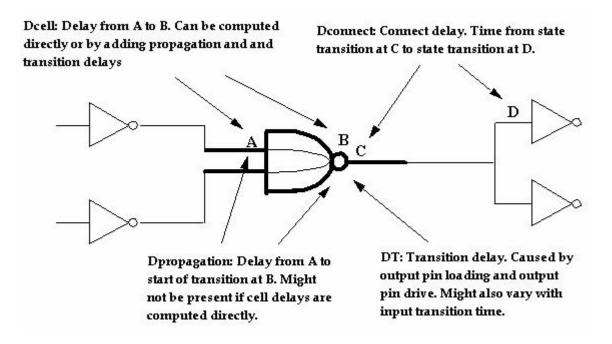

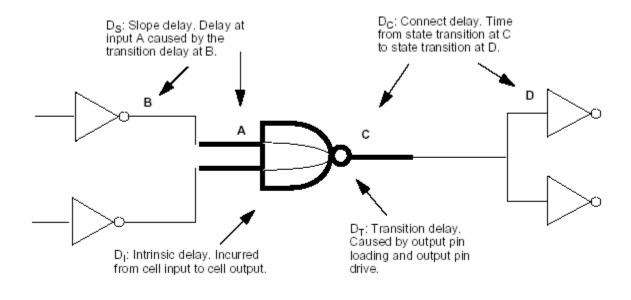

| Figure 3.1 Delay Equation Components for CMOS Nonlinear Delay Model [6]             | 27   |

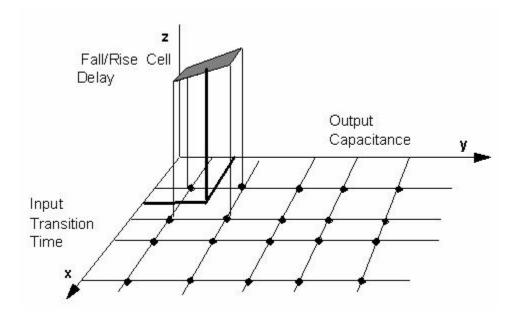

| Figure 3.2 Variation of Cell Delay with Input Transition and Output Capacitance [6] | 27   |

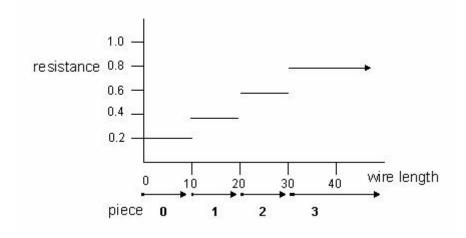

| Figure 3.3 Variation of resistance with wire length [6]                             | 31   |

| Figure 3.4 Intrinsic delay definition [2]                                           | 35   |

| Figure 3.5 Transition delay definition [2]                                          | 37   |

| Figure 3.6 Transition delay definition [2]                                          | 38   |

| Figure 3.7 Modeling of Connect delay [6]                                            | 41   |

| Figure 3.8 Linear delay model parameters for 2-input NAND gate [6]                  | 42   |

| Figure 3.9 Estimation of Resistance [2]                                             | 43   |

| Figure 3.10 Intrinsic delay measurement.                                            | 44   |

| Figure 3.11 Intrinsic delay waveform                                             | 45 |

|----------------------------------------------------------------------------------|----|

| Figure 3.12 Transition delay measurement.                                        | 46 |

| Figure 3.13 Transition delay waveform                                            | 47 |

| Figure 3.14 Slope delay measurement                                              | 48 |

| Figure 3.15 Slope delay waveform                                                 | 49 |

| Figure 3.16 Setup time measurement for positive edge Flip flop [2]               | 50 |

| Figure 3.17 Recovery and Removal time measurement for positive edge Flip flop    | 53 |

| Figure 4.1 Four input NAND gate showing Parasitic Capacitances                   | 59 |

| Figure 4.2 Four Input NAND gate equivalent RC Circuit.                           | 60 |

| Figure 4.3 Four input NOR gate showing Parasitic Capacitances                    | 65 |

| Figure 4.4 Four Input NOR gate equivalent RC Circuit                             | 66 |

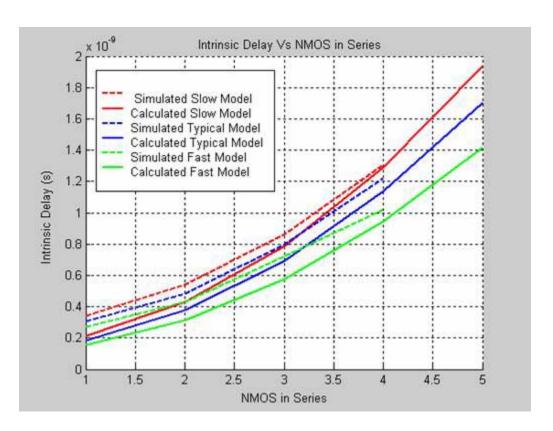

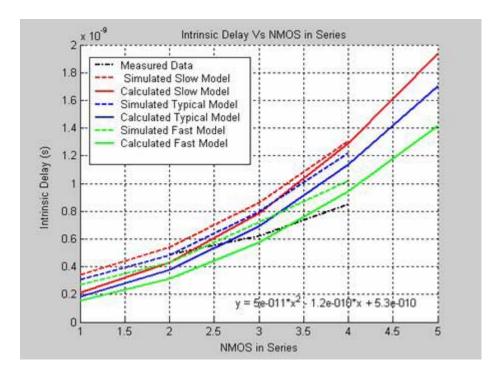

| Figure 4.5 Intrinsic Fall Delay Vs NMOS in Series (195°C)                        | 69 |

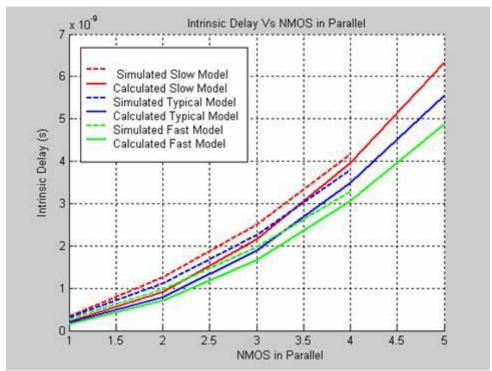

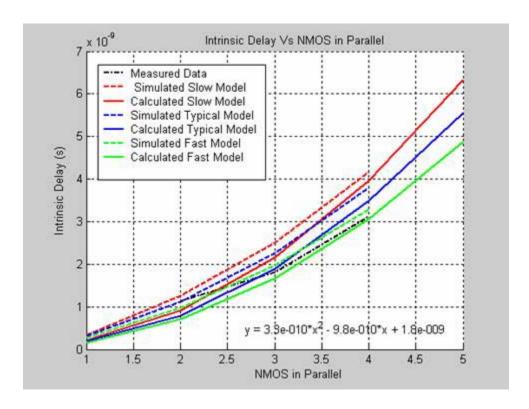

| Figure 4.6 Intrinsic Fall Delay Vs NMOS in Parallel (195°C)                      | 70 |

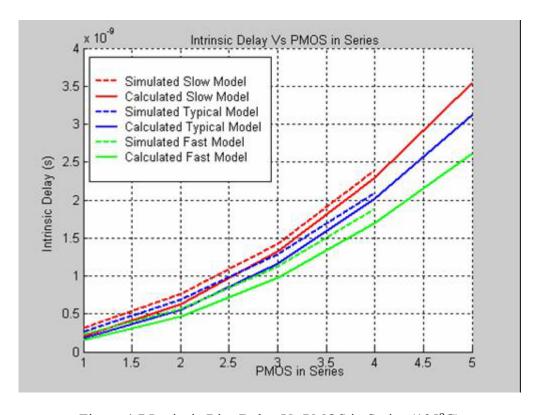

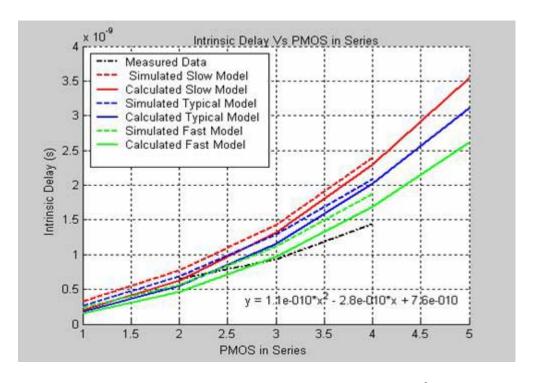

| Figure 4.7 Intrinsic Rise Delay Vs PMOS in Series (195°C)                        | 70 |

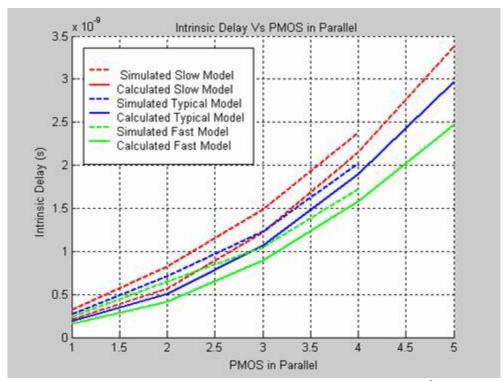

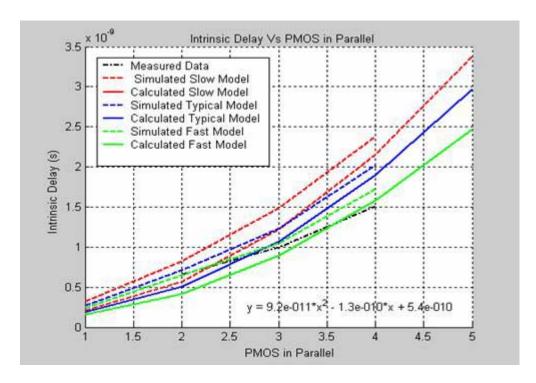

| Figure 4.8 Intrinsic Rise Delay Vs PMOS in Parallel (195°C)                      | 71 |

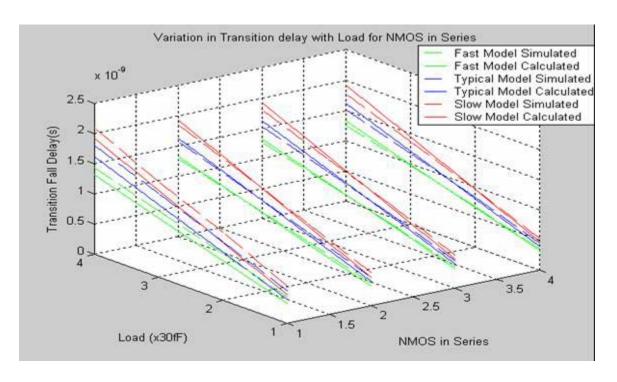

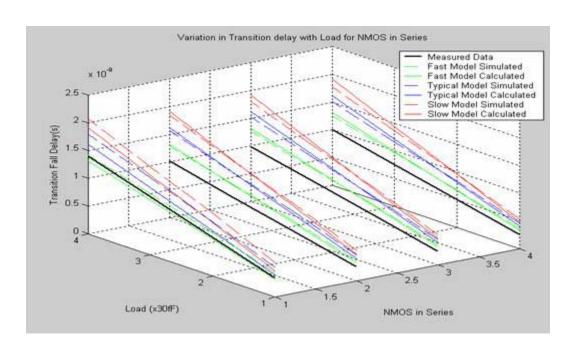

| Figure 4.9 Variation in Transition delay with Load for NMOS in Series (195°C)    | 72 |

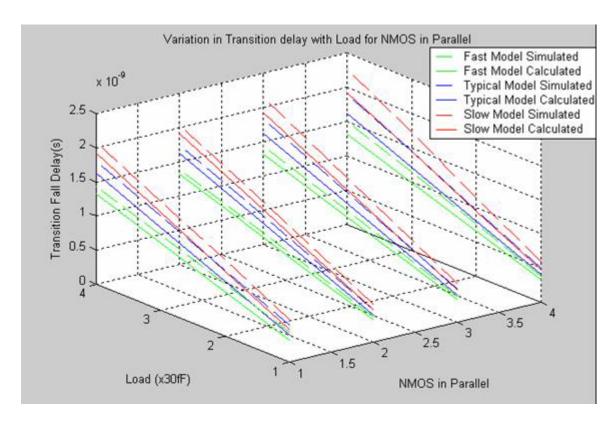

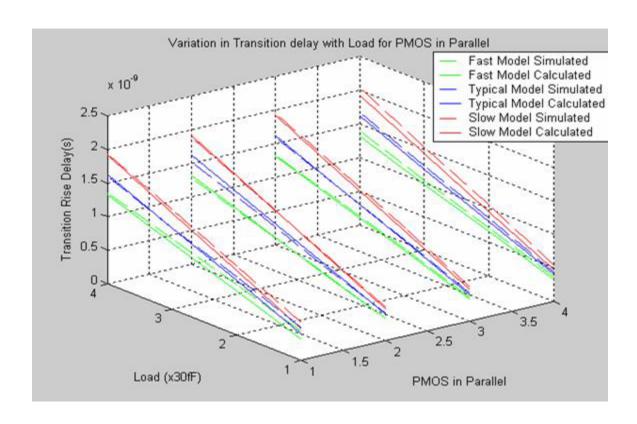

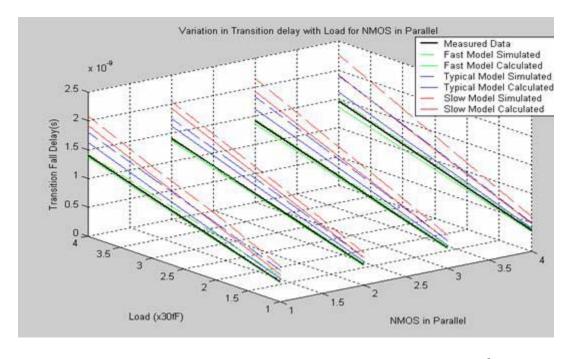

| Figure 4.10 Variation in Transition delay with Load for NMOS in Parallel (195°C) | 72 |

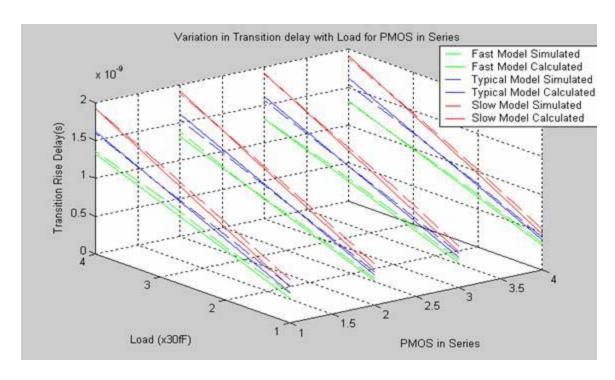

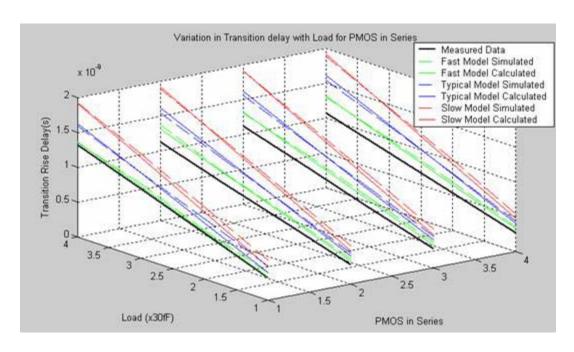

| Figure 4.11 Variation in Transition delay with Load for PMOS in Series (195°C)   | 73 |

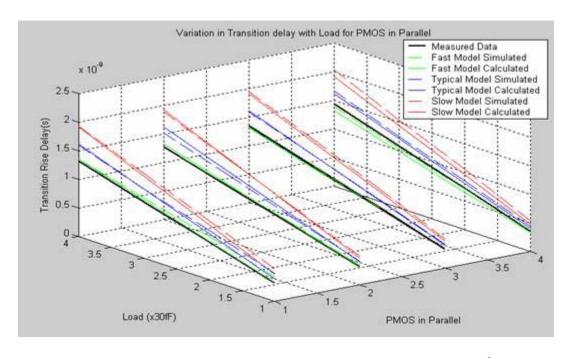

| Figure 4.12 Variation in Transition delay with Load for PMOS in Parallel (195°C) | 73 |

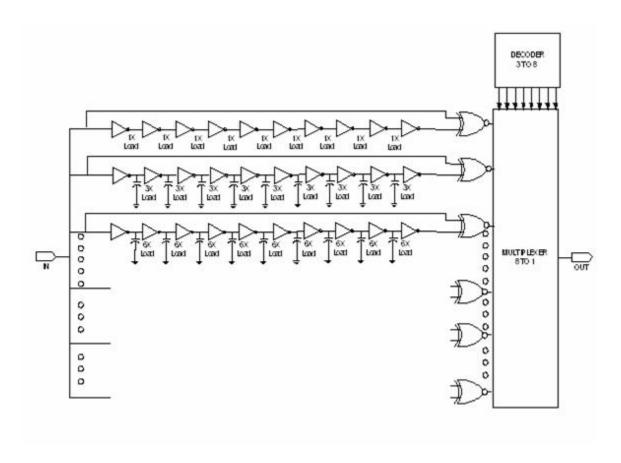

| Figure 4.13 Benchmark Circuits 1 for Functional Verification                     | 75 |

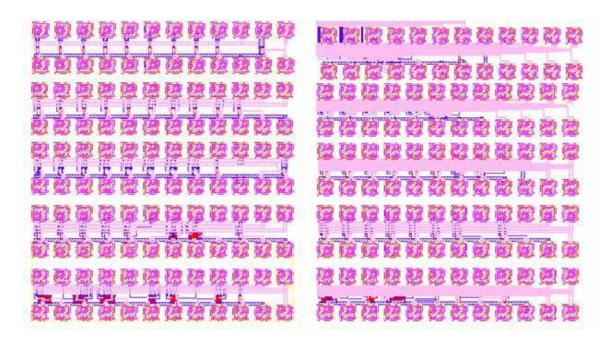

| Figure 4.14 Cadence Implementation of Renchmark circuits 1                       | 76 |

| Figure 4.15 Single Input Delay Chain                         | 78  |

|--------------------------------------------------------------|-----|

| Figure 4.16 Multi Input Delay Chain                          | 79  |

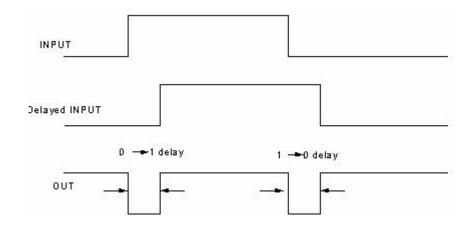

| Figure 4.17 Pulse Generator Waveform                         | 79  |

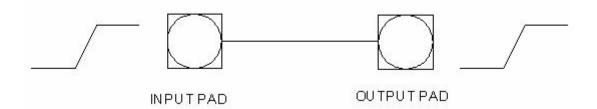

| Figure 4.18 I/O Buffer Characterization                      | 79  |

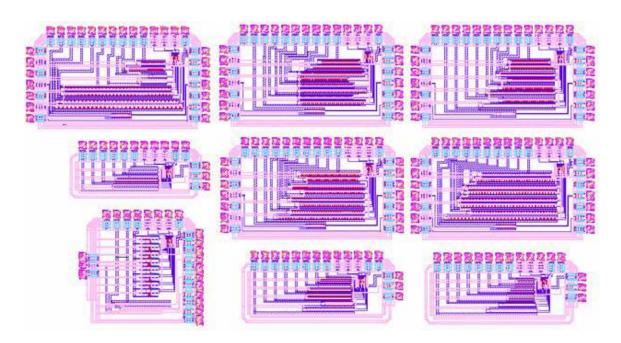

| Figure 4.19 Cadence Implementation of Test Plans             | 81  |

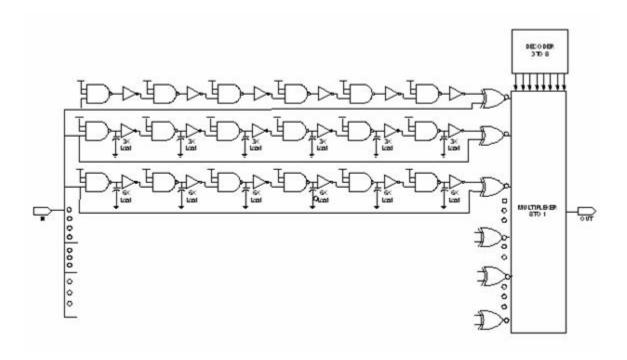

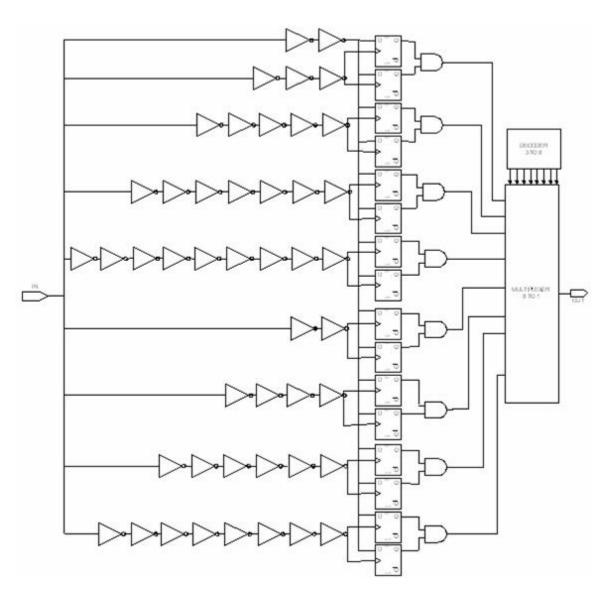

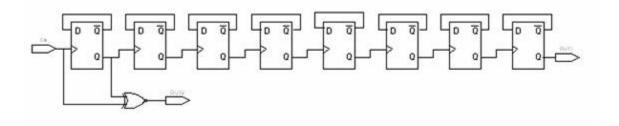

| Figure 4.20 Sequential Benchmark Circuit 1                   | 83  |

| Figure 4.21 Sequential Benchmark Circuit 2.                  | 84  |

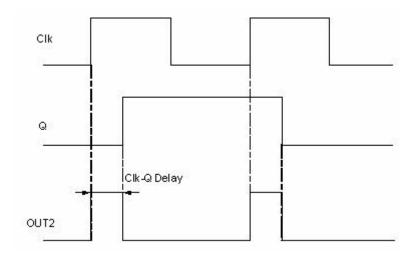

| Figure 4.22 Clock to Q Delay Waveform                        | 85  |

| Figure 5.1 Variation of Inverter delay with die samples      | 86  |

| Figure 5.2 Intrinsic Fall Delay Vs NMOS in Series (195°C)    | 88  |

| Figure 5.3 Intrinsic Fall Delay Vs NMOS in Parallel (195°C)  | 89  |

| Figure 5.4 Intrinsic Rise Delay Vs PMOS in Series (195°C)    | 89  |

| Figure 5.5 Intrinsic Rise Delay Vs PMOS in Parallel (195°C)  | 90  |

| Figure 5.6 Transition Fall Delay Vs NMOS in Series (195°C)   | 91  |

| Figure 5.7 Transition Fall Delay Vs NMOS in Parallel (195°C) | 91  |

| Figure 5.8 Transition Rise Delay Vs PMOS in Series (195°C)   | 92  |

| Figure 5.9 Transition Rise Delay Vs PMOS in Parallel (195°C) | 92  |

| Figure A.1 Naming Convention for Sequential Logic            | 102 |

| Figure A 2 Naming Convention for Combinational Logic         | 102 |

#### Glossary

- g<sub>x</sub> Horizontal grid spacing.

- g<sub>y</sub> Vertical grid spacing.

- s<sub>s</sub> Safety zone required to avoid butting DRC errors.

- w<sub>p</sub> Power rail width

- h Height of the cell

- w<sub>use</sub> Usable cell width

- D<sub>I</sub> Intrinsic delay

- D<sub>S</sub> Slope delay

- D<sub>C</sub> Interconnect delay

- D<sub>T</sub> Transition delay

- T<sub>period</sub> Time Period

- $T_{SU}$  Setup time

- $T_{\rm HD}$  Hold time

- T<sub>Clk-Q</sub> Clock to Q propagation delay

- R<sub>out</sub> Output Resistance

- C<sub>L</sub> Load Capacitance

- f Number of fan-ins

- R'<sub>P</sub> Rise resistance of inverter

$R'_{N}$  Fall resistance of inverter

C'<sub>p</sub> PMOS gate capacitance of inverter

$C'_n$  NMOS gate capacitance of inverter

N<sub>ML</sub> Low noise margin

N<sub>MH</sub> High noise margin

V<sub>th</sub> Threshold voltage

V<sub>T</sub> Thermal voltage

C<sub>ox</sub> Gate oxide capacitance

$\mu_0$  Zero bias mobility

m Subthreshold swing coefficient

W Width of transistor

L Length of transistor

F Number of fingers

## Chapter 1

#### Introduction

In the recent years there has been a significant increase in the complexity and operating temperature of integrated circuits. As the complexity of circuit designs grows, it is becoming highly impossible to design and layout those circuits by hand. As the operating temperature increases, conventional bulk-Silicon devices fail to operate due to the drift of bulk device parameters. This project is focused to overcome these problems by building a cell library with SOS technology that can work at ultra-high temperatures (200°C).

#### 1.1 Comparison between SOS and Bulk Process

In conventional bulk-Silicon circuits the active elements are placed in the thin surface layer and a depletion layer isolates it from the silicon body. The leakage current of the PN junctions so formed exponentially increases with the temperature and is responsible for several serious reliability problems. Excessive leakage currents and high power dissipation limits the operation of bulk-Silicon circuits at high temperature. Another important limitation of bulk-Silicon circuits is the formation of parasitic n-p-n and p-n-p transistors in the neighboring insulating tubs resulting in latch-up and significantly degrades circuit performance.

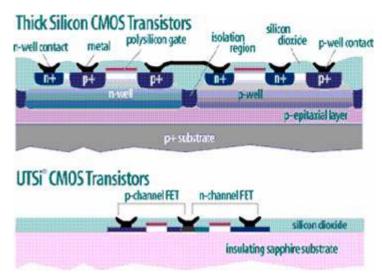

Figure 1.1. Comparison of standard bulk CMOS to Peregrine USTi® [1]

The drift in the device parameters of bulk CMOS device at elevated temperatures significantly affects the correct operation of both digital and analog circuits in terms of stand-by power dissipation, bandwidth, and precision and eventually results in complete loss of functionality or even to an extent of destruction of the device due to thermally-induced latch-up[19].

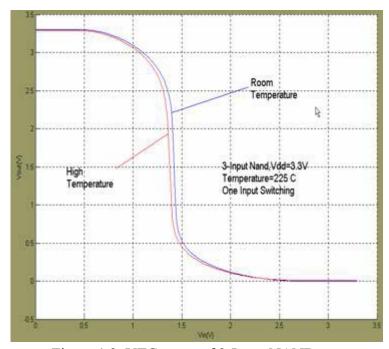

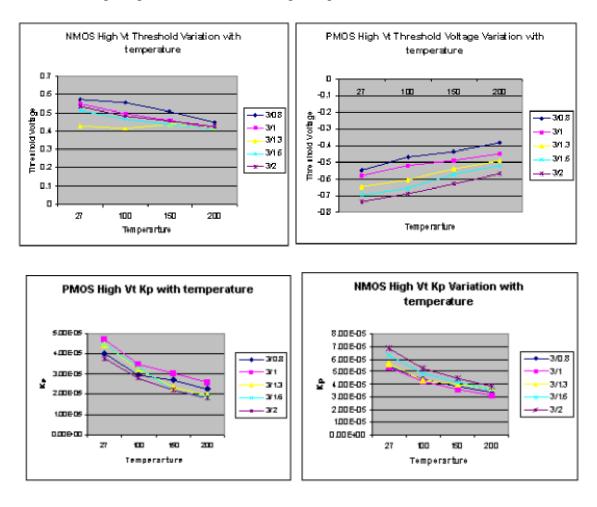

The focus of this thesis is to build a robust standard cell library for Ultra-High Temperature. A number of factors were considered to accomplish the successful operation of the cell library. From previous work done, the transistors were characterized to know the variation of mobility and threshold with variation in (W/L) ratios and temperature. At 225  $^{0}$ C, the SOS 3 input NAND gate shows only slight variations of noise margin, switching point and maximum gain.

Figure 1.2. VTC curve of 3-Input NAND gate

The main challenge to make the cell library robust is to minimize the leakage current by selecting the correct value of L without affecting the bandwidth too much. Traditionally the leakage of the chip is estimated using the leakage per micron obtained from sub-threshold behavior of the transistors.

The sub threshold current can be expressed based on the following [20],

$$I_{ds} = \mu_0 C_{ox} \frac{W}{L} (m-1) (v_T)^2 \times e^{(V_g - V_{th})/mv_T} \times (1 - e^{-v_{DS}/v_T})$$

$$m = 1 + \frac{C_{dm}}{C_{ox}} = 1 + \frac{\frac{\mathcal{E}_{si}}{W_{dm}}}{\frac{\mathcal{E}_{ox}}{t_{ox}}} = 1 + \frac{3t_{ox}}{W_{dm}}$$

Where  $V_{th}$  is the threshold voltage, and  $v_T = KT/q$  is the thermal voltage,  $C_{ox}$  is the gate oxide capacitance;  $\mu_0$  is the zero bias mobility and m is the subthreshold swing coefficient.  $W_{dm}$  is the maximum depletion layer width, and  $t_{ox}$  is the gate oxide thickness (approximately 95nm).  $C_{dm}$  is the capacitance of depletion layer. From the above equation the leakage current decreases with increase in the length of the transistor. The length of 1.6um was selected after testing transistors with different lengths to satisfy bandwidth, threshold voltage degradation and noise margin requirements.

Figure 1.3. Variation of Kp and Threshold with Temperature

The reduction of leakage current also results from reduction of the drain junction area and from a change of physical mechanism in SOS [1], the quasi-neutral region surrounding the drain junction is totally suppressed and the generation/recombination mechanisms in the depletion region is dominant so that the leakage current only increases with temperature as intrinsic concentration  $n_i$  instead of square of  $n_i$  as in the case of bulk devices. Subsequently, without even taking into account the very large well-to-substrate leakage currents, SOS has the potential to offer a reduction of static power dissipation by at least 2-3 orders of magnitude at 200 C when compared to bulk. The variation of threshold voltage with temperature is as low as 1 mV/ $^{\circ}$ C because of the suppression of depletion width, which is temperature dependent [1]. From the above plots it is clear that the mobility of PMOS devices are lesser than the NMOS devices, hence the noise margins of the inverters with minimum geometry have  $N_{ML} < N_{MH}$ . In order to maximize the noise margins the transistors are beta matched with a 1.8 beta ratio.

One of the disadvantages of SOS is the floating body problem; hence transmission gates are avoided in the design of cell library. Also previous test results show that for this process the NMOS devices tend to leak more than PMOS devices hence NAND type structures are mostly used with greater frequency than NOR type structures because in NOR type structures there are multiple paths for the NMOS leakage current to flow but in NAND there is only one path for leakage current to flow. Taking into account of all these factors the cell library is built in Peregrine SOS Process for sustaining ultra high temperature and is compatible with synthesis tools such as Cadence and Synopsys.

#### 1.2 Synthesis Tool-Based Design

In general, synthesis tool-based designs are performed using the following steps [2]:

- Description of circuit behavior in some high-level language, such as Verilog, VHDL or System C.

- Compilation of behavioral or RTL description into a logical netlist using logic synthesis tools such as Cadence or Synopsys.

- 3. Translation of the logical netlist into a geometric netlist, followed by placement and routing, with Placement-and-Routing (PNR) tools.

The second step presumes that the design environment already contains descriptions of some structural logic primitives (e.g. primitives for NAND gates, latches, flip- flops, etc), as those primitives will comprise the netlist produced by the synthesis tool. Similarly, the last step presumes that the translation of a netlist to geometric shapes is already defined for the design environment, i.e. The logic primitives referred to by the netlist is already present in some physical library. Hence, for the design environment, a library which contains both physical (i.e. layout) primitives and logic primitives which correspond to those structural primitives must already be present.

Therefore, with this design method, it is mandatory that a standard cell library be present.

Further, the standard cell library should consist of:

- 1. Layout, Schematic and Symbols with a fixed Naming Convention.

- 2. Logic description libraries, both for synthesis and simulation purposes, which features simplified timing and power dissipation modeling capabilities

- 3. Other geometric descriptions as needed by the PNR tools, if the full layout is deemed too complicated for this purpose.

- 4. List of logic primitives which correspond to those cells, including pinout.

### 1.3 Thesis Organization

This thesis consists of 6 chapters. Chapter 2 describes the details of cell library, layout format and its implementation. Chapter 3 describes the literary review of various delay models and estimation of linear delay model parameters. Chapter 4 describes the relationships between intrinsic delay with internal architecture and transition delay with output loading of the cell, hardware test plans for verifying the delay model is generated. Chapter 5 summarizes the measurements and test results and Chapter 6 is conclusion and future work on the cell library.

## Chapter 2

# **Cell Library Format**

The following section starts with an introduction to ASIC design and then describes the process flow for the cell library, design considerations of the cell library, their layout formats, cell grid selection, and an overview of a fully routed chip. A complete listing of all the cells resides in Appendix A. The final section 2.4 shows an example of a cell.

### 2.1 Introduction to ASIC design

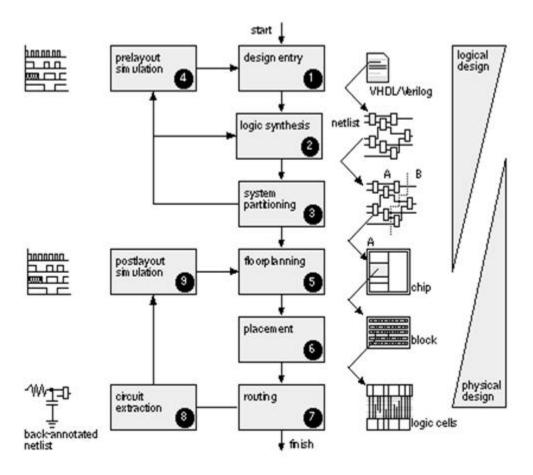

Typically, ASIC design starts with the functional description of the physical layout with some kind of high level hardware language such as Verilog, VHDL or system C. The flow diagram of ASIC design is shown in Figure 2.1.

The flow diagram shows the various steps involved in ASIC design. The cell library contains the description of all the cells to facilitate synthesis for translation of the behavioral code to netlist and have the physical description of the cells for the place and route tool to route the design.

Figure 2.1. ASIC Design Flow [21]

The different blocks in ASIC design are as follows[21]:

- 1. Design entry- Enter the design into an ASIC design system, either using a hardware description language (HDL) or schematic entry.

- 2. Logic synthesis- Use an HDL (VHDL or Verilog) and a logic synthesis tool to produce a netlist—a description of the logic cells and their connections.

- 3. System partitioning- Divide a large system into ASIC-sized pieces.

- 4. Prelayout simulation- Check to see if the design functions correctly.

- 5. Floorplanning- Arrange the blocks of the netlist on the chip.

- 6. Placement- Decide the locations of cells in a block.

- 7. Routing- Make the connections between cells and blocks.

- 8. Extraction- Determine the resistance and capacitance of the interconnect.

- 9. Post layout simulation- Check to see the design still works with the added loads of the interconnect.

The process flow can be divided into two main stages:

- 1. Logical Design- In this phase of the design the designer has more control over the design. This is a very important phase, if the logic is wrong it must be fixed here. The delay format file (.lib) is used to translate the RTL to netlist and this is performed repeatedly to make sure the speed, logic and power satisfy the needs.

- 2. Physical Design In this phase of the design the designer has more control over the area and static timing. The LEF(Library Exchange Format) file is provided to Silicon Ensemble P&R tool, which contains a partial description of all the cells in the library, some design rules pertinent to placement and routing process (such as metal and via spacing) and routing rules defined by the designer of the library (such as pitch and direction of metal tracks).

Steps 1–4 are part of logical design, and steps 5–9 are part of physical design. There is some overlap. For example, system partitioning might be considered as either logical or physical design. To put it another way, when we are performing system partitioning we have to consider both logical and physical factors[4]. It is important to note that both the steps are an iterative process until speed, power and area criteria are met.

#### 2.2 Standard cell Library Process Flow

Basically, the process involves three stages: creating the standard cells, extracting timing from each cell to create the timing file for synthesis and creating physical description library for place and routing. Creating standard cells involves selecting the right cells for the cell library drawing layouts according to specifications, schematics and symbols performing LVS and extracting SPICE level netlist for each cell. The timing is extracted using OCEAN (Open Command Environment for Analysis) Scripting which automates spice simulations to extract the intrinsic rise time, intrinsic fall time, rise resistance, fall resistance, setup time and hold time from the cells, an example script for an inverter is in Appendix B. These timing information is put together to form a .lib file which can be used by synthesis tool to convert the Behavioral code to verilog netlist and meet timing constraints.

Physical design involves in creating the LEF file from Abstract generator, which basically has the definitions of different routing layers and preferences of these layers in routing, the area of each cell along with the dimensions of the power and ground rails and the pin positions of each cell so that the router can route the I/O pins.

However created, each cell in an ASIC cell library must contain the following:

- A physical layout

- A behavioral model

- A Verilog/VHDL model

- A detailed timing model

- A test strategy

- A circuit schematic

- A cell icon

- A wire-load model

- A routing model

The physical layout describes the actual dimension of the cell with all the pin connections. The behavioral model describes the function of the cell without any actual dimensions of the cell. A Verilog/VHDL model is used to describe the cell during synthesis. While a detailed timing model of the library is used during synthesis for the synthesizer to optimize the design and verify the timing requirements of the design. A detailed test strategy is required to evaluate the performance of the cell library before it is actually used to generate layouts and is explained later. A circuit schematic is required to perform LVS with layout and make sure it is error free. A wire load model is needed to estimate the parasitic RC delay of the interconnects. Synthesizers do not take wire delay into account while synthesizing hence a separate wire load model has to be provided to the synthesizer and the additional wire delay forced on to the total delay of the design. A routing model is necessary for proper routing of the design in order to avoid large skews in the design and care must be taken while routing global signals such as clock lines where large skews could affect the performance of the design. Hence good clock tree models have to be developed and included in the cell library.

#### 2.3. Cell Format

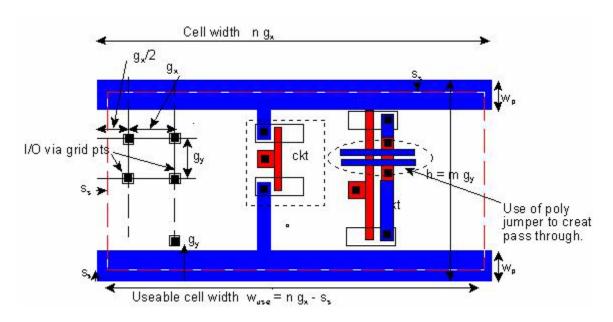

Below, in Figure 2.2, is a summary of the layout rules for the standard cell library. The power rails are 5um wide, routed horizontally in metal1. The I/O of the cell is routed vertically in metal2 over the cell, connecting to terminal pins defined by labeled metal2-metal1 pins. All I/O pins are placed on a  $g_x$  by  $g_y$  grid (called routing pitch), which starts  $g_x$  in from both vertical edges and  $g_y/2$  in from the horizontal cell edge. All cells will be n  $g_x$  by m  $g_x$ . Since there is over-the-cell routing, I/O terminals can be placed anywhere on the predefined grid points.

Also since routing tools use fixed-grid two-level routing the terminals must have a center-to-center spacing along both axes [9]. The overall width of the cell is an integer multiple of  $g_x$ . All metal1 must be wholly contained between the power rails, only polysilicon and locos are allowed to extend to within  $s_s$  of the cell boundary. Metal2 runs vertically with Metal1 running horizontally when used. The grid spacing  $g_x$  and  $g_y$  are set respectively by the minimum spacing of two m1 m2 vias.

Figure 2.2. Layout for logic cell library.

| Parameter                 | Value (um)                         | Comment                        |

|---------------------------|------------------------------------|--------------------------------|

| $g_{x}$                   | 2.2um                              | Horizontal grid                |

|                           |                                    | spacing.(isolated metal width) |

| $\mathbf{g}_{\mathrm{y}}$ | 2.2um                              | Vertical grid spacing.         |

| $S_{S}$                   | 0.5um                              | Safety zone required to avoid  |

|                           |                                    | butting DRC errors.            |

| $W_p$                     | 5um                                | Power rail width               |

| h                         | 55um                               | m equal 25                     |

| W <sub>use</sub>          | n g <sub>y</sub> - 2s <sub>s</sub> | n must be an integer           |

Table 1.1 Cell geometry definitions and values.

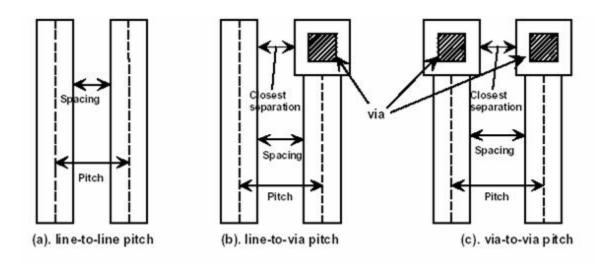

The routing pitch should at minimum be a line-to-via pitch, as defined in Figure 2.3(b), where the closest separation (line to metal extension of via) still satisfies design rule for metal-to-metal separation. Ideally, it should be at least via-to-via pitch (see picture 2.3(c)) which is 2.2um. This will allow the routing tool to drop via where necessary. Using only line-to-line pitch as in Figure 2.3 (a) is avoided as the routing tool may fail since it is unable to drop a via when it is needed. All available metal layers follow the rules, even if there is no intention to actually use it for routing. Two metal layers are

available for routing during the LEF file generation, and this will allow the routing tool to decide which metal layer will actually be used. This in turn will more likely result in better routing.

In a multi-metal process, if for any reason the routing pitch is not identical for all metal layers, then the ratio of pitch between any two metal layers should be kept simple, such as 2:1 or 3:2 (ideally should be 1:1 if possible). Complex ratios, such as 11:9, should be avoided. In this library 1:1 routing pitch is used so that the router can drop a via where ever needed.

Figure 2.3. Definition of Routing Pitch [2]

The transistors are stacked horizontally, with their width parallel to the vertical axis as shown in the above figure. The maximum width of any single PMOS transistor is 18 um, with the largest NMOS 9 um. While larger widths could be drawn the widths are set as such to minimize gate delay. Larger effective device widths must be composed of multiple fingers. Multiple fingers are designated by the following nomenclature

F@Wum. Where F is the number of fingers and W is the width of the finger. In addition, poly and n locos may also be used within the cell proper as an interconnect material however; all runs must be less than 16 squares. For example if you tap the center of the input line poly of an inverter you can have full 32 squares in series or for 1 um wide ploy this is better than a 16 um ploy run to each gate from the input.

The cells are tiled horizontally and vertically, so there must be no design rule violations when cells are abutted. This keeps all cell poly, metal1 and locos a minimum of  $s_s$  from the north and south edges of the power rail and the east and west edges of the cell. No metal1 or metal2 should be placed outside the power rails, as this would conflict with the router.

Generally, no metal2 is used inside the cell, as it must be made available for external routing and I/O connections. Every unused metal2 slot is used for a routing channel over the cell. The library contains a total of 89 cells. Cells present include the range of 2, 3 and 4 input "simple" gates -- nand/and, nor/or, muxes, and-or / or-and, etc. There are a wide range of inverters and buffers, 1X to 4X, to cover a range of drivable loads. There are 8 types of flip-flops, and 10 latches. Lastly, there are various adder and subtractor bit slices and pad cells.

For the SOS process ( $V_{TN} = 0.720 \text{V}$ ,  $V_{TP} = -0.850 \text{V}$  at room temperature [24]) high  $V_T$  devices are chosen as  $V_T$  degrades with temperature and still has the required noise margin, the average delay through an inverter is 0.3ns. For gates with longer stacks of

devices -- a four-input NOR, for example -- the delay can range up to 4.5ns. The effective switched input capacitance of the typical 1X inverter is a mere 30fF. Using a 3-input NAND gate as a more typical gate, the "average" gate has a delay of 0.9ns, and an energy consumption of 81.6 fJ at 3.3V. This corresponds to 81.6nW per MHz of effective throughput.

All gates are "optimal noise margin" ratioed and as a result the effective Wn to Wp ratio is 1.8 for all gates. By example for a 1X inverter  $(W/L)_n$  equal 2um/1.6um and  $(W/L)_p$  equal 3.6um/1.6um. For a 3x 3 input NAND  $(W/L)_n$  equal 3x3x2um/1.6um or laid out as 3@6um/1.6um while  $(W/L)_p$  for the PMOS devices is 3x3.6 um/1.6um (10.8um/1.6um) No NMOS or PMOS device is less than 2um/1.6um or 3.6um/1.6um or greater than 9um or 18um respectively.

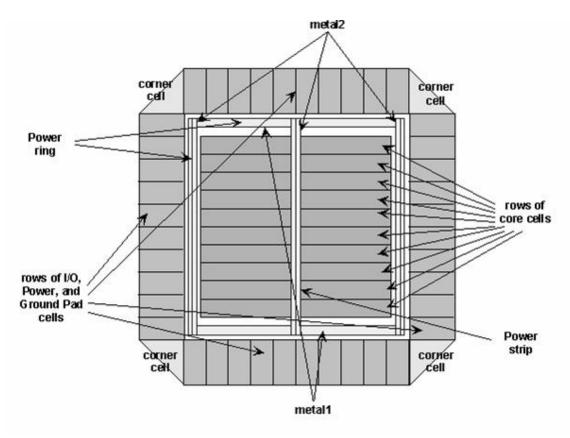

The general layout of Silicon Ensemble chip is as shown in Figure 2.4. The total area of the chip is determined by the padframe and depends on the number of power, ground and I/O pads used.

Figure 2.4. The general layout of a complete SE-routed chip [2]

Inside the padframe is the power ring for equal distribution of power through out the chip and the core cells are placed inside the power ring. For each metal layer, the direction could be horizontal or vertical, but one direction is always taken as the preferred direction, and the other one is automatically non-preferred in this case Metal1 is routed horizontally and Metal2 is routed vertically. The placement of the cells and routing is done according to the verilog netlist given to the SE by the designer. The rules previously discussed are necessitated by the way SE performs routing.

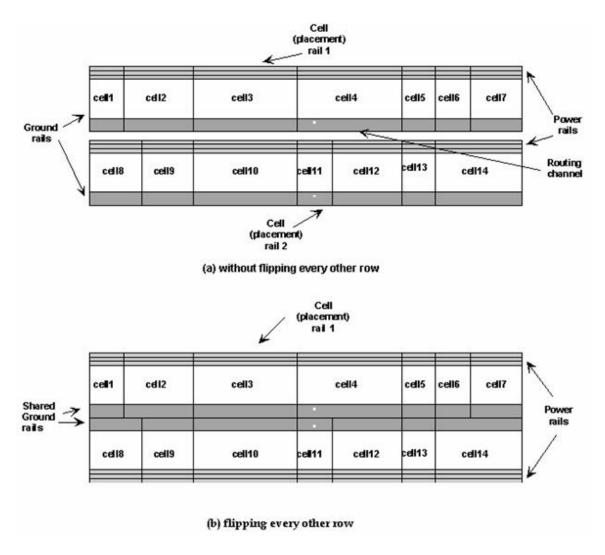

Figure 2.5. Stacking of Cells by SE [2]

The stacking of the cells is as shown in Figure 2.5. There are two ways of stacking the cells inside the power rings one way is to stack them without flipping every other row, this is not used as it consumes more area the other way is to flip every other row so that the power and ground rings are overlapped alternately saving area.

# 2.4. Example of a cell

Figure 2.6 Active high D Latch with Async Set and Reset

Some parameters of the cell:

Cell Width =  $59.4\mu m$  (27 times the pitch)

Cell Height =  $55\mu m$  (25 times the pitch)

Power rails width =  $5\mu m$

Pitch =  $2.2\mu m$

Preferred Directions – Metal1 (Horizontal), Metal2 (Vertical).

Note that in figure 2.6 a safety margin of more than 0.5µm is provided on either side of the cell this would avoid any kind of DRC errors and lets the router to abut the cells without wasting space. The width is always made a integer multiple of the pitch so that the continuity of routing grids between any two adjacent cells is guaranteed. Poly jumpers are used where ever possible to avoid the use of metal2 since metal2 is dedicated to routing and any use of it would result in the loss of a routing track. Multiple I/O pins are placed in the cells, this enhances the routing process of the router since it can pick any I/O pin at its convenience and thus route efficiently.

## Chapter 3

# **Timing Characterization**

This section starts with the background study of previous works on cell characterization, a literary review of different delay models used by synopsys and a detailed explanation of the linear delay model used to characterize this cell library, with estimation of capacitance and power parameters.

#### 3.1 Background

A number of techniques are available for characterizing the cell library; this work focuses on the simple and accurate characterization method. This section gives a brief explanation on the previous works on the characterization process. In particular, since the CMOS Generic timing model (Linear timing model) used by synopsys tools is largely based on Penfield-Rubinstein-slope model[5], most of the works on timing characterization discussed here will be the ones which focuses on the particular model.

In [2] Jos B. Sulistyo and Dong S. HA used the linear delay model to characterize the cell library. In their work the most commonly used 50%-50% delay is used to estimate the linear model delay parameters.

In [4], a method to characterize cell delay and capacitance parameters is proposed by Patel, and a system described for implementing the method. In this characterization technique he determines the actual switching voltages of the cell, as well as delay definition as switching-to-switching voltage instead of the more commonly used 50%-to-50% delay. While this proposed model is more accurate than the linear model for this type of cell, it is highly inconsistent for cases where a cell drives another cell of different type which results in different switching voltages.

Jou et al. in [7,8] proposed techniques to simplify characterization tables for complicated cells these tables can be 2-D or 3-D tables which are more accurate than the linear model. However, exhaustive calculations make the tool much slower. The proposed techniques are particularly useful for cases where the internal structures of the cells are known.

Further, in [3], a similar method was proposed by Cirit, which slightly differs in that it assumes the cell being characterized as a black box and the internal architecture of the cell is not taken into account. Initially this approach was followed to characterize this cell library due to its simplicity, but later a distinct relationship was observed between the delay and internal structure of the cell which makes the characterization process more accurate.

The cell delay model used in this work is the one described in Chapters I and II of [6]. Specifically, for timing characterization, the CMOS Generic delay model is used due to

its simplicity and relatively small numbers of simulations needed to characterize cells with acceptable accuracy. Also, in [5], several delay models are explained by Eshraghian and Weste, one of which, namely the Penfield-Rubenstein-slope model, appears to be identical with the Generic CMOS delay model used here.

## 3.2 Literature review on Different Delay Models

#### 3.2.1 CMOS Non-Linear Delay Model

The CMOS nonlinear delay model [6] uses lookup tables and interpolation to compute delays; this needs intelligent software to do mathematical analysis which makes the process slow. Due to its complexity the model can provide close timing correlation with a wide variety of submicron delay modeling schemes.

This model requires a clear understanding of the following:

- The total delay equation

- Cell delay (D<sub>cell</sub>)

- Propagation delay (D<sub>propagation</sub>)

- Transition delay (D<sub>transition</sub>)

- Connect delay (D<sub>Connect</sub>)

## 3.2.1.1 Total Delay Equation

The delay analysis of this model involves calculating the total delay of a logic gate i.e. the delay between the input pin of a first gate and the input pin of the next gate as shown in Figure 3.1. This includes four major components:  $D_{cell}$ ,  $D_{propogation}$ ,  $D_{transition}$  and  $D_{connect}$ .

If the cell delay tables are available for a timing arc, the total delay equation [6] is

$$D_{total} = D_{cell} + D_{connect} (3.1)$$

If the propagation delay tables are available instead, the total delay equation is

$$D_{total} = D_{propagation} + D_{transition} + D_{connect}$$

(3.2)

#### **3.2.1.2** Cell Delay

The delay contributed by the gate itself, is typically defined as the 50 percent input pin voltage to 50 percent output voltage [6]. Cell delay is usually a function of both output loading and input transition time. D<sub>cell</sub> is computed in two ways, depending on the timing data provided,

- Performing table lookup and interpolation in a cell delay table provided in the library.

- Using the propagation and transition tables, following this equation:

$$D_{cell} = D_{propagation} + D_{transition}$$

(3.3)

## 3.2.1.2. Propagation Delay

$D_{propagation}$  is the time from the input transition to completion of a specified percentage (for example, 10 percent) of the output transition.  $D_{propagation}$  is often a function of output loading and input transition time. If propagation delay tables are defined for a timing arc, cell delay tables must not be specified. The presence of propagation delay tables indicates that cell delays are computed by adding the propagation and transition delays.

#### 3.2.1.3. Transition Delay

$D_{transition}$  is the time required for an output pin to change state. It is used as a term in the cell delay calculation if propagation tables are specified. After applicable transition degradation, Computing  $D_{transition}$  involves performing table lookup and interpolation.  $D_{transition}$  is a function of capacitance at the output pin and can also be a function of input transition time in submicron technology.

## 3.2.1.3. Connect Delay

D<sub>connect</sub> is the time it takes the voltage at an input pin to charge after the driving output pin has made a transition. This delay is also called the *time-of-flight delay*—the time it takes for a waveform to travel along a wire. The CMOS nonlinear delay model computes connect delay by using the same equations as the generic delay model.

The CMOS non linear delay table is dependent on two parameters as shown in Figure 3.2. The Cell Fall/Rise delay has a non linear variation with Input transition time and output capacitance.

Figure 3.1 Delay Equation Components for CMOS Nonlinear Delay Model [6]

Figure 3.2 Variation of Cell Delay with Input Transition and Output Capacitance [6].

#### 3.2.2 Scalable Polynomial Delay Model

Scalable polynomials provide a smaller and faster alternative to nonlinear lookup tables. However they still need curve-fitting methods to convert the characterization data into computationally efficient polynomial equations with sufficient user-defined accuracy [6]. This makes this model complex. Currently, synthesis tools generate polynomials depending on the variables supported by the nonlinear delay model tables based on input transition time and the output capacitance load. One major disadvantage is that while synthesis tools use this model they do not currently support temperature and voltage effects.

This model needs a clear understanding of the following:

- Polynomial representation

- Model description

Scalable means that the form and order of the polynomials are determined by, or scaled according to the given data. Given a predefined accuracy, it is possible to model almost any delay data with polynomials.

The advantage of using a predefined set of polynomials is that it attempts to fit all cases with accuracy and efficiency using an arbitrary equation at the cost of complexity. However, it allows having a single library instead of multiple libraries for different operating conditions.

The process of library development of scalable polynomial models is similar to that of non linear model development; a circuit level simulator such as spice is required for characterizing the library. However, an additional step is required which uses curve fitting methods to translate the characterized data into computationally efficient polynomial equations to achieve sufficient user-defined accuracy.

#### 3.2.2.1. Polynomial Representation

A number of numerical computations involve polynomials; the fundamental theory of polynomials typically involves a Taylor series [6], where an analytical function is expressed as a finite series of polynomials.

The complete decomposed polynomial form represents the scalable polynomial delay model syntax. The following example shows two variable functions, but it is easy to extend to the case of more variables. A two-variable polynomial function  $D_{x,y}$  can be written as  $D(x,y) = P_m(x)Q_n(y)$ , where x and y are variables and  $P_m$  and  $Q_n$  are the mth-and nth-order polynomials, respectively. There are (m+1) (n+1) coefficients for any given m or n, as the follow equation illustrates.

$$P_{1}Q_{2} = (a_{0} + a_{1}x_{1})(b_{0} + b_{1}x_{2} + b_{2}x_{2}^{2}) = A_{00} + A_{10}x_{1} + A_{01}x_{2} + A_{11}x_{1}x_{2} + A_{02}x_{2}^{2} + A_{12}x_{1}x_{2}^{2}$$

(3.4)

#### 3.2.2.1. Model Description

The scalable polynomial delay model syntax allows three variable polynomials to be specified. The three dimensions are slew, input load, and output load. The model considers analytical parameters (that is, physical parameters) that affect the delay calculation results to be variables.

For a large data set with abrupt changes, the entire operating region cannot be represented by a single polynomial equation. In this case a piece wise delay model is more helpful to specify breakpoints over the characterization data domains.

The error distribution patterns between the fitted equation and data sets, generally result in the use of two kinds of curve fitting algorithms; Least Square Error (LSR) and Least Square Relative Error (LSRE). The choice of the fitting algorithm depends on the values of characterization and the level of accuracy needed.

#### 3.2.3 Piecewise Linear Delay Model

In the Linear delay model the effect of different wire lengths on a net is overlooked. The equations used by a piecewise linear model to calculate timing delays takes into consideration the delay effects of the actual length of wire has on various components of the total delay equation. The wire is divided into pieces based on the length with each length having a different delay associated with it.

This is achieved by assigning different values for resistance and capacitance values to different lengths of the wires. Hence this model has an overload of assigning resistance and capacitance values for all ranges of wire lengths.

Figure 3.3. Variation of resistance with wire length [6]

The total delay is defined as the delay between the input pin of a gate and the input pin of the next gate, which includes the connect delay (piecewise delay) from the driving pins to the load pins. This delay modeling divides the total delay in a network into four physical components whose sum is the total delay through a circuit element:

$$D_{Total} = D_I + D_S + D_C + D_T (3.5)$$

Where,

$D_{\rm I}$  - Intrinsic delay inherent in the gate, independent of any particular instantiation and zero load is applied.

D<sub>S</sub> - Slope delay caused by the ramp time of the input signal.

D<sub>C</sub> - Interconnect Delay i.e. delay due to wire load calculated using piecewise model.

D<sub>T</sub> - Transition delay caused by loading of the output pin.

All the above parameters are similar to the CMOS Generic delay model, and will be discussed in detail in section

## 3.2.4 CMOS2 Delay Model

The CMOS2 delay model uses advanced methods for modeling the effect of input signal ramp times of cell delays. Although a high level of accuracy is achieved by using the CMOS2 delay model to calculate propagation delays, the computational complexity of the model makes it less preferred [6].

The delay model requires a clear understanding of the following:

- Total Delay Equation

- Intrinsic Delay

- Transition Delay

- Edge-rate Delay

- Connect Delay

#### 3.2.4.1. Total Delay Equation

The following equation calculates the total delay for the CMOS2 delay model.

$$D_{cell} = D_I + D_T + D_E ag{3.6}$$

$D_I$  and  $D_T$  are Intrinsic and Transition delay respectively and are the same as in the CMOS Generic delay model. The total delay equation has another term called Edge-Rate  $Delay(D_E)$  which requires a detail explanation..

#### 3.2.4.2. Edge-Rate Delay

The incremental delay caused by the input edge rate is modeled as the Edge-Rate Delay. The edge-rate delay calculations in the CMOS2 model allows for a definition of the nonlinear variation of the delay caused by the input edge rate. Edge-rate delay is modeled as a two-piece, piecewise linear incremental delay. The required calculations draw on a set of parameters that characterize the edge rate of an input signal to the cell.

#### 3.2.5 CMOS Generic delay Model or Linear Delay Model

This delay model is mathematically the simplest form of delay model which allows rapid characterization with modest number of simulations, while still achieving an acceptable accuracy [2]. Due to its simplicity it is widely used for characterization of cell libraries.

In this model, transition delay is modeled to be linearly proportional to load capacitance, while slope delay is modeled as linearly proportional to the transition delay of the driver. The linear delay model divides the total delay of a network into four physical components whose sum is the total delay through a circuit element:

$$D_{total} = D_{Intrinsic} + D_{Transition} + D_{Slope} + D_{Connect}$$

(3.7)

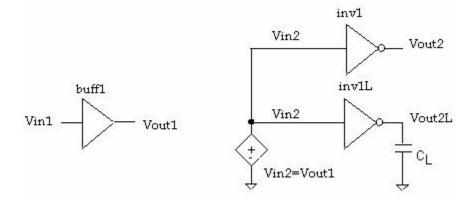

## 3.2.5.1 Intrinsic Delay

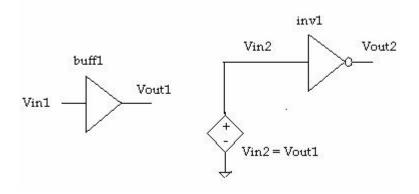

The **Intrinsic delay** (D<sub>Intrinsic</sub>) of a cell is defined as the propagation delay of the cell without any load applied to its output, when it is driven by another identical load less cell. It is also called the fixed (or zero load) delay from the input pin to the output pin of a circuit element [2]. This means that both the driving and driven cell should be load less. It is not practical to measure such a delay as this is a hypothetical condition. However, it is possible by means of simulation to measure it. This means that the driver cell must drive the driven cell indirectly as shown in Figure 3.4.

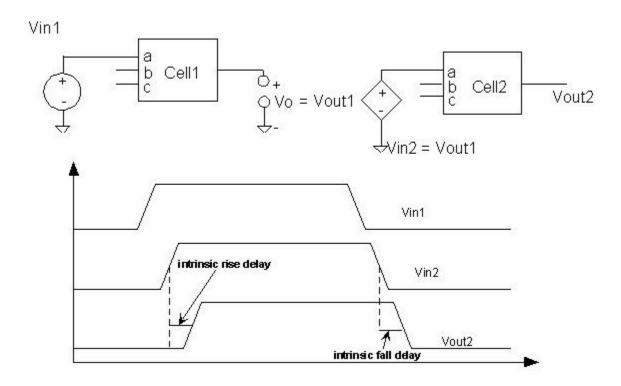

Figure 3.4 Intrinsic delay definition [2]

The output of Cell1 (Vout1) drives the input of Cell2 (Vin2) indirectly. The intrinsic rise delay may differ from the intrinsic fall delay and depends on the internal architecture of the cell and each input may have different intrinsic delays, do there can be six different delays from the above circuit with three inputs there are three different intrinsic rise delays and three different intrinsic fall delays.

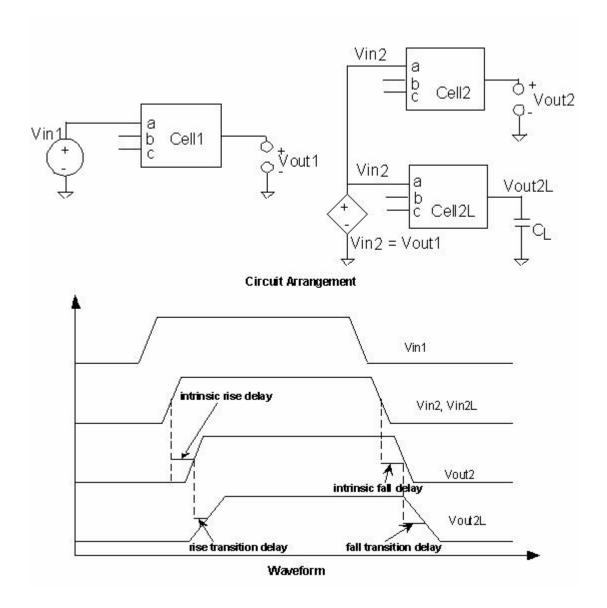

#### 3.2.5.2 Transition delay

The **Transition delay** (D <sub>Transition</sub>) is defined as the additional delay of a cell in the loaded condition, but driven by another identical load less cell, it is the time it takes the output of the loaded cell to change state [2]. The transition time of the output pin on a net is a function of the capacitance of all pins on the net and the capacitance of the interconnect network that ties the pins together.

The equation for transition delay can be modeled as:

$$D_T = R_{Cell} (C_{wire} + C_{pins})$$

(3.8)

This equation calculates the rise and fall delays of the cell. This delay is caused as the result of a cell having to drive a capacitive load causing the output to transition less steeply compared to the load less case as shown in Figure 3.5 and also increases delay with the load.

Transition delay is of two types, the rising transition delay is given by,

$$D_{Transition_{risin \, g}} = R_{Cell_{rise}} \times C_{Load(pin+wire)}$$

(3.9)

The falling transition delay is give by,

$$D_{Transition_{falling}} = R_{Cell_{fall}} \times C_{Load(pin+wire)}$$

(3.10)

Figure 3.5 Transition delay definition [2]

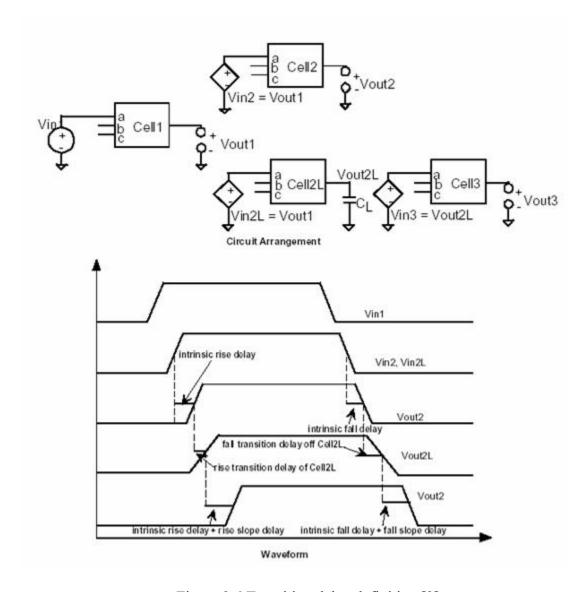

# **3.2.5.3** Slope delay

The Slope delay  $(D_{Slope})$  is an incremental time delay caused by slowly changing input signals; this is due to the transition delay of the driver, when it directly drives the driven cell, due to the input capacitance of the driven cell.

This transition delay causes the output slope of the driving cell to be less steep than the one without load capacitance. This slow ramp signal causes an additional delay at the output of the driven cell.

Figure 3.6 Transition delay definition [2]

This delay is a strong function of ramp time, in some technologies this delay does not vary over a wide range of ramp values. Slope delay is included in the delay equation to

allow additional accuracy in the modeling of technologies that are sensitive to input ramp time.

The slope delay is calculated as the product of the transition delay of the previous stage and the slope sensitivity of the cell.

$$D_{Slone} = S_S \times D_{Transition(Prev)}$$

(3.11)

Where,  $S_S$  is Slope Sensitivity factor accounting for the time at which the input begins to rise but has not reached the threshold level at which the channel begins to conduct

$D_{\mathit{Transition}(\mathrm{Pr}ev)}$  is the transition delay calculated at the driver output pin.

For an inverter the Slope delay is of two types, the rising slope delay is given by

$$D_{Slope_{rising}} = S_{S_{fall}} \times D_{Transition_{fall(input)}}$$

(3.12)

The falling slope delay is given by,

$$D_{Slope_{falling}} = S_{S_{rise}} \times D_{Transition_{rise(input)}}$$

(3.13)

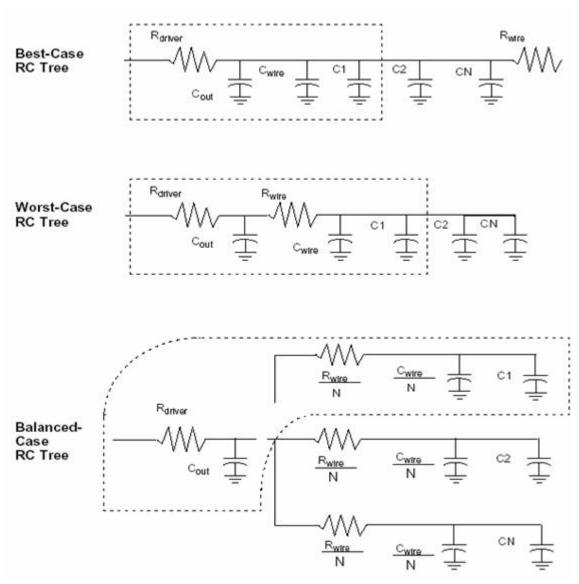

#### 3.2.5.4 Connect delay

The Connect delay ( $D_{Connect}$ ) of an element is the time it takes the voltage at an input pin to charge after the driving output pin has made a transition. This delay is also known as time-of-flight delay, which is the time it takes a waveform to travel along a wire. The connect delay can be modeled as three types. See Figure 3.7.

#### 3.2.5.4.1 Best Case Tree Model

In this model the load pin is physically adjacent to the driver. All the wire capacitance is incurred, but none of the wire resistance must be overcome. Wire resistance is assumed negligible. The best-case connect delay is calculated from the following equation. Because  $R_{\text{wire}}$  is always zero in this case, the resulting DC is always zero.

$$D_{Connect_{hest}} = R_{wire}(C_{wire} + C_{pin}) = 0 ag{3.14}$$

#### 3.2.5.4.2 Worst Case Tree Model

In this model the load pin is at the extreme end of the driver. Each load pin incurs both the full wire capacitance and the full wire resistance, as shown in the following equation.

$$D_{Connect_{worst}} = R_{wire}(C_{wire} + \sum_{pins} C_{pin})$$

(3.15)

#### 3.2.5.4.3 Balanced Case Tree Model

In this model all the load pins are on separate and equal branches of the interconnect wire. In the Balanced case, each load pin incurs an equal portion of the wire capacitance and wire resistance, as shown in the following equation.

Figure 3.7 Modeling of Connect delay [6]

## 3.2.5.5 Interconnect delay

Interconnect delay is defined as the delay caused by the connect delay and transition delay as a result of the number of fan-outs. Interconnect delay can be described by the following equation

$$D_{Interconnect} = D_{Transition} + D_{Connect}$$

(3.17)

Then, the total delay equation can be reduced as

$$D_{total} = D_{Intrinsic} + D_{Interconnect} + D_{Slope}$$

(3.18)

The linear delay model parameters for a 2-input Nand gate is as shown in figure 3.8

Figure 3.8 Linear delay model parameters for 2-input NAND gate [6]

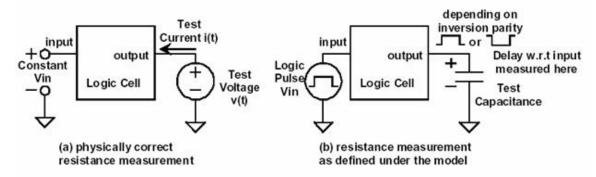

# 3.3 Estimation of Linear Delay Model Parameters

Linear model parameters can be extracted using SPICE simulations, the parameters that need to be extracted are intrinsic delay, cell resistance (Rise/Fall), input capacitance and slope delay. The cell resistance refers to some stipulated linear factor. It does not refer to the resistance that is used in conventional circuits. Normally resistance is defined as the derivative change in current with respect to change in voltage applied at a node as shown in figure 3.9(a).

Figure 3.9 Estimation of Resistance [2]

The resistance in figure 3.9(a) the output resistance is calculated as

$$R_{out} = \frac{d(I_{test})}{d(V_{test})}|_{V_{in} = \text{Constant}}$$

(3.19)

This is the actual small signal resistance of the circuit, and as such is very nonlinear in large signal circuits, In this model the resistance is calculated as a function of delay and load capacitance.

$$R_{out} = \frac{\Delta(delay)}{\Delta(\text{capacitance})}$$

(3.20)

This output resistance can vary for rising delays and falling delays, it can also vary depending which input pin is triggered and how many input pins are triggered, and here we have always accounted for worst case delays while estimating output resistance.

The output resistance is used to calculate the transition delay of the cell by synthesis tools. Though the value of physical definition resistance of a pin stipulates it to be an unique value the value of output resistance has many non unique values whose value depends on which pin triggers the output transition.

#### 3.3.1 Linear delay parameters Estimation for Combinational Logic

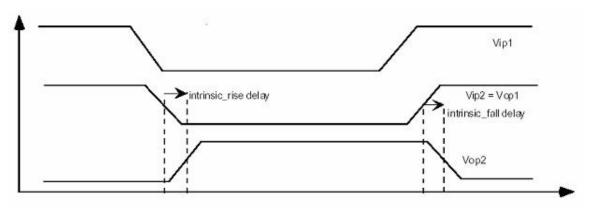

#### 3.3.1.1 Intrinsic delay Measurement

As mentioned previously, the intrinsic delay of a cell is defined as the propagation delay of the cell without any load applied to its output, when it is driven by another identical load less cell. This delay can be found from the measurement setup as below

Figure 3.10 Intrinsic delay measurement

The intrinsic delay is the inherent delay of the circuit and has no dependence on the load of the circuit, this can be measured by simulations but practically it is not possible to measure this directly. However, intrinsic delay can be calculated solving numerically. The cell buff1 of Figure 3.10 is a buffer cell and is used as waveform shaper, it does not drive the inverter directly but is made to indirectly drive the inverter, adding this buffer makes the input wave form less steep and would make it a more typical waveform with zero transition delay.

The waveform in Figure 3.11 shows the measurement of intrinsic delay, the input is passed through an isolation buffer and then fed to then inverter cell.

Figure 3.11 Intrinsic delay waveform

The intrinsic delay is measured for both rising and falling waveforms to determine the intrinsic\_rise and intrinsic\_fall values, all delays are measured as 50%-50% transition delays [2].

#### 3.3.1.2 Transition delay and Output resistance Measurement

The transition delay of the circuit is defined as the delay of a cell under loaded condition, but driven by another identical load less cell, it is the time it takes the output of the loaded cell to change state. Transition delay is calculated as the product of output resistance and load capacitance.

Mathematically

$$D_{transition} = R_{output} \times C_{load}$$

(3.21)

Where

$$R_{Output} = \frac{Intrinsic Delay-Loaded Delay}{Load Capacitance}$$

(3.22)

$$C_{load} = C_{pin} + C_{wire} (3.23)$$

The setup for measuring output resistance is as shown in figure 3.12. The input is fed to the buffer for wave shaping and then coupled to both an inverter without load to find the Intrinsic delay and to an inverter with varying load to determine loaded delay.

Figure 3.12 Transition delay measurement

The load  $C_L$  is varied from 1X to 4X load and the delay is calculated adding the difference in delays from previous loaded condition, this gives the  $\Delta$  change in delay. The output resistance is calculated by dividing this change in delay by the change in load i.e. 4X load. The waveform for measuring  $t_{phl}$  and  $t_{plh}$  is shown in figure 3.13

Figure 3.13 Transition delay waveform

## 3.3.1.3 Slope delay Measurement

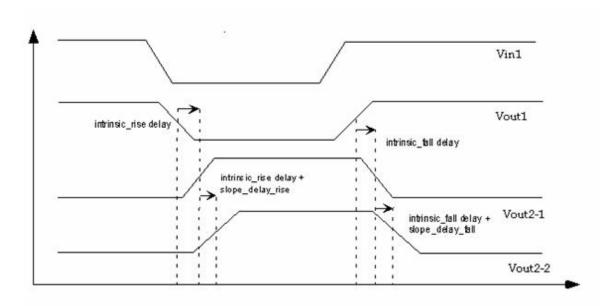

As explained previously slope delay is an incremental time delay caused by slowly changing input signals; this is due to the transition delay of driver, when it directly drives the driven cell, due to the input capacitance of the driven cell. The delay is an additional delay due to the varying input ramp signals at the input pin of the cell. The setup for measurement of slope delay is as shown in figure 3.14.

Figure 3.14 Slope delay measurement

The input ramp is changed and the buffer is used to provide the necessary waveform shaping for the inverter. Due to the change in input ramp an additional delay is added to the output Vout2 which accounts for the slope delay. First the intrinsic delay of the inverter inv1 is calculated using Vin1 as ideal slope, the output Vout1 adds a transition delay which is applied to the input of inverter inv1, then the input ramp is changed and the difference in intrinsic delay of inverter inv1 is calculated, this process is repeated for different ramp values and the slope delay in each case is calculated and their average gives the slope delay of the inverter. This is termed as slope sensitivity in the synopsys library.

There is rise slope sensitivity for both rising and falling edges termed as slope\_rise and slope\_fall respectively. The slop delay waveform is as shown in figure 3.15. Vout2-1 and Vout2-2 are obtained by varying the input slope of Vin1.

Figure 3.15 Slope delay waveform

# 3.3.2 Linear delay parameters Estimation for Sequential Logic.

Sequential cells have to be characterized with additional information in order to model them accurately. In addition to delay, the cells have to be characterized for

- 1. Setup and Hold time.

- 2. Recovery and Removal time.

- 3. Minimum and Maximum pulse widths.

#### 3.3.2.1 Estimation of Setup and Hold Time

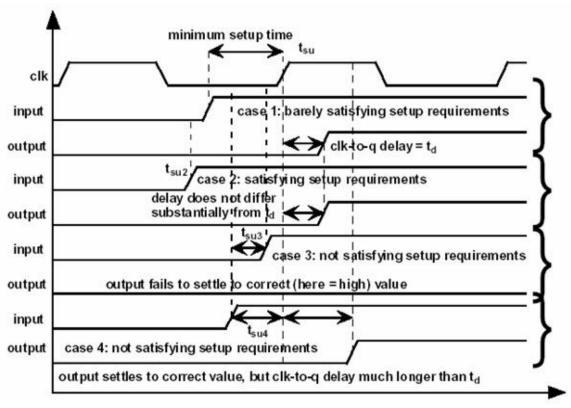

The setup time is generally defined as the minimum time allowed between the arrival of the data and the transition of the clock signal, so that the output signal will reach the expected logical value within a specific delay. If the data arrives later than the setup time an incorrect value is latched at the output [18]. This specific delay is introduced so that the setup does not degrade the clock to Q propagation time more than a pre determined tolerance value. This value must be modeled with reasonable accuracy in order for proper latching of data. The waveform in figure 3.16 shows data arriving times and setup requirements for active high flip-flop.

Figure 3.16 Setup time measurement for positive edge Flip flop [2]

In order to measure the setup time an iterative process is required in which an initial guesses of arrival time for the data is taken such that it satisfies the setup time requirement and the delay from clock-to-Q is calculated. The arrival time of the data with respect to the clock is then decreased until the output reaches 90% of its original value, the time difference between the arrival time of the data and the clock gives the setup time of the flip-flop. A safety margin i.e. of 20% is then added to the setup time. The typical waveforms are shown in figure 3.16 where the data arrival times and the setup requirements for active high flip-flop are demonstrated.

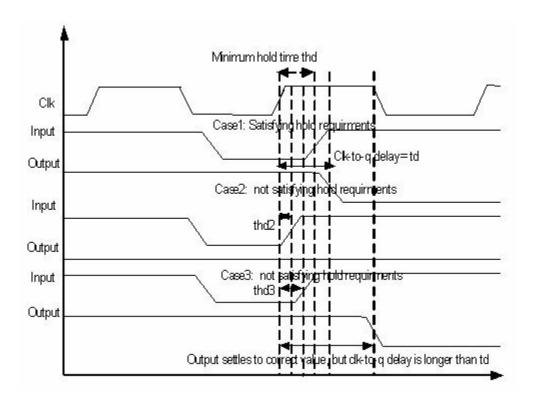

The hold time is generally defined as the minimum time allowed between the transition of the clock and the latching of data such that the output still maintains the expected logic level. If the data changes before the hold time an incorrect value is latched at the output [18].

Hold time measurement is similar to setup time, again it is an iterative process in which an initial latch up time for the data is guessed at such that it satisfies the hold time requirement and the delay from clock-to-Q calculated. The transition time of the data with respect to the clock is then decreased until the output reaches 90% of its original value, the time difference between the clock and the data gives the hold time of the flip-flop, again a safety margin e.g. 20% is added to the hold time. The waveform in figure 3.17 shows the data transition times and the hold requirements for active high flip-flop.

Figure 3.17 Setup time measurement for positive edge Flip flop

# 3.3.2.2 Estimation of Recovery and Removal Time

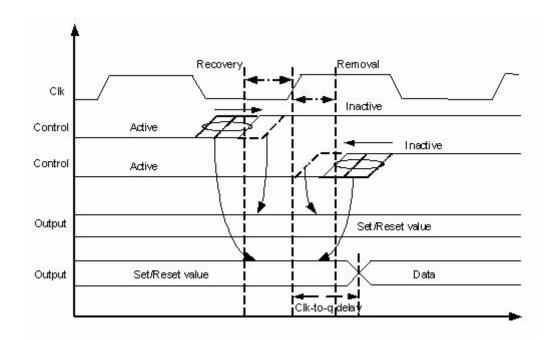

The recovery time is defined as the minimum allowable time between the control pin transition from active to the inactive state and the active edge of the synchronous clock signal [18]. Like the setup time a safety margin is added into the condition of recovery time. The waveform in figure 3.18 shows the recovery and removal times for active high flip-flop.

Removal time is defined as the minimum allowable time between the active edges of the synchronous clock pin while the asynchronous control pin is in transition from active to inactive state [18]. Similar to recovery time a safety margin is added to the removal time

value. Measurement of both recovery and removal times are similar to setup and hold time measurements in their use an iterative process to determine timing.

Figure 3.17 Recovery and Removal time measurement for positive edge Flip flop

The only difference between measuring recovery and removal time of a level sensitive cell to an edge triggered sequential cell is clock transition. For a level sensitive cell clock transition to inactive is the required stimulus condition whereas for an edge triggered sequential cell clock transition to active is the required stimulus condition

#### 3.3.2.3 Estimation of Minimum and Maximum pulse widths

The pulse widths that have to be considered are Clock, Set and Reset. Static CMOS circuits can hold their output indefinitely in the absence of clock hence have no maximum clock width requirements, the minimum clock width depends on the gate

delays of the logic and hence determined by the critical paths of the circuit, which usually far exceed the minimum clock period achievable. These can be measured by decreasing the clock period until the flip-flop fails to produce a desired output. Similarly the minimum SET/RESET pulse width can be calculated by decreasing the pulse width until the flip-flop fails to SET/RESET the output. Generally these signals are used with a generous amount of time; hence their estimation need not be characterized accurately. Since Master-Slave architectures for the flip-flops are used in this library the hold times tend to be shorter or even negative, meaning that the flip-flops or latches can latch data even if the data transition occurs before the clock arrives, hence setup time measurement is critical in these circuits.

# 3.4 Estimation of Capacitance and Area

The input capacitance associated with each pin is the output load for the previous cell. When a gate level power synthesis tool calculates switching power or a synthesis timing analysis tool calculates the delay input capacitance is required. Input capacitance is determined by the length and width of the transistors and can also be obtained from the extracted netlist of the layout.

The capacitance can be estimated from the following

$$C_{Pin} = C_{ox} \times W \times L \tag{3.24}$$

Where

$C_{ox} = \frac{\mathcal{E}_{ox}}{t_{ox}}$ ,  $C_{ox}$  is the gate oxide capacitance,  $\mathcal{E}_{ox}$  is the dielectric constant of silicon

dioxide and  $t_{ox}$  is the gate oxide thickness. W is the width of the transistor and L is the length of the transistor.

The area of the cell can be calculated from the layout of each cell and can be used by the synthesis tool to give a rough estimate of the total area of the chip excluding the routing area.

# 3.5 Estimation of Power dissipation

Power dissipation can be modeled in terms of 3 parameters leakage, short-circuit and dynamic power [9].

$$P_{dissipated} = P_{leakage} + P_{sc} + P_{switching}$$

(3.25)

Leakage power is the power dissipated by the cell when it is in stable condition i.e. there is no signal transition at the inputs or outputs of the cell [10]. Leakage power usually occurs when current carriers diffuse between the diffusion layers and substrate and this current is modeled as the sub threshold leakage per micron obtained from sub-threshold behavior of the transistors.

The sub threshold current can be expressed based on the following [20]

$$I_{ds} = \mu_0 C_{ox} \frac{W}{L} (m-1) (v_T)^2 \times e^{(V_g - V_{th})/mv_T} \times (1 - e^{-v_{DS}/v_T})$$

(3.26)

Where

$$m = 1 + \frac{C_{dm}}{C_{ox}} = 1 + \frac{\frac{\mathcal{E}_{si}}{W_{dm}}}{\frac{\mathcal{E}_{ox}}{t_{ox}}} = 1 + \frac{3t_{ox}}{W_{dm}}$$

(3.27)

Where  $V_{th}$  is the threshold voltage, and  $v_T = KT/q$  is the thermal voltage,  $C_{ox}$  is the gate oxide capacitance;  $\mu_0$  is the zero bias mobility and m is the sub threshold swing coefficient.  $W_{dm}$  is the maximum depletion layer width  $(T_{SI})$  as in case of SOS and  $t_{ox}$  is the gate oxide thickness.  $C_{dm}$  is the capacitance of depletion layer. The power is given by leakage is

$$P_{leakage} = I_{leakage} \times V_{\sup ply} \tag{3.28}$$

The short circuit power is due to a very small current that flows when the PMOS and NMOS transistors are switching simultaneously which results in a short-circuit path from supply to ground, this current flows for a very small period of time.

Since this current is for a very small amount of time it is very negligible.

$$P_{sc} = I_{sc} \times V_{\sup plv} \tag{3.29}$$

The most dominant term is the switching power, this result from charging/discharging of load capacitance. This can be calculated from the following expression.

$$P_{sw} = \frac{1}{T} \int_{0}^{T} v(t) i(t) dt$$

(3.30)

Considering that during the first half of the clock cycle the load capacitor discharges through the NMOS transistor and the second half cycle the load capacitor charges through the PMOS transistor.

$$P_{sw} = \frac{1}{T} \left[ \int_{0}^{\frac{T}{2}} V_{out} \left( -C_{load} \frac{dV_{out}}{dt} \right) dt + \int_{\frac{T}{2}}^{T} (V_{dd} - V_{out}) \left( C_{load} \frac{dV_{out}}{dt} \right) dt \right]$$

$$(3.31)$$

Evaluating the integrals in (3.31), we get

$$P_{sw} = \frac{1}{T} \left[ \left( -C_{load} \frac{V_{out}^{2}}{2} \right) \Big|_{0}^{\frac{T}{2}} + \left( V_{dd} V_{out} C_{load} - \frac{1}{2} C_{load} V_{out}^{2} \right) \Big|_{\frac{T}{2}}^{T} \right]$$

(3.32)

Applying the limits in (3.32), we get

$$P_{sw} = \frac{1}{T} C_{load} V_{dd}^{2}$$

(3.33)

Since  $f = \frac{1}{T}$ , we can rewrite the expression as

$$P_{sw} = C_{load} . V_{dd}^{2} . f (3.34)$$

Hence the switching power for the entire chip can be estimated as

$$P_{sw} = V_{dd}^{2} \cdot f \cdot \sum_{i} C_{i}$$

(3.35)

Where,

$C_i$  is the pin capacitance of each gate which is the load capacitance for previous stage.

However, the tricky part is not knowing the fraction of active gates for a particular application.

# **Chapter 4**

# **Cell Library Validation**

This section of the thesis discusses the procedures followed to validate the cell library. It starts with the observations made during simulations i.e. the relationship between delay and internal architecture of the cells followed by the circuits designed to validate the cell library.

# 4.1 Observation:

In the method proposed by Cirit [3], the cell is being characterized as a black box and the internal architecture of the cell is not taken into account. This is an easy method to estimate the timing of the circuit but does not give us an insight regarding the behavior of the cell with changing architecture. Though the Cirit model was followed to characterize the cell library, due to its simplicity, the simulations revealed a distinct relationship between intrinsic delay and the internal architecture of the cell. Specifically it was observed that the intrinsic delay fits a second order polynomial equation, increasing with the number of PMOS or NMOS either in series or parallel and the total delay varies linearly with increasing load.

# **4.2 Delay Estimation:**

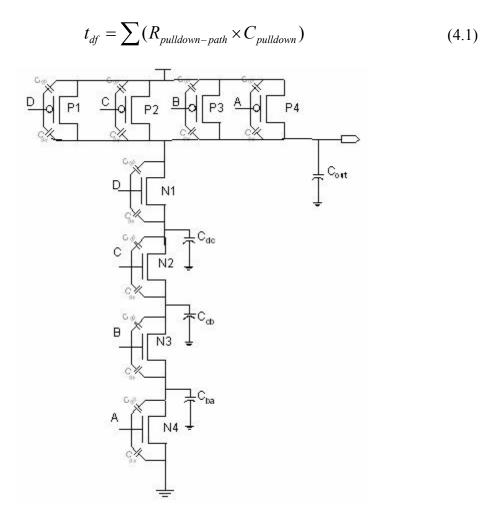

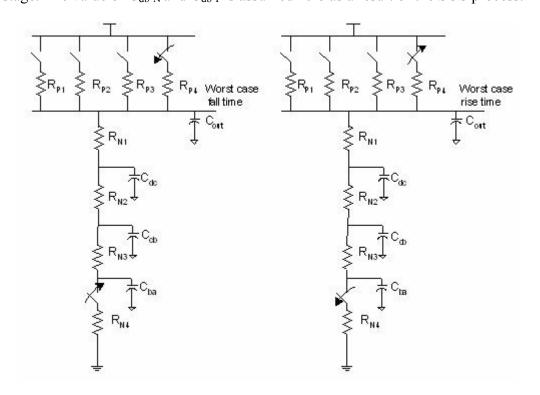

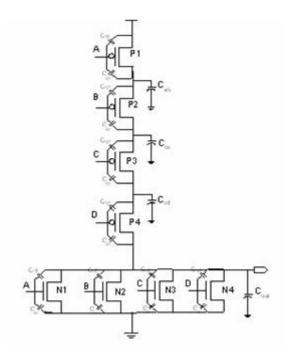

The circuit delay is due to the addition of all the capacitance nodes and resistances involved in switching. Any logic function can be synthesized from circuits which have NAND or NOR gates. First we will analyze NAND gate delays followed by NOR gates. The total fall delay for any input can be calculated using Elmore's delay model:

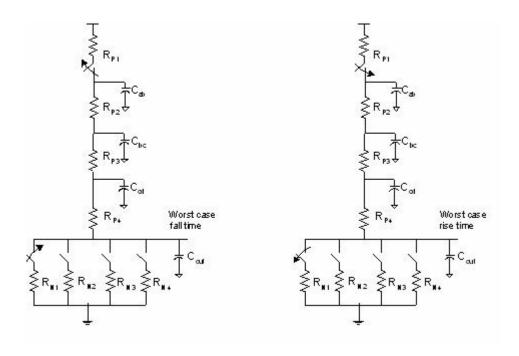

Figure 4.1 Four input NAND gate showing Parasitic Capacitances

For example the fall delay for a four input NAND gate with input A switching is [12],

$$t_{df} = R_{N4}C_{ba} + (R_{N3} + R_{N4})C_{cb} + (R_{N2} + R_{N3} + R_{N4})C_{dc} + (R_{N1} + R_{N2} + R_{N3} + R_{N4})C_{out}$$

(4.2) Where,

$$C_{out} = C_{gd-P1} + C_{gd-N1} + C_L$$

,  $C_{dc} = C_{gs-N1} + C_{gd-N2}$ ,  $C_{cb} = C_{gs-N2} + C_{gd-N3}$ ,  $C_{ba} = C_{gs-N3} + C_{gd-N4}$ .  $C_{gd-P}$  is the gate to drain capacitance of PMOS,  $C_{gd-N}$  is the gate to drain capacitance of NMOS,  $C_{gs-P}$  is the gate to source capacitance of PMOS,  $C_{gs-N}$  is the gate to source capacitance of NMOS and  $C_L$  is the load capacitance i.e. input or gate capacitance of next stage. The value of  $C_{db-N}$  and  $C_{db-P}$  is assumed zero as a result of the SOS process.

Figure 4.2 Four Input NAND gate equivalent RC Circuit

The value of rise resistance is made equal to fall resistance in the case of 4-Input NAND gate by making the width of the NMOS transistor 4 times wider since the resistance is inversely proportional to the width.

$$R = \rho \frac{L}{W} \Omega \tag{4.3}$$

Where L is the length, W is the width of the transistor and  $\rho$  is the equivalent sheet resistance.

Since the NMOS transistors are equal size  $C_{dc} = C_{cb} = C_{ba} = C_n$  and  $R_{N1} = R_{N2} = R_{N3} = R_{N4} = R_N$  and  $R_{P1} = R_{P2} = R_{P3} = R_{P4} = R_P$ . The value for  $C_n$  can be calculated as

$$C_n = C_{gs} + C_{gd} = \frac{1}{2}C_{ox}(L_n \times W_n) + \frac{1}{2}C_{ox}(L_n \times W_n)$$

(4.4)

$$C_n = C_{ox}(L_n \times W_n) \tag{4.5}$$

Since the transistors are scaled according to the number of inputs the capacitance increases with the number of inputs and is given by

$$C_n = f(C_{ox}(L_n' \times W_n')) = f \times C_n' \tag{4.6}$$

Where f is number of fan-in,  $L'_n$  is the length and  $W'_n$  is the width of an inverter.

Similarly the value of C<sub>p</sub> can be calculated as

$$C_p = C_{ox}(L_p \times W_p) = C_p' \tag{4.7}$$

The value of R based on 50%-50% delay is estimated by calculating the change in delay due to change in load and can be calculated as

$$R_{N} = \frac{\Delta Delay_{falling}}{\Delta Capacitance}$$

(4.8)

Similarly,

$$R_{p} = \frac{\Delta Delay_{rising}}{\Delta Capacitance}$$

(4.9)

The values of  $R_N$  and  $R_P$  are calculated from simulation values where  $R_N = \frac{R_N'}{f}$  and  $R_P = R_P'$ . Where, f is number of fan-in,  $R_N'$  and  $R_P'$  is inverter pull down and pull-up resistance respectively.

Replacing the Elmore delay equation with these parameters we get a solution with known parameters.

$$t_{df} = R_N C_n + 2R_N C_n + 3R_N C_n + 4R_N C_{out} (4.10)$$

$$t_{df} = 6R_{N}C_{n} + 4R_{N}C_{out} (4.11)$$

Generalizing the above equation for f number of inputs, the NAND gate will have f PMOS in parallel for pull up circuit and f NMOS in series for the pull down circuit. The width of each NMOS is scaled by a factor of f to make the pull up and pull down resistance equal. The worst case delay occurs when the NMOS near the rail switches.

$$t_{df} = f(R_N C_{out}) + (f - 1)R_N C_n + (f - 2)R_N C_n + \dots + R_N C_n$$

(4.12)

$$= f(R_N C_{out}) + \frac{f(f-1)}{2} R_N C_n \tag{4.13}$$

$$= fR_N \left[ C_{out} + \frac{(f-1)}{2} C_n \right] \tag{4.14}$$

Replacing  $C_{out} = \frac{C_n}{2} + \frac{C_p}{2} + C_L$ ,  $C_n = fC'_n$ ,  $R_N = \frac{R'_N}{f}$  and  $C_p = C'_p$  we get

$$= f \frac{R'_N}{f} \left[ \left[ \frac{fC'_n}{2} + \frac{C'_p}{2} + C_L \right] + \frac{(f-1)}{2} fC'_n \right]$$

(4.15)

$$=R'_{N}\left[\frac{C'_{p}}{2} + \frac{f}{2}C'_{n} + \frac{f^{2}}{2}C'_{n} - \frac{f}{2}C'_{n}\right] + R'_{N}C_{L}$$

(4.16)

$$t_{df} = R_N' \left[ \frac{C_p'}{2} + \frac{f^2}{2} C_n' \right] + R_N' C_L$$

(4.17)

Where,  $C_L$  is the load capacitor,  $R'_N$  is the fall resistance,  $C'_p$  is the PMOS gate capacitance and  $C'_n$  is the NMOS gate capacitance of the inverter in the library.

The first term in equation 4.17 is the intrinsic delay and the second term is the transition delay. From equation 4.17 for a given gate with f inputs the intrinsic delay remains constant, but the transition delay varies linearly with the load capacitance, similarly for a fixed load the transition delay remains constant. The intrinsic delay fits a second order polynomial equation with increasing number of inputs.