# SYSTEM-ON-CHIP DESIGN FOR RELIABILITY

# By

# MINSU CHOI

Bachelor of Science Oklahoma State University Stillwater, Oklahoma 1995

Master of Science Oklahoma State University Stillwater, Oklahoma 1998

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of DOCTOR OF PHILOSOPHY AUGUST 2002

C O P Y R I G H T

Ву

Minsu Choi

August, 2002

# SYSTEM-ON-CHIP DESIGN FOR RELIABILITY

Thesis Approved:

Thesis Advisor

# **ACKNOWLEDGMENTS**

I wish to express my sincere appreciation to my dissertation advisor, Dr. Nohpill Park for his excellent supervision. My appreciation extends to the other dissertation committee members, Dr. K.M. George, Dr. G.E. Hedrick and Dr. J.M. Chung. I would like to give my special thanks to my family as well; my wife, Sujeong; my father, Jinsung; and my mother, Daeja.

# TABLE OF CONTENTS

| 1 | INT                                                   | RODUCTION                                                              | 1  |  |  |

|---|-------------------------------------------------------|------------------------------------------------------------------------|----|--|--|

|   | 1.1                                                   | Reliability of Embedded Cores                                          | 2  |  |  |

|   | 1.2                                                   | Reliability Assurance Techniques for Embedded-core-based SoC           | 3  |  |  |

|   | 1.3                                                   | Reliability-driven Defect and Fault Tolerance in SoC                   | 7  |  |  |

| 2 | EMBEDDED MEMORY CORE ARCHITECTURE FOR ENHANCED MAN-   |                                                                        |    |  |  |

|   | UFA                                                   | CTURING YIELD AND FIELD RELIABILITY                                    | 10 |  |  |

|   | 2.1                                                   | Fault-Tolerant Memory Core Organization for SoC Applications           | 12 |  |  |

|   | 2.2                                                   | Repair Algorithm and Procedure                                         | 14 |  |  |

|   | 2.3                                                   | Fabrication-Time Yield Analysis of the Proposed Fault-Tolerant Mem-    |    |  |  |

|   |                                                       | ory Core                                                               | 17 |  |  |

|   | 2.4                                                   | Field Reliability Assurance of the Proposed Fault-tolerant Memory Core | 22 |  |  |

|   | 2.5                                                   | Quality Assurance of the Proposed Fault-Tolerant Memory Core           | 27 |  |  |

|   | 2.6                                                   | Summary                                                                | 29 |  |  |

| 3 | REDUNDANCY PARTITIONING FOR BALANCED MANUFACTURING    |                                                                        |    |  |  |

|   | YIE                                                   | LD AND FIELD RELIABILITY                                               | 35 |  |  |

|   | 3.1                                                   | Preliminaries                                                          | 36 |  |  |

|   | 3.2                                                   | Single Dimensional Redundancy Case                                     | 37 |  |  |

|   | 3.3                                                   | Two Dimensional Redundancy Case                                        | 40 |  |  |

|   | 3.4                                                   | Parametric Simulations and Results                                     | 44 |  |  |

|   | 3.5                                                   | Discussion                                                             | 47 |  |  |

| 4 | COI                                                   | NNECTIVITY-BASED RECONFIGURABLE SOC REPAIR                             | 57 |  |  |

|   | 4.1                                                   | Review and Preliminaries                                               | 58 |  |  |

|   | 4.2                                                   | Connectivity-based RSoC Repair Process                                 | 63 |  |  |

|   | 4.3                                                   | Connectivity-based RSoC Repair Scheduling                              | 67 |  |  |

|   | 4.4                                                   | Parametric Analysis                                                    | 69 |  |  |

|   | 4.5                                                   | Discussion                                                             | 74 |  |  |

| 5 | HW/SW CO-RELIABILITY IN CONFIGURABLE MULTI-PROCESSOR- |                                                                        |    |  |  |

|   | ME.                                                   | MORY-ON-CHIP                                                           | 80 |  |  |

|   | 5.1                                                   | Review and Preliminaries on Field Reconfigurable Multi-Processor-      |    |  |  |

|   |                                                       | Memory SoCs                                                            | 82 |  |  |

|   | 5.2                                                   | HW/SW Co-reliability Analysis                                          | 87 |  |  |

|   | 5.3                                                   | System Utilization Categories of the Proposed System                   | 90 |  |  |

|   | 5.4                                                   | Parametric Co-Reliability Analysis                                     | 91 |  |  |

|   | 5.5                                                   | Discussion and Conclusions                                             | 92 |  |  |

| 6  | CONCLUSION |  | 96  |

|----|------------|--|-----|

| RE | FERENCES   |  | 100 |

# LIST OF FIGURES

| 2.1  | SoC area share forecast of embedded memory cores from 1999 to 2014       |

|------|--------------------------------------------------------------------------|

|      | by ITRS2000                                                              |

| 2.2  | Architecture of the memory block and segment                             |

| 2.3  | Logical view of the proposed fault-tolerant memory core components 14    |

| 2.4  | Logical flow of the BIST/BISD/BISR procedure                             |

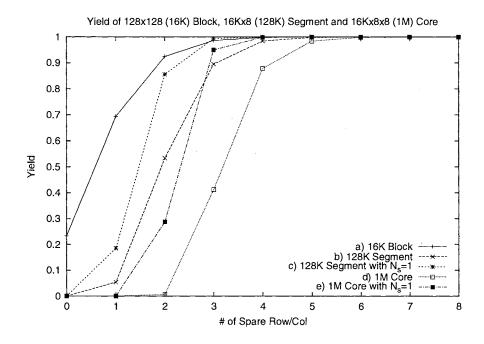

| 2.5  | Yield analysis results of the sample 1Mbit core                          |

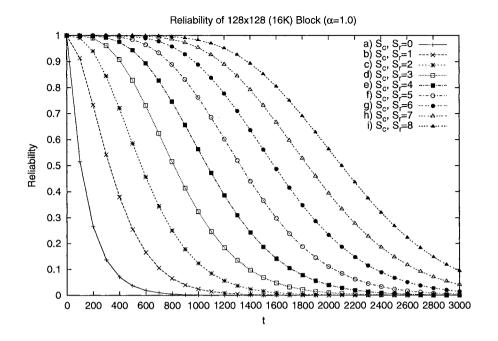

| 2.6  | Reliability analysis results of the sample 16K block                     |

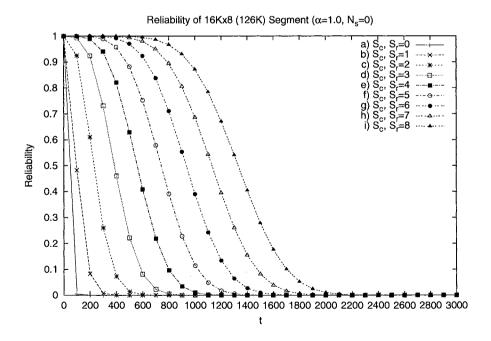

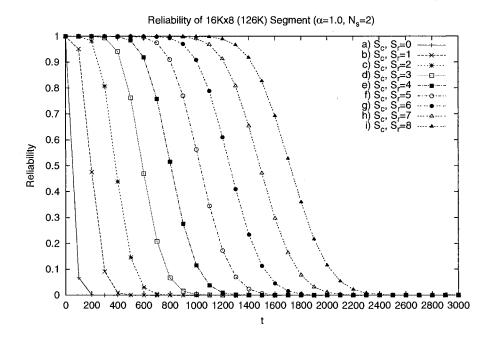

| 2.7  | Reliability analysis results of the sample 16K x 8 (128K) Segment        |

|      | $(N_s=0)$                                                                |

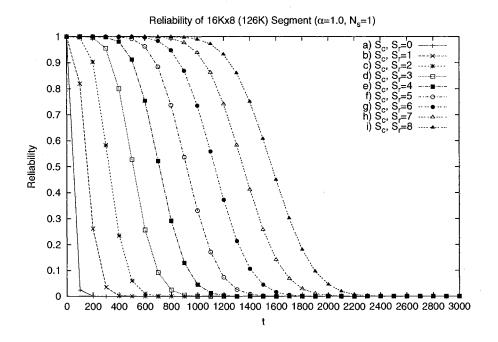

| 2.8  | Reliability analysis results of the sample 16K x 8 (128K) Segment        |

|      | $(N_s=1)$                                                                |

| 2.9  | Reliability analysis results of the sample 16K x 8 (128K) Segment        |

|      | $(N_s=2)$                                                                |

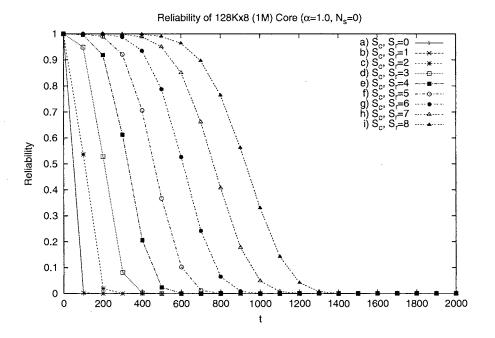

| 2.10 | Analysis results of the sample 16K x 8 x 8 (1M) Core $(N_s = 0)$ 33      |

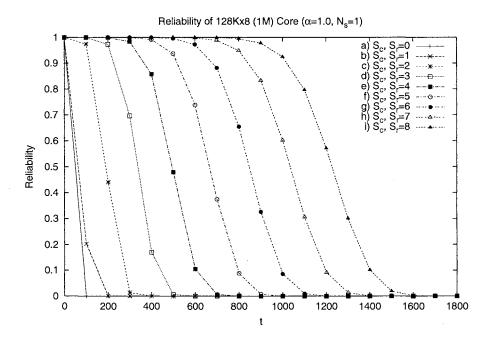

| 2.11 | Analysis results of the sample 16K x 8 x 8 (1M) Core $(N_s = 1)$ 33      |

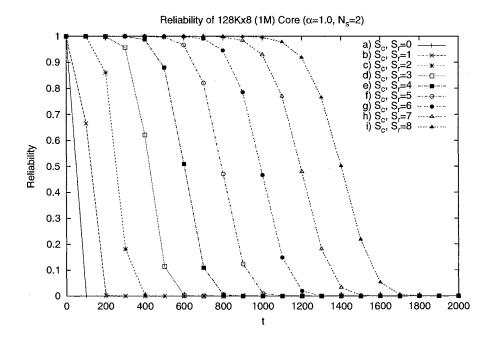

|      | Analysis results of the sample 16K x 8 x 8 (1M) Core $(N_s = 2)$ $3^{4}$ |

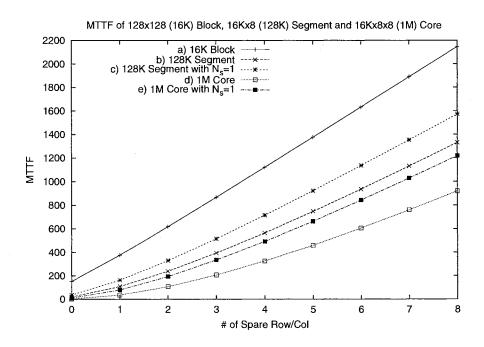

| 2.13 | MTTF analysis results of the sample 1Mbit core                           |

| 3.1  | Example of redundancy partitioning for single dimensional redundancy 40  |

| 3.2  | Example of redundancy partitioning for two dimensional redundancy 43     |

| 3.3  | Symmetric 1D dependability graph                                         |

| 3.4  | Balanced partitioning result [4,4]                                       |

| 3.5  | Reliability-intensive 1D dependability graph                             |

| 3.6  | Balanced partitioning result [3,5]                                       |

| 3.7  | Yield-intensive 1D dependability graph                                   |

| 3.8  | Balanced partitioning result [5,3]                                       |

| 3.9  | An example 1D dependability graph                                        |

| 3.10 | Balanced partitioning result $[6,2]$                                     |

| 3.11 | Symmetric 2D dependability graph                                         |

|      | Balanced partitioning result $\{[4,4],[4,4]\}$                           |

| 3.13 | Reliability-intensive 2D dependability graph                             |

| 3.14 | Balanced partitioning result $\{[3,5],[3,5]\}$                           |

|      | Yield-intensive 2D dependability graph                                   |

|      | Balanced partitioning result $\{[5,3],[5,3]\}$                           |

|      | An example of 2D dependability graph                                     |

| 3.18 | Balanced partitioning result $\{[2,6],[2,6]\}$                           |

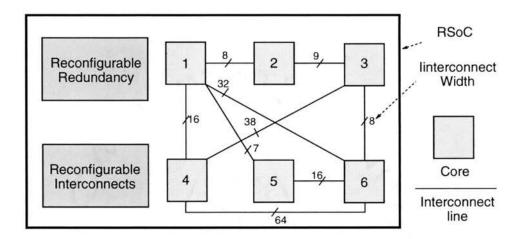

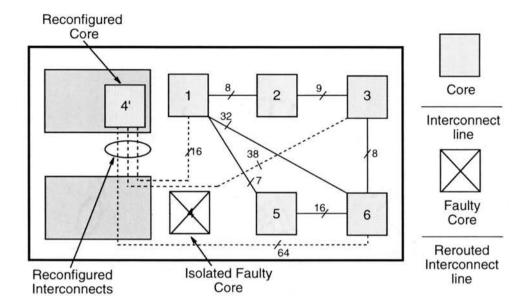

| 4.1  | An example of an RSoC with reconfigurable interconnect network and      |    |

|------|-------------------------------------------------------------------------|----|

|      | redundancy                                                              | 60 |

| 4.2  | An example of a repaired RSoC                                           | 61 |

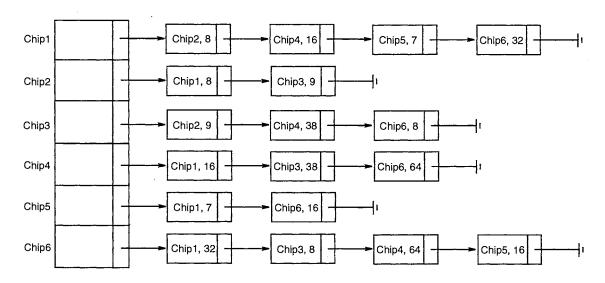

| 4.3  | Adjacency list representation of Figure (4.1)                           | 68 |

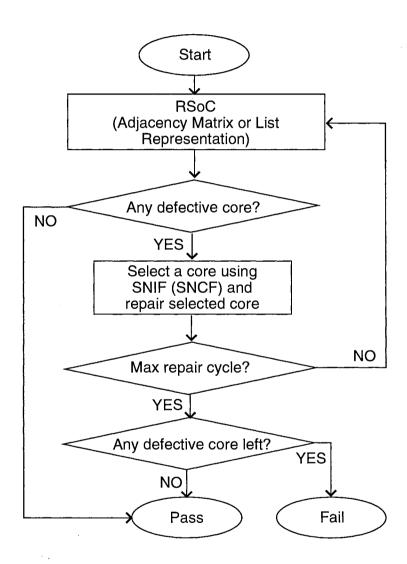

| 4.4  | Flow chart of the SNIF and SNCF                                         | 70 |

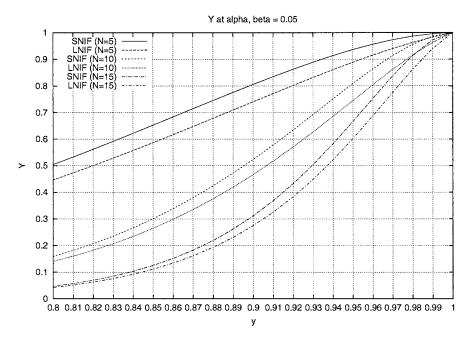

| 4.5  | Yield of SNIF and LNIF at $\alpha, \beta = 0.05$                        | 75 |

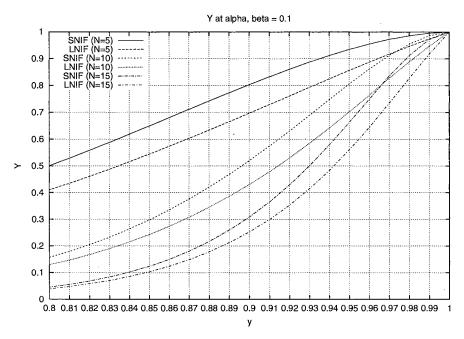

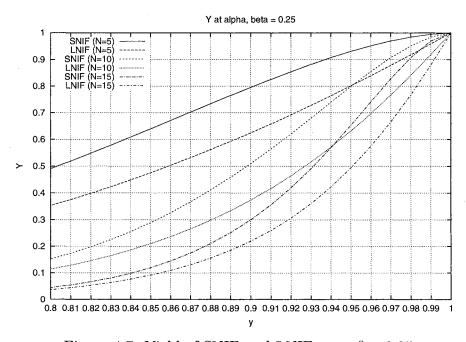

| 4.6  | Yield of SNIF and LNIF at $\alpha, \beta = 0.1 \dots \dots \dots \dots$ | 76 |

| 4.7  | Yield of SNIF and LNIF at $\alpha, \beta = 0.25$                        | 76 |

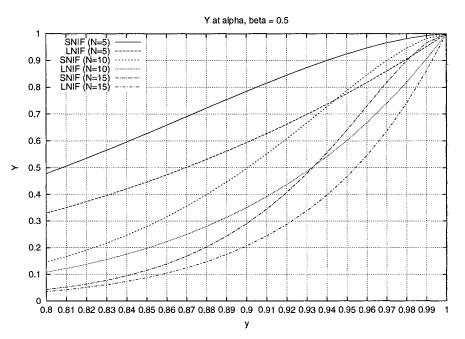

| 4.8  | Yield of SNIF and LNIF at $\alpha, \beta = 0.5 \dots \dots \dots \dots$ | 77 |

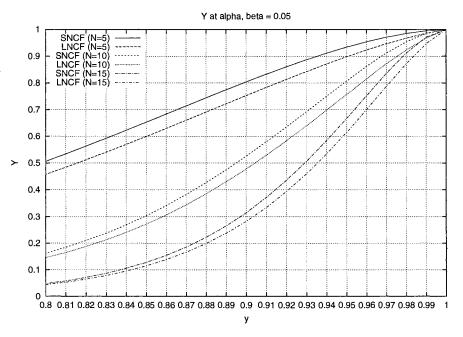

| 4.9  | Yield of SNCF and LNCF at $\alpha, \beta = 0.05$                        | 77 |

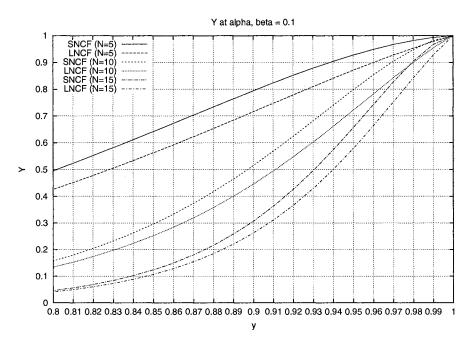

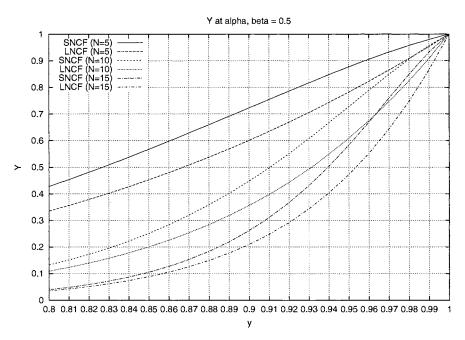

| 4.10 | Yield of SNCF and LNCF at $\alpha, \beta = 0.1 \dots \dots \dots$       | 78 |

| 4.11 | Yield of SNCF and LNCF at $\alpha, \beta = 0.25$                        | 78 |

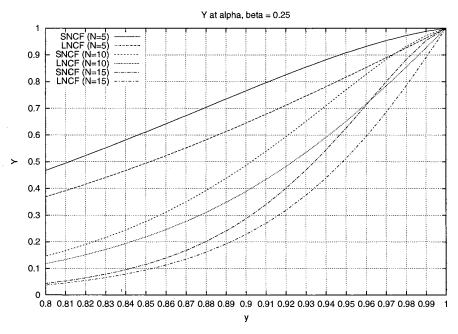

| 4.12 | Yield of SNCF and LNCF at $\alpha, \beta = 0.5$                         | 79 |

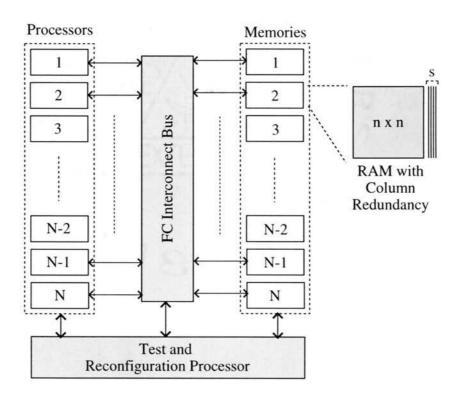

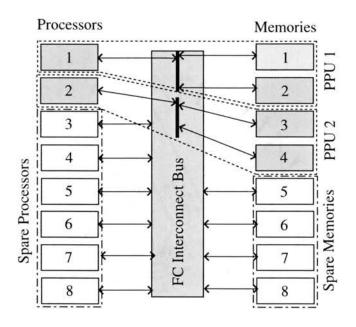

| 5.1  | Investigated Field Reconfigurable Multiprocessor SoC Model              | 84 |

| 5.2  | (1,2,2) System Configuration (2 1-processor 2-memory PPUs)              | 86 |

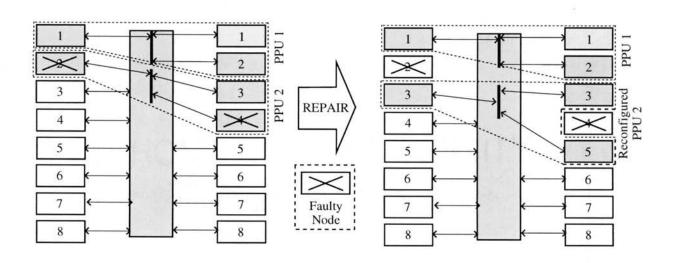

| 5.3  | Repair of faulty processor and memory throughout modular redun-         |    |

|      | dancy reconfiguration                                                   | 86 |

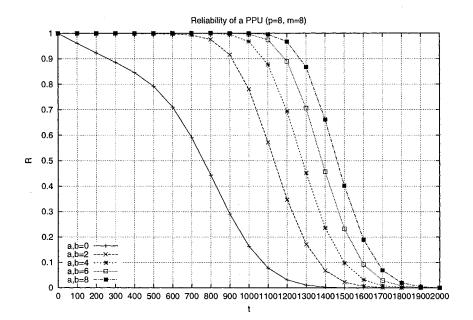

| 5.4  | Reliability comparison of the PPU without modular redundancy and        |    |

|      | PPUs with different numbers of modular redundancy                       | 89 |

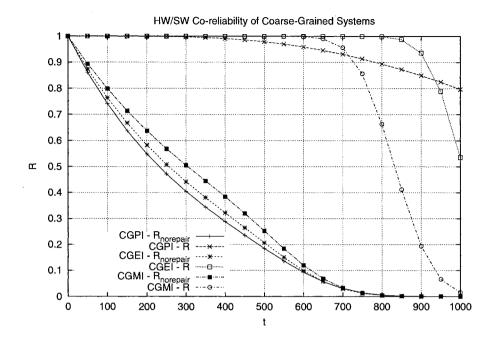

| 5.5  | HW/SW Co-reliability of the Coarse-Grained Systems                      | 94 |

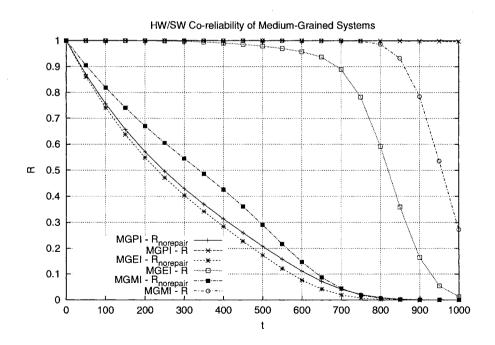

| 5.6  | HW/SW Co-reliability of the Medium-Grained Systems                      | 94 |

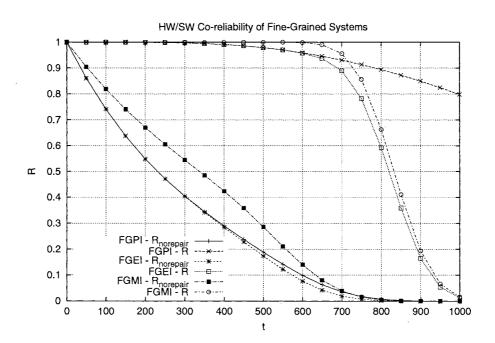

| 5.7  | HW/SW Co-reliability of the Fine-Grained Systems                        | 9. |

# LIST OF TABLES

| 2.1 | Simulation parameters for quality assurance                          | 28 |

|-----|----------------------------------------------------------------------|----|

| 3.1 | Simulation parameters for a one dimensional case                     | 44 |

| 3.2 | Simulation parameters for a two dimensional case                     | 44 |

| 4.1 | Adjacency matrix representation of Figure (4.1)                      | 67 |

| 4.2 | $Y$ and $\overline{Y}$ of the given RSoC without repair              | 71 |

| 4.3 | Performance comparison of the proposed repair strategies at each re- |    |

|     | pair cycle where $\alpha, \beta = 0.05$                              | 72 |

| 4.4 | Performance comparison of the proposed repair strategies at each re- |    |

|     | pair cycle where $\alpha, \beta = 0.5$                               | 72 |

| 4.5 | Repair performance of SNIF for the given parameters                  | 73 |

| 4.6 | Repair performance of SNCF for the given parameters                  | 73 |

| 5.1 | Common simulation parameters                                         | 92 |

| 5.2 | 3-tuple simulation parameters                                        | 93 |

#### CHAPTER 1

#### INTRODUCTION

System-on-Chip (SoC) is one of the most emerging Ultra-Large-Scale-Integration (ULSI) technologies in which numerous pre-designed and verified system components commonly known as *cores* can be seamlessly integrated into a single chip [8, 10, 13, 16, 20, 21, 22, 30, 31]. Since a complex application-specific system can be rapidly designed and fabricated on a single chip by dedicated Computer-Aided-Design (CAD) tools with vendor-supplied core designs, the SoC-based system requires less power, smaller space and shorter time-to-market [2]. Hand-held devices, wire-less communication devices, multimedia devices, PDAs (Personal Data Assistants), computer-controlled vehicles, unmanned autonomous vehicles, MEMS (Micro-Electo-Mechanical Systems) and embedded systems are commonly referred applications for which the SoC is the most suitable technology choice [8].

Two requirements must be realized in order for a SoC to be a viable and practical technology. First, the SoC fabrication line must be capable of mass production at costs that are competitive with alternative methods such as printed circuit boards (PCBs) and multichip modules (MCMs) to mention a few. This implies that the expected yield of SoCs must be high enough to be cost-effective [20]. Second, the cores and supporting circuitry must be capable of performing their intended function throughout their intended useful life [22]. The second requirement is commonly referred to as reliability.

The yield of a SoC is mainly determined by its manufacturing defect density [20]. As the more complicated fabrication technique is applied, the higher defect density

would be induced [28]. For example, memory cells in a DRAM (Dynamic Random Access Memory) core are more likely to experience defects than the other logic gates due to imperfect manufacturing processes and their complex three dimensional cell structure [40, 41, 42, 43, 45]. The reliability of a SoC is a function of time and fault arrival rate. In fact, cores cannot be physically repaired in the field, once they are packaged into a single chip. Therefore, a single unreliable core may devastate the intended functionality of the whole SoC.

As the need for SoC technology increases, high yield and solid reliability are becoming critical requirements for SoCs because insignificant degradation or defect of core components may result in seriously unacceptable low manufacturing yield. Furthermore, field reliability must be also assured because numerous unreplaceable/unrepairable cores are integrated onto a single chip to implement a complex monolithic system. In this context, core-based yield and reliability assurance techniques must be developed to achieve high yield and reliability for SoCs.

# 1.1 Reliability of Embedded Cores

Embedded cores are reusable modules to be embedded on a single chip to build an on-chip system [8, 10, 16, 20, 21, 22, 30, 31]. These cores are provided in the form of rich libraries of pre-designed and pre-verified building blocks. Cores are designed to embed hardware descriptions of today's standard ICs such as digital signal processor (DSP), microprocessor, or DRAM core.

Cores are categorized by *soft* (register-transfer level), *firm* (netlist level), and *hard* (technology-dependent layout) cores [26]. Soft cores are technology-independent for the system designer to be flexible in system-integration, which is best for implementation of functions with frequent customization needs [21]. Hard cores are designed

to be optimized for the given technology constraints such as area and performance, while its weakness mainly stems from the lack of flexibility. Hard cores are usually used for timing and function-critical components of the system such as the CPU or analog elements [30]. Firm cores are designed in an intermediate form of soft and hard cores. Firm cores are appropriate for implementing functions without timing requirements that dictate custom layout, but requiring intellectual property encryption [30]. Each core category provides different advantages and disadvantages due to its unique features, and hence requires different modeling and testing approaches.

A major advantage of the SoC is its customizability and reconfigurability by using its reusable predesigned/preverified and ideally preoptimized core components and interconnects for integration and manufacturing [8]. This yields tremendous cost and performance enhancements. However, integrating and manufacturing a SoC with reusable cores requires new fault-tolerance methodologies because of the unique characteristics created by the SoC with wide variation in reliability requirements for the heterogeneous cores, test structures and defect and fault tolerance [26]. Thus, the quality of each core and interconnect structure of a SoC must be assured and configured properly to achieve the desired higher manufacturing yield and field reliability.

#### 1.2 Reliability Assurance Techniques for Embedded-core-based SoC

SoCs using deep-sub-micron technology such as 100-nm technology, gigahertz clock frequency, and less than 1-V power supply by year 2003 to 2006 will cause serious on-chip noise due to increased cross-coupling of capacitances, inductances, and electromagnetic fields between bus interconnects [26]. New fault models, testing/diagnosis methods, and reliability assurance techniques should be developed for the realization of reliable SoCs [1, 16, 20, 26, 28].

Testing strategies and methodologies for embedded-core-based SoCs have been investigated in [26] in which the criticality of manufacturing test and design debugging in the embedded-core-based SoC has been addressed. In [5], a system tool was introduced to explore and compare different embedded-systems architectures. Another fast and low-cost testing technique for core-based system-chips was also proposed in [22].

In traditional PCB or MCM-based systems, component providers are responsible for chip design, manufacturing and testing, whereas system integrators are responsible for board-level design, integration and testing under the assumption of fault-free components. Thus, only the interconnects between components are to be tested [11].

Core testing is a joint responsibility of the core provider whereas the system integrator in embedded-core-based systems [10, 15, 16, 22, 26]. The core provider basically only transfers the description of a module and the system integrator manufactures a target system by testing the cores provided by the core providers and integrating them together through laying out and testing interconnects between the cores [8, 11, 10, 15, 16, 22, 26].

In core-level testing, a core is often dealt with as a black box to the system integrator if the core is hard or encrypted as an intellectual-property. The core provider can deliver to the system integrator the core test which generally consists of the design-for-test structures, built-in or out, and the corresponding test patterns [10, 12, 15, 16, 22, 26]. In [12], for example, an instruction-level design-for-test methodology for testing processor and IP cores in a SoC was proposed and validated. However, the core provider has little or no prior information about the manufacturing environment and the requirements of the target system, such as test methods, fault models, fault-coverage and quality levels, because different system integration and

manufacturing processes have different requirements due to different defect densities and distributions [1, 7, 20, 26, 28].

The accessibility of the component terminals (i.e., the primary inputs and outputs of chips and cores) of an embedded-core-based SoC is different from traditional systems [5, 51, 16, 19]. With PCB-based systems, the chips are tested as stand-alone units, and during tests, they can be accessed through direct physical access to chip pins. In contrast, cores are often deeply embedded in a SoC, so direct physical access is not available [5, 51, 16, 19, 26]. The chip design must then provide an electronic test access infrastructure from the chip pins to the terminals of the embedded core [14, 19, 26]. Infrastructure for testing the hardware in between the cores and isolating a core from its surroundings should also be provided [19, 26].

A system-level test is an integration and coordination of on-chip test and diagnosis capabilities, which is far more complex than the traditional PCB-based assembly test. It consists of individual tests for cores, tests for user-defined logics, and tests for interconnect logics and wires [1]. The SoC's composite test requires adequate test scheduling to coordinate several chip-level requirements, such as test time, power dissipation and area overhead. It is also necessary to run intra-core and inter-core tests in a certain order to avoid affecting the initialization and final content of individual cores [16]. In [7], delay fault testing using symbolic path modeling was proposed to test interconnection delay faults in SoCs. Deep submicron chip testing issues should be also taken into account to meet sufficient defect/fault coverage requirements, overall test cost and time-to-market [28].

Even though preverified cores are integrated, validating and debugging the functionality and timing of the SoC could be another challenge due to unique features such as the heterogeneous structure of the SoC; the need for software and hardware co-simulation; the design for integrated functionality; timing validation and debugging; and the accessibility problems of deeply embedded cores [5, 51, 16, 19, 26]. High-level prototype-level validation is usually co-simulated with silicon-level validation that requires at-speed validation [26]. In [11], for example, high-level crosstalk defect simulation techniques were proposed for SoC interconnects. Unfortunately, current high-level validation techniques cannot catch up with the silicon-level validation speed of a SoC yet, which gives a new challenge for achieving an accurate validation of the quality of SoCs [26].

On-chip testing circuitry takes a much larger area than the main circuitry resulting in reduced manufacturing yield and increased cost and low area utilization. Also, test circuitry for each core often exhibits an irregular structure making it difficult to generate core-specific deterministic test patterns on-chip at acceptable area costs even though it provides better accuracy and defect coverage. In practice, not all test patterns can be generated on-chip in a cost-effective manner [6, 7, 8, 12, 51, 15, 26]. In the meantime, it is becoming increasingly more difficult for off-chip ATE (automated test equipment) to keep up with today's high-speed, high-density, and mixed technology SoCs to sufficiently test their quality-related defects [6, 51, 19]. Hence, a combined ATE and BIST (built-in-self-test) approach is recommended to provide a capability for testing all different types of defects and faults and to meet the above-mentioned cost and quality-effectiveness [1, 6, 14, 16, 19, 26, 28, 29].

Embedded cores in a SoC cannot be replaced once they are fabricated even though the reliability of the end-product SoC is mainly determined by the reliabilities of the cores. Thus, repair of the SoC for more graceful reliability degradation usually requires advanced fault-tolerance techniques such as the Built-In-Self-Test, Diagnosis and Repair (BIST/BISD/BISR) [35, 36, 37]. Self-testability has been commonly

exploited for the systems with limited ATE testability [6, 14, 15, 29, 37] because a SoC has severe limitations on ATE accessibility. Test results gathered by either ATE or BIST or both then need to be diagnosed to suggest the most reliability enhancing repair configuration. External diagnosis softwares are usually employed to analyze different possible repair options. Once a SoC is packaged, self-diagnosability is desirable to provide field diagnosis of the BIST data. Finally, redundancy is to be switched in and configured as instructed by the diagnosis softwares or BISD to repair the SoC. Redundancy configuration has been done by external equipment such as a laser fuse blower, while self-repairability is also needed to enhance the reliability of the packaged SoC in field.

The self-testability/diagnosability/repairability is not free from penalty such as redundancy and test/diagnosis/repair circuitry overhead since it consumes valuable chip space, thereby increases manufacturing cost significantly [6, 7, 8, 12, 51, 15, 26]. Thus, minimization of the overhead due to the self-repairability as well as optimized utilization of the redundancy, while achieving maximum reliability, is desirable to maintain the cost-effectiveness of the SoC technology.

#### 1.3 Reliability-driven Defect and Fault Tolerance in SoC

A SoC can be modeled as a system which consists of a number of different cores and fully customized interconnect structures. As the more complex design is implemented in a SoC, its reliability assurance becomes a more critical issue since cost-effectiveness of the design and implementation is mainly affected by the reliability of embedded cores and interconnect structures [11, 20, 26]. The lifetime of a SoC can be categorized into three stages with respect to its reliability: design stage, fabrication stage and field stage. In the design stage, parametric reliability estimations are usually done, and

core-level or chip-level defect and fault tolerance techniques are introduced on the fly. In the fabrication stage, ATE performs a wafer probe to cope with the manufacturing defects on the SoC, and embedded redundancy, if any, can be utilized to repair the defects due to imperfect manufacturing. Thus, the yield (i.e., the reliability of a SoC at the fabrication stage) can be modeled by testability and repairability. In the field stage, BIST/BISD/BISR are exploited to further enhance the reliability of the SoC.

The main objectives of this work is to propose reliability assurance and reliability-driven defect and fault tolerance in SoC system, thereby realizing more dependable and cost-effective mass production of SoCs. The following specific problems will be addressed and resolved in this work.

- Reliability Assurance Techniques: Core-based assurance techniques are to be proposed to model and evaluate the reliability.

- Reliability-Driven Defect & Fault Tolerance: Defect and fault-tolerance techniques are to be developed driven by the proposed modeling and evaluation techniques.

- Redundancy Architecture and Reconfiguration Algorithms: Ad-hoc design of core-specific redundancy architectures and their reconfiguration algorithms are to be proposed.

- Reliability Enhancement Strategies in Configurable SoC: Reliability improving configuration strategies in configurable SoCs are to be investigated.

- Connectivity-Based Repair Scheduling Algorithms of reconfigurable SoCs: Repair algorithms selecting more reliable repair schedules are to be proposed for reconfigurable SoCs.

• HW/SW Co-Reliability in SoC: Reliability characteristics of hardware configuration, affected by application design software, are to be investigated.

The organization of the dissertation is as follows. In Chapter 2, a reliable embedded memory core and its yield and reliability assurance techniques are proposed. Hierarchical redundancy, ATE-based fabrication-time repairability and BIST/BISD/BISR-based field repairability are employed to achieve acceptable manufacturing yield and field reliability. Then in Chapter 3, a novel optimal redundancy partitioning technique will be proposed as well. In the following Chapter 4, connectivity-based reconfiguration algorithms for SoCs are proposed and validated by the reliability assurance techniques. It proposes how proper repair scheduling can guarantee the optimal reliability of a SoC. Then, HW/SW Co-reliability assurance and balancing techniques are proposed in Chapter 5. Reliability issues associated with the hardware configurations set up by the dynamic software demands are investigated. Finally, the conclusion is presented in the last chapter.

### CHAPTER 2

# EMBEDDED MEMORY CORE ARCHITECTURE FOR ENHANCED MANUFACTURING YIELD AND FIELD RELIABILITY

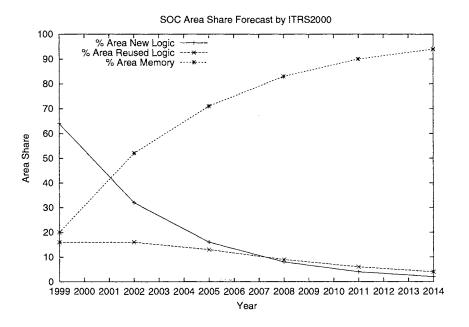

Among the cores for SoC integration, one of the most vulnerable cores is the embedded memory core since memory cells are commonly considered as most prone to defects and faults [35, 36, 37, 39, 41, 42, 43, 45]. As the SoC fabrication process goes toward the era of deep-sub-micron technology such as  $0.13\mu m$ , the need for high yield and ultra reliable embedded memory cores has become more urgent than ever before. According to the Semiconductor Industry Association and ITRS (International Technology Roadmap for Semiconductor) 2000, embedded memory will continue to dominate SoC content in the next several years, approaching 94% of the die area by 2014 as shown in Figure (2.1) [38]. The issues surrounding high-density multi-megabit memory dependability (i.e., the probability to be manufactured as good AND not failing during the time interval [0,t]) must be resolved in order to facilitate this trend and to produce a cost effective SoC product.

Traditionally, reconfiguration (repair) of memory arrays using spare memory lines is the most common technique for yield enhancement of memories with faults [35, 36, 37, 39, 41, 42, 43, 45]. In [37], a simple built-in-self-analysis-repair scheme for embedded DRAM was proposed and a row-column self-repair scheme for embedded SRAM for Alpha 21264 was shown in [39]. A shared built-in self-repair analysis scheme for multiple embedded memory cores in the SoC is proposed in [35] to realize minimum area penalty independent of the number of embedded memory cores. Software-based self-testing methodology for processor cores was reported in [15]. Virtual-socket archi-

Figure 2.1: SoC area share forecast of embedded memory cores from 1999 to 2014 by ITRS2000

tecture for embedded DRAM cores was proposed in [17] in which embedded DRAM cores with different sizes can be seamlessly integrated into a SoC by utilizing the core wrapper called virtual socket. Application specific synthesis of SoCs with flexible memory size was proposed in [27]. A programmable BIST core for embedded DRAM was introduced in [29]. [32] also reported a design methodology for embedded DRAM in multimedia SoCs. Error-correcting-code (ECC) has been also used to develop more reliable memory devices in terms of data integrity and dependability [43, 44]. Especially a synergistic fault-tolerance of the combination of ECC and row/column redundancy was discovered in [43]. An on-chip march pattern generator for testing embedded memory cores was proposed in [6] as well. However, a comprehensive research work on fault-tolerant embedded memory core organization and its quality assurance has not been reported yet.

The main motivation of this chapter is to propose a high yield, ultra reliable

embedded memory core organization for SoC applications which is capable of both factory and field repair to enhance its factory yield and field reliability at the same time, by establishing a series of accurate quality assurance techniques for the proposed memory core architecture.

The organization of this chapter is as follows: In the following section (Section 2.1), a fault-tolerant memory core organization which is capable of both factory and field repair will be proposed. Then, in section 2.2, the detailed factory and field repair procedure will be shown. Yield and reliability assurance techniques for the proposed embedded memory core will be proposed in chapters 2.3 and 2.4, respectively. Parametric simulations and results will be shown in section 2.5. Finally, discussion and conclusions will be given in Section 2.6.

## 2.1 Fault-Tolerant Memory Core Organization for SoC Applications

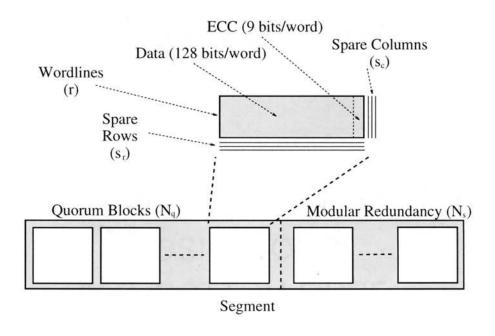

Figure 2.2: Architecture of the memory block and segment

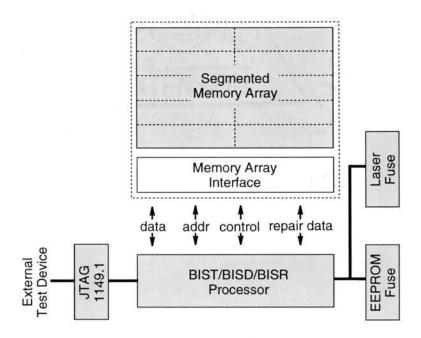

The atomic unit of the proposed memory core architecture is referred to as block. To enhance not only data integrity but also manufacturing yield and field reliability, both the double-error-detection, single-error-correction (DED-SEC) error-correctingcode (ECC) and the spare row/column redundancy are built into each block of the memory. 128 bit data word with 9 bit ECC has been chosen while the other configuration of ECC is technically feasible as well. Numerous error correcting codes were categorized in [44]. Each memory block has r ECC words,  $S_c$  spare columns, and  $S_r$ spare rows for the sake of fault-and-defect-tolerance of the core as shown in Figure (2.2). Almost every numerical parameter of the proposed memory core is left as a variable to facilitate the maximum flexibility in the resultant core, thereby allowing cost-effective and target-specific memory core design optimization. The next unit of the proposed memory core organization is the segment. Segment consists of  $N_q$  quorum ECC memory blocks with row/column redundancy. The SoC designer can assign  $N_s$  spare memory blocks to overcome costly block-wise failures. Figure (2.2) shows an illustration of a segment with  $N_q$  quorum memory blocks with  $N_s$  spare memory blocks. This kind of modular redundancy technique will enhance core dependability significantly. The detailed reconfiguration algorithm and repair procedure for the proposed memory core will be covered in the next section. The next memory unit is the segmented memory array which consists of  $N_{seg}$  segments. Therefore, the total size of the memory core is  $128 \times r \times N_q \times N_{seg}$  bits. The proposed memory core consists of the following components as shown in Figure (2.3).

- BIST/BISD/BISR Processor: This system component governs self-test, self-diagnosis, and self-repair procedures.

- Laser Fuse: A set of laser reconfigurable fuses to permanently program the given redundancy resources.

- EEPROM Fuse: A programmable, non-volatile memory to store additional reconfiguration signature generated by the BIST/BISD/BISR processor in field.

- IEEE JTAG (Joint Test Action Group) 1149.1: External boundary scan test equipment interface.

- Memory Array Interface: This component connects the segmented memory array and the BIST/BISD/BISR Processor together. Data, address, control and repair data flow via this component.

Figure 2.3: Logical view of the proposed fault-tolerant memory core components

### 2.2 Repair Algorithm and Procedure

Memory reconfiguration by using row/column redundancy is one of the well-known NP-complete problems in VLSI (Very Large Scale Integration) design [41, 42, 44, 45].

Thus, numerous approximation algorithms guaranteeing near-optimal solutions have been introduced with a quite unrealistic assumption, i.e., high faulty cell probability, while world-class semiconductor manufacturers produce quality memories which contain usually one or less faulty cell per million cells [43]. Also, most of the memory reconfiguration algorithms are not suitable to be embedded in the SoC in reality due to their high computational complexity. Thus, a very simple yet effective hierarchical repair algorithm is used for the proposed embedded memory core, while various reconfiguration algorithms can be applied as well. Quality assurance techniques for the proposed embedded memory core will be realized based on the following requirements:

- 1. ECC: single-error-correction and double-error-detection (SEC-DED) error correcting code covers one-bit permanent or transient faults and detects 2-bit permanent or transient faults.

- 2. Row Redundancy: If more than 2 failing bits in a row or the support circuitry of the row are diagnosed as faulty, a row spare replaces the faulty memory row.

- 3. Column Redundancy: Likewise, if more than 2 failing bits in a column or the support circuit of the column are diagnosed as faulty, a column spare replaces the faulty memory column.

- 4. Block-wise Modular Redundancy: Within a segment, a failing block also can be repaired by a spare block. This kind of repair method is commonly referred to as modular redundancy technique.

The proposed fault-tolerant memory core provides not only factory repairability but also field self-test and repair capabilities. The first repair process takes place during the wafer probe in the factory. The repair signature created by the proposed memory core is sent to an external test equipment via the IEEE JTAG 1149.1, which

is a common connectivity interface between the external tester and the embedded BIST/BISD/BISR processor [19, 35, 37, 39]. Then, conventional laser repair equipment blows the fuse box with the required reconfiguration information. Afterwards, the core contains the permanent memory repair signature unique to this particular SoC. The fabrication-time repair also has the advantage of performing test and repair at the wafer level. The wafer is subject to a variety of stringent conditions during testing which helps insure high memory and SoC dependability (i.e., extended voltage, temperature and frequency conditions).

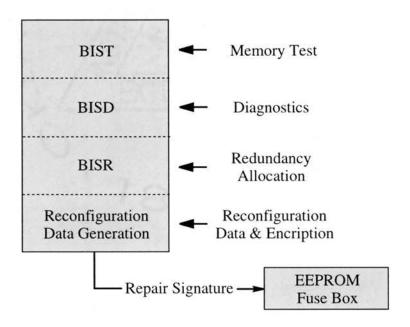

Figure 2.4: Logical flow of the BIST/BISD/BISR procedure

The field repair operation tests and repairs memory instances each time the end product starts up or is reset. Logical view of the field repair procedure is given in Figure (2.4). The BIST/BISD/BISR Processor initiates and operates the test program, determines defective memory locations (if any), allocates redundancy resources, and produces a new repair signature that resides in the EEPROM fuse on the memory

core (similar to the EEPROM-controlled redundancy allocation technique proposed in [36]). This non-volatile repair signature is applied to the redundancy control logic and remains there until a new repair signature is overwritten. As a result, it is possible to design an SoC that incorporates the proposed memory core with both fabrication-time and field repair in which the fabrication-time repair process repairs manufacturing defects, and the field repair operation covers any subsequent problems that may materialize over the life of the end SoC product.

- 2.3 Fabrication-Time Yield Analysis of the Proposed Fault-Tolerant Memory Core

The following parameters are used for the analysis:

- $\bullet$  d: Number of data bits per ECC word.

- c: Number of code bits per ECC word.

- $n_c$ : Number of columns per block without spare columns.  $(n_c = d + c)$

- $n_r$ : Number of rows per block without spare rows.

- $s_r$   $(s_c)$ : Number of spare rows (columns) per block.

- ullet  $N_q$ : Number of quorum blocks per segment.

- $N_s$ : Number of modular spare blocks per segment.

- ullet  $N_{seg}$ : Number of segments per memory system.

- $\lambda_m$ : Expected number of manufacturing failures per memory cell.

The following assumptions are also made to analyze the manufacturing yield of the proposed fault-tolerant memory core:

- A failing bit in a word is supposed to be corrected by Single-Error-Correction & Double-Error-Detection (SEC-DED) Error-Correcting-Code (ECC).

- Multiple faults in a word can be repaired by row redundancy.

- Multiple faults in a column can be repaired by column redundancy.

- Block-wise failure can be repaired by the block modular redundancy.

The yield of a single cell can be written as

$$Y_{cell} = e^{-\lambda_m} \tag{2.1}$$

where  $\lambda_m$  is the expected number of faults per memory cell due to imperfect fabrication. The probability of not having a failing cell in an  $n_c$  bit error-correcting-code word is then given by  $(Y_{cell})^{n_c}$  and the probability of having one of the  $n_c$  bits failing can be represented by  $n_c \cdot (Y_{cell})^{(n_c-1)} \cdot (1-Y_{cell})$ . Therefore, the yield of each word without ECC is

$$Y_{word} = (Y_{cell})^{n_c}$$

if ECC is not used. (2.2)

Since each ECC word can tolerate one failing bit, the yield of each word enhanced by ECC is given by

$$Y_{word} = (Y_{cell})^{n_c} + n_c \cdot (Y_{cell})^{(n_c-1)} \cdot (1 - Y_{cell})$$

if ECC is used. (2.3)

There are  $n_r$  words in each block of the proposed memory core. If we start with a fault-free block, the chances that the first failing cell will not occur coincident with another failing cell are absolute certainty. The probability for the second faulty cell not to occur in the same word as the first faulty cell is  $(n_r - 1)/r$ . For the third one,

the probability is  $(n_r - 2)/n_r$ , etc,. Thus, for the N single-cell faults in a block the probability of non-alignment can be written as [43]

$$P(no\ alignment|N) = \prod_{i=1}^{N} \frac{(n_r+1)-i}{n_r}$$

(2.4)

which can be rewritten in the form

$$P(no \ alignment|N) = \frac{n_r!}{n_r^N(n_r - N)!}$$

(2.5)

For example, as shown in [43], the calculations made with either one of the formulas given above show that with 100 randomly failing cells in a 16Mbit memory chip, there is a better than 97% chance that two such failing cells will not occur in the same error-correcting-code word of 137 (i.e, 128 data bits + 9 ECC bits) bits. Thus, the yield associated with all these defects would be more than 97%. Nevertheless, when there are 1,000 randomly failing cells on the memory, the probability for non-alignment of cells in any error-correcting-code word is less than 2%. This represents a 2% yield for such faults.

The ECC circuitry covers single-bit faults perfectly. However, its limitation mainly occurs when multi-bit faults hit on a single word. In addition, some of these faults affect the chip support circuitry, and the rows and columns. Because of this, the proposed fault-tolerant memory core also has redundant rows and columns to replace the defective ones entirely.

The probability of having two or more single-cell failures in a word is given by

$$P_{mfw} = \sum_{i=2}^{n_c} \binom{n_c}{i} (Y_{cell})^{(n_c - i)} \cdot (1 - Y_{cell})^i$$

(2.6)

where the subscript mfw is used to indicate that this probability is associated with the event of multiple faults in a word. This equation can be further simplified by Equation (2.3) and the binomial theorem as

$$P_{mfw} = 1 - Y_{word} \tag{2.7}$$

if ECC is used to cover one faulty cell in a word. Then, the probability of finding from one to  $s_r$  words with multiple faults can be written as

$$P_{s_r} = \sum_{j=1}^{s_r} \binom{n_r}{j} (P_{mfw})^j \cdot (1 - P_{mfw})^{(n_r - j)}$$

(2.8)

where the subscript  $s_r$  is used to indicate that these are the probabilities for the words that need to be replaced, if there are redundant rows available. The probability to fix those words with multiple faulty bits solely depends on the availability of fault-free spare rows. So, the probability of having j or more fault-free spare rows is given by

$$P_{s_r \ge j} = \sum_{k=j}^{s_r} {s_r \choose k} (Y_{word})^k \cdot (1 - Y_{word})^{(s_r - k)}$$

(2.9)

where the subscript  $s_r \geq j$  is self explanatory.

The probability of replacing the words with multiple faulty cells in a block is obtained by combining Equation (2.8) and (2.9) as follows

$$Y_{s_r} = \sum_{j=1}^{s_r} \sum_{k=j}^{s_r} \binom{n_r}{j} \binom{s_r}{k} (P_{mfw})^j \cdot (1 - P_{mfw})^{(n_r - j)} \cdot (Y_{word})^k \cdot (1 - Y_{word})^{(s_r - k)}$$

(2.10)

where  $Y_{s_r}$  is used to indicate that it is the yield of repaired block by spare rows. Taking the faults corrected with the SEC ECC circuitry into account, the yield of a block is improved from  $(Y_{word})^{n_r}$  to

$$Y_{block:s_r} = (Y_{word})^{n_r} + Y_{s_r} (2.11)$$

The yield of a block can be further enhanced with the spare columns. It is assumed that the spare columns are used to repair the block which cannot be repaired by the SEC ECC and spare rows. Using Equation (2.11), the probability of having a faulty column can be written as

$$P_{fc} = 1 - \log_{n_c} Y_{block} \tag{2.12}$$

Following the same manner which has been used to evaluate the effect of the spare rows, with  $s_c$  redundant columns given in a block, the probability of finding from one to  $s_c$  faulty columns in a block is given by

$$P_{s_c} = \sum_{j=1}^{s_c} \binom{n_c}{j} (P_{fc})^j \cdot (1 - P_{fc})^{(n_c - j)}$$

(2.13)

The subscript  $s_c$  is also used to indicate that these are the probabilities for the columns that need to be replaced, if there are redundant columns available. Then, the probability of having j or more fault-free spare columns can be also given by

$$P_{s_c \ge j} = \sum_{k=j}^{s_c} {s_c \choose k} (Y_{cell})^{(n_r \times k)} \cdot (1 - (Y_{cell})^{n_r})^{(s_r - k)}$$

(2.14)

Then, the probability of replacing the faulty columns in a block can be obtained by combining Equation (2.13) and (2.14) as follows

$$Y_{s_c} = \sum_{j=1}^{s_c} \sum_{k=j}^{s_c} \binom{n_c}{j} \binom{s_c}{k} (P_{fc})^j \cdot (1 - P_{fc})^{(n_c - j)} \cdot (Y_{cell})^{(n_r \times k)} \cdot (1 - (Y_{cell})^{n_r})^{(s_r - k)}$$

(2.15)

where  $Y_{s_c}$  is used to indicate that it is the yield of repaired block by spare columns. Taking the faults corrected with the SEC ECC circuitry and spare rows into account, the yield of a block is improved from  $(Y_{word})^{n_r}$  to

$$Y_{block} = Y_{block:s_r} + Y_{s_c} \tag{2.16}$$

Each segment of the proposed fault-tolerant embedded memory core consists of  $N_q + N_s$  blocks, where  $N_q$  is the number of quorum blocks that must be operational to guarantee the functionality of the segment and  $N_s$  is the number of spare blocks. By exploitation of this  $N_q$ -out-of- $(N_q + N_s)$  modular redundancy technique, the yield of each segment can be enhanced from  $(Y_{block})^{N_q}$  to

$$Y_{seg} = \sum_{i=0}^{N_s} {N_q + N_s \choose i} (Y_{block})^{N_q + N_s - i} \cdot (1 - Y_{block})^i$$

(2.17)

Finally, the overall yield of the proposed fault-tolerant memory system can be expressed as

$$Y = (Y_{seg})^{N_{seg}} (2.18)$$

## 2.4 Field Reliability Assurance of the Proposed Fault-tolerant Memory Core

As described in Section 2.2, the proposed fault-tolerant memory core is able to perform Built-In-Self-Test (BIST), Built-In-Self-Diagnosis (BISD), and Built-in-Self-Repair (BISR) in the field. These special capabilities of the proposed memory core archi-

tecture further enhance its reliability during field operation. Thus, rapid reliability degradation of the host SoC product can be prevented. In this section, reliability assurance of the proposed memory core architecture will be presented based on the following assumptions:

- As the yield of the laser-repaired core at the factory wafer probe stage has been analyzed based on the expected number of failures due to manufacturing defects, the failure arrival rate per unit time will be used to estimate the reliability of the proposed fault-tolerant memory core used in the SoC in the field. To differentiate the expected number of failures due to the manufacturing defects and the failure arrival rate per unit time during field operation,  $\lambda_m$  and  $\lambda_f$  are used in this chapter, respectively.

- Embedded BIST/BISD/BISR processor tests, analyzes and repairs the faulty memory core in the field when it is reset or restarted. For simplicity, the reset/restart event is assumed to occur once in every unit interval time (i.e.,  $\Delta t$ ).

The following parameters in addition to the ones introduced in Section 2.3 are used for the reliability assurance analysis of the proposed fault-tolerant memory core:

- $\bullet$  t: time.

- $\Delta t$ : Unit time interval (e.g., day, week or month, etc).

- $\lambda_f$ : Field failure arrival rate of memory cell per unit time interval.

- R(t): Reliability of the core at time t.

- D(t): Overall dependability of the core at time t (i.e., the probability to be manufactured as good AND not failing during the time interval  $[t_0, t]$ ).

The reliability of a system is a function of time which is defined by the conditional probability that the system performs correctly throughout the interval of time  $[t_0, t]$ , given that the system was performing flawlessly at the initial time  $t_0$  [40]. If we assume that the failure arrival rate of the system has a constant value of  $\lambda$ , the reliability of the system can be expressed as follows

$$R(t) = e^{-\lambda t} \tag{2.19}$$

The exponential relationship between the reliability and time is known as the exponential failure law which states that for a constant failure arrival rate function, the reliability varies exponentially as a function of time. The exponential failure law is quite valuable to analyze electronic components and is a very well-known and widely-used relationship between the reliability and time.

Since the yield can be viewed as the reliability of the system at the initial time  $t_0$ , the formulas for the yield assurance given in the previous section can be extended to derive the reliability formulas with some appropriate modifications in this section. At the initial time  $t_0$ , the probability that a single cell is fault-free is  $Y_{cell} = e^{-\lambda_m}$ . Therefore, the reliability of a single cell (i.e., the conditional probability that a single cell is fault-free from  $t_0$  to t) can be written as

$$R_{cell}(t) = Y_{cell} \cdot e^{-\lambda_f t} \tag{2.20}$$

where  $Y_{cell}$  is the yield of a single cell and  $\lambda_f$  is the failure arrival rate of a single memory cell in the field.

Since the BIST/BISD/BIST shares the same redundancy structure and repair mechanism with the fabrication-time repair, the yield assurance formulas proposed in the previous section can be used if  $R_{cell}(t)$  replaces  $Y_{cell}$ . Thus, the field reliability

13

assurance formulas will be listed without detailed explanations.

$$R_{word}(t) = R_{cell}(t)^{n_c}$$

if ECC is not used. (2.21)

$$R_{word}(t) = R_{cell}(t)^{n_c} + 137 R_{cell}(t)^{(n_c-1)} (1 - R_{cell}(t))$$

if ECC is used. (2.22)

$$P_{mfw}(t) = \sum_{i=2}^{n_c} \binom{n_c}{i} (R_{cell}(t))^{(n_c - i)} \cdot (1 - R_{cell}(t))^i$$

(2.23)

$$P_{mfw}(t) = 1 - R_{word}(t) (2.24)$$

$$P_{s_r}(t) = \sum_{j=1}^{s_r} \binom{n_r}{j} (P_{mfw}(t))^j \cdot (1 - P_{mfw}(t))^{(n_r - j)}$$

(2.25)

$$P_{s_r \ge j}(t) = \sum_{k=j}^{s_r} {s_r \choose k} (R_{word}(t))^k \cdot (1 - R_{word}(t))^{(s_r - k)}$$

(2.26)

$$R_{s_r}(t) = \sum_{j=1}^{s_r} \sum_{k=j}^{s_r} \binom{n_r}{j} \binom{s_r}{k} (P_{mfw}(t))^j \cdot (1 - P_{mfw}(t))^{(n_r - j)} \cdot (R_{word}(t))^k \cdot (1 - R_{word}(t))^{(s_r - k)}$$

(2.27)

$$R_{block:s_r}(t) = R_{word}(t)^{n_r} + R_{s_r}(t)$$

(2.28)

$$P_{fc}(t) = 1 - \frac{\log(R_{block}(t))}{\log(n_c)} \tag{2.29}$$

$$P_{s_c}(t) = \sum_{j=1}^{s_c} \binom{n_c}{j} (P_{fc}(t))^j \cdot (1 - P_{fc}(t))^{(n_c - j)}$$

(2.30)

$$P_{s_c \ge j}(t) = \sum_{k=j}^{s_c} {s_c \choose k} (R_{cell}(t))^{(n_r \times k)} \cdot (1 - (R_{cell}(t))^{n_r})^{(s_r - k)}$$

(2.31)

$$R_{s_c}(t) = \sum_{j=1}^{s_c} \sum_{k=j}^{s_c} \binom{n_c}{j} \binom{s_c}{k} (P_{fc}(t))^j \cdot (1 - P_{fc}(t))^{(n_c - j)} \cdot (R_{cell}(t))^{(n_r \times k)} \cdot (1 - (R_{cell}(t))^{n_r})^{(s_r - k)}$$

(2.32)

$$R_{block}(t) = R_{block:s_r}(t) + R_{s_c}(t) \tag{2.33}$$

$$R_{seg}(t) = \sum_{i=0}^{N_s} {N_q + N_s \choose i} (R_{block}(t))^{N_q + N_s - i} \cdot (1 - R_{block}(t))^i$$

(2.34)

$$R(t) = (R_{seg}(t))^{N_{seg}} (2.35)$$

The overall dependability (i.e.,  $Pr\{\text{manufactured as good AND not failing during the time interval }[0,t]\}) can be written as follows:$

$$D(t) = Y \cdot R(t) \tag{2.36}$$

In addition to the reliability, the mean time to failure (MTTF) is another useful measurement to specify the quality of a system since the MTTF is the expected time that a system will operate before the first failure occurs. Therefore, it can be used to measure the system operation life without failure. The MTTF is defined in terms of the reliability function as

$$MTTF = \int_0^\infty R(t)dt \tag{2.37}$$

which is valid for any reliability function that satisfies  $R(\infty) = 0$ . Thus, the reliability function given in Equation (2.35) can be directly applied to Equation (2.37) to obtain the mean-time-to-failure (i.e., expected system operation life without failure) of the proposed fault-tolerant memory core.

# 2.5 Quality Assurance of the Proposed Fault-Tolerant Memory Core

In this section, the quality of the proposed fault-tolerant memory core in terms of the manufacturing yield, field reliability and mean-time-to-failure is assured by the proposed estimation techniques via a series of parametric simulations. The parameters are summarized as shown in Table 2.1. Although the proposed memory core architecture is flexible enough to implement various embedded memory core configurations, a sample 1Mbit memory core has been used for the parametric simulations. The sample 1Mbit memory core consists of 8 segments and each segment has 8 blocks of  $128 \times 128$  memory array without considering ECC and redundancy. Therefore, each block is a 16Kbit memory array and each segment is  $16K \times 8 = 128K$  and the core is  $128K \times 8 = 1M$ . The following observations and discussions can be made from the simulations:

• Manufacturing Yield Enhancement Ability of the Proposed Memory Core: In Figure (2.5), the manufacturing yield of the block, the segment and the core are initially given (i.e., Figure (2.5-a,b,d)) as a function of  $S_c$  and  $S_r$ . The ECC-only core configuration (i.e.,  $S_c$  and  $S_r = 0$  and  $N_s = 0$ ) shows almost zero manufacturing yield while the allocation of 5 spare rows and columns guarantees an almost perfect yielding core. In addition to the spare row/column redundancy,

Table 2.1: Simulation parameters for quality assurance

| Parameter   | Meaning                                         | Value             |

|-------------|-------------------------------------------------|-------------------|

| $\lambda_m$ | Expected manufacturing failures per memory cell | $1 \cdot 10^{-3}$ |

| $S_r, S_c$  | # of spare row/column                           | Variable          |

| $N_q$       | # of quorum block                               | 8                 |

| $N_s^-$     | # of spare block                                | Variable          |

| $N_{seg}$   | # of segment                                    | 8                 |

| $\lambda_f$ | Field failure arrival rate for memory cell      | $5 \cdot 10^{-6}$ |

| $\Delta t$  | Unit time interval                              | One week          |

the modular block redundancy also enhances the manufacturing yield significantly as shown in Figure (2.5-e). The combination of 4 spare rows and columns and a spare block per segment amazingly covers almost every manufacturing defect and achieves near 100% core yield. The results given in Figure (2.5) assure the manufacturing yield enhancement ability of the proposed fault-tolerant memory core architecture. Intelligent exploitation of the proposed quality assurance techniques can be also used to optimize the core design in terms of the desirable manufacturing yield while minimizing cost due to redundancy overhead.

• Field Reliability Enhancement Ability of the Proposed Memory Core: In Figures (2.6)-(2.12), extensive field reliability simulation results are shown. Numerous combinations of  $S_c$  ( $S_r$ ) from 0 to 8, and  $N_s$  from 0 to 2 are used to identify the robust field reliability enhancement ability of the proposed memory block, segment and core. As given in Figure (2.10-a), the ECC-only configuration of the sample core configuration hardly retains its reliability for the first 100 weeks while the  $S_c$ ,  $S_r = 8$  and  $N_s = 2$  core configuration (e.g., Figure (2.12-i)) successfully maintains its reliability more than 95% for 1200 weeks. The

common reliability requirement for long life applications is  $\geq 95\%$  for a 10 year mission period. Thus, the proposed embedded memory core even qualifies for the strict field reliability requirement.

• Prolonged MTTF: Mean-time-to-failure (MTTF) is a commonly used measurement of the average system life time. The redundancy configuration of  $S_c$ ,  $S_r = 8$  and  $N_s = 1$  has  $MTTF \approx 1200$  weeks while the ECC-only configuration has  $MTTF \approx 0$  weeks.

## 2.6 Summary

A high yield, ultra reliable embedded memory core architecture for SoC applications and its quality assurance techniques have been discussed in this chapter. The proposed fault-tolerant memory core organization takes advantage of the double-errordetection and single-error-correction (DED-SEC) error-correcting-code (ECC) to circumvent the single-bit faults while the row/column redundancy repairs more than two simultaneous faulty cells in a memory line or in wordline (bitline) failures. Synergistic fault-tolerance, first discovered in [43], has been also achieved in the proposed memory core design. The modular redundancy technique has been also introduced to overcome the memory-block-wise failures. The proposed memory core provides two distinctive repair mechanisms: the permanent laser redundancy reconfiguration during the wafer probe stage in the factory to enhance its manufacturing yield, and the dynamic BIST/BISD/BISR-based field reconfiguration of the redundant resources in the field to maintain high field reliability of the host SoC. The quality assurance techniques based on the combinatorial modeling scheme, which is suitable for the proposed memory core design, further verifies its abilities of enhancing manufacturing yield, excellent field reliability, improved tolerance against increasing failure arrival rates, and prolonged MTTF.

Figure 2.5: Yield analysis results of the sample 1Mbit core

Figure 2.6: Reliability analysis results of the sample 16K block

Figure 2.7: Reliability analysis results of the sample 16K x 8 (128K) Segment ( $N_s=0$ )

Figure 2.8: Reliability analysis results of the sample 16K x 8 (128K) Segment  $(N_s=1)$

Figure 2.9: Reliability analysis results of the sample 16K x 8 (128K) Segment ( $N_s=2$ )

Figure 2.10: Analysis results of the sample 16K x 8 x 8 (1M) Core  $(N_s=0)$

Figure 2.11: Analysis results of the sample 16K x 8 x 8 (1M) Core  $(N_s=1)$

Figure 2.12: Analysis results of the sample 16K x 8 x 8 (1M) Core  $(N_s=2)$

Figure 2.13: MTTF analysis results of the sample 1Mbit core

#### CHAPTER 3

# REDUNDANCY PARTITIONING FOR BALANCED MANUFACTURING YIELD AND FIELD RELIABILITY

As advances in Ultra-Large-Scale-Integration (ULSI) technologies make possible the seamless embedding of numerous cores on a single chip (i.e., Commonly referred to as System-On-Chip technology), solid dependability becomes an urgent requirement of such ultra density and high performance systems since insignificant degradation or defects of core components could result in unacceptably low resultant SoC manufacturing yield and field reliability. However, fabricated embedded memory system cores cannot be physically replaced in the field. Thus, built-in self-test, diagnosis and repair circuits are commonly practiced along with ATE-based repair to assure improved manufacturing yield and field reliability of the embedded memory core [36, 35, 37, 39]. Although it is obvious that the combination of ATE and BISR is able to achieve significant manufacturing yield <sup>1</sup> and field reliability <sup>2</sup> enhancements for embedded memory system core, one problem still remains unsolved:

How the given redundancy can be partitioned into two groups (i.e., one for ATE repair and another one for BISR repair) to balance the manufacturing yield and field reliability for the maximum dependability?

Since ATE (for repairing manufacturing defects) and BISR (for repairing field faults) share the given common redundancy, balanced redundancy partitioning and

<sup>&</sup>lt;sup>1</sup>the probability of being manufactured and repaired as functional

<sup>&</sup>lt;sup>2</sup>a function of time which is defined by the conditional probability that the system performs correctly throughout the interval of time  $[t_0, t]$  given the system was performing flawlessly at the initial time  $t_0$

utilization techniques are very important to achieve optimal combination of yield and reliability of the embedded memory system core. Thus, dependability evaluation techniques for single and two dimensional redundancy architectures will be initially investigated to unveil the significance of redundancy balancing. Then, balanced redundancy partitioning and utilization techniques for both single and two dimensional redundancy architectures will be investigated. Extensive parametric simulation results will be also shown.

The organization of this chapter is as follows: In the following section (Section 3.1), a conceptual architectural model of the embedded memory core with both ATE and BISR repair capabilities will be shown and significance of redundancy partitioning and utilization for balanced yield and reliability will be discussed. In Sections 3.2 and 3.3, detailed yield and reliability assurance techniques for single and two dimensional redundancy cases will be shown. Then, balanced redundancy partitioning and utilization techniques for both cases will be proposed as well. A set of parametric simulations further verifies the effectiveness of the proposed redundancy balancing techniques in Section 3.4. Finally, discussion and conclusions will be given in Section 3.5.

## 3.1 Preliminaries

Figure (2.3) shows a model of the embedded memory system core under investigation in which both ATE-based factory repair and BISR-based field repair are practiced for manufacturing yield and field reliability enhancements. The embedded memory system core under investigation consists of the following components:

• IEEE JTAG (Joint Test Action Group) 1149.1: External ATE interface for factory repair.

- Laser Fuse: A set of laser reconfigurable fuses to permanently program the given redundancy resources in the factory.

- BIST/BISD/BISR Processor: This system component governs the self-test, self-diagnosis, and self-repair procedures.

- Programmable Fuse: A set of programmable fuses to store additional reconfiguration signatures generated by the BIST/BISD/BISR processor in the field.

- Memory Array Interface: This component connects the EAB (embedded array block) array and the BIST/BISD/BISR Processor together. Data, address, control and repair data flow via this component.

The given embedded memory system core is tested and repaired as follows:

- Factory Repair Process: To circumvent the defects due to imperfect manufacturing processes, ATE communicates with the embedded memory system core via the external test equipment interface. Then, the laser fuse is permanently programmed to allocate redundancy to repair manufacturing defects in EABs.

- Field Repair Process: Whenever the host SoC is reset or powered, BISR tests, diagnoses and repairs EABs. The programmable fuse is programmed to store redundancy allocation information.

# 3.2 Single Dimensional Redundancy Case

The following notations will be used throughout this chapter:

- $n_c$ : Number of columns (i.e., number of bits per word).

- $n_r$ : Number of rows (i.e., number of words).

- $s_c$ : Number of spare columns.

- $s_{cm}$ : Number of spare columns used for manufacturing yield enhancement (i.e.,  $s_c s_{cf}$ ).

- $s_{cf}$ : Number of spare columns used for field reliability enhancement (i.e.,  $s_c s_{cm}$ ).

- $\bullet \ \lambda_m$  : Expected number of manufacturing defects per memory cell.

- $\lambda_f$  : Field failure arrival rate of memory cell per unit time interval.

- *Y* : Manufacturing yield.

- R(t): Field reliability at time t.

- D(t): Overall dependability.

The yield of a single cell can be formulated by the exponential failure law as

$$Y_{cell} = e^{-\lambda_m} \tag{3.1}$$

Then, the probability of having  $n_r$  non-defective cells in a column (i.e., the yield of a column) can be written as

$$Y_{column} = (Y_{cell})^{n_r} (3.2)$$

The given memory consists of  $n_c$  memory columns and  $s_{cm}$  spare memory columns for yield enhancement. The quorum size of  $n_c$  of the total of  $n_c + s_{cm}$  columns are required to be functional. Thus, the yield of the given memory with column-redundancy can be formulated by the binomial distribution as follows:

$$Y = \sum_{i=0}^{s_{cm}} \binom{n_c + s_{cm}}{i} (Y_{column})^{n_c + s_{cm} - i} \cdot (1.0 - Y_{column})^i$$

(3.3)

Reliability assurance equations are similar to the yield assurance equations and can be expressed as follows:

$$R_{cell}(t) = e^{-\lambda_f \cdot t} \tag{3.4}$$

$$R_{column}(t) = (R_{cell})^{n_r} (3.5)$$

$$R(t) = \sum_{i=0}^{s_{cf}} \binom{n_c + s_{cf}}{i} (R_{column}(t))^{n_c + s_{cf} - i} \cdot (1.0 - R_{column}(t))^i$$

$$= \sum_{i=0}^{s_c - s_{cm}} \binom{n_c + s_c - s_{cm}}{i} (R_{column}(t))^{n_c + s_c - s_{cm} - i} \cdot (1.0 - R_{column}(t))^i$$

(3.6)

The conditional probability of having manufactured-as-good (i.e., Y) and not-failing-in-the-field during the time interval  $[t_0, t]$  (i.e., R(t)) is referred to as dependability denoted by D(t). Since Y and R(t) are serial probabilities, the product of equations 3.3 and 3.7 can be used to formulate D(t).

$$D(t) = Y \cdot R(t)$$

$$= \sum_{i=0}^{s_{cm}} {n_c + s_{cm} \choose i} (Y_{column})^{n_c + s_{cm} - i} \cdot (1.0 - Y_{column})^i$$

$$\times \sum_{i=0}^{s_c - s_{cm}} {n_c + s_c - s_{cm} \choose i} (R_{column}(t))^{n_c + s_c - s_{cm} - i}$$

$$\times (1.0 - R_{column}(t))^i$$

(3.8)

To find the most balanced  $s_{cm}$ , D(t) can be differentiated and solved with respect to  $s_{cm}$  as follows.

$$\frac{dD(t)}{ds_{cm}} = 0 (3.10)$$

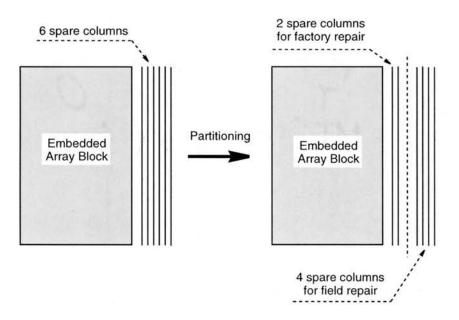

Note that  $s_{cf} = s_c - s_{cm}$  holds and  $s_{cm}$  must be an integer value. So, both  $\lceil s_{cm} \rceil$  and  $\lfloor s_{cm} \rfloor$  must be evaluated to determine the final partitioning position. Figure (3.1) shows an example of an EAB with six spare columns. Later, they are partitioned into two groups: two spare columns for ATE repair and four spare columns for BISR repair.

Figure 3.1: Example of redundancy partitioning for single dimensional redundancy

# 3.3 Two Dimensional Redundancy Case

The following notations will be used in addition to the ones given in the previous section throughout this chapter:

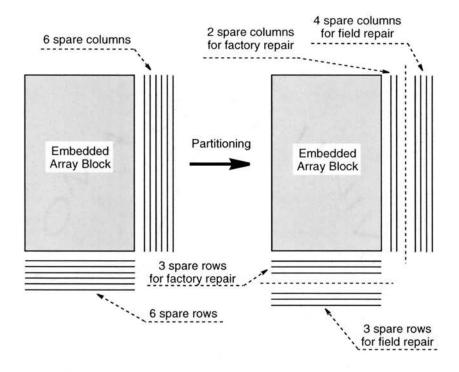

Figure 3.2: Example of redundancy partitioning for two dimensional redundancy

- $s_r$ : Number of spare rows.

- $s_{rm}$ : Number of spare rows used for manufacturing yield enhancement (i.e.,  $S_r S_{rf}$ ).

- $s_{rf}$ : Number of spare rows used for field reliability enhancement (i.e.,  $S_c S_{rm}$ ).

- $\lambda_{cm}$ : Expected number of manufacturing defects per memory column.

- $\lambda_{rm}$  : Expected number of manufacturing defects per memory row.

- $\lambda_{cf}$ : Field failure arrival rate of memory column per unit time interval.

- $\lambda_{rf}$  : Field failure arrival rate of memory row per unit time interval.

Since row/column deletion is one of the NP-complete problems, there is no effective way to derive closed formulas for Y and R(t). So, in this chapter, a line-based fault

model is used rather than the cell-based fault model for 2-D case.

The yield of a row and a column can be approximated as  $Y_{row}=e^{-\lambda_{rm}}$  and  $Y_{column}=e^{-\lambda_{cm}}.$

Then, the yield of rows is

$$Y_{rows} = \sum_{i=0}^{s_{rm}} \binom{n_r + s_{rm}}{i} (Y_{row})^{n_r + s_{rm} - i} \cdot (1.0 - Y_{row})^i$$

(3.11)

and the yield of columns is

$$Y_{columns} = \sum_{i=0}^{s_{cm}} \binom{n_c + s_{cm}}{i} (Y_{colmun})^{n_c + s_{cm} - i} \cdot (1.0 - Y_{column})^i$$

(3.12)

Thus, the overall yield is

$$Y = Y_{rows} \times Y_{columns} \tag{3.13}$$

Likewise,

$$R_{row}(t) = e^{-\lambda_{rm} \cdot t} \tag{3.14}$$

$$R_{column}(t) = e^{-\lambda_{cm} \cdot t} \tag{3.15}$$

$$R_{rows}(t) = \sum_{i=0}^{s_{rf}} {n_r + s_{rf} \choose i} (R_{row}(t))^{n_r + s_{rf} - i} \cdot (1.0 - R_{row}(t))^{i}$$

$$= \sum_{i=0}^{s_r - s_{rm}} {n_r + s_r - s_{rm} \choose i} (R_{row}(t))^{n_r + s_r - s_{rm} - i} \cdot (1.0 - R_{row}(t))^{i} (3.16)$$

$$R_{columns}(t) = \sum_{i=0}^{s_{cf}} \binom{n_c + s_{cf}}{i} (R_{colmun}(t))^{n_c + s_{cf} - i} \cdot (1.0 - R_{column}(t))^{i}$$

$$= \sum_{i=0}^{s_c - s_{cm}} \binom{n_c + s_c - s_{cm}}{i} (R_{colmun}(t))^{n_c + s_c - s_{cm} - i}$$

$$\times (1.0 - R_{column}(t))^{i}$$

(3.17)

$$R(t) = R_{rows}(t) \times R_{columns}(t) \tag{3.18}$$

The overall dependability, then, can be written as

$$D(t) = Y \times R(t) \tag{3.19}$$

To find the most balanced  $s_{cm}$  and  $s_{rm}$ , D(t) can be differentiated and solved with respect to  $s_{cm}$  and  $s_{rm}$  as follows:

$$\frac{d^2D(t)}{ds_{cm}ds_{cm}} = 0 ag{3.20}$$

Note that  $s_{cf} = s_c - s_{cm}$  and  $s_{rf} = s_r - s_{rm}$  hold and  $s_{cm}$  and  $s_{rm}$  must be integer values. So, the combination of  $\lceil s_{cm} \rceil$  &  $\lfloor s_{cm} \rfloor$  and  $\lceil s_{rm} \rceil$  &  $\lfloor s_{rm} \rfloor$  must be evaluated to determine the final partitioning positions. Figure (3.2) shows an example of an EAB with six spare columns and six spare rows. Later, spare columns are partitioned into two groups: two spare columns for ATE repair and four spare columns for BISR repair and spare rows are also partitioned into two groups: three spare columns for ATE repair and three spare columns for BISR repair.

## 3.4 Parametric Simulations and Results

The effect of the redundancy balancing for both single and two dimensional cases will be studied through numerical experiments in this section. Parameters used in the simulation for the single dimensional redundancy case are summarized in Table 3.1 and for the two dimensional redundancy case are summarized in Table 3.2

Table 3.1: Simulation parameters for a one dimensional case

Table 3.2: Simulation parameters for a two dimensional case

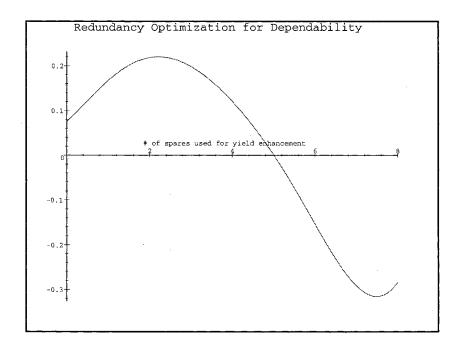

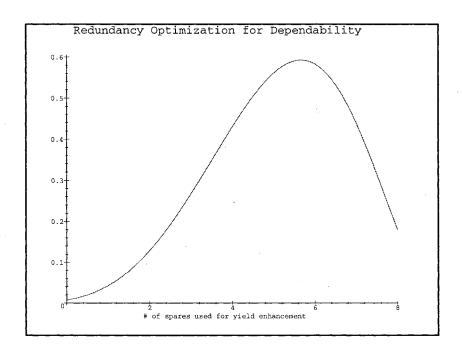

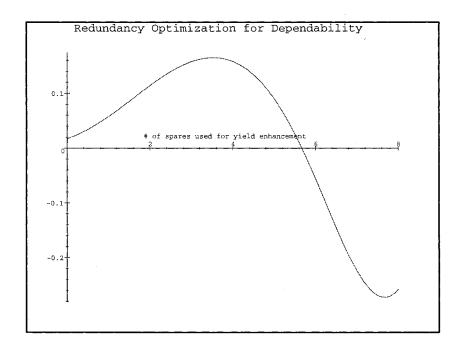

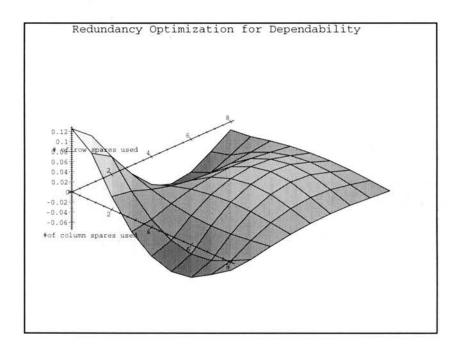

Observation 1 The simulation results for the single dimensional redundancy case are shown in Figures (3.3) - (3.8) and the following observations can be made:

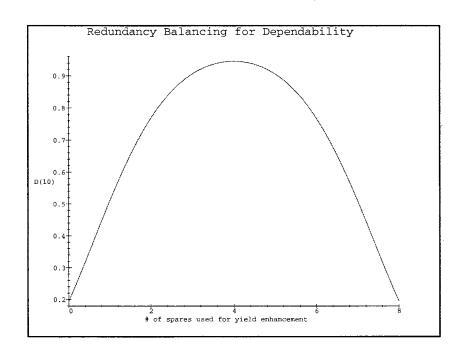

- Symmetric Case: In Figures (3.3) and (3.4), the dependability and its derivative of the given EAB are plotted with respect to  $s_{cm}$ . In this case, the parameters are selected in order that Y and R(t) show exactly symmetric behaviors. Thus, the partitioning result is [4,4]: 4 spare columns for factory repair and 4 spare columns for field repair. The spares are evenly partitioned and utilized in this case.

- Reliability-Intensive Case: In Figures (3.5) and (3.6), the dependability and its derivative of the given EAB are plotted with respect to  $s_{cm}$ . In this case,

the parameters are selected in order that more field faults than manufacturing defects are induced (i.e.,  $t=10 \rightarrow 20$ ). Thus, the partitioning result is [3,5]: 3 spare columns for factory repair and 5 spare columns for field repair. The spares are partitioned and utilized in favor of field reliability enhancement in this case.

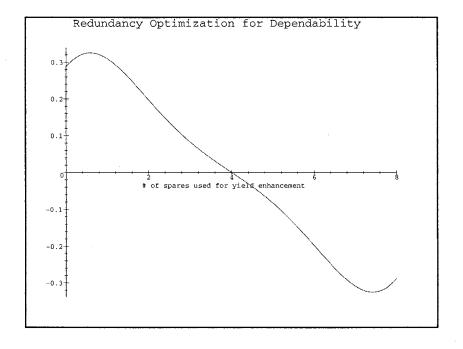

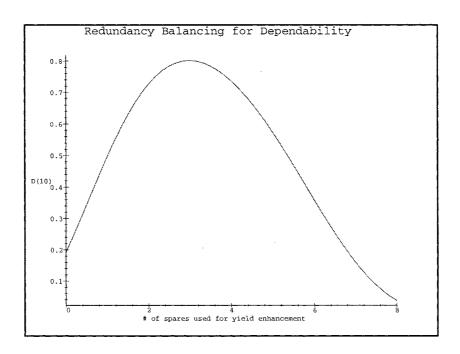

• Yield-Intensive Case: In Figures (3.7) and (3.8), the dependability and its derivative of the given EAB are plotted with respect to  $s_{cm}$ . In this case, the parameters are selected in order that more manufacturing defects than field faults are induced (i.e.,  $\lambda_m = 10^{-4} \rightarrow 2 \times 10^{-4}$ ). Thus, the partitioning result is [5,3]: 5 spare columns for factory repair and 3 spare columns for field repair. The spares are partitioned and utilized in favor of manufacturing yield enhancement in this case.

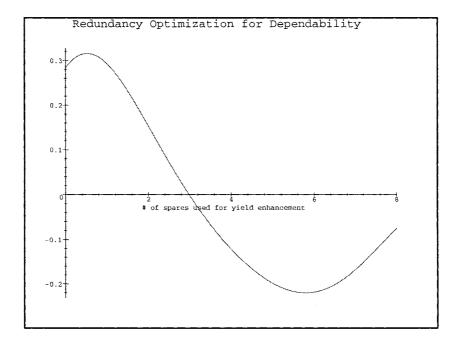

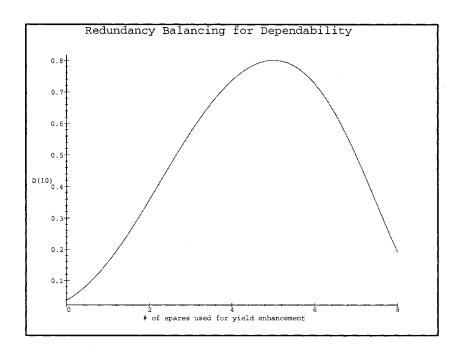

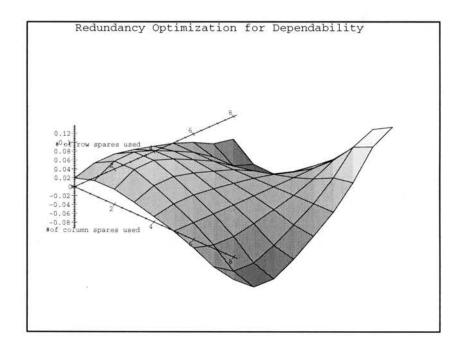

Case Study 1 The redundancy balancing results,  $s_{cm}$  and  $s_{cf}$ , must be integer values. So, both  $\lceil s_{cm} \rceil$  and  $\lfloor s_{cm} \rfloor$  must be evaluated to determine the final partitioning position, if the solution to the  $\frac{dD(t)}{ds_{cm}} = 0$  is not an integer value. An example is given in Figures (3.9) and (3.10), in which the redundancy optimization result is not an integer. Thus, both D(t) at  $\lceil s_{cm} \rceil$  and D(t) at  $\lfloor s_{cm} \rfloor$  are compared to find the optimal balancing. As a result, the proposed redundancy balancing technique partitions the redundancy into [6,2].

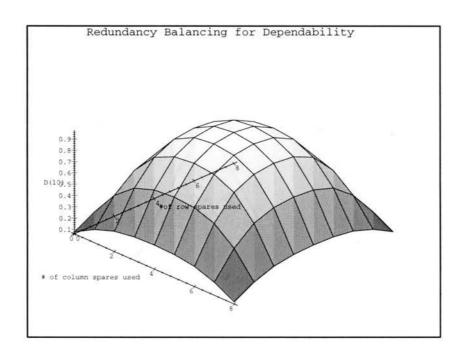

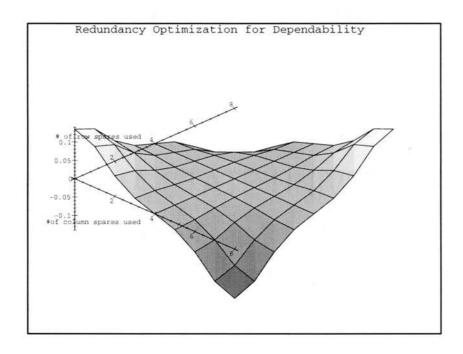

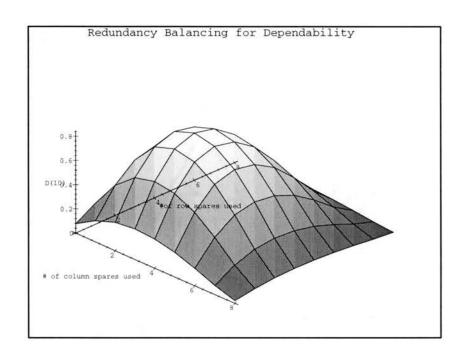

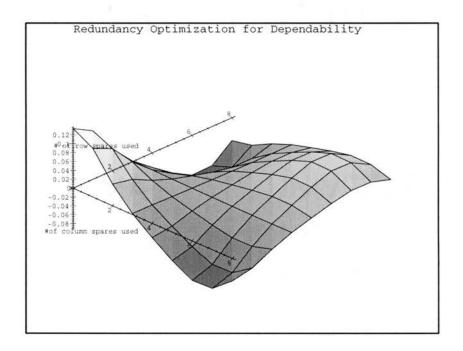

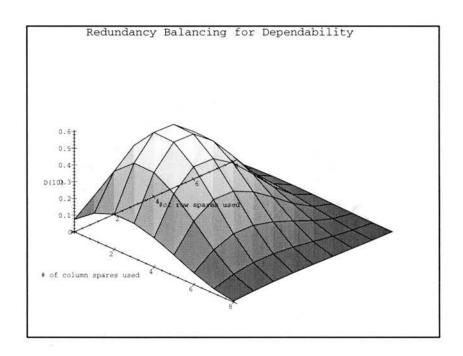

**Observation 2** The simulation results for the two dimensional redundancy case are shown in Figures (3.11) - (3.16), the following observations can be extended from the observation 1:

• Symmetric Case: In Figures (3.11) and (3.12), the dependability and its derivative of the given EAB are plotted with respect to  $s_{cm}$  and  $s_{rm}$ . In this case,

the parameters are selected in order that Y and R(t) show exactly symmetric behaviors. Thus, the partitioning result is  $\{[4,4],[4,4]\}$ : 4 spare columns and rows for factory repair and 4 spare columns and rows for field repair. The spares are evenly partitioned and utilized in this case.

- Reliability-Intensive Case: In Figures (3.13) and (3.14), the dependability and its derivative of the given EAB are plotted with respect to s<sub>cm</sub> and s<sub>rm</sub>. In this case, the parameters are selected in order that more field faults than manufacturing defects are induced (i.e., t = 10 → 20). Thus, the partitioning result is {[3,5],[3,5]}: 3 spare columns and rows for factory repair and 5 spare columns and rows for field repair. The spares are partitioned and utilized in favor of field reliability enhancement in this case.

- Yield-Intensive Case: In Figures (3.15) and (3.16), the dependability and its derivative of the given EAB are plotted with respect to  $s_{cm}$  and  $s_{rm}$ . In this case, the parameters are selected in order that more manufacturing defects than field faults are induced (i.e.,  $\lambda_m = 10^{-4} \rightarrow 2 \times 10^{-4}$ ). Thus, the partitioning result is {[5,3],[5,3]}: 5 spare columns and rows for factory repair and 3 spare columns and rows for field repair. The spares are partitioned and utilized in favor of manufacturing yield enhancement in this case.

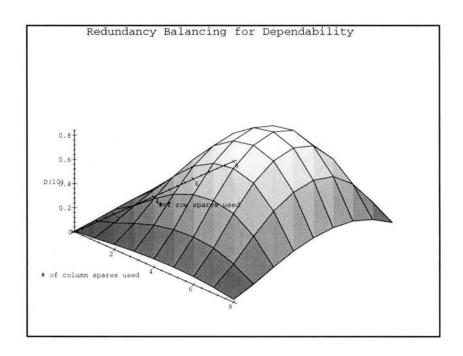

Case Study 2 The 2-D redundancy balancing results,  $s_{cm}$  and  $s_{cf}$  and  $s_{rm}$  and  $s_{rf}$ , must be integer values. So, the following four combinations must be evaluated to find the optimal balancing, if the solution to the  $\frac{d^2D(t)}{ds_{cm}ds_{rm}} = 0$  is not integer values:

- $\lceil s_{cm} \rceil$  and  $\lceil s_{rm} \rceil$

- $\lceil s_{cm} \rceil$  and  $\lfloor s_{rm} \rfloor$

- $\lfloor s_{cm} \rfloor$  and  $\lceil s_{rm} \rceil$

- $\lfloor s_{cm} \rfloor$  and  $\lfloor s_{rm} \rfloor$

An example is given in Figures (3.17) and (3.18), in which the redundancy optimization result is not a pair of integers. Thus, all D(t)'s of the four possible balancing candidates shown above are compared to find the optimal balancing. As a result, the proposed redundancy balancing technique partitions the redundancy into  $\{[2,6],[2,6]\}$ .

## 3.5 Discussion

Among the cores for SoC integration, one of the most sensitive cores is the embedded memory core since memory cells are commonly considered as more prone to defects and faults than logic cells. Since cores cannot be physically replaced once they are fabricated onto a SoC, a combination of both ATE and BISR is commonly practiced. Proper partitioning and utilization of given shared redundancy is highly desirable to achieve balanced manufacturing yield and field reliability of the embedded memory system core. Thus, yield and reliability assurance techniques have been initially proposed for the single dimensional redundancy case, then extended to the two dimensional redundancy case. Since yield and reliability trade off with each other, dependability (i.e.,  $Y \times R(t)$ ) reaches its maximum only if properly partitioned groups of the given redundancy are utilized to repair both manufacturing defects (i.e., ATE-based repair) and field faults (i.e., BISR-based repair). To effectively achieve the balanced redundancy partitioning and utilization, the dependability equations are differentiated and solved with respect to the number of spares used to enhance manufacturing yield. Parametric simulation results have further verified that the proposed redundancy partitioning and utilization techniques for embedded memory system core achieves the theoretically optimal redundancy balancing. The proposed

redundancy balancing techniques can be possibly incorporated into the existing CAD compilers for embedded memory system cores, thereby cost-effective partitioning and utilization of the shared redundancy can be realized.

Figure 3.3: Symmetric 1D dependability graph

Figure 3.4: Balanced partitioning result [4,4]

Figure 3.5: Reliability-intensive 1D dependability graph

Figure 3.6: Balanced partitioning result [3,5]

Figure 3.7: Yield-intensive 1D dependability graph

Figure 3.8: Balanced partitioning result [5,3]

Figure 3.9: An example 1D dependability graph

Figure 3.10: Balanced partitioning result [6,2]

Figure 3.11: Symmetric 2D dependability graph

Figure 3.12: Balanced partitioning result  $\{[4,4],[4,4]\}$

Figure 3.13: Reliability-intensive 2D dependability graph

Figure 3.14: Balanced partitioning result  $\{[3,5],[3,5]\}$

Figure 3.15: Yield-intensive 2D dependability graph

Figure 3.16: Balanced partitioning result  $\{[5,3],[5,3]\}$

Figure 3.17: An example of 2D dependability graph

Figure 3.18: Balanced partitioning result  $\{[2,6],[2,6]\}$

## CHAPTER 4

## CONNECTIVITY-BASED RECONFIGURABLE SOC REPAIR