# EFFICIENT SCHEMES TO SIZE TRANSISTORS FOR OPTIMAL DELAY BY SOLVING FANOUT BRANCHES WITH BALANCING ALGORITHM

#### By

#### Mehedi Sarwar

Bachelor of Science in Electrical and Electronics

Engineering

Bangladesh University of Engineering and Technology

(BUET)

Dhaka, Bangladesh

2005

Master of Science in Electrical Engineering University of Texas at Dallas Richardson, TX 75080 USA 2008

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of DOCTOR OF PHILOSOPHY MAY, 2015

# EFFICIENT SCHEMES TO SIZE TRANSISTORS FOR OPTIMAL DELAY BY SOLVING FANOUT BRANCHES WITH BALANCING ${\bf ALGORITHM}$

| Dissertation Approved: |  |  |  |  |

|------------------------|--|--|--|--|

|                        |  |  |  |  |

| Dr. James E. Stine Jr. |  |  |  |  |

| Dissertation Adviser   |  |  |  |  |

| Dr. Louis G. Johnson   |  |  |  |  |

|                        |  |  |  |  |

| Dr. Chriswell Hutchens |  |  |  |  |

|                        |  |  |  |  |

| Dr. Blayne E. Mayfield |  |  |  |  |

#### ACKNOWLEDGMENTS

I would like express my sincere appreciation and gratitude to my PhD adviser Dr. James E. Stine for his motivation, continuous support for my PhD and research works. Specially, his immense knowledge on VLSI had helped me a lot in generating new ideas and implementing them. He also should get special thanks for providing very good lab facilities, state of the art licensed software and high-performance server machines which helped not only me but our entire research group.

I will also want to express my humble gratitude to my PhD review committee members – Dr. Louis G. Johnson, Dr. Chriswell Hutchens and Dr. Blayne E. Mayfield for their encouragement, insightful comments and questions at my PhD qualifiers that helped me to do research in many new angles.

I want to thank my close friend and University of Texas at Dallas alumni Altaf Rahman for his generosity , knowledge sharing and inspirations.

My sincere thanks goes to my fellow lab-mates at the VLSI Computer Architecture Group (VCAG) in Oklahoma State University: Dr. Masoud Sadeghian, Dr. Son Bui, Samira Ataei, Manju Kiran Subbarayappa, Robert Elliot, Rabin Thapa, Tuan Nguyen for their since support, encouragement, ideas and discussion.

Lastly, I want to thank my family for their patience and encouragement.

Acknowledgements reflect the views of the author and are not endorsed by committee members or Oklahoma State University.

Name: Mehedi Sarwar

Date of Degree: MAY, 2015

Title of Study: EFFICIENT SCHEMES TO SIZE TRANSISTORS FOR

OPTIMAL DELAY BY SOLVING FANOUT BRANCHES

WITH BALANCING ALGORITHM

Major Field: Electrical Engineering

High performance digital system requires minimal logic and properly sized transistor to operate in all PVT corners. Specifically, high-speed data-path design is mostly about optimizing the system for better timing. In this work, the author proposed a better timing model to analyze parallel data-paths better for performance comparison. Moreover, a novel transistor sizing technique is also proposed as part of the work to minimize delay in parallel data-path circuits in the presence of practical wire capacitance. With this technique it is easier to calculate the optimal capacitance distribution in a fanout branch path that equalizes the delays in all branches as well as minimizes the overall delay starting from the primary inputs to the primary outputs of a circuit. The problem is widely termed as the "Load distribution problem at branch". A collection of fast algorithms were designed to accurately solve the load distribution problem for branch in digital circuits for optimal delay. The author used prior work on Unified Logical Effort[1] as a tool for delay estimation and transistor sizing. This research work also shows the impact of branching on critical path. Experiments are run on industry standard circuits using different types of tools developed to model the circuit. The new developed theories are tested on the circuit models, that are also included in this work.

### TABLE OF CONTENTS

| Cł | Chapter |        |                                                                |      |

|----|---------|--------|----------------------------------------------------------------|------|

| 1  | Inti    | oduct  | ion                                                            | 1    |

|    | 1.1     | Circui | it and system design                                           | . 1  |

|    |         | 1.1.1  | Design flow                                                    | . 1  |

|    |         | 1.1.2  | Electronic design automation (EDA)                             | 2    |

|    |         | 1.1.3  | Motivation for EDA tool design in academia                     | . 3  |

|    |         | 1.1.4  | Overview of path optimization using gate sizing                | 4    |

|    |         | 1.1.5  | Orientation of the thesis                                      | 4    |

| 2  | Ok      | CAD    | tools                                                          | 6    |

|    | 2.1     | Ok C   | AD tools                                                       | . 6  |

|    |         | 2.1.1  | Ok CAD tool flow                                               | . 6  |

|    |         | 2.1.2  | ANTLR parser generator                                         | . 8  |

|    |         | 2.1.3  | Verilog subset compiler                                        | . 8  |

|    |         | 2.1.4  | LogicGraph : digital circuit expressed as directed graph       | 10   |

|    | 2.2     | Summ   | nary                                                           | . 11 |

| 3  | Bin     | ary de | ecision diagram (BDD)                                          | 12   |

|    | 3.1     | Logic  | optimization with reduced ordered binary decision diagram (ROB | DD)  |

|    |         | techni | iques                                                          | . 12 |

|    |         | 3.1.1  | History and background                                         | 12   |

|    |         | 3.1.2  | Basic concepts                                                 | . 13 |

|    |         | 3.1.3  | Shanon's co-factor                                             | . 14 |

|   |                                 | 3.1.4                                                  | ROBDD output function inversion                                                                                                                                                                                                                                                                        | 15                                           |

|---|---------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|   |                                 | 3.1.5                                                  | ROBDD input variable inversion                                                                                                                                                                                                                                                                         | 16                                           |

|   |                                 | 3.1.6                                                  | Ordering rules                                                                                                                                                                                                                                                                                         | 17                                           |

|   |                                 | 3.1.7                                                  | Reduction rules                                                                                                                                                                                                                                                                                        | 18                                           |

|   |                                 | 3.1.8                                                  | BDD reduction example                                                                                                                                                                                                                                                                                  | 19                                           |

|   |                                 | 3.1.9                                                  | ROBDD manipulation                                                                                                                                                                                                                                                                                     | 22                                           |

|   |                                 | 3.1.10                                                 | ITE algorithm                                                                                                                                                                                                                                                                                          | 23                                           |

|   |                                 | 3.1.11                                                 | Variable ordering                                                                                                                                                                                                                                                                                      | 25                                           |

|   | 3.2                             | OkBD                                                   | D features                                                                                                                                                                                                                                                                                             | 28                                           |

|   |                                 | 3.2.1                                                  | ROBDD data structure                                                                                                                                                                                                                                                                                   | 28                                           |

|   |                                 | 3.2.2                                                  | GraphStream visualization                                                                                                                                                                                                                                                                              | 29                                           |

|   | 3.3                             | Compa                                                  | arison and analysis                                                                                                                                                                                                                                                                                    | 29                                           |

|   | 3.4                             | Summ                                                   | ary                                                                                                                                                                                                                                                                                                    | 30                                           |

|   |                                 |                                                        |                                                                                                                                                                                                                                                                                                        |                                              |

| 4 | Tec                             | hnolog                                                 | y mapping                                                                                                                                                                                                                                                                                              | 33                                           |

| 4 | <b>Tec</b> : 4.1                | 0.                                                     | y mapping chnology mapping problem                                                                                                                                                                                                                                                                     | <b>33</b>                                    |

| 4 |                                 | The te                                                 |                                                                                                                                                                                                                                                                                                        |                                              |

| 4 | 4.1                             | The te                                                 | chnology mapping problem                                                                                                                                                                                                                                                                               | 33<br>33                                     |

| 4 | 4.1 4.2                         | The te                                                 | chnology mapping problem                                                                                                                                                                                                                                                                               | 33<br>33                                     |

| 4 | 4.1 4.2                         | The tell History Technology 4.3.1                      | chnology mapping problem                                                                                                                                                                                                                                                                               | 33<br>33<br>37                               |

| 4 | 4.1 4.2                         | The tell History Technology 4.3.1                      | chnology mapping problem                                                                                                                                                                                                                                                                               | 33<br>33<br>37<br>38                         |

| 4 | 4.1 4.2                         | The tell History Technology 4.3.1 4.3.2                | chnology mapping problem                                                                                                                                                                                                                                                                               | 33<br>33<br>37<br>38<br>39                   |

| 4 | 4.1 4.2                         | The tell History Technol 4.3.1 4.3.2 4.3.3 4.3.4       | chnology mapping problem                                                                                                                                                                                                                                                                               | 33<br>37<br>38<br>39<br>40                   |

| 5 | 4.1<br>4.2<br>4.3               | The tell History Technol 4.3.1 4.3.2 4.3.3 4.3.4 Summ. | chnology mapping problem                                                                                                                                                                                                                                                                               | 33<br>33<br>37<br>38<br>39<br>40<br>41       |

|   | 4.1<br>4.2<br>4.3               | The te History Technol 4.3.1 4.3.2 4.3.3 4.3.4 Summ    | chnology mapping problem                                                                                                                                                                                                                                                                               | 33<br>37<br>38<br>39<br>40<br>41<br>41       |

|   | 4.1<br>4.2<br>4.3<br>4.4<br>ULI | The te History Technol 4.3.1 4.3.2 4.3.3 4.3.4 Summ    | chnology mapping problem  y and background  ology mapping using structural hashing and dynamic programming  Base function and pattern graph  Structural hashing and pattern matching  Optimal covering with dynamic programming  Technology mapping features in OK CAD tools  ary  fied logical effort | 33<br>33<br>37<br>38<br>39<br>40<br>41<br>41 |

|   |     | 5.1.3   | ULE expressions for long wire segments                          | 51 |

|---|-----|---------|-----------------------------------------------------------------|----|

|   |     | 5.1.4   | Application of ULE to repeater insertion problems               | 53 |

|   |     | 5.1.5   | ULE method handling branch                                      | 53 |

|   | 5.2 | Summ    | nary                                                            | 56 |

| 6 | Pat | h optii | mization using ULE                                              | 57 |

|   | 6.1 | Backg   | round                                                           | 57 |

|   | 6.2 | Load    | distribution and path optimization                              | 59 |

|   |     | 6.2.1   | Load distribution problem                                       | 59 |

|   |     | 6.2.2   | Path optimization problem                                       | 60 |

|   |     | 6.2.3   | Calculating branching effort for equal delay for fan-out of two |    |

|   |     |         | path                                                            | 62 |

|   |     | 6.2.4   | Calculation method for multiple branching paths                 | 63 |

|   | 6.3 | Summ    | nary                                                            | 67 |

| 7 | Opt | imal b  | oudget capacitance                                              | 68 |

|   | 7.1 | Calcul  | lation of optimal budget capacitance                            | 68 |

|   |     | 7.1.1   | Upper bound and lower bound of optimal budget capacitance       | 68 |

|   |     | 7.1.2   | 5-point algorithm                                               | 71 |

|   |     | 7.1.3   | Multiple branch points                                          | 74 |

|   | 7.2 | Summ    | ary                                                             | 76 |

| 8 | Exp | erime   | nts and results                                                 | 77 |

|   |     | 8.0.1   | Experimental setups                                             | 77 |

|   |     | 8.0.2   | Metropolis simulated annealing gate placement algorithm         | 78 |

|   | 8.1 | Result  | 58                                                              | 81 |

|   |     | 8.1.1   | Results branching effort calculations                           | 81 |

|   |     | 812     | Data-paths under test                                           | 85 |

|   | 8.1.3     | Results of delay optimization with accurate branching for large |    |

|---|-----------|-----------------------------------------------------------------|----|

|   |           | data-paths                                                      | 86 |

|   | 8.2 Summ  | nary                                                            | 89 |

| 9 | Conclusio | n                                                               | 90 |

|   | 9.0.1     | Research accomplished                                           | 90 |

|   | 9.0.2     | Future work                                                     | 91 |

## LIST OF TABLES

| Table |                                                                     | Page |

|-------|---------------------------------------------------------------------|------|

| 3.1   | Truth table representation of a Boolean function                    | 20   |

| 3.2   | Boolean functions of two arguments and equivalent representation in |      |

|       | terms of the ITE operator                                           | 24   |

| 3.3   | Measures for Table 3.4                                              | 31   |

| 3.4   | Comparison of BDD packages adapted from Janssen's paper $[2]$       | 32   |

| 8.1   | Runtime                                                             | . 81 |

| 8.2   | Algorithm simulation results for high-performance adders            | 87   |

| 9.1   | Summary of algorithms                                               | 90   |

### LIST OF FIGURES

| Figure |                                                                         | Page |

|--------|-------------------------------------------------------------------------|------|

| 1.1    | ASIC design flow                                                        | 2    |

| 2.1    | OK CAD tool flow                                                        | 7    |

| 2.2    | OkCAD tool with generated sample ROBDD                                  | 7    |

| 2.3    | OkCAD tools with generated sample LogicGraph                            | 7    |

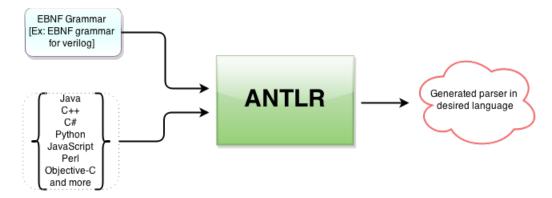

| 2.4    | ANTLR flow                                                              | 8    |

| 2.5    | Verilog parse tree generated by ANTLR 4 based Verilog compiler $$       | 9    |

| 3.1    | BDD of basic functions                                                  | 15   |

| 3.2    | Shanon's expansion in OBDD                                              | 16   |

| 3.3    | ROBDD function inversion                                                | 16   |

| 3.4    | ROBDD of different flavors of NAND3function                             | 17   |

| 3.5    | Ordering rule                                                           | 18   |

| 3.6    | OBDD reduction rules                                                    | 19   |

| 3.7    | OBDD reduction example                                                  | 21   |

| 3.8    | ROBDD sharing example                                                   | 22   |

| 3.9    | ITE analogy with 2:1 MUX in hardware                                    | 23   |

| 3.10   | Complexity of variable ordering                                         | 27   |

| 3.11   | Adjacent variable exchange in ROBDD                                     | 28   |

| 4.1    | Pattern graph of different logic elements of a typical standard library | 37   |

| 4.2    | Asymmetric pattern graph example                                        | 38   |

| 4.3    | AIG pattern variation of 4-input AND gate                               | 38   |

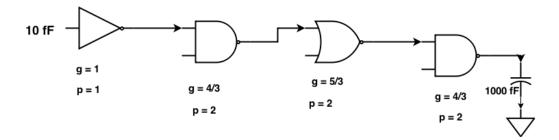

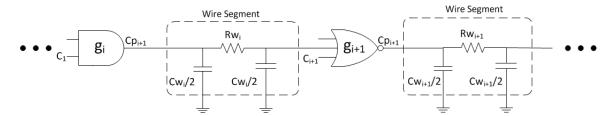

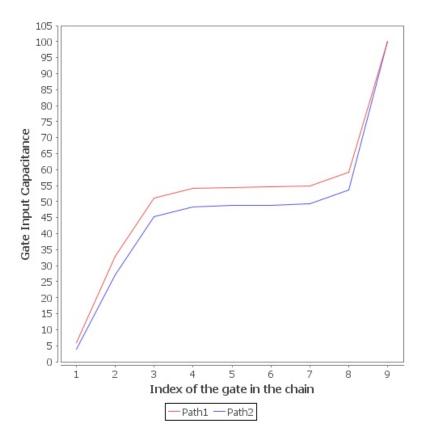

| 5.1 | Logical Effort (LE) example                                                          | 43 |  |

|-----|--------------------------------------------------------------------------------------|----|--|

| 5.2 | Practical logic path with logic gates and RC interconnect                            |    |  |

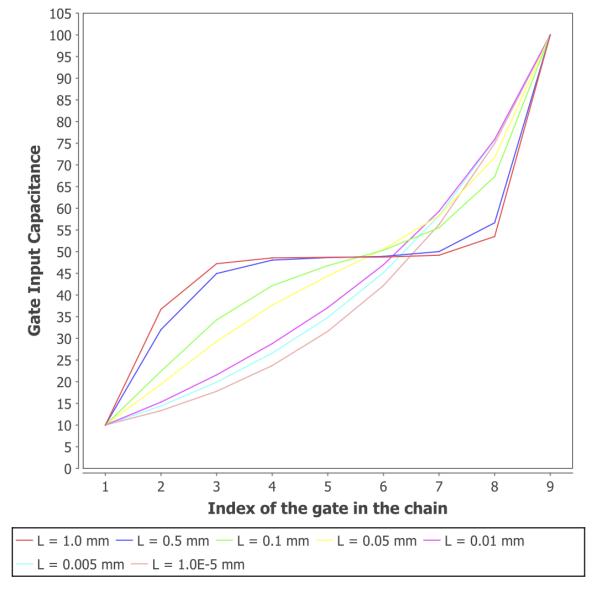

| 5.3 | Optimization with ULE for a chain of nine NAND gates with equal                      |    |  |

|     | wire segments in between for a variety of wire length. All the gate                  |    |  |

|     | sizes are normalized with respect to $C_0$ . Input capacitance of the first          |    |  |

|     | and the last gates are $10 \cdot C_0$ and $100 \cdot C_0$ respectively and H = 10    | 49 |  |

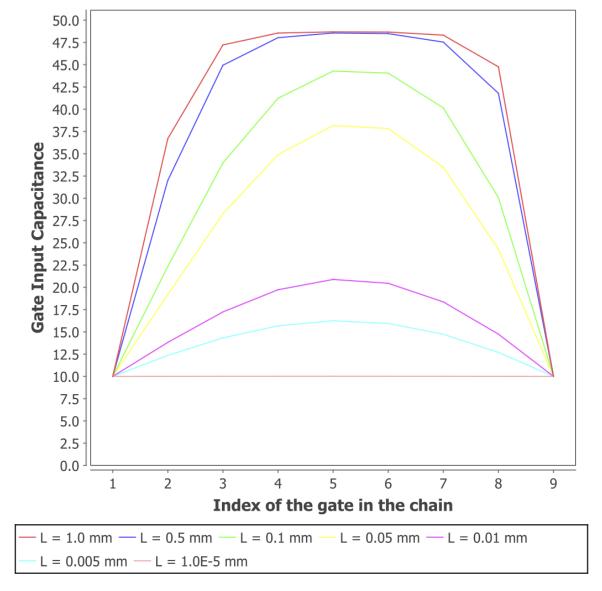

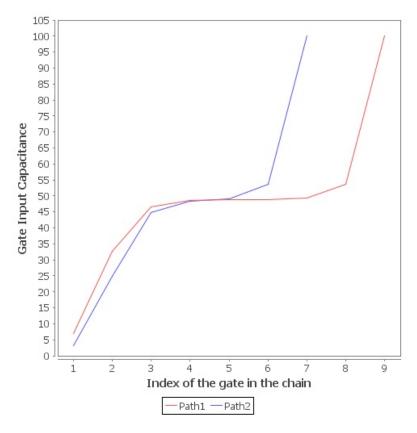

| 5.4 | The optimization with ULE for a chain of nine NAND gates with equal                  |    |  |

|     | wire segments in between for a variety of wire length. All the gate sizes            |    |  |

|     | are normalized with respect to $C_0$ . Input capacitance of the first and            |    |  |

|     | the last gates are $10 \cdot C_0$ and $10 \cdot C_0$ respectively and $H = 1, \dots$ | 50 |  |

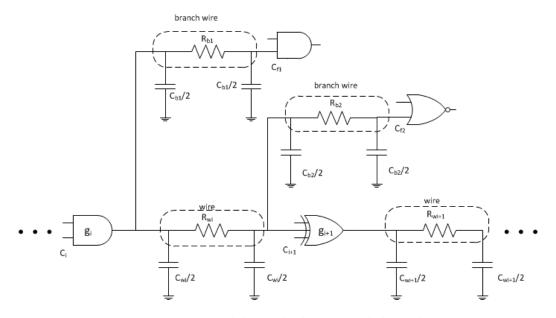

| 5.5 | ULE delay calculation with branching                                                 | 54 |  |

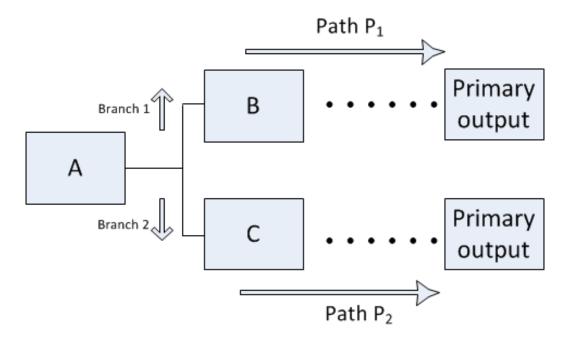

| 6.1 | Load distribution model                                                              | 59 |  |

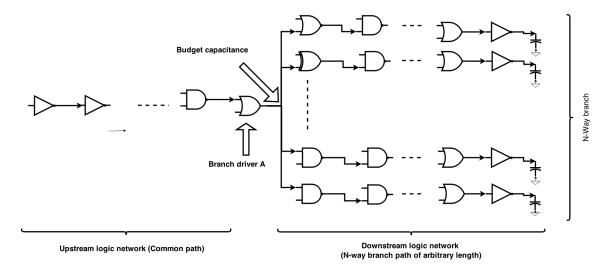

| 6.2 | Practical logic network with arbitrary number of branch fan-out $$ . $$ .            | 61 |  |

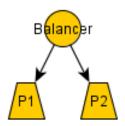

| 6.3 | Single balancer with two logic path $P_1$ and $P_2$                                  | 63 |  |

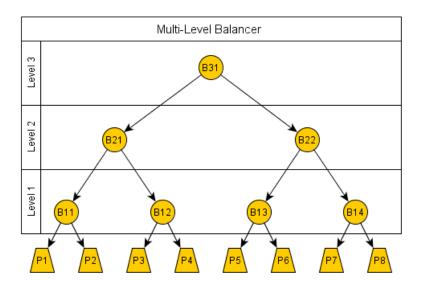

| 6.4 | Hierarchical setup for solving branch with multiple path                             | 64 |  |

| 7.1 | Bounds of 5 point algorithm                                                          | 69 |  |

| 7.2 | Delay vs budget capacitance                                                          | 72 |  |

| 7.3 | Case 1: optimal point lies between point 2, 4                                        | 72 |  |

| 7.4 | Case 2: optimal point lies between point 1, 3                                        | 73 |  |

| 7.5 | Case 3: optimal point lies between point 3, 5                                        | 73 |  |

| 7.6 | Heuristic for solving multi-level branches in practical circuit                      | 74 |  |

| 8.1 | Tool/Algorithm flow for the experiments                                              | 78 |  |

| 8.2 | Test 1 : Sizing logic chain of equal length but different type                       | 81 |  |

| 8.3 | Sizing result of test 1                                                              | 82 |  |

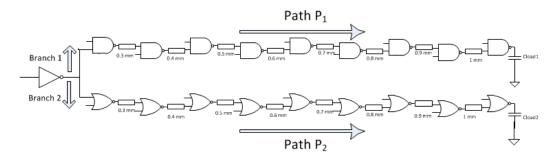

| 8.4 | Test 2: Branch consisting logic path of varying wire length                          | 83 |  |

| 8.5 | Sizing result of test 2                                                              | 84 |  |

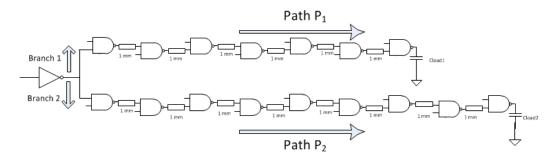

| 8.6 | Test $3$ : Branch consisting logic path of unequal number of gates | 85 |

|-----|--------------------------------------------------------------------|----|

| 8.7 | Sizing result of test 3                                            | 85 |

#### CHAPTER 1

#### Introduction

In modern days, electronics and computer-based products are shaping the way of human life in this planet. In the last 30 years, digital circuit technology has advanced by giant leaps compared to other technologies largely because of scaling of transistors as well as the emergence of different computer aided design tools and algorithms.

Digital circuits are built with logic elements. Logic elements are built with tiny MOSFET (Metal Oxide Semiconductor Field Effect Transistor). Transistors were first invented in 1947 and the MOSFET was invented in 1952. The MOSFET was the first electronic device consisting of three node where the voltage between two nodes can be controlled by the voltage at the third node. The MOSFETs works as a switching device and it is an ideal device to implement switching binary logic.

#### 1.1 Circuit and system design

#### 1.1.1 Design flow

Digital circuit design consists of several stages. The primary few stages deals with optimization and conversion between several different logic level abstraction. These steps are performed in the Front End of the design flow.

In the later stages the actual physical system is implemented on chip by following physical design and verification steps which are collectively called the Back End of design flow.

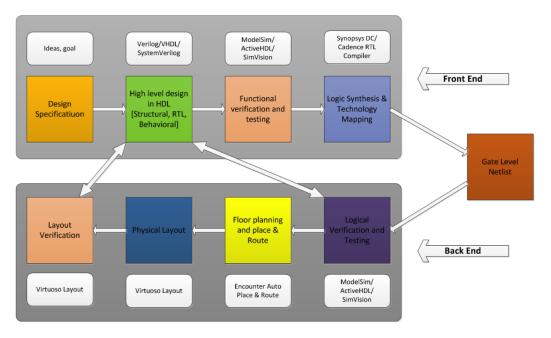

Figure 1.1 shows the basic front End and back End design flow. Digital circuit design starts with the HDL code that describes the logic or netlist of connection. The

Figure 1.1: ASIC design flow

primary HDL code is then optimized with a logic optimizer. In the next stage, the optimized logic is mapped to the standard cells. The output is called the technology-mapped netlist or netlist in short. Netlist is the last abstraction level before building the actual System on Chip(SOC).

In the back end flow, designers do necessary timing analysis and re-adjust timing performance to ensure desired performance. In the next steps, the netlist is placed and routed and large blocks, analog circuit, memory, power rail and IOs are placed with floor-planning. Eventually, full-chip semiconductor layout is produced and sent to fab to manufacture.

#### 1.1.2 Electronic design automation (EDA)

EDA (Electronic Design Automation) tools are a type of software that is used in electronic design. These design tasks are mostly computationally expensive and hence efficient algorithm and data structures are necessary to efficiently model circuit in many different kind of abstraction level. In the old days before CAD tools, integrated

circuits were designed by hand, and manually laid out. In some advance situations layout was generated using geometric software.

CAD algorithms and tools began to emerge during mid 1970s. During this era the Design Automation Conference started its journey and the ground-breaking text on VLSI system was published in 1980 called as "Introduction to VLSI Systems" by Carver Mead and Lynn Conway [3]. This text advocated for design automation using programming language and also showed that chip design pattern consists of a lot of repetitive modular design routines especially in the layout generation part. The logic optimization algorithm evolved thoroughly over the next decades and open more doors for automation.

Historians marks 1981 as the year when commercial EDA tools started their journey. Semiconductor companies like IBM, Hewlett Packard, Intel were the pioneers and later companies like Cadence, Synopsys, Mentor Graphics dedicated themselves only to EDA development.

#### 1.1.3 Motivation for EDA tool design in academia

- VLSI CAD or EDA tools are around since 1970s.

- Many CAD ideas were generated in academia. Modern days well-known EDA developer like Synopsys and Cadence also started their journey in academia.

- To solve many design problems without actually building the physical device.

- With the change in transistor sizes many new design challenges emerge. Need proper modeling of new process technologies and integrate with existing tools.

- To facilitate developing new algorithm techniques to solve new problems.

- To automate design process of physical device used for other research.

#### 1.1.4 Overview of path optimization using gate sizing

Modern digital circuit design usually starts with a circuit model written in a HDL (Hardware Description Language). Then, the circuit model goes through logical optimization and converted to a structural level logic gate network model that is semantically equivalent to the initial behavioral model through technology mapping process. Logical equivalency does not ensure that the circuit will function properly, because each logic element used in the network consists of practical transistors and wires which are immune to several variables such as Process, Voltage, Temperature (PVT) conditions etc. In order to maintain the correct logic levels at each logic gates output and ensure timely signal propagation, designers usually use gate or transistor sizing techniques.

In this dissertation, the author presented some novel techniques to size paths for optimal delay by taking accurate branching effort into consideration. These techniques solves branching in the context of proper load distribution and minimizes delay by balancing each path from input to output. Chapter 5 and Chapter 6 have all the details of these techniques.

#### 1.1.5 Orientation of the thesis

This thesis consists of two major type of work. The first type is implementation of modeling tools and algorithms that model the behavior of the circuit and helps analyze the performance of the circuit under test. The second type of work are the algorithms for path optimization. The rest of dissertation is organized in the following order – Chapter 2 introduces OkCad tools collection. Then in the following chapters the theories and algorithms behind the tool are explained (in Chapter 3, 4). In Chapter 5 the theories of Unified Logical Effort (ULE) is revisited and ULE is used as an aiding tool for path optimization. Chapter 6, 7 give the details of path optimization techniques developed for the work followed by experimental results

(Chapter 9 ) . Finally , Chapter 9 concludes the dissertation.

#### CHAPTER 2

#### Ok CAD tools

#### 2.1 Ok CAD tools

OkCAD tools is a collection of various synthesis, logic optimization and technology mapping tools designed in JAVA. The collection has rich sets of algorithm to carry out the tasks. Moreover, the tools are designed with a object oriented reusable software architecture which provides a lot of flexibility for the end user to explore the existing algorithms and contribute his/her own algorithm and integrate into the system quite easily. In the subsequent sections each tools are described briefly.

#### 2.1.1 Ok CAD tool flow

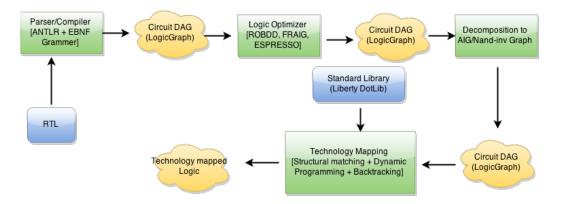

OkCad tool collection consists of several basic tools for modeling and analyzing circuits as shown in figure 2.1. In the heart of OkCad tool is LogicGraph, a package written in Java. LogicGraph is basically a Directed Acyclic Graph (DAG) to represent the circuit schematic in program domain. The designs are imported from Verilog RTL text. An ANTLR based parser is used to parse a subset of Verilog 2001 and convert the HDL text to LogicGraphs.

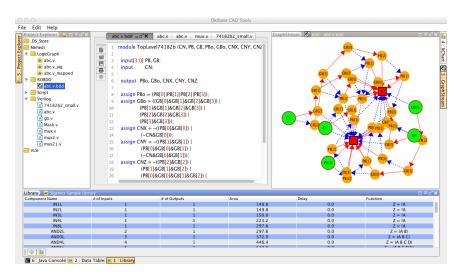

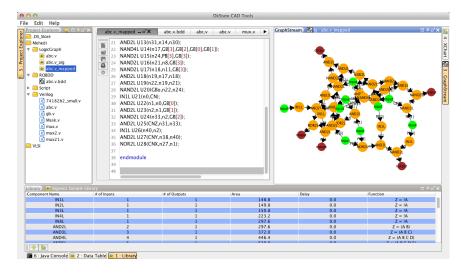

The logic optimizer and equivalence checker is based on Binary Decision Diagram (BDD). A separate independent package was developed for the BDD package. The technology mapping tool is based on structural matching of AIG or Nand-Inv of the subject graph of the circuit and pattern graph from the standard library cell. Figure 2.2 shows a sample ROBDD derived from Verilog HDL and Figure 2.3 shows the technology mapped LogicGraph of the same Verilog.

Figure 2.1: OK CAD tool flow

Figure 2.2: OkCAD tool with generated sample ROBDD

Figure 2.3: OkCAD tools with generated sample LogicGraph

Figure 2.4: ANTLR flow

#### 2.1.2 ANTLR parser generator

ANTLR (ANother Tool for Language Recognition) is a efficient modern parser generator written in Java [4]. The tool takes EBNF (Extended Backus-Naur Form) grammar of a language and generates parser for it in several different target language such as Java, C++, Python, JavaScript, Perl, Objective-C etc.

ANTLR can generate lexer, parser, tree parser, and combined lexer-parser. The generated parser can automatically generate abstract syntax trees which can be further processed with tree parser. Unlike other parser generator ANTLR generates the lexer, parser and tree-parser automatically and generates event-listener classes. This classes are open and can be extended by the client to implement interpreter. The role of the interpreter is to execute some tasks when certain language pattern in detected.

#### 2.1.3 Verilog subset compiler

The compiler is an important and essential tool to build the primary data structure from text form. In past, many kind of text form has been used such as PLA, BLIF, BLIF MV etc. Although those formats are easier to understand they are not sufficient to model real life complex circuits.

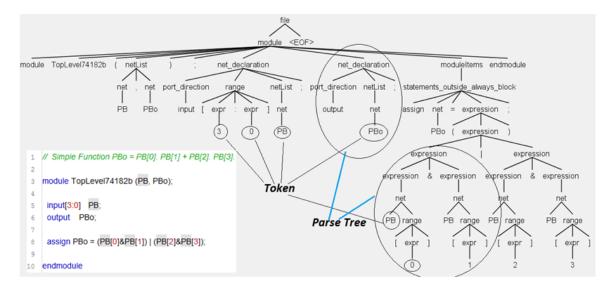

The compiler included in OkCAD is a Verilog subset compiler designed using state of the art ANTLR 4 parser generator [4]. ANTLR 4 is powered by event driven and

Figure 2.5: Verilog parse tree generated by ANTLR 4 based Verilog compiler

listener based architecture which makes it easier to put the target language action code separately. The compiler produces Logic Graphs (discussed later) as output.

Figure 2.5 shows the abstract syntax tree of a small sample of Verilog. Lexing and parsing is performed from left to right and the parse tree is built bottom-up. ANTLR also generates parse tree walker class and also provides listener classes.

Figure 2.5 shows a sample Verilog module and corresponding parse tree produced by the OkCAD Verilog compiler. The major features of the compiler are listed below

- Full RTL / Structural Verilog.

- Partial support for behavioral (if-else, Case etc).

- Implemented Event driven pattern.

- Understands all kinds of Verilog number notations. Example: 4b1100, 16hffff etc.

- Supports array indexing, mathematical expressions.

- Supports all RTL expression maintaining proper precedence.

- Supports module instantiation.

#### 2.1.4 LogicGraph: digital circuit expressed as directed graph

The logic networks are represented using a graph data structure called "Logic Graph" which is basically a directed graph. The vertices represents different logic elements like logic gates, flip-flop and edges represents connecting wires. Both vertices and edges have the expected functional behavior of different logic gates and connecting wires respectively.

The most useful features of Logic Graphs are described below

#### A Features in LogicGraph

- Modeled all primitive logic gates for any input.

- Event-driven simulation model.

- Circuit simulation with event based signal propagation through edges

- Static Timing Analysis (STA)

- Basic placement with simulated annealing (Metropolis algorithm)

#### B Graph algorithms integrated in LogicGraph

- Breadth-first traversal

- Depth-first traversal

- Topological order traversal

- Shortest-path computation

- Longest-path computation

- Cycle detection

#### 2.2 Summary

OK CAD tools is a collection of basic data structures and algorithms to aid in modeling and analyzing circuits. It contains an ANTLR based Verilog compiler to convert Verilog text to graph based data structure. There are separate packages for logic compression, technology mapping and gate placement features. Basically, it is a platform to implement and test new ideas and suitable for academic use. The collection is written entirely in object oriented Java. Hence, it is efficient and platform independent. It is extensively used to conduct most of the research work described in this dissertation.

#### CHAPTER 3

#### Binary decision diagram (BDD)

# 3.1 Logic optimization with reduced ordered binary decision diagram (ROBDD) techniques

OkCAD is equipped with a logic optimizer based on Reduced Ordered Binary Decision Diagram (ROBBD), a data structure that ensures a canonical representation of any logic function for a particular variable order. ROBDD maintains a variable order and hash-based data-structure named unique table to keep track of all the unique subfunctions. Hash-based implementation also ensures fast amortized time for ROBDD operation. in the subsequent the fundamentals of BDD theory and logic optimization is discussed briefly. These theories and ideas are already implemented in the OkCAD BDD package.

#### 3.1.1 History and background

The original idea of Binary Decision Diagram came from Lee (1959) [5] and Akers (1978) [6]. Later in 1986, Randal E Bryant at Carnegie Melon University extended traditional BDD [7]. Bryant represented BDD with a defined variable order and shaped BDD to a strong canonical form. This ordered BDD is called OBDD in short. In the same paper Bryant also showed that by sharing redundant isomorphic subgraph the logic representation can be compressed. His proposed data structure is now called a Reduced Ordered Binary Decision Diagram (ROBDD) [8], [9], a well-defined data structure with strong canonical form. It is proven that two functions are equivalent if and only if , the ROBDD's for each function are isomorphic [9].

In 1992, Brace, Rudell and Bryant [8] improved the notion of ROBDD with complemented edge BDD. A complement edge indicates that the connected formula is to be interpreted as the complement of the ordinary formula. In this way, complemented functions share the same BDD and thus reduces the size of the overall ROBDD.

The Problem with ROBDD is that some function has exponential size ROBDD for one variable order and linear size ROBDD for another variable order. Bolling and Wegener showed that finding optimal variable order is NP-Complete [10]. Variable order can be computed statically [11],[12],[13]. Static variable ordering works well for many combinational functions that come from circuits we actually build but it usually works does not do well for unstructured problems.

Friedman and Supowit found that permuting any top part of the variable order has no effect on the nodes labeled by variables in the bottom part and vice verse [14]. Their work lead to researcher to investigate dynamic variable ordering methods. The most popular method is a heuristic called sifting [15].

Many researcher used BDD for technology mapping for VLSI circuit as general. Among them, some of the techniques were pruned and optimized properly to support FPGA. In this regard the work of Mailhot and De Micheli [16],[17] is worth mentionable for their early work in this field. Later, Lehman et al.[18] used BDD for logic optimization and then converted BDD to AIG network with choice node. Their method of technology mapping takes all the optimization choices into consideration through choice nodes.

#### 3.1.2 Basic concepts

Although the underlying model of the decision diagram already studied by Lee (1959) [5] and Akers (1978) [6], this kind of representation of switching function was not used seriously until 1986. In 1986, by introducing some ingenious ordering restrictions to BDD and providing sophisticated reduction mechanism, R. Bryant [7] substantially

improved the model. Since then ROBDD became a useful data structure to represent switching function with strong canonical form and became useful for robust model checking, validation and technology mapping. These facts have been established by the following variable properties

- ROBDD provides a strong canonical representation of switching function.

- ROBDD can be manipulated efficiently.

- For many practical switching function ROBDD representation are quite small.

- A ROBDD can represent an exponential number of paths with a linear number of nodes.

- On a more abstract level, BDDs can be considered as a compressed representation of sets or relations. Unlike other compressed representations, the actual operations are performed directly on that compressed representation, i.e. without decompression.

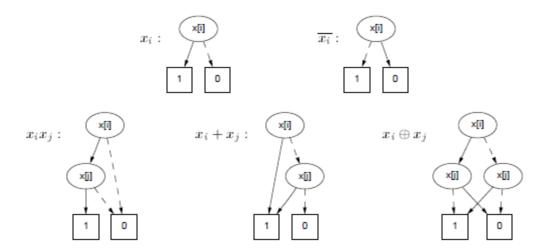

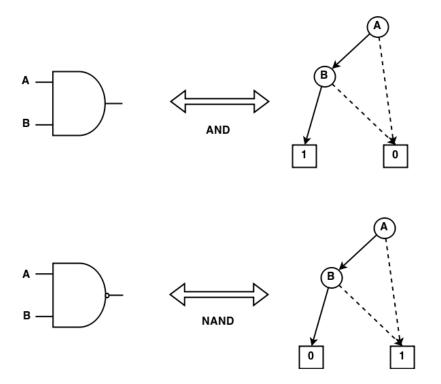

Binary decision Diagram (BDD) is directed acyclic graph, in which each vertices or node represents a Boolean function. Each vertex has one associated variable v. Depending on Boolean value (TRUE or FALSE), the associated function is further decomposed into two sub-functions which are independent of variable v and these sub-functions becomes associated with child nodes of the current node. When v is TRUE the true-child node is chosen and its associated function represents the resultant sub-function. In the same way false child node is chosen when v is false. Thus the variable v gives us a decision. Some ROBDD of basic functions are show in figure 3.1.

#### 3.1.3 Shanon's co-factor

The Shannon expansion theorem is an important idea in Boolean algebra. It paved the way for Binary decision diagrams, Satisfiability solvers, and many other techniques

Figure 3.1: BDD of basic functions

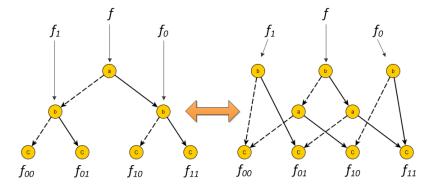

relevant for computer engineering and formal verification of digital circuits. Shanons expansion is the fundamental mathematics of OBDD. Shanon co-factors are used in ITE algorithm to build ROBDD. When OBDD nodes are spitted to child nodes, the Boolean function associated with the node is decomposed and represented as sum of sub-functions of the original. Shanon's co-factors are also important in tautology checking in formal verification. Shanons expansion is expressed in equation 3.1

$$f = x \cdot f_{\bar{x}} + \bar{x} \cdot f_x \tag{3.1}$$

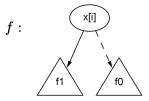

where  $f_x$  and  $f_{\bar{x}}$  are Shanon's positive and negative co-factor respectively. The **positive co-factor** of f with respect to variable x is the sub-function  $f_{x_{i-1}} = f(x_1, ..., x_{i-1}, 1, x_{i+1}, ...x_n)$ . The **negative co-factor** of f with respect to variable x is the sub-function  $f_{x_{i-1}} = f(x_1, ..., x_{i-1}, 0, x_{i+1}, ...x_n)$ . Shanon's expansion is physically expressed in OBDD as in figure 3.2, where  $f_1 = f(x_1, ..., x_{i-1}, 1, x_{i+1}, ...x_n)$  and  $f_0 = f(x_1, ..., x_{i-1}, 0, x_{i+1}, ...x_n)$

#### 3.1.4 ROBDD output function inversion

When a logic function is inverted in logic domain, logic 1 and logic 0 nodes swap in the ROBDD domain. In figure 3.3, ROBDD of AND function and NAND function

Figure 3.2: Shanon's expansion in OBDD

Figure 3.3: ROBDD function inversion

are shown. The only change in the ROBDDs is the logic "1" and logic "0" nodes swapped their places. In other words, all incoming edges towards the logic "1" node is now directed to logic "0" node and vice verse. With this manipulation property it is easy to invert function in ROBDD domain by swapping constant logic nodes.

#### 3.1.5 ROBDD input variable inversion

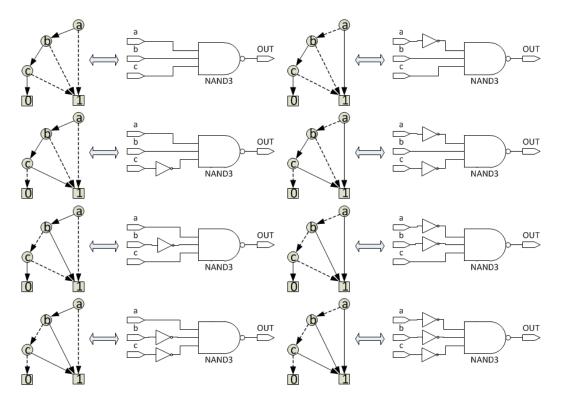

Figure 3.4 shows ROBDD of different flavors of NAND3 functions with inverted and non-inverted inputs a, b and c. It is noticeable that when a input is inverted a transition edges coming out of that corresponding variable's BDD node is also gets

Figure 3.4: ROBDD of different flavors of NAND3function

inverted. For example, in Figure 3.4, the top left ROBDD denotes NAND3 of a,b,c (all of them non-inverted) and in the next ROBDD (2nd row, left) only input c gets inverted. The difference between these two BDD is only in the "c" nodes. In the first ROBDD, c node's true edge goes to logic 1 and false edge goes to logic 0. In the second ROBDD c nodes true edge goes to logic 0 and false edge goes to logic 1. Thus, when inputs gets inverted in logic domain, edges gets inverted in ROBDD domain.

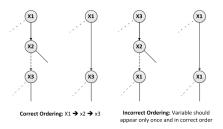

#### 3.1.6 Ordering rules

A BDD with a specific variable order in all path provides strong canonical representation of logic [7], [9]. With a specific order, it is ensured that decision on one particular variable will take place in the same level of nodes. In other words, Any particular level of nodes is functionally independent of their parent level nodes. This property allows all the nodes with same variable, same true-child and same false-child

to be shared. During tautology checking the variables of the two function need to be ordered. Theoretically, two BBD are tautological if and only if they have same variable order and encounter same node functions in any chosen path from root to leaves. The BDD ordering rules are

- No variable appears more than once along a path.

- In all paths variable appear in the same order.

Figure 3.5 shows the ordering rule.

#### 3.1.7 Reduction rules

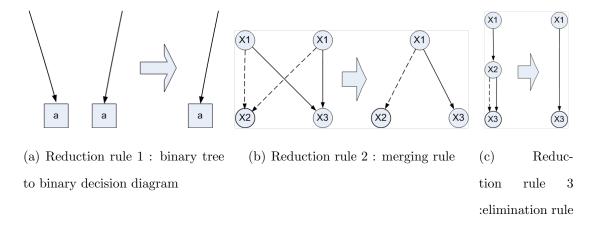

In 1986, Bryant [7] showed that, when BDD is ordered and reduced it offers a strong canonical representation of logic. This form of BDD is called ROBDD which can represent exponential number of paths in linear number of nodes and hence it is useful for synthesis. There are three reduction rules which are discussed below.

#### A Reduction rule #1: elimination of redundant leaves

At first, Boolean function is represented by Truth Table or Binary Decision Tree. The first reduction step is to convert the Binary Decision Tree to OBDD by eliminating all the redundant leaves. OBDD should have only two leaves, a constant 1 and a constant 0. According to the first reduction rule, only one copy of the leaves are kept. All the edges that went to redundant leaves are redirected to the surviving leaves. Figure 3.6(a) shows rule #1.

Figure 3.5: Ordering rule

Figure 3.6: OBDD reduction rules

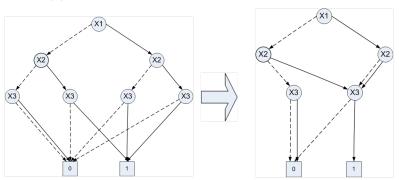

#### B Reduction rule #2: merging rule

If two internal nodes are labeled by the same variable, their true-edges lead to the same node and their false-edges lead to the same node, then one of the two nodes is eliminated and all the incoming edges of the eliminated node is redirected to the remaining one. Figure 3.6(b) shows rule #2, where there were two nodes labeled "X1" pointing to the same X3 nodes through true and false edges. One of the node is eliminated.

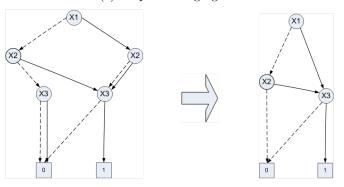

#### C Reduction rule #3: elimination rule

If the true-edge and false-edge of a node v points to the same node u then v is eliminated and all the incoming edges of v is redirected to u. Figure 3.6(c) shows rule # 3, where the true edge and false edge of the X2 node is pointing to the same X3 node. Hence, the X2 node is eliminated.

#### 3.1.8 BDD reduction example

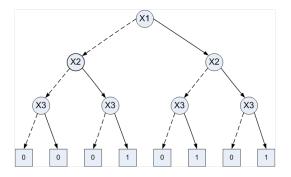

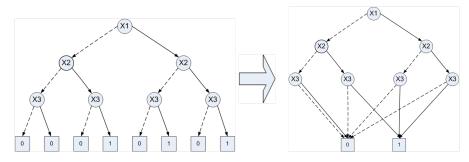

Table 3.1 shows the truth table of a Boolean function and figure 3.7(a) shows the Binary Decision Tree for the same function with a variable order  $X_1 > X_2 > X_3$ . BDD reduction rules are always applied bottom-up. Figure 3.7(b), 3.7(c) and 3.7(d)

| $x_1$ | $x_2$ | $x_3$ | f |

|-------|-------|-------|---|

| 0     | 0     | 0     | 0 |

| 0     | 0     | 1     | 0 |

| 0     | 1     | 0     | 0 |

| 0     | 1     | 1     | 1 |

| 1     | 0     | 0     | 0 |

| 1     | 0     | 1     | 1 |

| 1     | 1     | 0     | 0 |

| 1     | 1     | 1     | 1 |

Table 3.1: Truth table representation of a Boolean function

shows the three reduction steps mentioned above to form ROBDD.

(a) Begin: binary tree of the function of table

3.1

(b) Step 1: binary tree to binary decision diagram

(c) Step 2 : merging rule

(d) Step 3: elimination rule

Figure 3.7: OBDD reduction example  $\,$

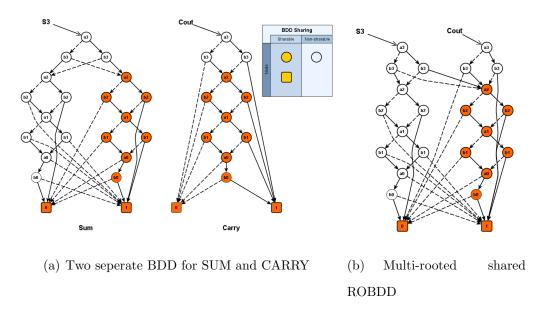

Figure 3.8: ROBDD sharing example

#### 3.1.9 ROBDD manipulation

In traditional commercial Electronic Design Automation (EDA) tools, BDDs are built correctly on the fly. It is better to build it on the fly than to build a bad non-canonical BDD and try to fix it later. The main concept is to create vertices or nodes selectively. With the clever use of a hash table the already created unique nodes are stored and a new node is created if it is not found in the hash table. The hash table is also called a unique table.

In ROBDD if a node is found in the unique table, instead of creating new node the old one is shared. As a result, same node can be shared by multiple parent nodes under same root or multiple roots. Node sharing in ROBBD is the strongest feature of ROBDD. It helps reducing the size of the BDD and in the long run produces optimized circuits with heavily shared resources. For example, in Figure 3.8(a) and Figure 3.8(b) it is shown how BDDs are shared and multi-rooted BDDs are formed.

Figure 3.9: ITE analogy with 2:1 MUX in hardware

#### 3.1.10 ITE algorithm

ITE algorithm is the core algorithm behind ROBDD manipulation. It is inconvenient and inefficient to build a BDD and then order and reduce it. This algorithm helps to incrementally build the ROBDD with correct order and reduction on the fly.

- ITE stands for IF THEN ELSE. In Boolean algebra,  $ITE(F,G,H) = F \cdot G + \bar{F} \cdot H$

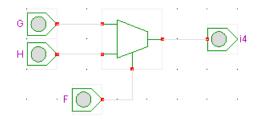

- In hardware ITE can be viewed as 2:1 MUX as shown in figure 3.9. In MUX, signal G is selected when F is logic 1 and signal H is selected when F is logic 0. In comparison, the node variable in ROBDD is analogous to selector signal F, true child is analogous to signal G and false child is analogous to signal H.

- ITE applies Shannon's expansion theorem on the fly when building ROBDD.

- ITE takes three BDD node as I,T and E and performs If Then Else operation on the nodes and ultimately returns another BDD node.

- If the required node is found in unique table. then the found node from unique table is sent. In this way, same node is shared.

- If terminal cases are met, trivial results are sent, otherwise Shannon co-factors are computed and a new node is created in the unique table and that node is sent.

Very useful, as it can be used to implement many other common logic such as AND, OR, NOT etc. Table 3.2 shows a list of common logic function represented in term of *ite* operator.

**algorithm** 1 shows the ITE algorithm and **algorithm** 2 shows the "Find or Create" algorithm used in Unique table.

| Subset     | Expression          | Equivalent ite form  |

|------------|---------------------|----------------------|

| 0          | 0                   | 0                    |

| 1          | 1                   | 1                    |

| f          | f                   | f                    |

| g          | g                   | g                    |

| NOT(f)     | $ar{f}$             | ite(f,0,1)           |

| NOT(g)     | $ar{g}$             | ite(g,0,1)           |

| AND(f,g)   | $f \cdot g$         | ite(f,g,0)           |

| f > g      | $f\cdot ar{g}$      | $ite(f,ar{g},0)$     |

| f < g      | $ar{f}\cdot g$      | ite(f,0,g)           |

| NOR(f,g)   | $ar{f}\cdot ar{g}$  | $ite(f,0,ar{g})$     |

| OR(f,g)    | f+g                 | ite(f,1,g)           |

| $f \ge g$  | $f + \bar{g}$       | $ite(f,1,ar{g})$     |

| $f \leq g$ | $\bar{f} + g$       | ite(f,g,1)           |

| NAND(f,g)  | $\bar{f} + \bar{g}$ | $ite(f, \bar{g}, 1)$ |

| XOR(f,g)   | $f\oplus g$         | $ite(f,ar{g},g)$     |

| XNOR(f,g)  | $far{\oplus}g$      | $ite(f,g,ar{g})$     |

Table 3.2: Boolean functions of two arguments and equivalent representation in terms of the ITE operator

# Algorithm 1: ITE

**input**: Associated variable v, node loson, node hison

output: If the node already exists in the unique table then the pointer to the existing node is returned otherwise a new node is created and stored in unique table and a pointer to the new node is returned

# ITE(node I, node T, node E)

```

begin

```

```

if (terminal case applies to I,T,E) then

| return (immediately computed result for terminal conditions)

end

else if (Computation table has entry (I,T,E)) then

| return (result node from computation table)

end

else

| pick minimum variable x among roots of I,T,E

| PosFactor = ITE (I_x,T_x,E_x)

| NegFactor = ITE (I_{x'},T_{x'},E_{x'})

| R = FindOrCreate(x,PosFactor,NegFactor)

| InsertToComputationTable(hashfunction(I,T,E), address)

| return (R)

end

```

## 3.1.11 Variable ordering

The size of the ROBDD depends on the variable order. And finding optimal variable order is NP-Complete [10]. Some exact variable ordering algorithm gives excellent result but expensive in time. Sometimes complexity becomes exponential, specially for functions that have few symmetric variable. FYI, symmetric variable are those set

## **Algorithm 2:** Find or create

input: Associated variable v, node loson, node hison

output: If the node already exists in the unique table then the pointer to the existing node is returned otherwise a new node is created and stored in unique table and a pointer to the new node is returned

# FindORCreateNode(var v, node loson, node hison)

# begin

```

if (v is actually a constant) then

if (if this constant does not already exist in unique table) then

put this constant in the unique table

return (pointer to constant)

end

end

else if (loson == hison) then

return (loson)

end

else if ((v,loson,hison) node already exists in unique table) then

return (lpointer to (v,loson,hison) node from unique table)

end

else

create new node = (v, loson, hison)

put this node in unique table

return (pointer to this node)

end

end

```

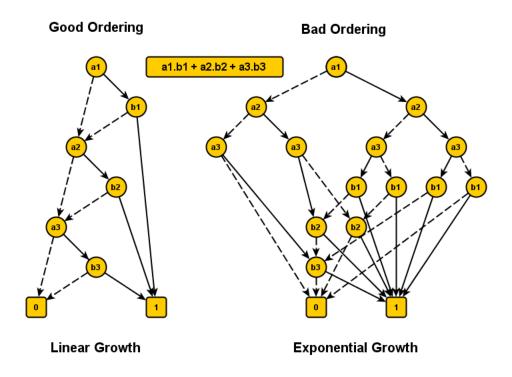

of variable that does not effect other variables or the ROBDD as a whole when they change places among themselves. Figure 3.10 shows a example of variable ordering complexity for good and bad variable order for the function  $a_1 \cdot b_1 + a_2 \cdot b_2 + a_3 \cdot b_3$

Variable ordering algorithms are divided into two classes a) Static and b) Dynamic. In static method, variable order is computed up-front based on the problem structure. It works well for many combinational function that comes from circuits designers build but does not work well for unstructured problems. Thats why, dynamic variable ordering is preferable.

According to the Friedman theorem [14], permuting any top part of the variable order has no effect on the nodes labeled by variables in the bottom part. Permuting any bottom part of the variable order has no effect on the nodes labeled by variables in the top part. In figure 3.11, two adjacent variable layer exchange using Friedman's theorem is shown.

Friedman's theorem is the basis for the sift algorithm, a popular dynamic variable ordering scheme first proposed by Rudell [15]. Later the idea was extended by taking variable symmetry into consideration. This form of dynamic variable sifting is called symmetric sifting and it is investigated by many researchers till today [19], [20], [21],

Figure 3.10: Complexity of variable ordering

Figure 3.11: Adjacent variable exchange in ROBDD

[22].

#### 3.2 OkBDD features

#### 3.2.1 ROBDD data structure

OkBDD uses pointer based BDD nodes. The node is only 16 bit w.r.t 32-bit OS for minimal basic function. There are 4 more Boolean flags (another 4 byte) for graph processing and visualization tasks. There is a BDD manager class called only "BDD" in the core BDD package. All the BDD formation and variable ordering algorithms are associated with the BDD manager to keep the Node data structure lightweight. OkBDD support dynamic variable ordering. The BDD variable can be declared any time during runtime and ordering algorithm can be invoked anytime selectively. There is a general variable ordering algorithm interface declared and user can use their own implementation of algorithm. The OkBDD also implements separate unique tables for each variable to make variable ordering efficient. The variable ordering problem is nothing but a combinatorial optimization problem and the ordering interface provides the facilities to use any other general optimization algorithm framework with minimal effort. That means, user can use 3rd party optimization framework without knowing any details about the ROBDD data structure.

## 3.2.2 GraphStream visualization

OkBDD visualization is based on GraphStream [23], [24] - an open source dynamic graph library that provides an easy way to represent dynamic evolving graph in memory, in GUI and save it as popular graph format files. GraphStream provides a framework to handle the evolution of graphs, that is the changes on values stored on edges and nodes of a graph during time and also the "topology" changes of the graph that is the addition, removal and modification of nodes and edges during time. As GraphStream can handle graph evolution, graphs are defined as a "flow of graph events", instead of only a set of nodes, edges and eventually sets of values associated to node and edges. Dynamic graphs events tells when a node, edge or associated value appears, changes and disappears. GraphStream provides the ideal model, view , controller paradigm (MVC). Here, the model is the ROBDD data structure, the view is the visualization which runs on a separate thread and follows the evolving model accurately. Controllers are separate Java classes that initiates the communication between the model and view. Apart from visualization, GraphStream also provides the facilities to save the ROBDD graphs as popular graph formats such as Dot, GraphML, GML, TLP, NET, GEXF etc which allows the graphs to be analyzed by other Graph processing and analysis tools.

## 3.3 Comparison and analysis

ROBDD formation and manipulation of ROBDD is memory and computation intensive task. ROBDD operations create large amount of intermediate data, performs hashing function frequently. Specially, memory management and garbage collection is vital for processing ROBDDs in machine with limited memory. Most of the BDD packages came out in 1995 to 2000 and at that time memory size was a huge concern. Cache misses and page faults were frequent and degraded the performance and decreased the usefulness of BDD packages. In modern days, memory size requirement

is not a great issue but better memory access and utilization of spatial and temporal locality will still boost-up performance. In summary, raw performance depends on memory size, memory hierarchy and even OS. Also, many packages are not exhaustive in their implementation and thus they remain lightweight. On the other hand, packages like CUDD[25], CMU[26] offers more advanced functionality. In short, comparing different packages only by raw performance and completion time measurement is misleading.

In 2003, Janssen from IBM TJ Watson Research center published a through report on 13 BDD packages at that time [2]. In his own words, he investigated underlying algorithmic and data structure principles that are at the core of each package's implementation and tried to relate the strength of various BDD packages with respect to their usefulness in serious applications. Table 3.4 is adapted from Janssen's paper which shows how the packages faired with respect to the different criteria. We entered our BDD package as the 14th entry in the table and compared according to the same measures that were used for the previous 13 packages. Table 3.3 elaborates all the measurement keys used in Table 3.4. It is worth to mention that, BDD node size can be squeezed to as little as 8 byte but it will decrease the capacity of handling nodes and variables as shown in the case of ABCD and StaticBDD. As OkBDD node uses pointer-based referencing, the node size is expected to increase in 64 bit machines. The authors wanted to extend the functionality of the package in future with bidecomposition algorithms and functionalities, cube manipulation and logic synthesis oriented architecture.

## 3.4 Summary

Binary decision diagram is a powerful data structure to manipulate Boolean logic.

BDDs are frequently used for logic minimization and equivalence checking. In industry, BDDs are used in logic minimization, formal verification and test pattern

| Key       | Description                                             |

|-----------|---------------------------------------------------------|

| Package   | Name of the package                                     |

| Lang.     | Programming language used                               |

| Т         | Integer indices (I) or Pointer (P) based parent-sibling |

|           | relationship                                            |

| R         | Depth-first traversal(D) / Breadth-first traversal(B)   |

| M         | Presence of BDD manager                                 |

| $N_{max}$ | Max nodes that can be allocated assuming infinite mem-  |

|           | ory                                                     |

| Size      | A single BDD node size for basic function               |

| 64        | Indicates whether the node size will increase if ported |

|           | to 64 bit system                                        |

| $V_{max}$ | Max number of variables disregarding machine resources  |

| P         | Indicates whether nodes are kept in separate unique ta- |

|           | bles per variable                                       |

| GC        | Garbage collection scheme                               |

| CT        | Single (S) / Multiple (M) compute table                 |

| DVO       | Dynamic variable algorithm supported or not             |

| Year      | Year of first release                                   |

Table 3.3: Measures for Table 3.4

generation. Its unique ability to represent logic in canonical form and representing exponential amount of information in linear space made it a popular choice for both industry and academia.

| Package          | Lang. | T | R | M | $N_{max}$       | Size     | 64 | $V_{max}$ | Ь | GC                       | CT       | DVO | Year |

|------------------|-------|---|---|---|-----------------|----------|----|-----------|---|--------------------------|----------|-----|------|

| ABCD 0.3         | Э     | Ι | D | Y | $2^{25}$        | $\infty$ | ı  | $2^{10}$  | Z | $\overline{\mathrm{MS}}$ | $\infty$ | N   | 1997 |

| Alliance 5.0     | C     | Ь | D | Y | 228             | 16       | Y  | 216       | 7 | MS/RC16                  | $\infty$ | Y   | 1996 |

| BuDDy 1.9        | C/C++ | Ι | D | Z | 232             | 20       | Z  | $2^{21}$  | Z | MS                       | M        | Y   | 1996 |

| CAL (VIS)        | C     | Ь | В | Y | 228             | 16       | Y  | 216       | 7 | RC8                      | $\infty$ | Y   | 1994 |

| CMU (VIS)        | C     | Ь | D | > | 2 <sup>29</sup> | 16       | Y  | 216       | 7 | RC8                      | $\infty$ | Y   | 1993 |

| CUDD 2.31        | C/C++ | Ь | D | Y | 228             | 16       | Y  | 216       | Z | RC16                     | $\infty$ | Y   | 1995 |

| EST led          | Э     | Ь | D | N | $2^{32}$        | 36       | Υ  | $2^{32}$  | N | RC32                     | M        | N   | 2000 |

| $_{ m IBM}$      | C     | Ι | D | Y | $2^{30}$        | 16       | Z  | $2^{24}$  | Z | $\overline{\mathrm{MS}}$ | $\infty$ | Y   | 1999 |

| MONA             | С     | Ι | D | Y | $2^{24}$        | 16       | N  | $2^{16}$  | N | $\overline{\mathrm{MS}}$ | M        | N   | 1997 |

| PDT              | C     | Ι | D | Z | $2^{31}$        | 24       | Z  | $2^{16}$  | Z | $\overline{\mathrm{MS}}$ | M        | N   | 1993 |

| StaticBDD 1.0    | C++   | Ι | D | N | $2^{23}$        | 8        | N  | 29        | N | $\overline{\mathrm{MS}}$ | S        | N   | 1999 |

| ${ m TiGeR}~3.0$ | C     | Р | D | Y | $2^{30}$        | 16       | Y  | $2^{16}$  | Y | RC16                     | M        | Y   | 1994 |

| TUDD             | C     | Ι | D | Y | $2^{30}$        | 20       | Z  | $2^{16}$  | Y | RC16                     | $\infty$ | Y   | 1998 |

| OkBDD            | JAVA  | Ь | D | Y | 2 <sup>31</sup> | 16       | Y  | $2^{31}$  | Y | MS                       | S        | Y   | 2012 |

Table 3.4: Comparison of BDD packages adapted from Janssen's paper [2]

#### CHAPTER 4

# Technology mapping

# 4.1 The technology mapping problem

The technology mapping problem is in general a combinatorial optimization problem with the goal of optimally transform a technology independent Boolean logic into physical logic elements available through one particular technology.

In general the problem is defined as: given a set of gates L, called the library, and a Boolean network G, let M be the set of Boolean networks constructed using gates from L that are functionally equivalent to G. In this scenario, M is called the mapped networks. The goal of mapping is to find a optimal mapped network that minimizes some objective such as area. delay etc subject to certain constraints such as timing.

The general theory is applicable to both standard cells and look-up table (LUT) based FPGAs. (A look-up table with k inputs, called a k-LUT is a configurable gate that can implement any Boolean function of k variables.)

## 4.2 History and background

In the general terms, the mapping problem is intractable since it is hard to enumerate either implicitly or explicitly the elements of M that optimizes the desired goal. The first most significant algorithm was proposed by Keutzer [27]. He proposed a significant simplification of the mapping problem by restricting the set of mapped networks considered during mapping to be those networks that are structurally similar to [27]. As this approach depends on structural matching of network, this approach is defined

as structural matching approach.

The main idea behind the structural mapping algorithm is a simple one. It is assumed that the original Boolean network G already has a good structure. Mapping is then done by a process of local re-writing. In this process, a single output subnetwork N of G is identified that is functionally equivalent to a gate g in L and replace N by g.

The problem is, there are many ways to do this re-writing and finding the optimal re-writing in polynomial time is tricky. Keutzer proved that for certain classes of networks (trees) and for certain cost functions (delay in the constant-delay timing model and area) it is possible to compute the optimally mapped network by a dynamic programming algorithm.

For this to work, it is assumed that G has a good structure for the final network. This is ensured by applying technology independent logic synthesis algorithms before the technology mapping steps to the initial Boolean network entered by the circuit designer to obtain G. Structural mapping is not expected to significantly change the network structure of G, but merely to convert it in to a similar network built from gates in L.

In Keutzers original work [27], the subject graph is first partitioned in to a forest of trees. Each library gate is decomposed in to a tree of two input and gates and inverters. These trees are called pattern graphs. A multi-input gate may lead to multiple pattern graphs since the decomposition is not unique. A pattern graph (and thereby an equivalent library gate) is matched at a node n by checking for structural isomorphism using a tree matching algorithm.

Richard Rudell extended tree matching algorithm to the case where the pattern graphs could be leaf DAGs [28]. This allowed non-tree gates such as multiplexers and xors to be matched. He also observed that by replacing every wire in the subject graph by a pair of inverters, and by adding a wire gate to the library (whose pattern

consists of a pair of inverters in series), the set of matches is larger.

A radically new method to reduce structural bias was proposed by Lehman et al. [18]. They observed that there are many different ways in which a subject graph can be derived from a Boolean network. For example, a multi-input AND can be decomposed in to a tree of 2-input AND gates in a variety of ways. However, in the mapping algorithm described above, a decision has to be made a priori as to which decomposition is to be used to generate the subject graph. Thus, certain matches that would have been detected with a different decomposition are no longer detected.

A different approach was inspired by a solution in the FPGA domain. Kukimoto extended the set of matches explored at a node by using a general DAG matching procedure instead of tree matching [29]. Thus both the subject graph and the pattern graphs are allowed to be general DAGs in Kukimotos extension. This significantly increases the number of matches found at a node, especially when partitioning the subject graph into a forest of trees would lead to many small trees which eventually will result in many local optima but will be globally sub-optimal.

Mailhot and De Micheli initiated a different line of research with their proposal for Boolean matching [30]. Keutzers work [27] (and later in Lehman et al. [18] and Kukimoto [29]) the actual process of matching a gate (or more precisely, its pattern graph) with a sub-graph H rooted at a node n is through graph isomorphism. Since a library gate, especially complex gates, have many possible decompositions into pattern graphs, only a subset of all possible decompositions is used in practice. Now if the sub-graph of the subject graph is not structurally identical to any one of the decompositions of the library gate, a match may not be found, even though replacing the H by the gate is valid. One can think of this as being a more local structural bias as opposed to the global bias that we were so far concerned with.

Boolean matching addresses local structural bias by directly matching a gate with the sub-graph H by comparing their Boolean functions. Thus, with Boolean matching there is no need for pattern graphs.

Kravets and Sakallah advanced their research in the line of constructive synthesis algorithm proposed by [31] and subsequently improved by Mishchenko et al. [32]. In these algorithms, the structure of the subject graph is not used at all instead the subject graph is used to construct a representation of the Boolean functions (using BDDs or truth-tables), and then a decomposition algorithm is applied to the functions to obtain the mapped network. At first, this may seem like the answer to our original technology mapping formulation. However, the chief conceptual drawback of these algorithms is that they are committed to a specific decomposition scheme. Thus they are not able to explore the full space of mapped solutions, i.e. M. Therefore, they just introduce a structural bias of a different kind.

In FPGA mapping, local structural bias is not a problem since a k-LUT can implement any function of k variables or less. The main challenge is to enumerate the possible different sub-networks rooted at a node n in the subject graph that is implementable by a k-LUT.

Cong and Ding presented a network flow based algorithm Flowmap that can identify a single sub-network rooted at a node n that minimizes depth [33]. The limitation of Flowmap is, it produces only one cut that minimizes depth. However, the network flow based method that it uses to find the cut cannot be extended easily to handle other cost functions. Cong and Ding explored further techniques to enumerate all cuts [34]. This work was later improved by Pan and Lin who presented an elegant algorithm to enumerate all cuts [35]. It is worth mentionable that Chen and Cong adapted the algorithm proposed by Lehman et al [18] for FPGA mapping [36].

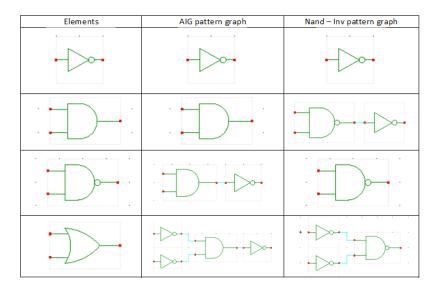

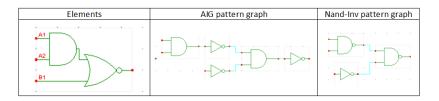

Figure 4.1: Pattern graph of different logic elements of a typical standard library

# 4.3 Technology mapping using structural hashing and dynamic programming

Technology mapping is the process of mapping logic independent circuit to technology dependent circuit using resources available in the standard library. The idea is to represent each logic elements in standard cell library with base function which will produce circuit graph with base elements. This graphs are called pattern graphs. The technology independent circuit is also represented by the same base function and the resultant graph is called subject graph. In the last crucial stage, pattern graphs are structurally matched with sub-graphs of subject graph. Subsequently, the matched portion of subject graph is replaced with corresponding standard cell of the matched pattern graph. Generally, there are multiple choices for matches and the best overall match is found by dynamic programming based algorithm and appropriate cost model. The cost model can be function of one or combination of more than one factor such as delay, area, power etc.

Figure 4.2: Asymmetric pattern graph example

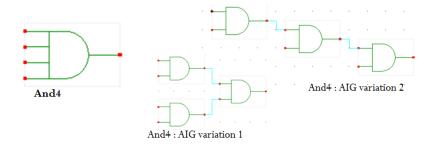

Figure 4.3: AIG pattern variation of 4-input AND gate

## 4.3.1 Base function and pattern graph

The base function is the smallest subsets to represent circuit. Two types of base functions are most frequently used namely 1) Inverter and 2-input AND 2) Inverter and 2-input NAND. They produce AIG (AND-Invert Graph) and NAND2-Invert pattern graphs respectively. Figure 4.1 shows an example of a typical standard cell library and pattern graphs. The pattern graphs of Figure 4.1 are symmetric ie, any path from primary input to primary output traverse through the same kind of elements. Figure 4.2 shows an example of asymmetric pattern graph. Asymmetric pattern graph has different structure when input orders are changed and hence all different pattern should be tried in the matching algorithm. The logic gates with more than 3-input usually have different pattern graph structures. For example, 4-input AND gate can have two different structure as shown in figure 4.3.

# Algorithm 3: Pattern matching

```

input : Subject Graph Node *subject, Pattern Graph Node *pattern

output: Subject Graph Node *matchedNode

Match(node subject, node pattern)

begin

if (NodeType(pattern) == INPUT) then

return matchedNode

end

else if (subject == Leaf \ of \ Subject \ Graph) then

return null

end

else if (NodeType(pattern) != NodeType(subject)) then

| return null

end

else if (NodeType(pattern) != NOT) then

return Match((child(subject), child(pattern)))

end

else

return Match(left(subject), left(pattern)) && Match

(right(subject),right(pattern)) ||

Match

(left(subject), right(pattern)) \&\& Match(right(subject), left(pattern))

end

```

# 4.3.2 Structural hashing and pattern matching

end

Algorithm 3 shows the pattern matching algorithm implemented in OkCAD. The matching criteria is described below

- Pattern graph's leaf (Input) matches anything in subject graph

- Pattern graph's Inverter matches inverter in subject graph

- Pattern graph's And2/Nand2 matches And2/Nand2 in subject graph

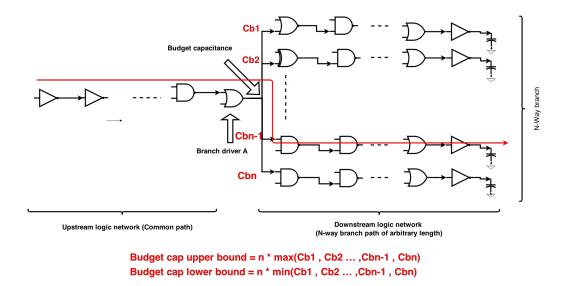

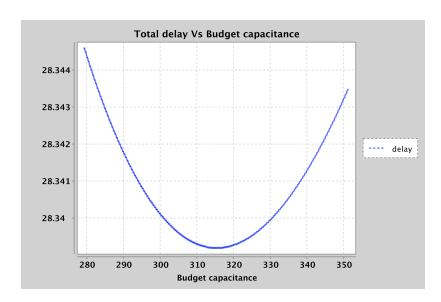

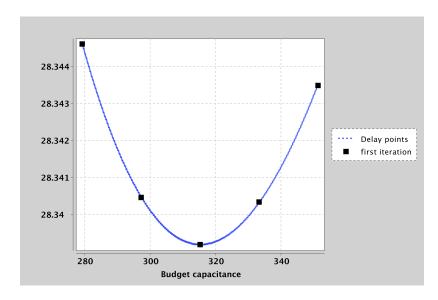

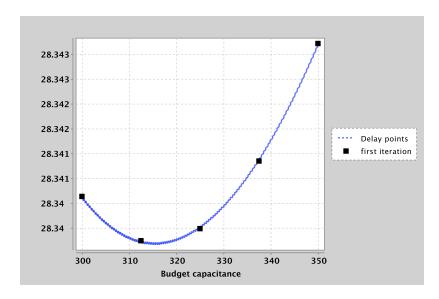

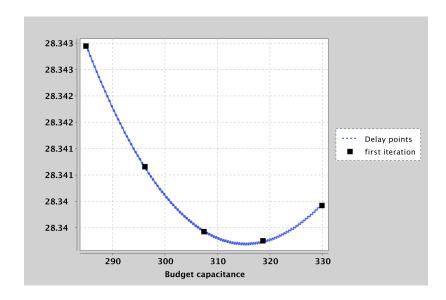

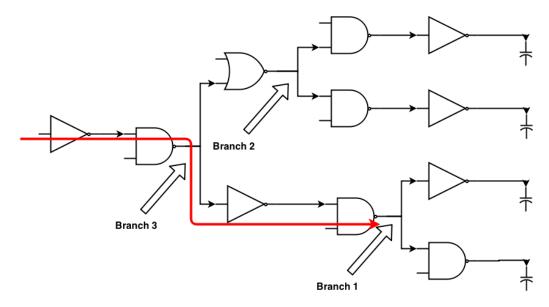

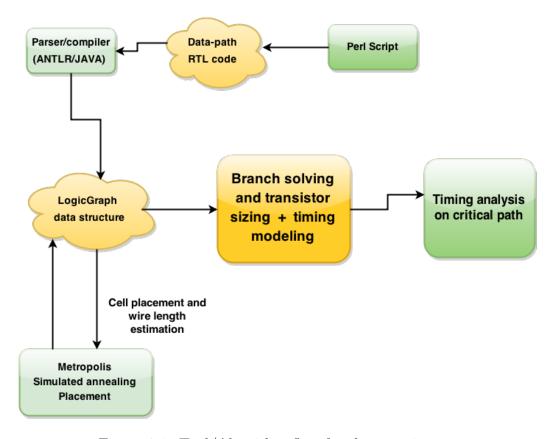

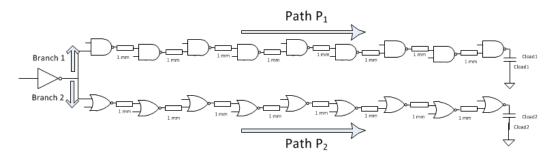

## 4.3.3 Optimal covering with dynamic programming