# UNIVERSITY OF OKLAHOMA GRADUATE COLLEGE

# REAL-TIME ADAPTIVE PULSE COMPRESSION ON RECONFIGURABLE, ${\tt SYSTEM-ON-CHIP} \ ({\tt SOC}) \ {\tt PLATFORMS}$

#### A DISSERTATION

SUBMITTED TO THE GRADUATE FACULTY

in partial fulfillment of the requirements for the

Degree of

DOCTOR OF PHILOSOPHY

By

HERNAN SUAREZ Norman, Oklahoma 2015

# REAL-TIME ADAPTIVE PULSE COMPRESSION ON RECONFIGURABLE, SYSTEM-ON-CHIP (SOC) PLATFORMS

# A DISSERTATION APPROVED FOR THE SCHOOL OF ELECTRICAL AND COMPUTER ENGINEERING

BY

Dr. Yan Zhang, Chair

Dr. Sesh Commuri

Dr. Caleb Fulton

Dr. Boon-Leng Cheong

Dr. John Dyer

Dr. John Albert

## Acknowledgements

I would like to gratefully thank my advisor, Dr. Yan Zhang, for his guidance, support, and constant encouragement during my graduate study at University of Oklahoma.

My gratitude to my doctoral committee: Dr. Sesh Commuri, Dr. Caleb Fulton, Dr. Boon-Leng Cheong, Dr. John Dyer, and Dr. John Albert for their valuable comments, suggestions and corrections.

In addition, I would like to extend my thanks to the Advanced Radar Research Center (ARRC), its director Dr. Robert Palmer, faculty, staff and students, for their generous assistance during my research at OU.

Last but not least, I would like to thank my parents, Ramon Suarez Castro and Graciela Montalvo de Suarez; and my brothers Antonio, Anibal and Nicolas, for their endless support and encouragement.

# **Table of Contents**

| Acknowledge   | ements                                                     | iv                 |

|---------------|------------------------------------------------------------|--------------------|

| Table of Con  | tents                                                      | V                  |

| List of Table | S                                                          | vii                |

| List of Figur | es                                                         | ix                 |

| Abstract      |                                                            | xii                |

| Chapter 1     | Introduction                                               | 1                  |

| 1.1<br>Radar  | Expectations of High-Performance Embedded Computing (HPI 4 | EC) in             |

| 1.2           | Overview of Real-Time Signal Processing Technologies       | 6                  |

| 1.3           | Current State of FPGA Technology                           | 9<br>14            |

| 1.4           | System on a Chip (SoC)  1.4.1 Introduction                 | 16<br>20<br>nology |

| 1.5           | Dissertation Outline                                       | 24                 |

| Chapter 2     | Adaptive Pulse Compression (APC) and Implementations       | 26                 |

| 2.1           | Pulse Compression Waveforms                                | 28                 |

|        | 2.2            | Adaptive Pulse Compression Algorithms                                                                          | 33               |

|--------|----------------|----------------------------------------------------------------------------------------------------------------|------------------|

|        | 2.3<br>Algori  | Real-Time Computational Load Requirements of Pulse Compressions                                                |                  |

|        | 2.4            | State of the Art of Pulse Compression Implementations                                                          | 41               |

|        | 2.5            | Basic Considerations for Hardware Implementation                                                               |                  |

| Chapte | er 3           | FPGA Cores for Radar Signal Processing                                                                         | 47               |

|        | 3.1            | Optimized Adder and Multiplier Designs                                                                         | 47               |

|        | 3.2            | Matrix Multiplication                                                                                          | 55               |

|        | 3.3            | Matrix Inversion                                                                                               | 63               |

| Chapte | er 4           | FPGA implementation of Pulse Compression                                                                       | 69               |

|        | 4.1            | Hardware Implementation of Pulse Compression 4.1.1 FPGA in Existing SDR platforms 4.1.2 Radar TR Control Layer | 69               |

|        | 4.2<br>Circuit | Architecture Design and Analysis for Real-Time Pulse Compressity                                               |                  |

|        | 4.3            | FPGA Device Implementations of Real-Time Pulse Compression 4.3.1 Hardware Resource Utilization                 | 78               |

|        | 4.4            | Experiment Results                                                                                             | 83<br>86<br>ning |

|        | 4.5            | Conclusions                                                                                                    | 89               |

| Chapte | er 5           | SoC Implementation of an Adaptive Radar Processor                                                              | <b>9</b> 1       |

|        | 5.1            | Literature Review: Implementation of Traditional Adaptive Filters                                              | 93               |

|        | 5.2            | System-on-Chip (SoC) Implementation of APC                                                                     | 95               |

| 5.3          | LS-APC Multi-Coprocessor Architecture                 | 96  |

|--------------|-------------------------------------------------------|-----|

| 5.4          | Single LS-APC Processor                               | 100 |

| 5.5          | LS implementation based on Floating-Point Data Format | 102 |

| 5.6          | RMMSE-APC Co-Processor Architecture                   | 109 |

| 5.7          | Summary                                               | 119 |

| Chapter 6    | Conclusions                                           | 120 |

| 6.1          | Achievements                                          | 120 |

| 6.2          | Future Work                                           | 123 |

| Bibliography | <i>y</i>                                              | 129 |

| Annendix - I | ist Of Acronyms and Abbreviations                     | 141 |

# **List of Tables**

| Table 1-1: List of Xilinx FPGA families and principal characteristics              |

|------------------------------------------------------------------------------------|

| Table 1-2: Principal Specifications of Altera FPGA Families                        |

| Table 2-1: Binary Barker Codes                                                     |

| Table 2-2: Comparison of different APC algorithms                                  |

| Table 2-3: Computational cost of APC algorithms per stage                          |

| Table 3-1: Hardware utilization for floating-point and fixed-point of matrix       |

| multiplication59                                                                   |

| Table 3-2: Hardware resource utilization for a pipelined design61                  |

| Table 3-3: Hardware resource utilization when pipelining and distributed memory    |

| are considered in the design                                                       |

| Table 3-4: Hardware utilization for floating-point and fixed-point of matrix       |

| inversion65                                                                        |

| Table 3-5: Comparison of hardware utilization for floating-point and fixed-point   |

| implementation of matrix inversion67                                               |

| Table 3-6: Comparison of timing results for floating-point and fixed-point         |

| implementation of matrix inversion                                                 |

| Table 4-1: Device Resource Utilization for two Xilinx FPGAs for the typical        |

| matched filter implementation.                                                     |

| Table 4-2: Power consumption of pulse compression                                  |

| Table 5-1: Total hardware resources for the matrix multiplication and matrix       |

| inversion98                                                                        |

| Table 5-2: Total hardware resources for pipelined version of matrix multiplication |

| and matrix inversion                                                               |

| Table 5-3: Hardware utilization of LS fixed-point implementation using 16-bit      |

| fixed-point format for Xilinx XC7k325t FPGA101                                     |

| Table 5-4: Hardware utilization of LS fixed-point implementation using 32-bit      |

| fixed-point format for Xilinx XC7k325t FPGA101                                     |

| Table 5-5: FPGA resource utilization for floating-point implementation             |

| Table 5-6: FPGA hardware resource utilization for pipelined floating point         |

| implementation                                                                     |

| Table 5-7: FPGA hardware resource utilization for initiation interval of 50 clock  |

| cycles106                                                                          |

| Table 5-8: RMMSE coprocessor synthesis results                                     |

| Table 5-9: Hardware resources for partially pipelined version of RMMSE             |

| coprocessor                                                                        |

| Table 5-10: Hardware Resources for fully pipelined RMMSE coprocessor115            |

# **List of Figures**

| Figure 1-1: Typical functions of a radar receiver.                                                | 4    |

|---------------------------------------------------------------------------------------------------|------|

| Figure 1-2: Computation load for an example GMTI radar [12]                                       | 6    |

| Figure 1-3: Processing technologies classification                                                | 7    |

| Figure 1-4: Comparison of different technologies for DSP implementation                           | 8    |

| Figure 1-5: Xilinx's DSP48E1 architecture [16]                                                    | 13   |

| Figure 1-6: Xilinx's carry logic slice architecture [18]                                          | 14   |

| Figure 1-7: Traditional FPGA design flow.                                                         | 15   |

| Figure 1-8: Basic concept of a generic SoC architecture.                                          | 17   |

| Figure 1-9: Block diagrams of a Xilinx MicroBlaze Processor [30] and an Al                        | tera |

| Nios II Processor [31]                                                                            |      |

| Figure 1-10: General SoC system implementation model                                              | 20   |

| Figure 1-11: Hardware/software partitioning                                                       | 21   |

| Figure 1-12: Top-level AXI interconnect [32].                                                     |      |

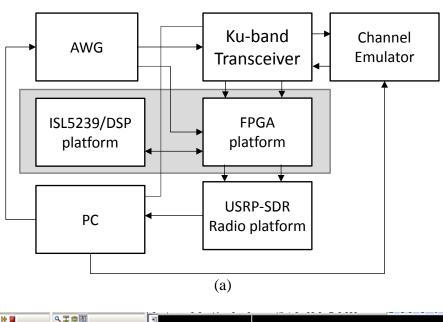

| Figure 1-13: Testbed for the implementation of APC. It includes a Ku-b                            |      |

| transceiver, (a) Kintex-7 and (b) Avnet ZedBoard evaluation boards                                | 24   |

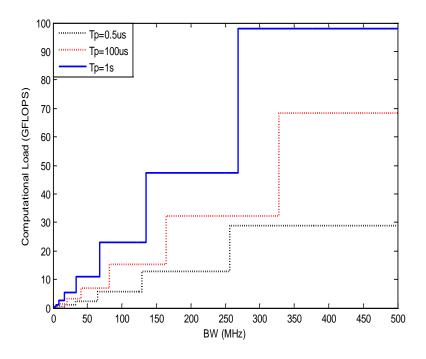

| Figure 2-1: Estimation of computational load requirement for real-time matc                       |      |

| filter pulse compressor, with different signal bandwidths and pulse len                           | _    |

| Assuming 20% transmitter duty cycle for all cases                                                 |      |

| Figure 2-2: Computational analysis of APC algorithms                                              |      |

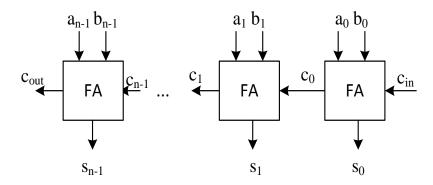

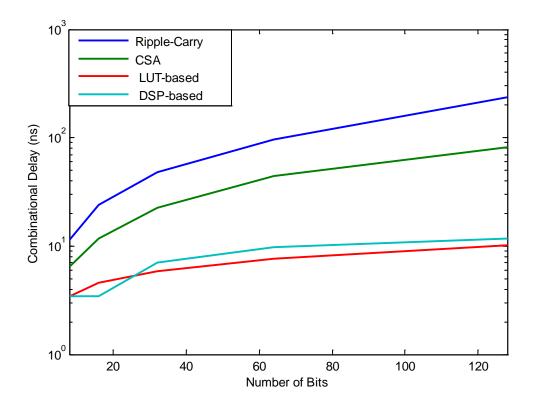

| Figure 3-1: Operation of a conventional <i>n</i> -bit ripple carry adder                          |      |

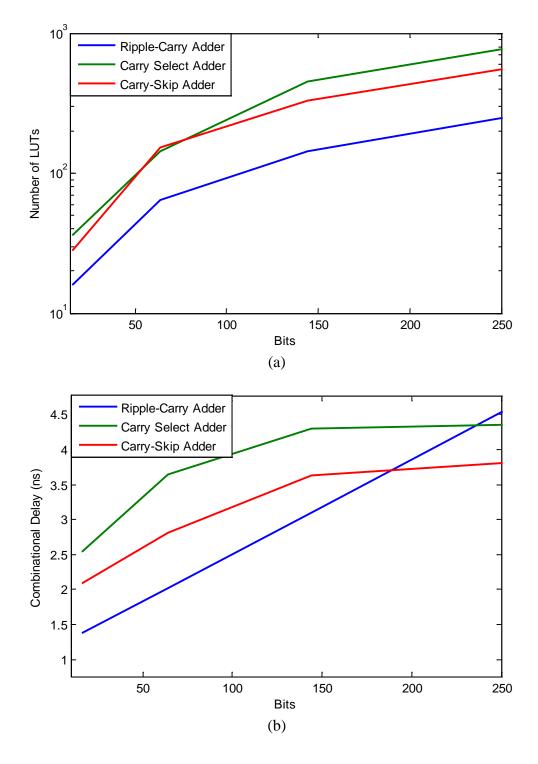

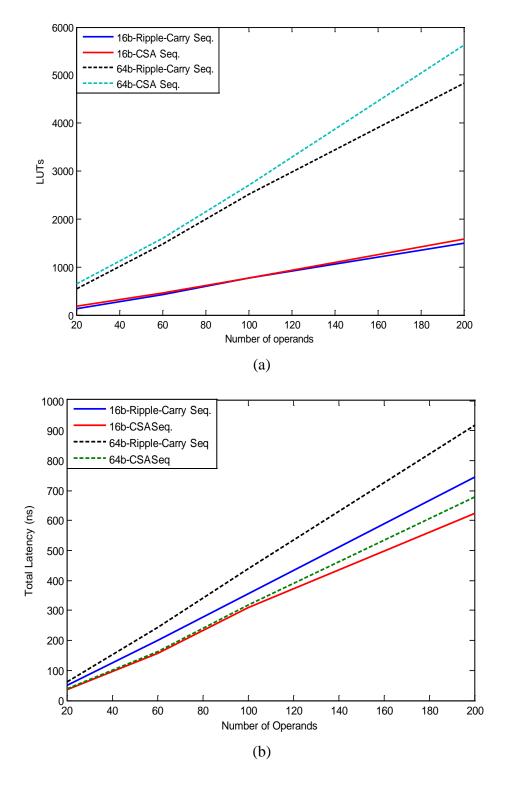

| Figure 3-2: Performance of two-operand adders using different implementations                     |      |

| a Kintex-7 FPGA (xc7k325t-2-ffg900). (a) Number of LUTs,                                          |      |

| Combinational Delay.                                                                              |      |

| Figure 3-3: Performance of sequential multi-operand adders for 16 and 64                          |      |

| operands on a Kintex-7 FPGA                                                                       |      |

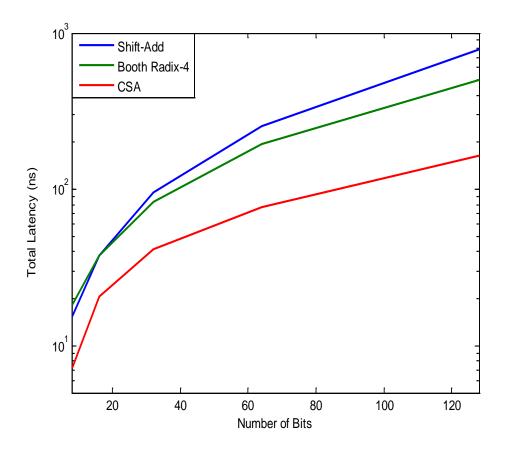

| Figure 3-4: Comparison of latency performance of three sequential multiple                        |      |

| through implementation on Kintex-7 FPGA.                                                          |      |

| Figure 3-5: Comparison of combinational delay performance of different para                       |      |

| multipliers including designs using Xilinx commercial building blocks                             |      |

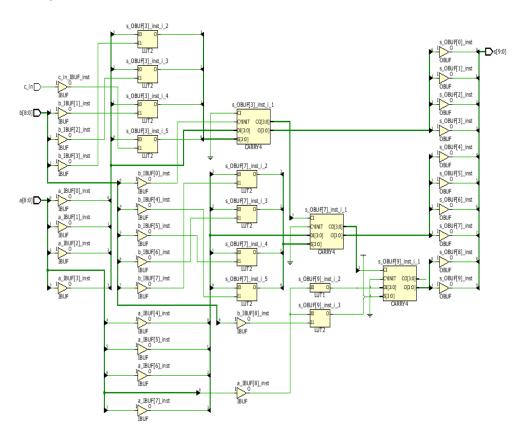

| Figure 3-6: Schematic for an 8-bit 2's complement adder on Kintex-7 FPGA                          |      |

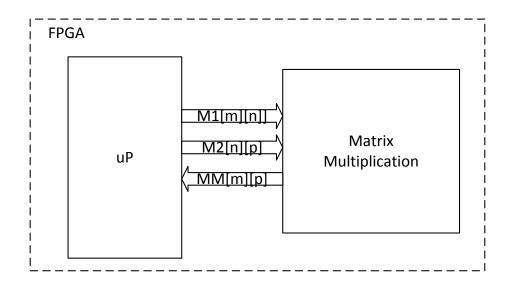

| Figure 3-7: High-level configuration of matrix multiplication coprocessor                         |      |

| Figure 3-8: Matrix multiplication results from MicroBlaze with and with                           |      |

| coprocessor on Kinte-7 FPGA. Latency measured with a timer attached to                            |      |

| AXI Lite bus. (a) 4x4 matrix multiplication. (b) 8x8 matrix multiplication                        |      |

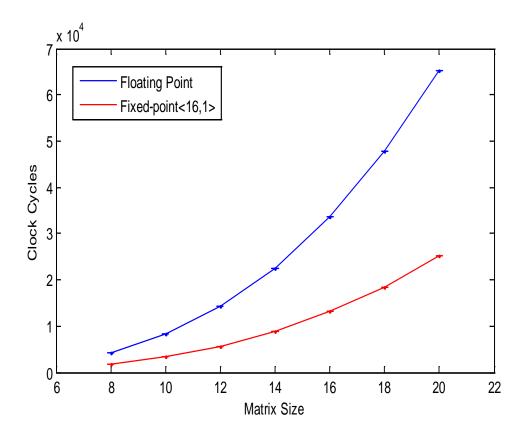

| Figure 3-9: Matrix multiplication total latency for floating point and fixed-point implementation |      |

| mpicmentation                                                                                     | 00   |

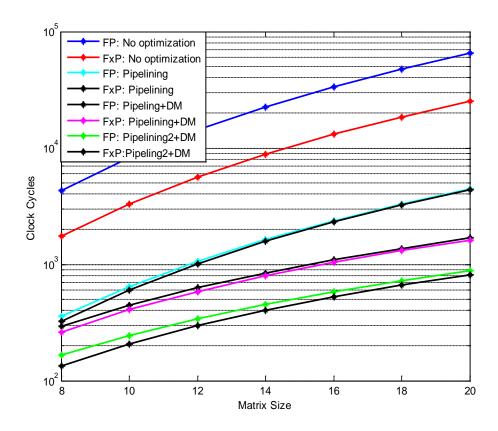

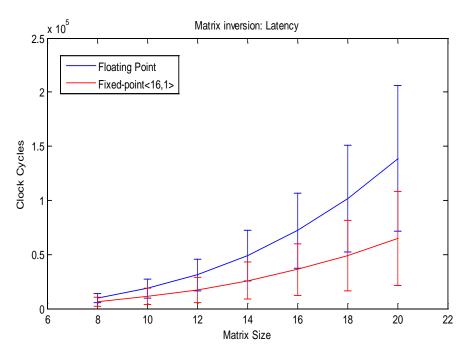

| Figure 3-10: Latency in terms of clock cycles for floating point and fixed point implementation using different techniques                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

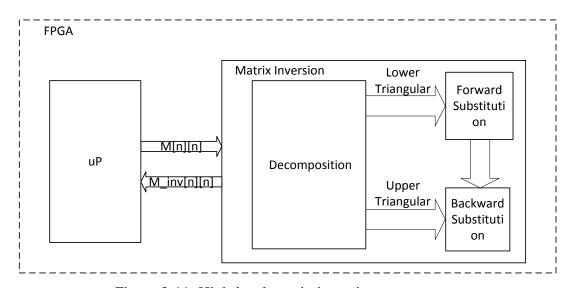

| Figure 3-11: High-level matrix inversion coprocessor                                                                                                                                                      |

| Figure 3-12: Matrix inversion latency for single precision floating-point and fixed-                                                                                                                      |

| point <16, 1>                                                                                                                                                                                             |

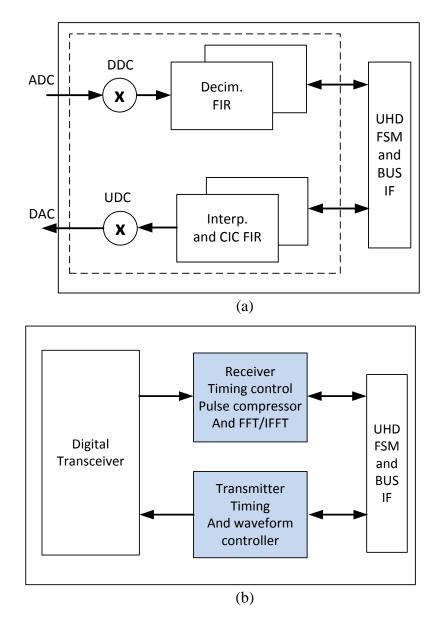

| (b) Proposed FPGA configuration for Radar transceiver (with enhanced radar transceiver Real-time range-Doppler processing blocks)71                                                                       |

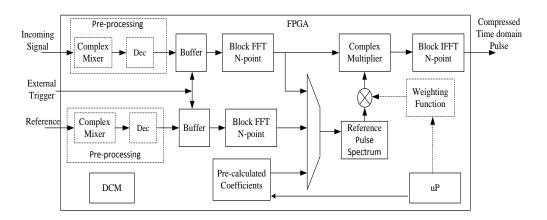

| Figure 4-2: High-level block diagram for matched-filter pulse compression implementation                                                                                                                  |

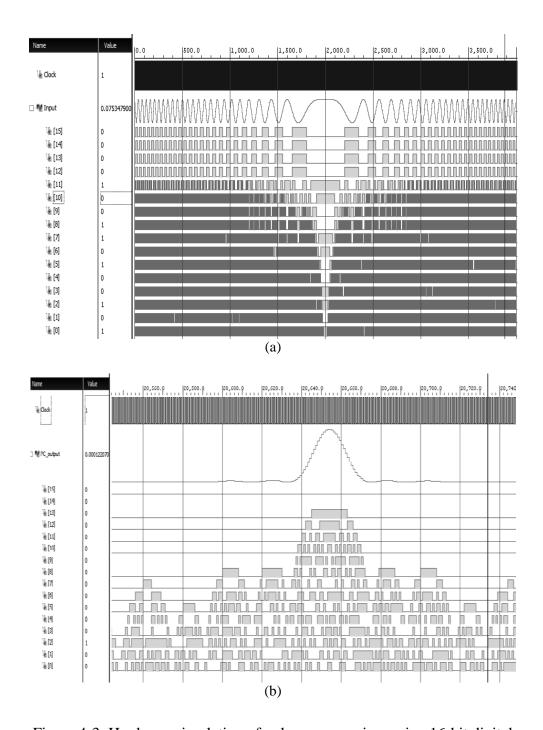

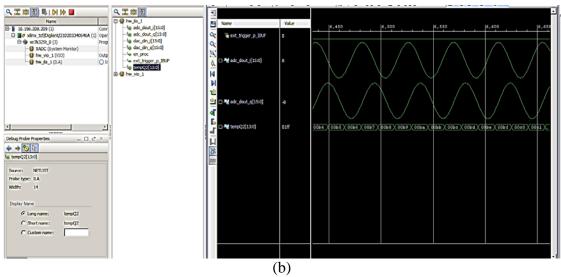

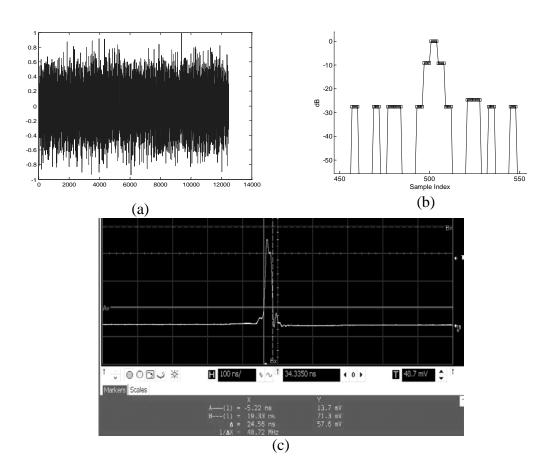

| Figure 4-3: Hardware simulation of pulse compression, using 16-bit digital representation. (a) Uncompressed input signal. (b) Compressed output signal                                                    |

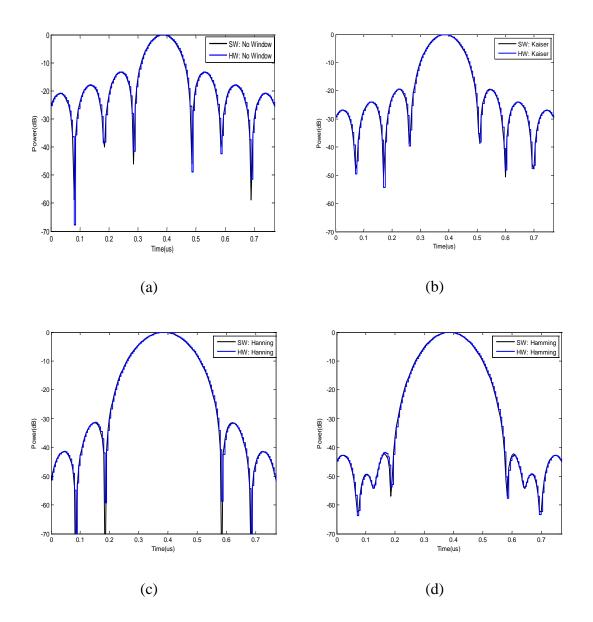

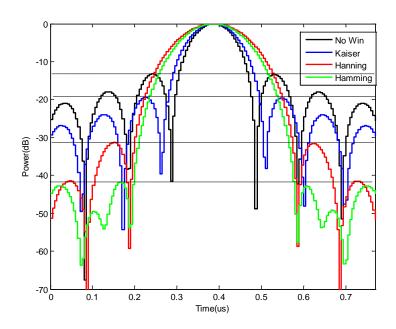

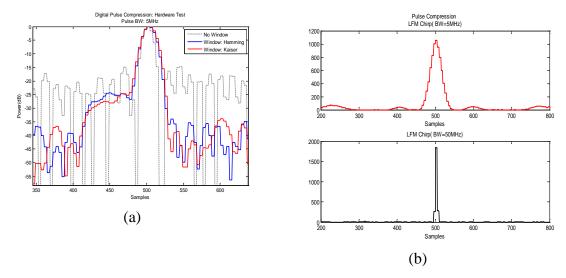

| Figure 4-4: Comparison between MATLAB and hardware (Kintex-7 FPGA) simulations of pulse compression for different weighing windows. (a) No window. (b) Kaiser ( $\beta$ = 2.23). (c) Hanning. (d) Hamming |

| Figure 4-5: Comparison of pulse compression hardware simulation results using different windows: Kaiser ( $\beta$ = 2.23), Hanning, and Hamming. The simulation target is a Kintex-7 FPGA                 |

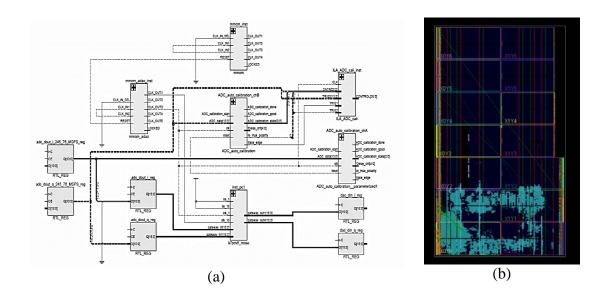

| Figure 4-6: Examples of on-chip implementation results. (a) Simplified Vivado                                                                                                                             |

| RTL schematic for pulse compression. (b) The resulting layout of pulse compression implementation (light blue area) on the XC7k325t-2-ffg990 FPGA                                                         |

|                                                                                                                                                                                                           |

| Figure 4-7: Methods of hardware verification. (a) Complete hardware testbed, (b) Using Vivado logic analyzer for probing internal signals82                                                               |

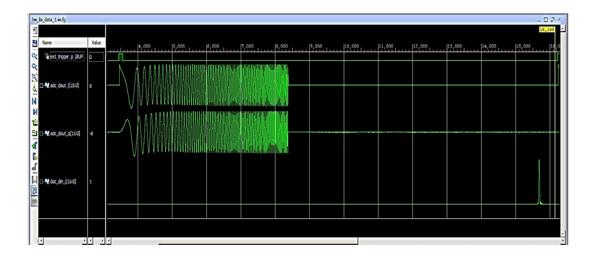

| Figure 4-8: Pulse compression results captured using Xilinx's integrated logic analyzer (ILA). External trigger with pulse duration of 500 ns, I and Q with                                               |

| pulse duration of 20 µs and bandwidth of 10 MHz83                                                                                                                                                         |

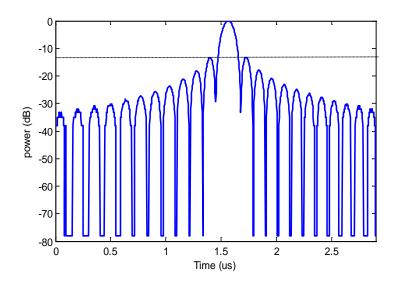

| Figure 4-9: ILA samples of pulse compression output converted to logarithmic scale (dB)                                                                                                                   |

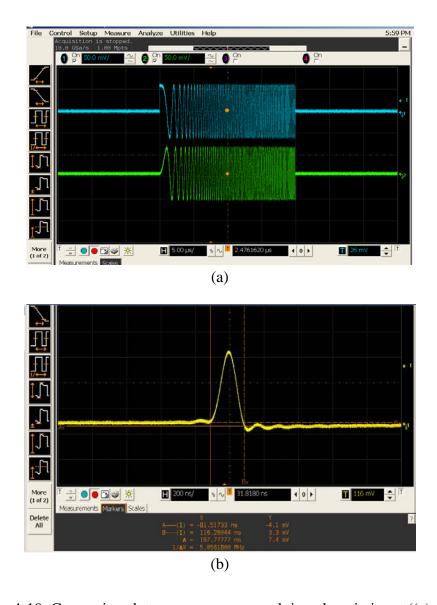

|                                                                                                                                                                                                           |

| Figure 4-10: Comparison between uncompressed time domain input ((a), pulse bandwidth = $10$ MHz, pulse length = $20 \mu s$ ), and compressed time domain                                                  |

| output pulse ((b), captured by DSO)                                                                                                                                                                       |

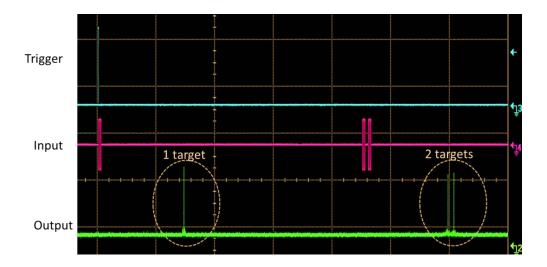

| Figure 4-11: Pulse compressor output for multiple emulated targets. Captured by DSO.                                                                                                                      |

| Figure 4-12: Real-time pulse compression of band-limited random noise with the                                                                                                                            |

| FPGA pulse compression implementation, (a) Input waveform (40 MHz signal bandwidth), (b) Pulse compressor output captured using Vivado logic analyzer                                                     |

| (before DAC output), (c) Pulse compressor output converted to analog pulse                                                                                                                                |

| and captured by DSO87                                                                                                                                                                                     |

| Figure 4-13: Comparison between the PC outputs using internal waveform template                                                                                                                           |

| generation (without external waveform samples) and PC outputs with external waveform templates and different bandwidths                                                                                   |

| Figure 5-1: System elements of the proposed radar transceiver optimizer91                                                                                                                                 |

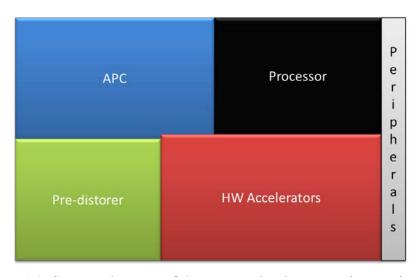

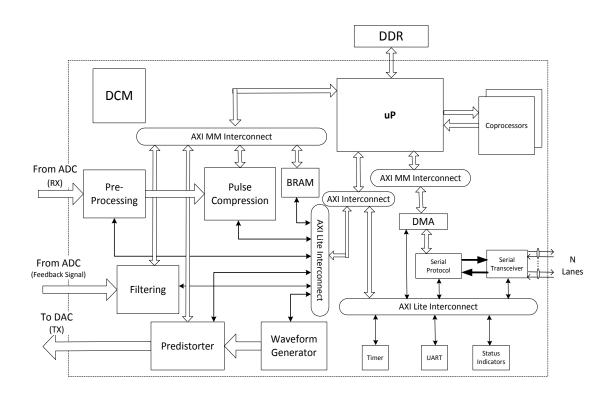

| Figure 5-2: Transceiver optimizer System-on-Chip (SoC)                                                                                                                                                    |

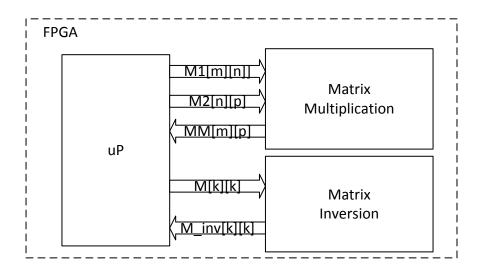

| Figure 5-3: Multiple co-processor for LS-APC96                                                                                                                                                            |

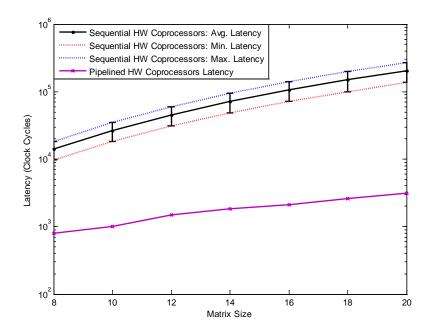

| Figure 5-4: Combined latency of matrix inversion and matrix multiplication          |

|-------------------------------------------------------------------------------------|

| coprocessors for the sequential and pipelined versions99                            |

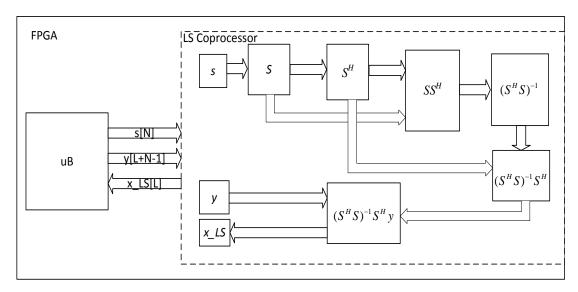

| Figure 5-5: Internal architecture of the single LS coprocessor option               |

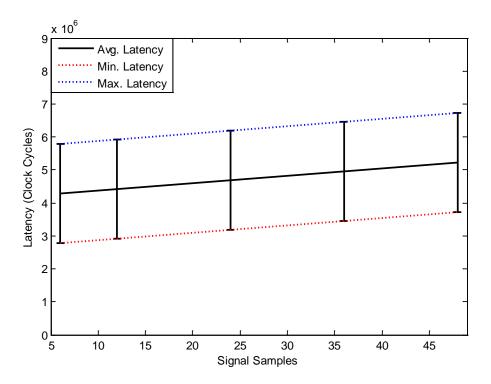

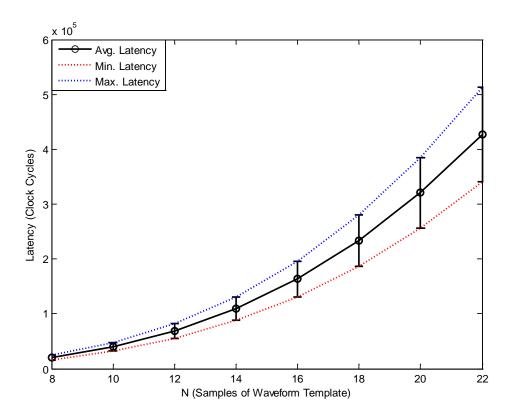

| Figure 5-6: Estimated latency of LS coprocessor for different number of signa       |

| samples with a constant number of range gates. The bar plot also shows the          |

| range of variation (max and min) of latency estimation. Number of range gates       |

| = 60                                                                                |

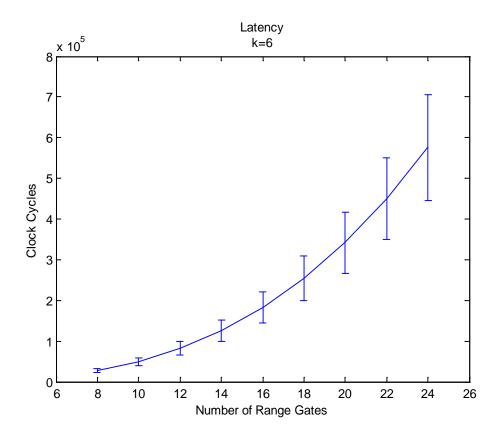

| Figure 5-7: Estimated latencies for different number of range gates for floating    |

| point implementation, assuming the number of transmitted signal samples is          |

| (a short pulse)104                                                                  |

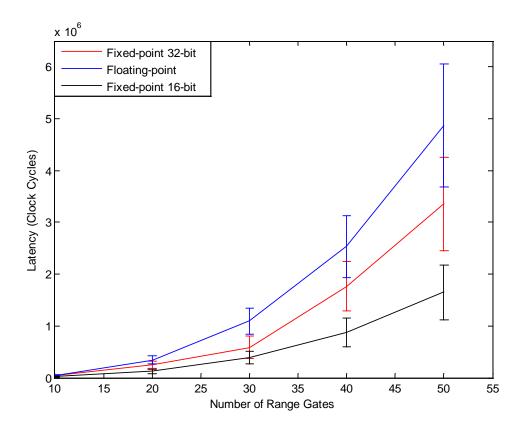

| Figure 5-8: Performance comparison between fixed-point and floating-poin            |

| implementation for different number of range gates. Comparison of Latency           |

| Between Fixed-point and Floating Point Implementation                               |

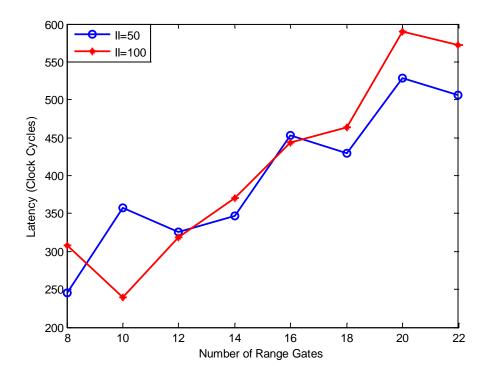

| Figure 5-9: Comparison of latency in terms of clock cycles for different initiation |

| intervals when number of samples is 6107                                            |

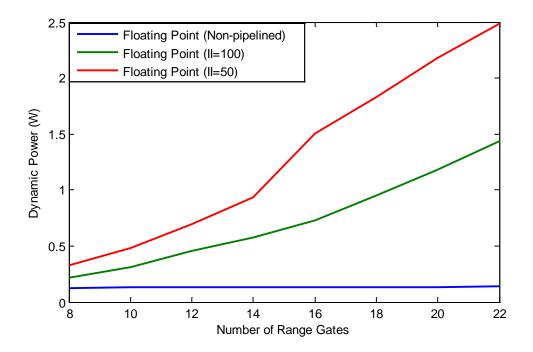

| Figure 5-10: Comparison of dynamic power consumption required by the LS             |

| coprocessor                                                                         |

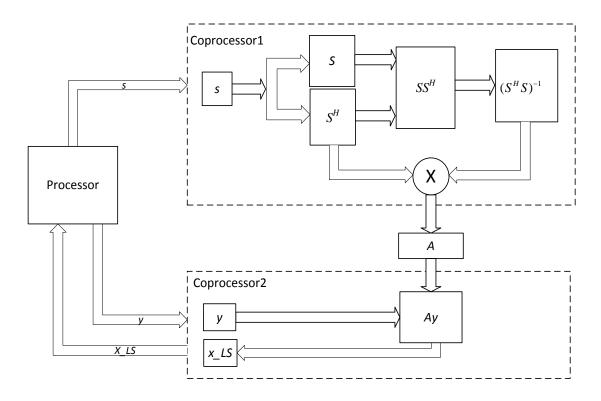

| Figure 5-11: Architecture for fixed-waveform architecture, where Coprocessor 1 is   |

| only activated for the estimation of the filter coefficients109                     |

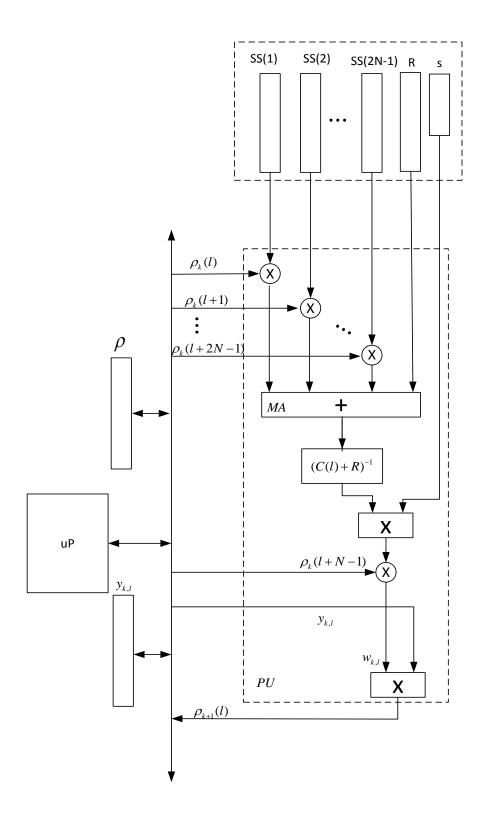

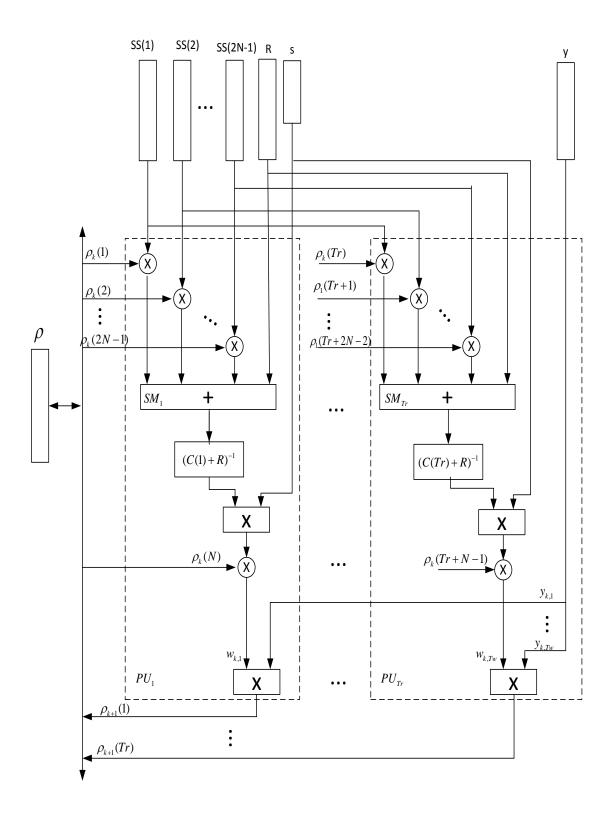

| Figure 5-12: RMMSE coprocessor architecture                                         |

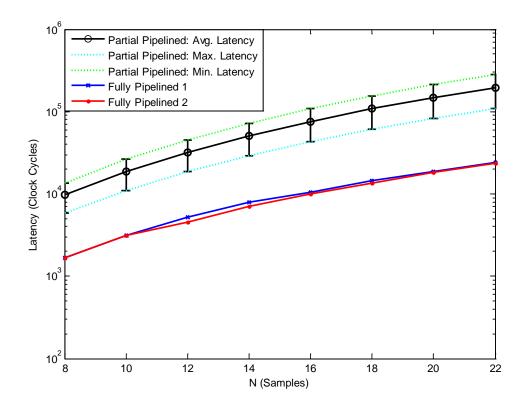

| Figure 5-13: Latency estimation per range gate without optimization113              |

| Figure 5-14: Latency comparison of implementation of RMMSE coprocessor 114          |

| Figure 5-15: Architecture of RMMSE processor                                        |

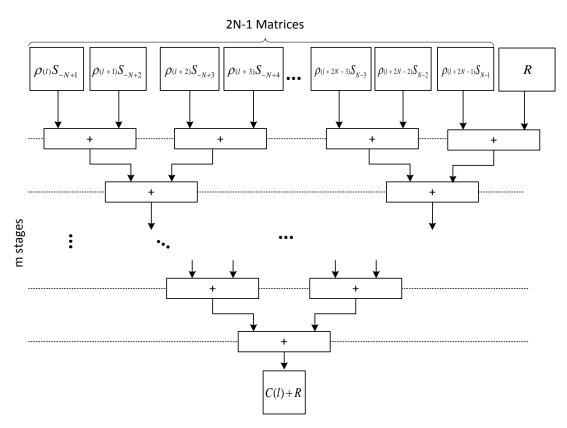

| Figure 5-16: Architecture of the matrix summation to compute the matrix $C(l) + R$  |

| for a range gate                                                                    |

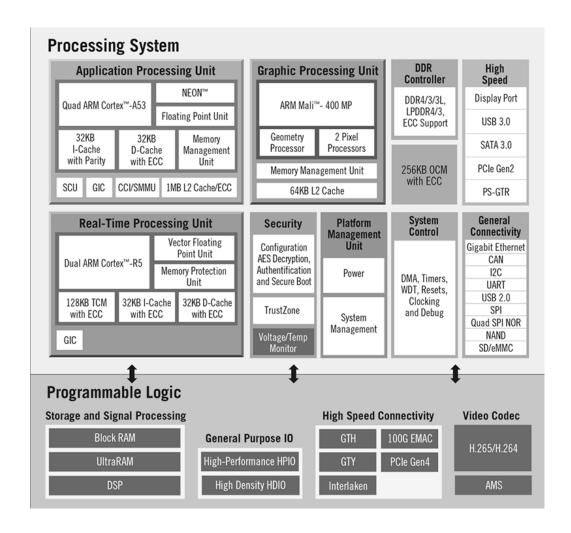

| Figure 6-1: Illustration from Xilinx. The new Zynq UltraScale+ architecture [138    |

| $\frac{1}{2^2}$                                                                     |

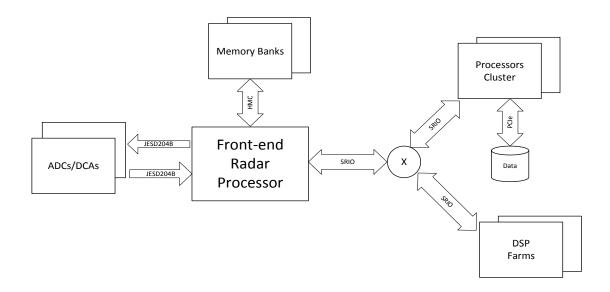

| Figure 6-2: A general architecture of a radar processing system based on seria      |

| technologies.                                                                       |

| 100111010g10g 120                                                                   |

#### **Abstract**

New radar applications need to perform complex algorithms and process a large quantity of data to generate useful information for the users. This situation has motivated the search for better processing solutions that include low-power highperformance processors, efficient algorithms, and high-speed interfaces. In this work, hardware implementation of adaptive pulse compression algorithms for real-time transceiver optimization is presented, and is based on a System-on-Chip architecture for reconfigurable hardware devices. This study also evaluates the performance of dedicated coprocessors as hardware accelerator units to speed up and improve the computation of computing-intensive tasks such matrix multiplication and matrix inversion, which are essential units to solve the covariance matrix. The tradeoffs between latency and hardware utilization are also presented. Moreover, the system architecture takes advantage of the embedded processor, which is interconnected with the logic resources through high-performance buses, to perform floating-point operations, control the processing blocks, and communicate with an external PC through a customized software interface. The overall system functionality is demonstrated and tested for real-time operations using a Ku-band testbed together with a low-cost channel emulator for different types of waveforms.

### Chapter 1

#### Introduction

The general operation of a pulsed radar system consists of transmitting electromagnetic (EM) signals to an area of interest. The reflected EM signals from the environment are captured by the antenna and transformed into electrical signals. The radar receiver filters, amplifies and also transforms the radio frequency (RF) signal to an intermediate frequency (IF) signal by mixing the RF signal with local oscillators. A range profile can be generated based on the processed receive signal and its respective round-trip delay time.

Modern radars demand bigger computing power as well as reconfigurable flexibility, which is important for multiple functions. A good example is pulse compression (PC), which is the main focus of this dissertation. Theoretically, in order to increase the radar ability to distinguish nearby targets and maximize the detectable range, it would be necessary to transmit a narrower pulse width with a higher peak energy, which is infeasible due to power limitations of the transmitter, especially for solid-state transmitters. To overcome this problem, the pulse compression technique [1] has been used for decades.

It is known that a long pulse with frequency or phase modulation is able to achieve equivalent spectral bandwidth to that of a narrow pulse. When applying pulse

compression technique, the receiver can compress the modulated long pulse of bandwidth B to a pulse width equal to I/B, which improves not only the range resolution but also the signal to noise ratio (SNR). Traditional pulse compression commonly uses linear frequency modulation (LFM) due to its simplicity for generation and processing; however, the resultant compressed pulse presents range side lobes in the range gates adjacent to a strong target, which could potentially mask any weak targets [2]. Space and Airborne radars are some example applications, for which range side lobe mitigation is highly desired because the strong scatters from the earth's surface can distort the observations.

Different processing techniques have been investigated to suppress the range side lobes [2-8]. These techniques consider the usage of weighting windows, special waveforms, inverse filters, and adaptive filters. Other techniques are based on adaptive pulse compression (APC) such as the least square (LS) method, as well as optimized and recursive approaches. The reiterative minimum mean-square error (RMMSE) algorithm, derived from the LS method, is a localized optimization-type estimation, which can achieve good performance in terms of retrieving the ground truth [2].

APC algorithms require intensive computation of mathematical operations, for instance, Fourier transforms, matrix multiplications, and matrix inversions. A real-time, high-performance implementation of adaptive pulse compression is a huge challenge to traditional processors due to their fixed architecture and sequential nature of operation. Moreover, in airborne and spaceborne radar applications where size, weight and power consumption (SWaP) are critical constraints, not only the

implementation of efficient algorithms, but also the design of optimal hardware architectures and the use of the appropriate technology are important.

Currently, thanks to the advancement of silicon technology, it is possible to establish a variety of potential real-time and embedded processing solutions with integrated computing resources. These solutions range from general purpose processors (GPP) to application-specific integrated circuits (ASICs). As one of the promising technologies, Field Programmable Gate Arrays (FPGAs) has evolved during the past decades, and incorporated more logic resources, multipliers, memory, high-speed transceivers, processors in a single chip device, and also allowed the interaction between processing units through high-performance buses. The design tools for FPGA have become more matured. In addition, the integration of hardware and software solutions in a single device allowed the design and implementation of customized architectures in a single device to achieve better SWaP, greater reliability and reduced manufacturing cost.

In this dissertation, processor architectures of radar waveform processing, including pulse compression and APC on reconfigurable platforms for radar transceiver optimization are investigated. The objective for this work is to design high-performance System-on-Chip (SoC) processors, which can provide improved target sensing, reduced artifacts, accelerated result generations and reconfigurable capability compared to traditional radar signal processors.

# 1.1 Expectations of High-Performance Embedded Computing (HPEC) in Radar

The main components of a radar system are the transmitter, antenna, and receiver. Raw radar signals are then passed to the signal processors, which extract useful information regarding targets or scene, and the data processor generates useful information for the users [9]. A radar system can be configured to operate with pulsed or continuous waveforms, with coherent or non-coherent modes [10].

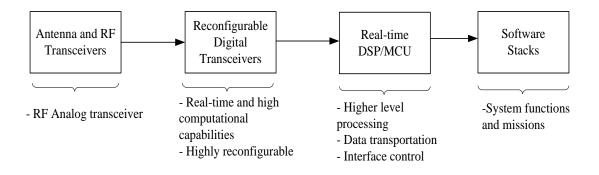

Within a radar receiver, the received signal passes through different processing components, which consist of analog transceivers, digital transceivers with real-time and high computational capabilities, signal processors with efficient data transportation protocol and interface control, and software programs running on CPUs to perform system functions and missions. These characteristics are illustrated in Figure 1-1.

Figure 1-1: Typical functions of a radar receiver.

Initially, radar systems were limited to target detection and range determination functions. With the necessity of more advanced functions in a radar

system, the complexity of digital radar receivers has been increased significantly, which demands more memory, higher speed communication buses, and the computation of large quantities of data in shorter time. Additionally, mobile radars and airborne radars have more SWaP constraints. Modern radar application requires multiple functions, and the computation capability is on the order of GFLOPs and TeraFLOPs, with limited SWaP such as in unmanned aerial vehicle (UAV) and airborne platforms. Furthermore, the digitization at the element level in future phased array radars will increase the computational load to hundreds of TeraOPS for the front-end processing and several TeraFLOPS for the back-end [11].

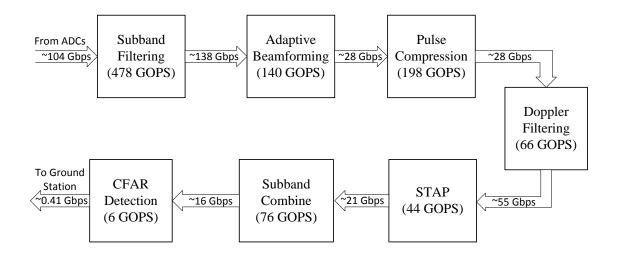

Surface moving target indicator (SMTI) radar, used to detect and track moving targets on the earth's surface, is a good example of a radar application where the computational load is significant. The computational load for a 48-channel phased array, sampled at 480MHz and 12 bits per sample was estimated in [12]. The processing flow and the number of GOPS for each stage are illustrated in Figure 1-2. It can be observed that pulse compression is one of the processing stages that demands the greatest number of GOPS. The aggregate computational complexity of this system is about 1TeraOPS.

Figure 1-2: Computation load for an example GMTI radar [12]

Historically, to meet these demanding new requirements, manufacturers have been developing more powerful computers or processors by increasing the processor's *clock speed*, but this effort was constrained by physical limitations such as heat dissipation. A new trend is incorporating more processing cores with the intention of executing billions of instructions per second, but the power consumption is increased, and an efficient software application that can take full advantage of all the cores is still absent. This situation has motivated our investigation for hardware-based, reconfigurable parallel computer technologies using FPGAs. The advantages of FPGAs are reconfigurable, low-power, and the software re-programmability.

### 1.2 Overview of Real-Time Signal Processing Technologies

Gordon Moore estimated in 1965 that the number of transistors on integrated circuits doubles every year [13]. But then in 1975, he updated his estimation to doubling every two years. Nowadays, it is possible to find processing devices with

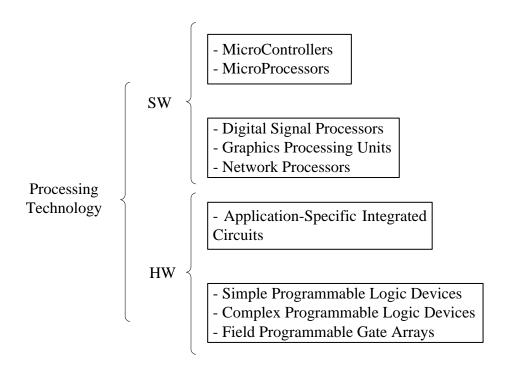

billions of transistors in a single chip. The processing technologies can be classified in two groups as 'hardware-based' and 'software-based' solutions.

The hardware-based solutions deliver higher performance with lower power consumption. They can be grouped in application-specific integrated circuits (ASICs) and field-programmable logic devices (FPLDs). On the other hand, the software-based solutions are constituted by programmable processors which by nature execute the instruction in a serial sequence from memory, and possess programmable flexibilities. This group can be divided into two subgroups: the general-purpose processors and the application-specific devices (such as digital signal processors (DSPs), general graphics processing units (GPUs)).

Figure 1-3: Processing technologies classification.

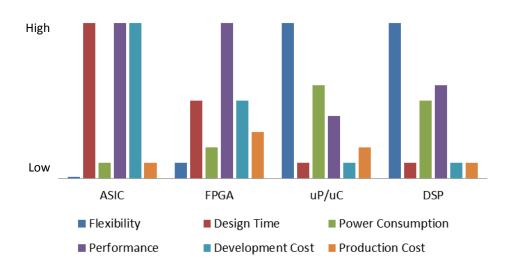

The selection of the appropriate device for a particular radar backend processor is a challenging process because it requires the consideration of several factors such as development cost, performance, hardware resources, power consumption, production cost, time to market, and flexibility. In Figure 1-4, the principal characteristics of some processing technologies are compared. An ideal processing system may incorporate a combination of different technologies and take advantage of the strength of each one.

Figure 1-4: Comparison of different technologies for DSP implementation.

A traditional microprocessor ( $\mu P$ ) is one of the most common processing solutions in many applications, because of its flexibility to be reprogrammed and relatively low development cost. Most  $\mu Ps$  are based on Von Neumann architecture and have inferior computing performance compared to DSPs. Microcontrollers are usually targeted for applications with limited processing requirements. However, some microcontrollers include signal processing engine (SPE) units, such as the Freescale MPC5500 family, which are designed for automotive applications [14].

Because multiply and accumulate (MAC) operations are common to signal processing, DSP devices include dedicated MAC units with particular instructions to accelerate computation. Modern DSPs use Very Long Instruction Word (VLIW) architecture and single instruction multiple data (SIMD) extensions to enhance the levels of data and instruction parallelism.

ASICs and FPGAs are used commonly in applications that require high throughput, especially as front-end signal processors in digital receivers because of their capabilities to handle a large amount of data samples from ADCs. ASIC designs are optimized for specific operations, which can achieve relative small latency and low power consumption, but the fabrication process demands longer time and higher costs, and once the design is fabricated, it cannot be modified. In contrast, FPGAs have the advantage of re-configurability and low power consumption, which are important characteristics for a technology to be considered as a radar front-end signal processor. Moreover, FPGA's computing capabilities are increased if the hard-processor is tightly coupled to create a SoC solution.

### 1.3 Current State of FPGA Technology

#### 1.3.1 Overview of Device Technologies

The Field Programmable Gate Array (FPGA) was originally developed in the 1980s, and since then it has evolved significantly. The technology has migrated from a simple programmable-logic prototype device to a complex system that includes many hardware resources, such as a large quantity of programmable logic units, dedicated

DSP blocks, embedded processors, block random access memory (BRAM), phase-locked loop (PLL), high-speed gigabit transceivers, and other components. FPGAs are widely used in different areas; the range of applications can be from small digital circuits to larger advanced systems. One important characteristic of FPGAs is reconfigurability, which allows the modification of the processing blocks and rerouting of the interconnections to perform a different function without the necessity of powering off. Some FPGAs also offer partial re-configuration capabilities, in which specific areas of the FPGA are modified at the run-time while keeping the other areas operating, which increases silicon reusability significantly.

For a long period, the programmable-logic market was dominated by two vendors, Xilinx and Altera [15]. The XC2000 family was the first FPGA developed by Xilinx and it was comprised of programmable logic units attached to programmable interconnects, and programmable I/O. Altera's first FPGA was based on a PLD structure. The manufacturers have evolved their initial architectures and their programming technologies. Xilinx and Altera FPGAs are based on static random-access memory (SRAM) technology, while Microsemi (previously known as Actel) uses flash and antifuse technology.

The fundamental structure of an FPGA is called 'logic block', which is distributed across the FPGA fabric and interconnected via programmable switches. Xilinx uses the name configurable logic block (CLB), and Altera uses logic element (LE). The content of a logic block also differs from manufacturer to manufacturer. Xilinx's CLB is constituted by two slices; each slice contains a number of look-up

tables (LUTs), storage elements, and multiplexers. For instance, in the Xilinx 7 series FPGAs each slice contains four 6-input LUTs and eight flip-flops [16].

The majority of Xilinx FPGAs are based on 6-input LUTs. Kintex Ultra and Virtex Ultra are the latest families when this dissertation is written, which are based on 16 nm and 20 nm technologies. The on-chip memory size of Spartan and Virtex-4 family is 18 Kbits, while it is 36 Kbits for the 7 Series and UltraScale family. The principal characteristics and the year of introduction of Xilinx and Altera FPGAs are listed in Table 1-1 and Table 1-2, respectively.

Table 1-1: List of Xilinx FPGA families and principal characteristics.

| Family       | LUT Input | Multiplier | BRAM (Kbits) | μP  | Year | Tech (nm) |

|--------------|-----------|------------|--------------|-----|------|-----------|

| Spartan 3    | 4         | 18x18      | 18           |     | 2003 | 90        |

| Virtex 4     | 4         | 18x18      | 18           | PPC | 2004 | 90        |

| Virtex 5     | 6         | 25x18      | 36           | PPC | 2006 | 65        |

| Spartan 6    | 6         | 18x18      | 18           |     | 2009 | 45        |

| Virtex 6     | 6         | 25x18      | 36           |     | 2009 | 40        |

| Artix 7      | 6         | 25x18      | 36           |     | 2010 | 28        |

| Kintex 7     | 6         | 25x18      | 36           |     | 2010 | 28        |

| Virtex 7     | 6         | 25x18      | 36           |     | 2010 | 28        |

| Zynq-7K      | 6         | 25x18      | 36           | ARM | 2011 | 28        |

| Kintex Ultra | 6         | 27x18      | 36           |     | 2014 | 20        |

| Virtex Ultra | 6         | 27x18      | 36           |     | 2014 | 20        |

|              |           |            |              |     |      |           |

Currently, Altera offers four FPGA families, which are called Cyclone series, Stratix series, Arria series, and Max10 series. As shown in Table 1-2, these FPGAs incorporate memory blocks of different sizes such as M512 (512-bit), M4K (4Kb),

M9K (9Kb), M144K (144Kb), MRAM (512Kb), MLAB (640b ROM/320b RAM), M20K [17].

Table 1-2: Principal Specifications of Altera FPGA Families.

| Family      | LUT Input | Multiplier | BRAM (Kbits)  | μP  | Year | Tech(nm) |

|-------------|-----------|------------|---------------|-----|------|----------|

| Cyclone II  | 4         | 18x18      | 4             |     | 2004 | 90       |

| Stratix II  | 8         | 18X18      | 0.5,4,512     |     | 2004 | 90       |

| Stratix III | 8         | 18X18      | 0.624, 9, 144 |     | 2006 | 65       |

| Cyclone III | 4         | 18x18      | 9             |     | 2007 | 65       |

| Arria       | 8         | 18X18      | 576           |     | 2007 | 90       |

| Stratix IV  | 8         | 18X18      | 0.624, 9, 144 |     | 2008 | 40       |

| Arria II    | 8         | 18X18      | 9             |     | 2009 | 40       |

| Cyclone IV  | 4         | 18x18      | 9             |     | 2009 | 60       |

| Stratix V   | 8         | 27X27      | 0.640, 20     |     | 2010 | 28       |

| Cyclone V   | 8         | 27X27      | 10            |     | 2011 | 28       |

| Arria V     | 8         | 27X27      | 10            | ARM | 2011 | 28       |

| Arria 10    | 8         | 27x27      | 0.640, 20     | ARM | 2013 | 20       |

| Stratix 10  | 8         | 27x27      |               | ARM | 2013 | 14       |

Because multipliers and accumulators are essential operations for the implementation of signal processing algorithms, FPGA vendors have included small DSP blocks into the fabric of the FPGA to improve the performance of arithmetic operations and release the logic resources (flip-flops, look-up tables) for other functions. Each Xilinx's DSP block contains two DSP slices. A DSP slice can perform logic and arithmetic functions such as multiply-accumulator, multiply-adder, and counter. DSP slices can also be cascaded to implement more sophisticated functions such as complex multipliers or n-tap FIR filters, thus achieving higher clock rates.

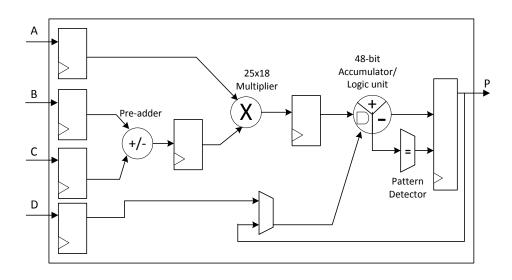

The DSP blocks included in Xilinx FPGAs are called DSP48s, each DSP is mainly composed of a pre-add/subtract unit, a multiplier, and an add/subtract/accumulate engine. Each family of Xilinx's FPGA has a different version of the DSP with some variations in its architecture. DSP48As are included in Xilinx Spartan-3A devices, which consist of an 18-bit pre-adder, followed by an 18x18-bit signed multiplier and a 48-bit add/subtract/accumulate engine. In the Spartan-6 family, it is called DSP48A1, or DSP48E in Virtex-5, and also called DSP48E1 in the Virtex-6 and the 7 series families. The architecture of a DSP48E1 is shown in Figure 1-5, where the main components are a 25-bit pre-adder, 25x18 multiplier, and pattern detector. In the Xilinx UltraScale family, it is called DSP48E2s, and the multiplier and pre-adder width is increased to 27x18 bits and 27 bits, respectively.

Figure 1-5: Xilinx's DSP48E1 architecture [16]

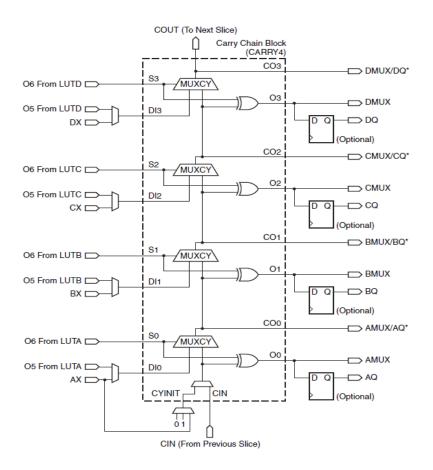

Another important resource included in an FPGA is fast carry circuitry to perform faster arithmetic operations.

For instance, Xilinx includes dedicated carry logic blocks, called CARRY4 [18]. The logic elements of each block are shown in Figure 1-6.

Figure 1-6: Xilinx's carry logic slice architecture [18]

## 1.3.2 Design Flows

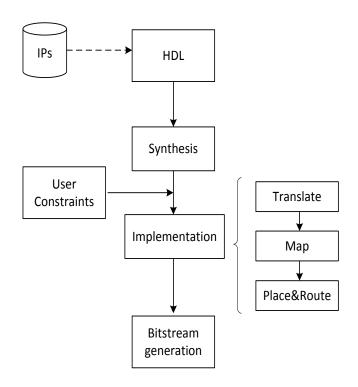

The traditional FPGA design flow is shown in Figure 1-7. The design starts with the description of the system architecture using a hardware description language (HDL), which may include prebuilt functions or intellectual property cores (IPs). HDL design files are synthesized to register-transfer level (RTL), then an implementation process is performed, which consists of three steps: translate, map, place and route.

Finally, a bitstream file is generated, which is downloaded and used to configure the FPGA device.

Figure 1-7: Traditional FPGA design flow.

#### **1.3.3 IP Cores**

Intellectual property (IP) cores are prebuilt functions that provide solutions to enhance system implementation productivity. IP cores are available for a variety of general functions from simple arithmetic operations to microprocessors, as well as for specific applications such as signal processing, video, networking, storage, and other areas. FPGA vendors offer both own and third-party IP libraries, including IP programs such the Xilinx Alliance program and the Altera Megafunctions Partner Program (AMPP). IP cores can be classified as soft IP, firm IP, or hard IP. A soft IP

core is distributed as synthesizable files describing the register transfer logic of a design. The advantages of a soft IP include flexibility, scalability and portability. A firm IP is delivered in the form of synthesized netlists, which has a certain type of technology dependence. A hard IP core is presented as a mask layout with characteristics such as high performance and predictable functionality, but limited flexibility for system optimization.

#### 1.4 System on a Chip (SoC)

#### 1.4.1 Introduction

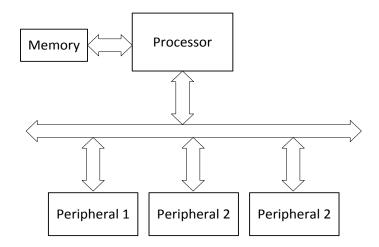

According to [19], the evolution of digital design styles occurred in three stages. The first stage, *system-on-backplanes*, was based on several printed boards with specific functions interconnected through the backplane to form a system. This architecture evolved to *system-on-board*, in which processing components were mounted on a single board. And the third stage, *system-on-chip* (*SoC*), integrates the board-level functionalities into a single device, resulting in a design with more efficient data exchange between processing units, better computing performance, and improved SWaP compared to a system of discrete components [20].

A SoC design includes at least one microprocessor to run the software component of the system, memory attached to the processor for temporary storage of data and instructions, and peripherals, which can be a coprocessor, a soft-core/hard-core IP, additional memory, or general input and output ports. Processor and peripherals are interconnected via standard buses. A general representation of a SoC solution is shown in Figure 1-8.

Figure 1-8: Basic concept of a generic SoC architecture.

Early studies proposed different reconfigurable architectures which combined reconfigurable fabric and a programmable processor. For instance, the hybrid architecture Garp was proposed in [21]; the system included a reconfigurable coprocessor which was connected to a MIPS-II processor in the same die. The coprocessor was also able to access the processor's data memory and the external shared memory through dedicated interconnections. In [22], the authors proposed a reconfigurable architecture called PipeRench; this reconfigurable fabric allowed pipelined reconfiguration of the processing blocks through a hardware virtualization process. A drawback of this architecture was the bandwidth limitations between the main memory, the PipeRench fabric, and the host processor, since PipeRench was connected as a coprocessor. Chimaera architecture was proposed in [23]; this architecture consisted of a small reconfigurable functional unit integrated into a microprocessor itself, reducing the communication bottleneck and taking advantage of the reconfigurable fabric to general-purpose computing. Other reconfigurable systems

were proposed in: PRISM [24], PRISM-II [25], OneChip [26], REMARC [27], MOLEN [28], XiRISC [29], etc.

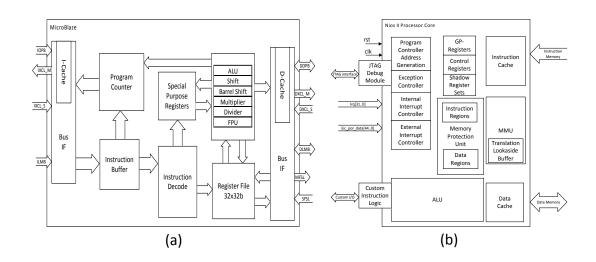

Xilinx and Altera offer processors in the form of soft-core IP or hard-core IP. Soft-processors are built from logic resources of the FPGA. Xilinx's soft-processor is called MicroBlaze, which is a 32-bit processor with reduced instruction set computing (RISC) architecture. Similar architecture is adopted for Altera's soft-processor, Nios II, which has three different versions: Nios II/f (performance), Nios II/s (performance and low cost), and Nios II/e (low cost).

Figure 1-9: Block diagrams of a Xilinx MicroBlaze Processor [30] and an Altera Nios II Processor [31].

Some FPGA families incorporate hard microprocessors into their logic fabrics. For this type, there are commercial FPGA families available in the market such as Xilinx Zynq, Microsemi SmartFusion, and Altera Arria. Earlier Xilinx Virtex families include PowerPC processors, which are based on Harvard architecture and can run up to 550 MHz. The Xilinx Zynq architecture comprises two main units: the Processing

System (PS) and the Programmable Logic (PL), which are interconnected through dedicated Advanced eXtensible Interface (AXI) buses. The PS unit is basically a dual-core ARM Cortex-A9 processor operating at clock speeds up to 1 GHz. Each core is connected to optimized computational units, such as a media processing engine (MPE) or a floating-point processing unit (FPU). Different cache levels are also part of the system, which are controlled by a memory management unit (MMU). A snoop control unit (SCU) interfaces the L1 and L2 caches to ensure consistency of data between them. The processor includes separate L1 caches for data and instructions with a size of 32 KB. The two cores also share a larger L2 cache of 512 KB for instruction and data. In addition, there is 256KB of on-chip memory within the application processing unit (APU).

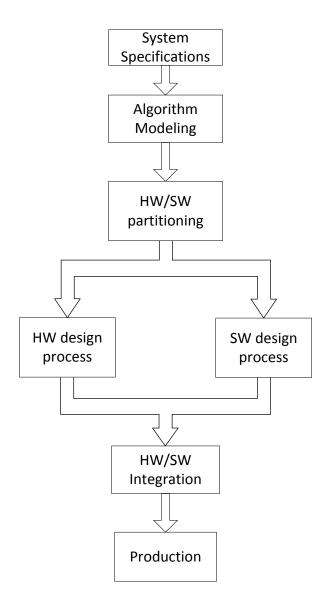

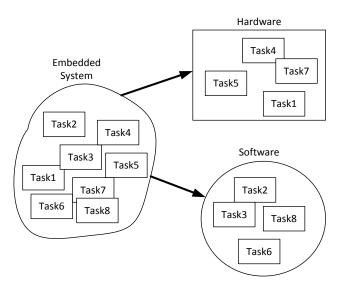

A SoC design involves hardware logic and programmable processors. Figure 1-10 shows a general overview of the process to implement a SoC solution. This process starts with the specifications of the system, followed by modelling the algorithm. Partition of the design between hardware and software is then performed. Hardware and software partitions follow independent paths first, then they are integrated to obtain the final product and ensure all the parts are tightly coupled.

Figure 1-10: General SoC system implementation model.

## 1.4.2 Hardware/Software Partitioning

The hardware/software (HW/SW) partitioning, or hardware/software codesign, involves the identification of tasks that are more suitable for hardware or software implementation. HW/SW partitioning is a key process in the design of an embedded system because it can have a considerable impact on the performance of the

overall system. There is no tool that can do this process automatically. Due to its parallel nature, programmable hardware is preferred for tasks that are repetitive, and can be efficiently split into multiple and concurrent tasks. Dynamic and unpredictable tasks are better suited for a software-based implementation [20].

Dynamic range is another important factor when deciding the appropriate partition implementation. Traditionally, a general-purpose processor (GPP) has been used for floating-point tasks, due to their special math engines and dedicated floating point units. On the other hand, FPGAs used to be mostly for fixed-point implementations, since floating-point implementations demand much more logic resources. However, in modern FPGAs this is compensated with the increased number of logic resources and DSPs. Therefore, tasks that require floating-point format representation can be implemented in either software or hardware.

Figure 1-11: Hardware/software partitioning

#### 1.4.3 Advanced eXtensible Interface (AXI) Interconnect Technology

Another essential component in a SoC design is the bus interconnection that coordinates and moves data between the different processing units within the FPGA. Xilinx's interconnect technology prior to the 7 series family is based on the IBM CoreConnect standard, which includes three types of buses: the processor local bus (PLB) for high-speed transactions, the On-chip Peripheral Bus (OPB) for I/O devices, and the device control register (DCR) for configuration and status.

The Xilinx 7 series and UltraScale FPGAs are based on the AXI AMBA 4 standard. AXI was proposed by ARM Holdings public limited company (ARM). This standard defines three types of buses: AXI4, AXI4 Stream, and AXI-Lite. AXI4 is a high-performance bus for memory mapped links, and supports data burst transfer up to 256 data words with data width from 32 to 1024 bits. AXI4-Stream is a non-address based bus with unlimited data bursts, and AXI-lite interconnect is intended to interconnect slow peripherals or control/monitor signals from processing units.

Figure 1-12 shows the top-level architecture of the AXI interconnect core. The core consists of slave interface, master interface, and processing blocks. The crossbar routes the traffic on the AXI channels between the devices connected to the master and slave interface [9].

Figure 1-12: Top-level AXI interconnect [32].

#### 1.4.4 Evaluation Platforms

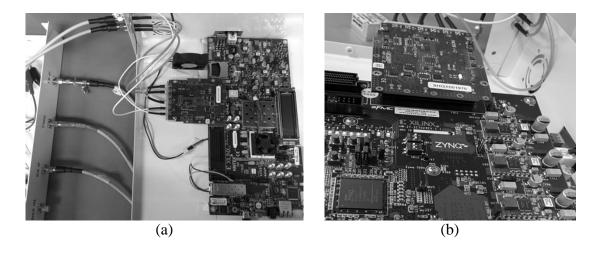

Today's FPGAs are gaining more and more computing power. Xilinx claims 987 GFLOPS peak computing power in a single Virtex-7 980XT FPGA and Altera claims close to 1 TFLOPS peak computing performance for the Stratix V FPGA. The same design and implementation procedure developed in this work can be applied to different and smaller devices. Specifically, we have used two different platforms in most of this dissertation: the KC705 DSP evaluation board and the Avnet ZedBoard 7020 baseboard.

The KC705 board includes an XC7k325t-2-ffg990 FPGA, which has 356K logic cells, BRAMs memory with a total of 16,020KB, and 840 DSP blocks. The ZedBoard's FPGA is the XC7Z020-CLG484-1, which includes a dual-core ARM Cortex-A9 and 85K logic slices, 4,480KB of BRAM, and 220 DSP blocks. Figure 1-13 shows the photos of KC705 and ZedBoard evaluation boards.

Figure 1-13: Testbed for the implementation of APC. It includes a Ku-band transceiver, (a) Kintex-7 and (b) Avnet ZedBoard evaluation boards.

#### 1.5 Dissertation Outline

The main contribution of this work is developing a general FPGA based SoC framework for radar signal processing, and demonstration of this framework through Xilinx FPGA devices, for specific pulse compression algorithms.

This dissertation is organized as follows: Chapter 2 provides an overview of pulse compression technologies and algorithms. This chapter also introduces the concept of adaptive pulse compression (APC) and its application to modern radar systems. Different algorithms, as well as their computational load requirements are summarized.

Chapter 3 describes the principal processing cores used for the implementation of APC (and other adaptive processing). Hardware implementation of linear algebra operations, such as matrix multiplication and matrix inversion are also discussed.

The details of FPGA implementation of traditional pulse compression is presented in chapter 4. Tradeoffs between different specific design approaches are also discussed.

Chapter 5 focuses on APC processing implementations, and compares various SoC architectures based on basic units of Chapter 4, summarizes design considerations and hardware design results. The achieved performance of the SoC implementations of APC are also discussed.

Finally, Chapter 6 addresses the long-term roadmap of embedded processors and proposed future work for high performance, embedded radar processors.

# Chapter 2

# **Adaptive Pulse Compression (APC) and Implementations**

The range (R) between a pulsed Doppler radar and a point target is calculated based on the round-trip travel time of the pulse (T): R = cT/2, where (c) is the speed of light. The radar's range resolution is defined as the ability of the radar to resolve objects in range [10]. The maximum detection range can be increased by transmitting a longer pulse width, since more energy is transmitted in the pulse, but a longer pulse can degrade the range resolution ( $\Delta R$ ). In order to improve the radar range resolution and maximize the detectable range, it would be necessary to transmit a narrower pulse width with a higher peak energy, which is generally not feasible due to power limitations of the transmitter, especially for solid-state transmitters. Pulse compression overcomes this problem by using a long pulse modulated in frequency or phase to achieve a similar spectral bandwidth of a short pulse, the long pulse is then "compressed" by the receiver to a width equal to 1/B, and the range resolution is improved to  $\Delta R \approx c/2B$ . This improvement can also be represented by a factor called pulse compression ratio (CR), which is approximately the multiplication between the pulse width  $(\tau)$  and the bandwidth (B), and it is usually much larger than unity. However, traditional pulse compression presents some drawbacks since it uses linear frequency modulated waveforms. In recent years, there are numerous waveform

modulations and processing techniques that have been developed in order to overcome hardware constraints, and improve target detection, interference mitigation, and others.

In general, the radar waveform modulation scheme can be classified as frequency and phase modulation. Frequency modulation waveforms can use either linear or nonlinear modulations. On the other hand, phase modulation can use either biphase or polyphase waveforms.

A filter that maximizes the SNR at the radar receiver is referred to as the matched filter, which is derived from the transmit waveform. Waveform properties such as SNR, range resolution, and Doppler tolerance can be defined in terms of the matched filterer response [10]. The output of the matched filter is equivalent to the cross-correlation between the received signal and the transmit signal. The matched filter is expressed as [1]:

$$MF = \int_{-\infty}^{\infty} s_r(t) \ s * (t - T_R) \ df$$

(2.1)

where,  $s_r(t)$  is the received signal, s(t) is the transmit signal,  $T_R$  is the estimate of the time delay, and  $(\bullet)^*$  denotes the complex conjugate.

The traditional matched filter can generate significant sidelobes in the range gates adjacent to a strong target, which could potentially mask the presence of smaller targets. For applications such as satellite-borne weather radar the range sidelobes generated from the earth surface can distort the measurements, so that low range sidelobes are highly desired [33], preferably lower than 60dB for light rain measurements [34]. Different types of waveforms, which are designed to achieve low

sidelobe levels, have been studied in [7, 33, 35-37], each type of waveform has advantages and drawbacks.

The characteristics of a radar waveform such as range resolution, range sidelobe level, spacing and range ambiguities, Doppler resolution, Doppler sidelobe level, and spacing of Doppler ambiguities [35], can be described by the *ambiguity* function (AF). AF is derived from equation (2.1) by replacing  $s(t) = u(t) \exp(j2\pi f_0 t)$ , and obtaining:

$$\left|\chi(\tau, f_d)\right|^2 = \left|\int_{-\infty}^{\infty} u(t) \, u * (t + \tau) \, e^{j2\pi f_d t} dt\right|^2$$

(2.2)

In which u(t) is the complex envelop of the signal,  $\tau$  is the time delay, and  $f_d$  is the Doppler frequency which is the difference between the received signal and the nominal values expected by the matched filter.

# 2.1 Pulse Compression Waveforms

# 2.1.1 Frequency Modulated Waveforms

The most common pulse compression waveform that has been used in radar systems is the linear frequency modulated waveform (LFM) because it is easy to generate and process. The LFM waveform with rectangular shape, bandwidth (B), and pulse width T is represented as:

$$s(t) = \frac{1}{\sqrt{T}} \operatorname{Rect}(\frac{t}{T}) \exp(j\pi K t^2)$$

(2.3)

in which K is the slope frequency which is equal to the ratio between the bandwidth (B) and the pulse width (T). Using equation (2.2) to find the ambiguity function of s(t), the following expression is obtained:

$$\left|\chi(\tau, f_d)\right|^2 = \left|\frac{1}{T} \int_{-\infty}^{\infty} Rect(\frac{t}{T}) Rect(\frac{t+\tau}{T}) \exp(i\pi K t^2 - j\pi K (t+T)^2)\right|^2$$

(2.4)

Therefore, the ambiguity function of an LFM waveform can be written as:

$$\left|\chi(\tau, f_d)\right|^2 = \left|(1 - \frac{|\tau|}{T})sinc(\pi(f_d - K\tau)(T - |\tau|))\right|^2, \quad |\tau| \le T; \quad 0 \text{ elsewhere} \quad (2.5)$$

Here  $\tau$  is the shift in time, and  $f_d$  is the Doppler shift defined as the difference between the received signal and the nominal values expected by the matched filter.

The autocorrelation of the LFM waveform is essentially a *sinc* function shape with high peak sidelobes of approximately -13.2 dB, and sidelobe levels decreasing at a rate of -4 dB per sidelobe interval. The common method for mitigation of the high sidelobe levels is applying weighting functions to the signal spectrum, but this method may cause SNR loss and degradation of the range resolution. In [7], range sidelobe of -55 dB was achieved by *weighting* the amplitude of the transmit waveform using a half-wave sinusoidal function, with the transmitter operating in the linear rather than saturation region. However, in order to avoid power efficiency degradation in the transmitters, it is preferable to perform the weighting process only on the receiver. The common window functions are Hamming, Kaiser, Hanning, Blackman, etc. Details about their characteristics can be found in [38, 39].

Another method to achieve low range side lobes is through the design of specific non-linear frequency modulated waveform (NLFM) with a suitable matched-filter signal spectrum, where the non-linear rate of the frequency variation plays the same role as amplitude weighting of the spectrum without affecting the radar transmitter efficiency. The complexity of an NLFM might be higher than LFM waveform, but it can provide low sidelobes without the SNR loss caused by a mismatched filter [1]. The literature about NLFM design is vast. For example, [8] described a method for NLFM pulse compression waveform with a truncated Gaussian spectrum, achieving sidelobes of -46 dB for TB = 1000. [33] proposed a piecewise NLFM waveform with range sidelobes less than -60 dB. This design was then improved [40] to a continuous NLFM waveform with side lobes of better than -70dB. More information about other implementations can be found in [41-43].

#### 2.1.2 Phased-Coded Waveforms

Phased-coded waveforms are used widely in airborne radars and even in ground-based weather radars recently, e.g. the Next Generation Weather Radar (NEXRAD) system. The waveform is constituted of a sequence of sub-pulses, also known as 'chips'; the phase modulation has finite states among these chips. The characteristics of phased-coded waveforms are fundamentally dependent on the coding sequence employed [10]. These types of waveforms can be classified into two groups: biphase and polyphase-coded waveforms.

The phases of a biphase-coded waveform are usually either 0 or  $\pi$ . A well-known binary set of codes is the Barker codes, for which the sidelobe levels of the compressed pulse are equal. The periodic autocorrelation function is given by the following equation:

$$\chi(m,0) = \sum_{k=0}^{N-1} c_k c_{k+m} = \begin{cases} N, & m = 0 \pmod{N} \\ \\ a < N, & m \neq 0 \pmod{N} \end{cases}$$

(2.6)

where N represents the code length. The seven Barker codes and their principal characteristics are listed in Table 2-1, where '1' indicates 0 phase and '0' means  $\pi$  radian phase, and the relationship between the peak side lobe level and the code length is given by:  $10\log(\frac{1}{N^2})$  [1].

Table 2-1: Binary Barker Codes

| Code<br>Symbol  | Code<br>Length | Code          | Side Lobe<br>level (dB) | Integrated Sidelobe<br>Levels(dB) |  |

|-----------------|----------------|---------------|-------------------------|-----------------------------------|--|

| $\mathbf{B}_2$  | 2              | 11/10         | -6                      | -3                                |  |

| $\mathbf{B}_3$  | 3              | 110           | -9.5                    | -6.5                              |  |

| $B_4$           | 4              | 1110/1101     | -12                     | -6                                |  |

| B <sub>5</sub>  | 5              | 11101         | -14                     | -8                                |  |

| B <sub>7</sub>  | 7              | 1110010       | -16.9                   | -9.1                              |  |

| B <sub>11</sub> | 11             | 11100010010   | -20.8                   | -10.8                             |  |

| B <sub>13</sub> | 13             | 1111100110101 | -22.3                   | -11.5                             |  |

Another type of binary code is the Maximal Length Sequence (MLS), which is generated using an n-stage linear feedback register. The length of the binary sequence

is  $N = 2^n - 1$ , where *n* is an integer, and the typical sidelobes are approximately  $10\log(\frac{1}{N})$  [10].

When the phases of the sub-pulses are not limited to the two phases of 0 and  $\pi$ , the code scheme is called polyphase code, and the sidelobe levels are lower than for the binary codes. The Frank code, which is described in [44], is a popular polyphase code. Variants of the Frank code are the P-codes; P1 and P2 are described by Lewis and Kretschmer in [45]. However, due to the very low Doppler tolerance of P1 and P2, two new codes were then developed: P3 and P4 codes [46]. The k-phase value of P3 and P4 codes are defined in the following equations:

$$\Phi_{k}^{(3)} = \frac{\pi (k-1)^{2}}{BT} \tag{2.7}$$

$$\Phi_k^{(4)} = \frac{\pi (k-1)^2}{BT} - \pi (k-1)$$

(2.8)

In [47], Felhauer proposed the P(n,k) codes, which are derived by step approximation of the phase function of an NLFM waveform, and can improve the peak sidelobe ratio and the tolerance of low Doppler shifts.

Numerous pulse compression waveform designs can also be found in the literature, each design with advantages and limitations. Some examples are: Costas codes [48], Welti Codes [49], complementary codes [50], Hoffman codes [37], and others.

#### 2.2 Adaptive Pulse Compression Algorithms

In the previous section, several types of waveforms designed to mitigate masking problem of the high range sidelobes were introduced. Although those waveforms can achieve low sidelobes, the implementation is constrained to tradeoffs among range sidelobe level, range resolution, energy efficiency, Doppler tolerance, and other hardware-related factors such as the nonlinearity of power amplifiers and calibration errors [51]. In general, optimal waveform design can achieve low-sidelobes but the waveform can become very complicated, and be specific to a particular radar transmitter chain operation state. To further improve the range sidelobe reduction with "waveform independent" ground truth estimation, several adaptive processing techniques have been proposed: mismatched filtering [52], least-squares estimation [53], and inverse filtering [54]. A waveform-independent approached was proposed in [2], which is based on adaptive estimation at each range cell, while reducing the range sidelobes to level of the noise floor.

The basic Least Squares Estimator (LSE) [55] assumes N samples of the time-waveforms are transmitted, denoted as:  $s = [s_0 \ s_1 \ s_2 \ ... \ s_{N-1}]^T$ , where,  $(\cdot)^T$  indicates the transpose operation. The received signal is given by:  $y = Sx + \eta$ , where the range profile is  $x = [x(0) \ x(1) \ ... \ x(L-1)]^T$ ,  $\eta$  is the noise vector, and S is the (L+N-1)xL matrix of the transmitted waveform

$$S = \begin{pmatrix} s_0 & 0 & \cdots & \cdots & 0 \\ \vdots & s_0 & & & \vdots \\ s_{N-1} & \vdots & \ddots & & & \\ 0 & s_{N-1} & & \ddots & & \vdots \\ \vdots & 0 & \ddots & & \ddots & 0 \\ & \vdots & 0 & \ddots & \ddots & 0 \\ & \vdots & \vdots & & \ddots & \vdots \\ 0 & 0 & \cdots & \cdots & 0 & s_{N-1} \end{pmatrix}$$

$$(2.9)$$

It is also assumed that the range profile of the ground truth x has length L, and the received signal vector  $y = [y(0) \ y(1) ... \ y(L+N-2)]^T$  is the convolution between the transmitted waveform and the ground truth. Therefore, the estimation of ground truth is given by the following equation [56]:

$$\hat{x}_{IS} = (S^H R S)^{-1} S^H R^{-1} y \tag{2.10}$$

R is the covariance matrix of the noise vector  $\eta$ :  $R = E[\eta(l) \eta^H(l)]$ . This estimation requires the complete range profile, which may demand more computing power and larger memory size. An optimized version, truncated LS (TLS), is based on the segmentation of the received signal into k-blocks:  $\hat{x}_{TLS} = (S_k^T R_k S_k)^{-1} S_k^T R_k^{-1} y_k$ , and processing of each individual block.

Another adaptive APC algorithm, which is based on minimal mean-squared error (MMSE) criteria related to the following cost function (c(l)), was introduced first in [56].

$$c(l) = E \left[ \| x(l) - w^{H}(l)Y(l) \|^{2} \right]$$

(2.11)

where,  $Y(l) = [y(l) \ y(l+1) \dots y(l+N-1)]$ . Taking the partial derivative of equation (2.11) with respect to  $w^H$ , the MMSE filter weights are obtained:

$$w(l) = (E[Y(l)Y^{H}(l)])^{-1}E[Y(l)x(l)]$$

(2.12)

It is also known that  $Y(l) = A(l)s + \eta$ , where A(l) represents the matrix of the range profile:

$$A(l) = \begin{pmatrix} x(l) & x(l-1) & \cdots & x(l-N+1) \\ x(l-1) & x(l) & \ddots & \vdots \\ \vdots & \vdots & \ddots & x(l-1) \\ x(l-N+1) & x(l-N) & \cdots & x(l) \end{pmatrix}$$

(2.13)

The simplified format for the MMSE filter is derived as:

$$w(l) = \left| x(l) \right|^2 \left( \sum_{n=-N+1}^{N-1} \left| x(l+i) \right|^2 s_n s_n^H + R \right)^{-1} s$$

(2.14)

Further details can be found in [2]. In addition, [3] proposed a reduced-dimension algorithm for the MMSE adaptive pulse compression. The reduction is based on two forms of dimensionality reduction: decimation and contiguous blocking.

The different adaptive pulse compression algorithms can be grouped into two groups: global deconvolution-type solution and localized optimization-type estimation. Their computational complexity and features are summarized in Table 2-2.

Table 2-2: Comparison of different APC algorithms

| Algorithm (1D)                         | Computational complexity                                | Features                                                                                     |  |  |  |  |  |  |

|----------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Matched Filter (MF)[1]                 | O(N) Per range/angular cell N as the length of waveform | Simplest and standard                                                                        |  |  |  |  |  |  |

| Global deconvolution-                  | Global deconvolution-type solution                      |                                                                                              |  |  |  |  |  |  |

| Normal LSE [55]                        | $O(L^2)$ per gate, L is total number of range gates     | Large computation load and sensitive to errors                                               |  |  |  |  |  |  |

| Segmented LSE[57]                      | $O(M(\frac{L}{M})^2)$ per gate, M is number of segments | Loss of information due<br>to segmentation (can be<br>improved using random<br>segmentation) |  |  |  |  |  |  |

| RLS[55]                                | $O(N^3)$ Per range/angular cell                         | Reiterative LS                                                                               |  |  |  |  |  |  |

| Improved RLS[58]                       | $O(N^2)$ Per range/angular cell                         | Reduced computation of RLS                                                                   |  |  |  |  |  |  |

| MF-RLS                                 | $O(N^2)$ Per range/angular cell                         | RLS use MF output as input                                                                   |  |  |  |  |  |  |

| conjugate gradient (CG)[59]            | $O(L^{1.5})$ , L is total number of range gates         | Another method to reduce computational load of LS                                            |  |  |  |  |  |  |

| Localized optimization-type estimation |                                                         |                                                                                              |  |  |  |  |  |  |

| RMMSE (APC)[2]                         | $O(N^3)$ Per range/angular cell                         | Reiterative MMSE with<br>no prior knowledge of<br>GT                                         |  |  |  |  |  |  |

| MF-RMMSE[51]                           | $O(KN + K^3)$ per gate, K is filter length              | RMMSE use MF output as input, usually K< <n< td=""></n<>                                     |  |  |  |  |  |  |

Certain radar systems require the completion of these FLOPs operations within a strict time window. For example, Multi-functional Phased Array Radar (MPAR).

# 2.3 Real-Time Computational Load Requirements of Pulse Compression Algorithms

The *computation complexity* of an algorithm can be measured by estimating the number of floating-point operations (FLOPs). A FLOP is considered any floating-point operation such as add, subtract, multiply, or divide. For instance, the addition of two complex numbers requires two real additions, while complex multiplication requires six operations, including four real multiplications and two real additions. In matrix computation, the number of FLOPs is generally estimated by the amount of arithmetic associated with the most deeply nested statement. In this work, the notation for the number of FLOPs per second is FLOPS.

Traditional digital pulse compression can be implemented in the time-domain by using cross-correlation, in which the number of FLOPS is given by:  $KN_{gates}N_{taps}PRF$ , where K=8 and represents the total number of FLOPs for a complex multiplication and addition.  $N_{gates}$  and  $N_{taps}$  are the number of gates and number of taps, respectively. PRF is pulse repetition frequency. In practice, it is more efficient to implement pulse compression in the frequency domain using Fast Fourier Transforms (FFTs).

Assuming pulse compression is applied to a single receive channel, the computational complexity of the frequency-domain pulse compression can be roughly estimated by this formula [12]:

$$F_{pc} = (2C_{fft-pc} + C_{mult}N_{fft-pc})PRF$$

(2.15)

where,  $N_{\it fft-pc}$  is the number of samples used in FFT/IFFT,  $C_{\it fft-pc}$  is the complexity of the FFT/IFFT for the  $N_{\it fft-pc}$  complex signal samples, and  $C_{\it mult}$  is the complexity of the point-wise complex multiplication.

$N_{\it fft-pc}$ ,  $C_{\it fft-pc}$ , and  $C_{\it mult}$  are factors related to the specific fixed-point implementation architecture and waveforms based on the required number of addition and multiplication. For the basic fixed-point implementations, we have:

$$C_{fft-pc} \approx 5N_{fft-pc} \log_2(N_{fft-pc}) \tag{2.16}$$

The design of waveform diversity that supports pulse compressor must consider the possible reconfigurable capability requirement in terms of  $N_{\it fft-pc}$ . In general, the constraint of  $N_{\it fft-pc}$  is defined by:

$$N_{fft-pc} > 2BW * T_p \tag{2.17}$$

where  $T_p$  is the pulse length (duration in  $\mu$ s), and BW is the baseband waveform modulation bandwidth expressed in MHz.

Figure 2-1: Estimation of computational load requirement for real-time matched filter pulse compressor, with different signal bandwidths and pulse length. Assuming 20% transmitter duty cycle for all cases.

Based on equations (2.15)-(2.17), an estimation of real-time computing load requirement for basic matched filter type pulse compression with different waveform parameters can be performed, and some examples are plotted in Figure 2-1. The graph of the estimation presents a stair-stepped shape due to the fixed number of points (power of two) required by the FFT operations. As is seen, for normal weather radar operations, the computational load for a single channel is generally less than 1 GFLOPS, while for wideband noise radar and high-resolution SAR/STAP, the real-time computational load can easily reach more than 40 GFLOPS. A complete digital

processor would also need front-end FIR filtering and implementation of clutter suppression, which can add more computational loads to the processor.

For APC algorithms, much higher computational loads are demanded. The computational cost per stage of the adaptive algorithms is shown in Table 2-3. Where, N is the length of the transmitted waveform, M is the number of subgroups, and K is the length of the MF-RMMSE filter.

Table 2-3: Computational cost of APC algorithms per stage.

| Algorithm                    | Computational Cost (per stage)                      |  |  |  |

|------------------------------|-----------------------------------------------------|--|--|--|

| Matched Filter (time-domain) | N                                                   |  |  |  |

| RMMSE (APC) [2]              | $6N^2 + 14N$                                        |  |  |  |

| RMMSE (FAPC) [3]             | $\frac{3N^2}{M}(1+\frac{1}{M}) + N(1+\frac{13}{M})$ |  |  |  |

| RMMSE (Parallelized)         | $N^2(\frac{5}{M^2}) + N(4 + \frac{13}{M})$          |  |  |  |

| MF-RMMSE [51]                | $(2K+1)N + \frac{K(K-1)}{2}$                        |  |  |  |

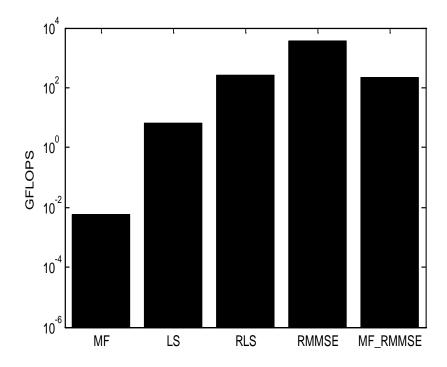

An example of the estimation of numbers of complex FLOPS for each APC algorithm is shown in Figure 2-2. This example assumes 100 range gates, 30 signal samples, *M*=5, *K*=3, and PRF=1 KHz. It can be noticed that the RMMSE algorithm requires a significant number of FLOPS, and the MF\_RMMSE approach is able to reduce the complexity to a reasonable number of FLOPs.

Figure 2-2: Computational analysis of APC algorithms.